Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1936-i-sp |

# 28/40/44-Pin Flash-Based, 8-Bit CMOS Microcontrollers with LCD Driver with nanoWatt XLP Technology

#### **Devices Included In This Data Sheet:**

- PIC16F1934

- PIC16LF1934

- PIC16F1936

- PIC16LF1936

- PIC16F1937

- PIC16LF1937

### Other PIC16(L)F193X Devices Available:

- PIC16(L)F1933 (DS41575)

- PIC16(L)F1938/9 (DS41574)

Note:

PIC16(L)F193X devices referred to in this data sheet apply to PIC16(L)F1934/6/7.

### **High-Performance RISC CPU:**

- · Only 49 Instructions to Learn:

- All single-cycle instructions except branches

- · Operating Speed:

- DC 32 MHz oscillator/clock input

- DC 125 ns instruction cycle

- Up to 16K x 14 Words of Flash Program Memory

- Up to 1024 Bytes of Data Memory (RAM)

- Interrupt Capability with Automatic Context Saving

- 16-Level Deep Hardware Stack

- · Direct, Indirect and Relative Addressing modes

- Processor Read Access to Program Memory

- Pinout Compatible to other 28/40/44-pin PIC16CXXX and PIC16FXXX Microcontrollers

#### **Special Microcontroller Features:**

- · Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range from 32 MHz to 31 kHz

- · Power-Saving Sleep mode

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Selectable between two trip points

- Disable in Sleep option

- · Multiplexed Master Clear with Pull-up/Input Pin

- · Programmable Code Protection

- High Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

- · Wide Operating Voltage Range:

- 1.8V-5.5V (PIC16F193X)

- 1.8V-3.6V (PIC16LF193X)

#### PIC16LF193X Low-Power Features:

- · Standby Current:

- 60 nA @ 1.8V, typical

- · Operating Current:

- 7.0 μA @ 32 kHz, 1.8V, typical (PIC16LF193X)

- 150 μA @ 1 MHz, 1.8V, typical (PIC16LF193X)

- Timer1 Oscillator Current:

- 600 nA @ 32 kHz, 1.8V, typical

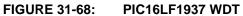

- · Low-Power Watchdog Timer Current:

- 500 nA @ 1.8V, typical (PIC16LF193X)

### **Peripheral Features:**

- Up to 35 I/O Pins and 1 Input-only Pin:

- High-current source/sink for direct LED drive

- Individually programmable interrupt-on-pin change pins

- Individually programmable weak pull-ups

- · Integrated LCD Controller:

- Up to 96 segments

- Variable clock input

- Contrast control

- Internal voltage reference selections

- Capacitive Sensing module (mTouch™)

- Up to 16 selectable channels

- A/D Converter:

- 10-bit resolution and up to 14 channels

- Selectable 1.024/2.048/4.096V voltage reference

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1

- Dedicated low-power 32 kHz oscillator driver

- 16-bit timer/counter with prescaler

- External Gate Input mode with toggle and single shot modes

- Interrupt-on-gate completion

- Timer2, 4, 6: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

- Two Capture, Compare, PWM modules (CCP)

- 16-bit Capture, max. resolution 125 ns

- 16-bit Compare, max, resolution 125 ns

- 10-bit PWM, max. frequency 31.25 kHz

- Three Enhanced Capture, Compare, PWM modules (ECCP)

- 3 PWM time-base options

- Auto-shutdown and auto-restart

- PWM steering

- Programmable dead-band delay

FIGURE 3-9: **INDIRECT ADDRESSING** 0x0000 0x0000 **Traditional Data Memory** 0x0FFF 0x0FFF 0x1000 Reserved 0x1FFF 0x2000 Linear **Data Memory** 0x29AF 0x29B0 Reserved **FSR** 0x7FFF Address 0x8000 0x0000 Range **Program** Flash Memory 0xFFFF 0x7FFF Note: Not all memory regions are completely implemented. Consult device memory tables for memory limits.

### REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | TUN     | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **TUN<4:0>:** Frequency Tuning bits

011111 = Maximum frequency

011110 =

•

•

000001 =

000000 = Oscillator module is running at the factory-calibrated frequency.

111111 =

•

•

100000 = Minimum frequency

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0                 | Register<br>on Page |

|---------|--------|--------|-------|---------------------|--------|--------|--------|-----------------------|---------------------|

| OSCCON  | SPLLEN |        | IRCF  | <3:0>               |        | 1      | SCS-   | 81                    |                     |

| OSCSTAT | T10SCR | PLLR   | OSTS  | HFIOFR              | HFIOFL | MFIOFR | LFIOFR | HFIOFS                | 82                  |

| OSCTUNE | 1      | -      |       |                     | TUN    | <5:0>  |        |                       | 83                  |

| PIE2    | OSFIE  | C2IE   | C1IE  | EEIE                | BCLIE  | LCDIE  | _      | CCP2IE <sup>(1)</sup> | 100                 |

| PIR2    | OSFIF  | C2IF   | C1IF  | EEIF                | BCLIF  | LCDIF  | _      | CCP2IF <sup>(1)</sup> | 103                 |

| T1CON   | TMR1C  | S<1:0> | T1CKP | T1CKPS<1:0> T1OSCEN |        |        | _      | TMR10N                | 203                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F1934 only.

#### TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name          | Bits | Bit -/7 | Bit -/6 | Bit 13/5              | Bit 12/4 | Bit 11/3 | Bit 10/2  | Bit 9/1 | Bit 8/0 | Register on Page |  |

|---------------|------|---------|---------|-----------------------|----------|----------|-----------|---------|---------|------------------|--|

| CONFICA       | 13:8 | _       | _       | FCMEN                 | IESO     | CLKOUTEN | BOREI     | N<1:0>  | CPD     | 60               |  |

| CONFIG1       |      |         | MCLRE   | PWRTE WDTE<1:0>       |          |          | FOSC<2:0> |         |         | 62               |  |

| CONFICA       | 13:8 | _       | _       | LVP                   | DEBUG    | _        | BORV      | STVREN  | PLLEN   | 64               |  |

| CONFIG2 7:0 — |      | _       | VCAPEN  | V<1:0> <sup>(1)</sup> | _        | _        | WRT-      | <1:0>   | 64      |                  |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F1934/6/7 only.

## 12.4 PORTC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 12-12). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 12-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 12-12) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

## 12.4.1 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 12-7.

TABLE 12-7: PORTC OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup>                              |

|----------|---------------------------------------------------------------|

| RC0      | T1OSO (Timer1 Oscillator)<br>CCP2/P2B<br>RC0                  |

| RC1      | T1OSI (Timer1 Oscillator)<br>CCP2/P2A<br>RC1                  |

| RC2      | SEG3 (LCD)<br>CCP1/P1A<br>RC2                                 |

| RC3      | SEG6 (LCD)<br>SCL (MSSP)<br>SCK (MSSP)<br>RC3                 |

| RC4      | SEG11 (LCD)<br>SDA (MSSP)<br>RC4                              |

| RC5      | SEG10 (LCD)<br>SDO (MSSP)<br>RC5                              |

| RC6      | ISEG9 (LCD) TX (EUSART) CK (EUSART) CCP3/P3A, 28-pin only RC6 |

| RC7      | SEG8 (LCD)<br>DT (EUSART)<br>CCP3/P3B, 28 pin only<br>RC7     |

**Note 1:** Priority listed from highest to lowest.

#### REGISTER 12-11: PORTC: PORTC REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits

1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 12-12: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 12-13: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

Note 1: Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is

return of actual I/O pin values.

### **REGISTER 12-20: LATE: PORTE DATA LATCH REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | _   | _   | _   | _   | LATE2   | LATE1   | LATE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-3 **Unimplemented**: Read as '0'

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

#### REGISTER 12-21: ANSELE: PORTE ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1                | R/W-1                | R/W-1                |

|-------|-----|-----|-----|-----|----------------------|----------------------|----------------------|

| _     | _   | _   | _   | _   | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup> | ANSE0 <sup>(2)</sup> |

| bit 7 |     |     |     |     |                      |                      | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: ANSELE register is not implemented on the PIC16(L)F1936. Read as '0'

#### REGISTER 18-2: CMxCON1: COMPARATOR CX CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | U-0 | U-0 | R/W-0/0    | R/W-0/0 |

|---------|---------|------------|---------|-----|-----|------------|---------|

| CxINTP  | CxINTN  | CxPCH<1:0> |         | _   | _   | CxNCH<1:0> |         |

| bit 7   |         |            |         |     |     |            | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 CXINTP: Comparator Interrupt on Positive Going Edge Enable bits

1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit

0 = No interrupt flag will be set on a positive going edge of the CxOUT bit

bit 6 CXINTN: Comparator Interrupt on Negative Going Edge Enable bits

1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit

0 = No interrupt flag will be set on a negative going edge of the CxOUT bit

bit 5-4 **CxPCH<1:0>:** Comparator Positive Input Channel Select bits

00 = CxVP connects to CxIN+ pin

01 = CxVP connects to DAC Voltage Reference

10 = CxVP connects to FVR Voltage Reference

11 = CxVP connects to Vss

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 CxNCH<1:0>: Comparator Negative Input Channel Select bits

00 = CxVN connects to C12IN0- pin 01 = CxVN connects to C12IN1- pin

10 = CxVN connects to C12IN2- pin

11 = CxVN connects to C12IN3- pin

### **REGISTER 18-3: CMOUT: COMPARATOR OUTPUT REGISTER**

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |  |

|-------------|-----|-----|-----|-----|-----|--------|--------|--|

| _           | _   | _   | _   |     | _   | MC2OUT | MC1OUT |  |

| bit 7 bit 0 |     |     |     |     |     |        |        |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-2 **Unimplemented:** Read as '0'

bit 1 MC2OUT: Mirror Copy of C2OUT bit bit 0 MC1OUT: Mirror Copy of C1OUT bit

## 20.2 Option and Timer0 Control Register

### REGISTER 20-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1 |  |  |

|---------|---------|---------|---------|---------|---------|---------|---------|--|--|

| WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     | PS<2:0> |         |         |  |  |

| bit 7   |         |         |         |         |         |         | bit 0   |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 WPUEN: Weak Pull-up Enable bit

1 = All weak pull-ups are disabled (except  $\overline{MCLR}$ , if it is enabled)

0 = Weak pull-ups are enabled by individual WPUx latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of INT pin0 = Interrupt on falling edge of INT pin

bit 5 TMR0CS: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (Fosc/4)

bit 4 TMR0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is not assigned to the Timer0 module0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

Bit Value Timer<sub>0</sub> Rate 1:2 000 1:4 001 010 1:8 011 1:16 1:32 100 101 1:64 110 1:128 111 1:256

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERO

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register on Page |

|------------|------------------------|--------|--------|--------|--------|---------|--------|--------|------------------|

| CPSCON0    | CPSON                  | _      | _      | _      | CPSRN  | G<1:0>  | CPSOUT | T0XCS  | 323              |

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 98               |

| OPTION_REG | WPUEN                  | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        |        | 193              |

| TMR0       | Timer0 Module Register |        |        |        |        |         |        |        | 191*             |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1 | TRISA0 | 133              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

Page provides register information.

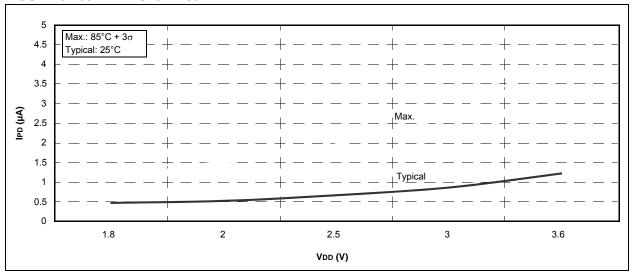

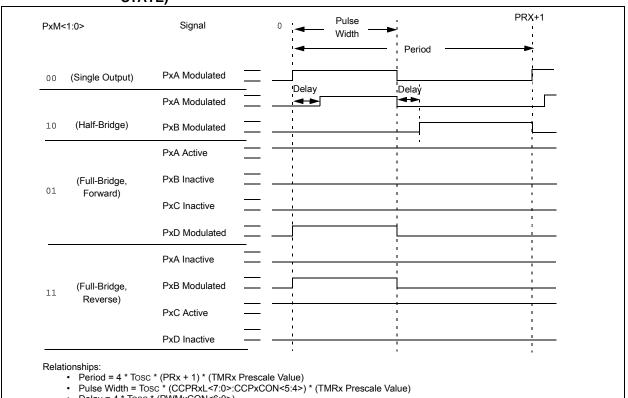

### 23.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1, ECCP2 and ECCP3, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- · TxCON registers

- · CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- · CCPxAS registers

- · PSTRxCON registers

- · PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- · Single PWM

- · Half-Bridge PWM

- · Full-Bridge PWM, Forward Mode

- · Full-Bridge PWM, Reverse Mode

- · Single PWM with PWM Steering Mode

To select an Enhanced PWM Output mode, the PxM bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 23-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Table 23-9 shows the pin assignments for various Enhanced PWM modes.

- **Note 1:** The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- **2:** Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- **4:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

## FIGURE 23-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The 8-bit timer TMRx register is concatenated with the 2-bit internal Q clock, or 2 bits of the prescaler to create the 10-bit time base.

**TABLE 23-9: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES**

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

Note 1: PWM Steering enables outputs in Single mode.

**EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH FIGURE 23-6:**

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

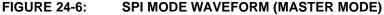

#### 24.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 24-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set).

The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 24-6, Figure 24-8 and Figure 24-9, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 24-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

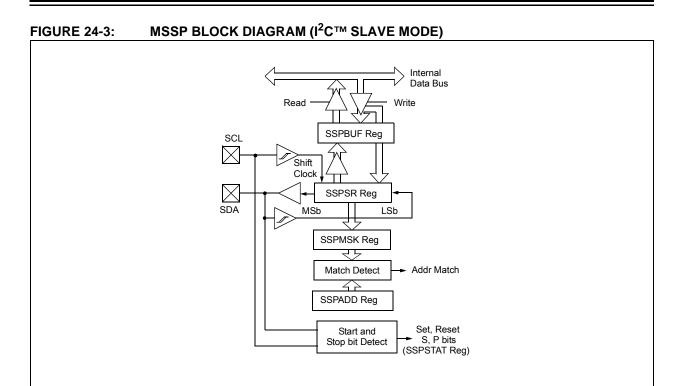

#### 24.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register, and an  $\overline{ACK}$  pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 24.5.6** "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This  $\overline{ACK}$  value is copied to the ACKSTAT bit of the SSPCON2 register. If ACKSTAT is set (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the not  $\overline{ACK}$  is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

#### 24.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPCON3 register is set, the BCLIF bit of the PIR register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

### 24.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 24-17 can be used as a reference to this list.

- Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPIF bit.

- Slave hardware generates an ACK and sets SSPIF.

- 5. SSPIF bit is cleared by user.

- Software reads the received address from SSPBUF, clearing BF.

- R/W is set so CKP was automatically cleared after the ACK.

- The slave software loads the transmit data into SSPBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master  $\overline{\mathsf{ACK}}$ s the clock will be stretched.

- 2: ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

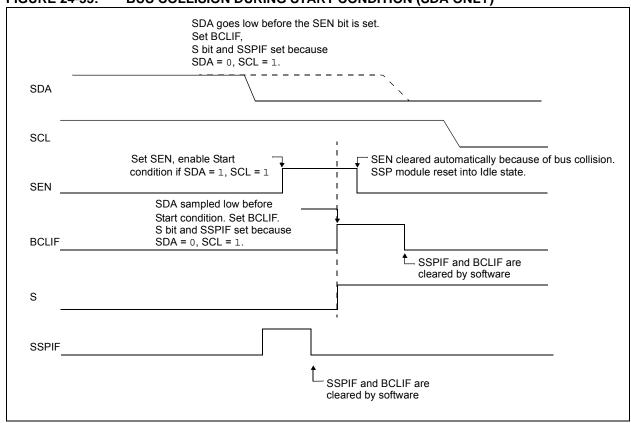

## 24.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 24-32).

- b) SCL is sampled low before SDA is asserted low (Figure 24-33).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 24-32).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 24-34). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

FIGURE 24-33: BUS COLLISION DURING START CONDITION (SDA ONLY)

#### REGISTER 27-2: LCDPS: LCD PHASE REGISTER

| R/W-0/0     | R/W-0/0 | R-0/0 | R-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-1/1 |  |

|-------------|---------|-------|-------|---------|---------|---------|---------|--|

| WFT         | BIASMD  | LCDA  | WA    | LP<3:0> |         |         |         |  |

| bit 7 bit ( |         |       |       |         |         |         |         |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared C = Only clearable bit

bit 7 WFT: Waveform Type bit

1 = Type-B phase changes on each frame boundary

0 = Type-A phase changes within each common type

bit 6 BIASMD: Bias Mode Select bit

When LMUX<1:0> = 00:

0 = Static Bias mode (do not set this bit to '1')

When LMUX<1:0> = 01:

1 = 1/2 Bias mode

0 = 1/3 Bias mode

When LMUX<1:0> = 10:

1 = 1/2 Bias mode

0 = 1/3 Bias mode

When LMUX<1:0> = 11:

0 = 1/3 Bias mode (do not set this bit to '1')

bit 5 LCDA: LCD Active Status bit

1 = LCD Driver module is active

0 = LCD Driver module is inactive

bit 4 WA: LCD Write Allow Status bit

1 = Writing to the LCDDATAn registers is allowed

0 = Writing to the LCDDATAn registers is not allowed

bit 3-0 LP<3:0>: LCD Prescaler Selection bits

1111 = 1:16

1110 = 1:15

1101 = 1:14

1100 = 1:13

1011 = 1:12

1010 = 1:11

1001 = 1:10

1000 = 1:9

0111 = 1:8

0111 - 1.0

0110 = 1:70101 = 1:6

0100 = 1:5

0011 = 1:4

0010 = 1:3

0001 = 1:2

0000 = 1:1

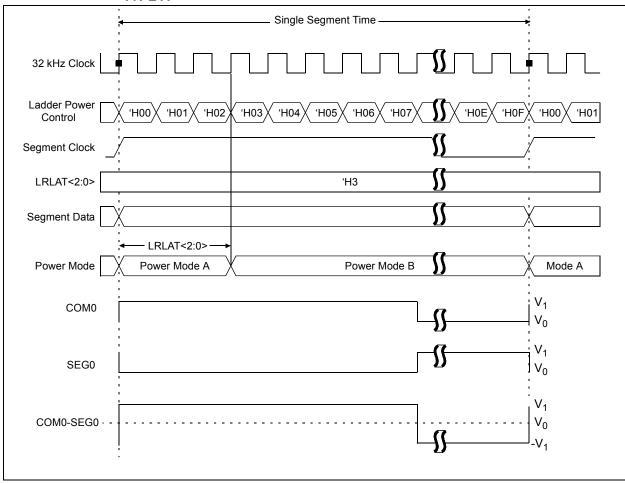

## 27.4.3 AUTOMATIC POWER MODE SWITCHING

As an LCD segment is electrically only a capacitor, current is drawn only during the interval where the voltage is switching. To minimize total device current, the LCD internal reference ladder can be operated in a different power mode for the transition portion of the duration. This is controlled by the LCDRL register (Register 27-7).

The LCDRL register allows switching between two power modes, designated 'A' and 'B'. 'A' Power mode is active for a programmable time, beginning at the time when the LCD segments transition. 'B' Power mode is the remaining time before the segments or commons change again. The LRLAT<2:0> bits select how long, if any, that the 'A' Power mode is active. Refer to Figure 27-4.

To implement this, the 5-bit prescaler used to divide the 32 kHz clock down to the LCD controller's 1 kHz base rate is used to select the power mode.

FIGURE 27-4: LCD INTERNAL REFERENCE LADDER POWER MODE SWITCHING DIAGRAM – TYPE A

TABLE 30-4: CLKOUT AND I/O TIMING PARAMETERS

|              | Standard Operating Conditions (unless otherwise stated) Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |                                                           |               |      |      |       |                |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|------|------|-------|----------------|--|--|--|--|

| Param<br>No. | Sym.                                                                                                                                       | Characteristic                                            | Min.          | Тур† | Max. | Units | Conditions     |  |  |  |  |

| OS11         | TosH2ckL                                                                                                                                   | Fosc↑ to CLKOUT↓ (1)                                      | _             |      | 70   | ns    | VDD = 3.3-5.0V |  |  |  |  |

| OS12         | TosH2ckH                                                                                                                                   | Fosc↑ to CLKOUT↑ (1)                                      | _             |      | 72   | ns    | VDD = 3.3-5.0V |  |  |  |  |

| OS13         | TckL2ioV                                                                                                                                   | CLKOUT↓ to Port out valid <sup>(1)</sup>                  | _             |      | 20   | ns    |                |  |  |  |  |

| OS14         | TioV2ckH                                                                                                                                   | Port input valid before CLKOUT <sup>(1)</sup>             | Tosc + 200 ns | _    | _    | ns    |                |  |  |  |  |

| OS15         | TosH2ioV                                                                                                                                   | Fosc↑ (Q1 cycle) to Port out valid                        | _             | 50   | 70*  | ns    | VDD = 3.3-5.0V |  |  |  |  |

| OS16         | TosH2ioI                                                                                                                                   | Fosc↑ (Q2 cycle) to Port input invalid (I/O in hold time) | 50            | _    | _    | ns    | VDD = 3.3-5.0V |  |  |  |  |

| OS17         | TioV2osH                                                                                                                                   | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)  | 20            | _    | _    | ns    |                |  |  |  |  |

| OS18         | TioR                                                                                                                                       | Port output rise time                                     | _             | 40   | 72   | ns    | VDD = 1.8V     |  |  |  |  |

|              |                                                                                                                                            |                                                           | _             | 15   | 32   |       | VDD = 3.3-5.0V |  |  |  |  |

| OS19         | TioF                                                                                                                                       | Port output fall time                                     | _             | 28   | 55   | ns    | VDD = 1.8V     |  |  |  |  |

|              |                                                                                                                                            |                                                           | _             | 15   | 30   |       | VDD = 3.3-5.0V |  |  |  |  |

| OS20*        | Tinp                                                                                                                                       | INT pin input high or low time                            | 25            |      |      | ns    |                |  |  |  |  |

| OS21*        | Tioc                                                                                                                                       | Interrupt-on-change new input level time                  | 25            | _    | _    | ns    |                |  |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

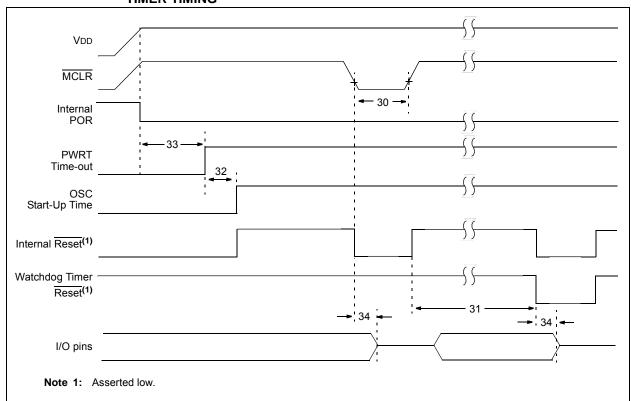

FIGURE 30-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

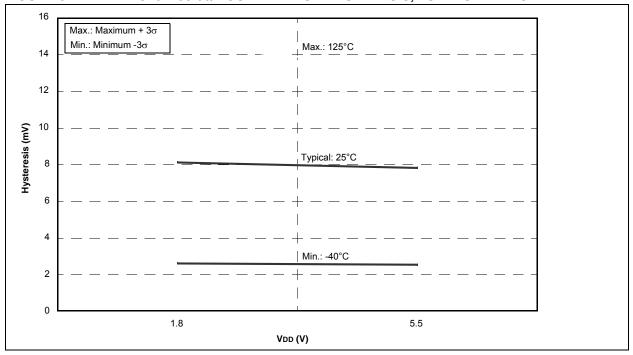

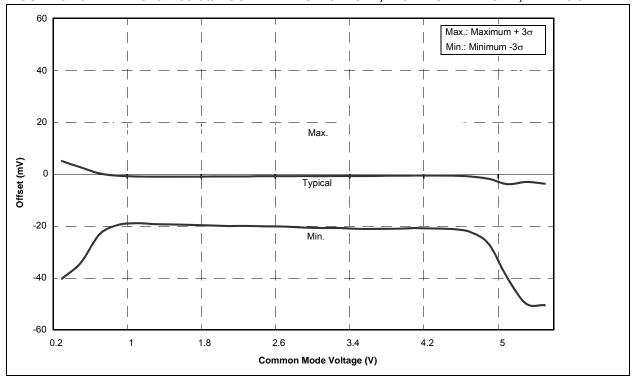

FIGURE 31-7: PIC16F1934/6/7 COMPARATOR HYSTERESIS, LOW-POWER MODE

FIGURE 31-8: PIC16F1934/6/7 COMPARATOR OFFSET, HIGH-POWER MODE, VDD = 5.5V

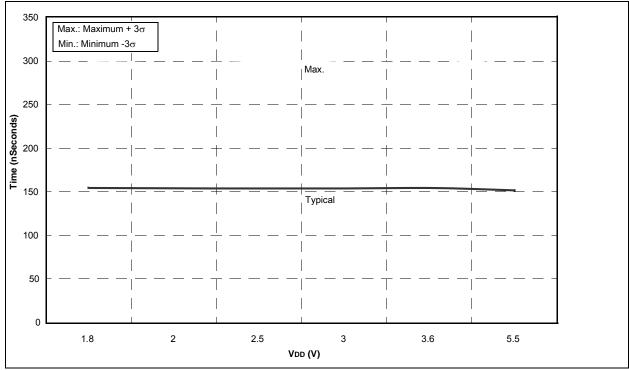

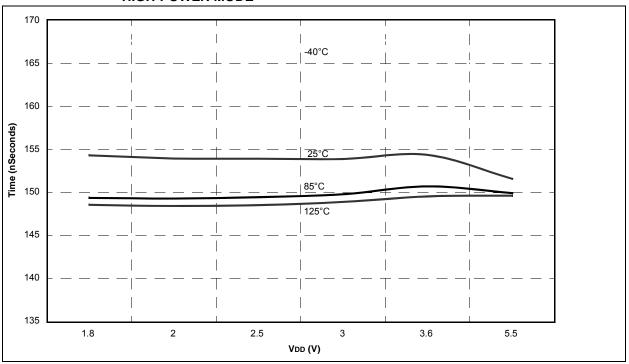

FIGURE 31-10: TYPICAL COMPARATOR RESPONSE TIME OVER TEMPERATURE, HIGH-POWER MODE

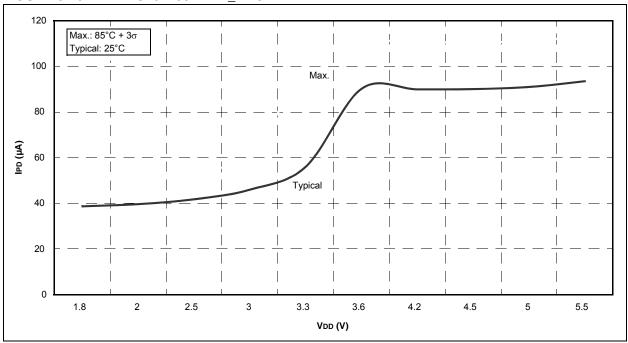

FIGURE 31-67: PIC16F1937 FVR\_ADC