Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1936t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

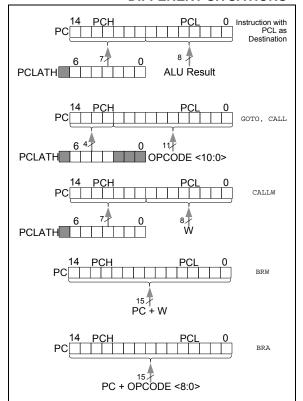

## 3.3 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-4 shows the five situations for the loading of the PC.

FIGURE 3-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper 7 bits to the PCLATH register. When the lower 8 bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

#### 3.3.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

### 3.3.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.3.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

NOTES:

#### **REGISTER 4-1: CONFIGURATION WORD 1**

| R/P-1/1              | R/P-1/1                                                                                                                                           | R/P-1/1                                                                       | R/P-1/1                                                | R/P-1/1                                 | R/P-1/1              | R/P-1/1           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|----------------------|-------------------|

| FCMEN                | IESO                                                                                                                                              | CLKOUTEN                                                                      | BOREN1                                                 | BOREN0                                  | CPD                  | CP                |

| oit 13               |                                                                                                                                                   | ·                                                                             |                                                        |                                         |                      | bit               |

| R/P-1/1              | R/P-1/1                                                                                                                                           | R/P-1/1                                                                       | R/P-1/1                                                | R/P-1/1                                 | R/P-1/1              | R/P-1/1           |

| MCLRE                | PWRTE                                                                                                                                             | WDTE1                                                                         | WDTE0                                                  | FOSC2                                   | FOSC1                | FOSC0             |

| bit 6                |                                                                                                                                                   |                                                                               |                                                        |                                         |                      | bit               |

| Legend:              |                                                                                                                                                   |                                                                               |                                                        |                                         |                      |                   |

| R = Readable bit     |                                                                                                                                                   | P = Programmab                                                                | le bit                                                 | U = Unimplemente                        | ed bit_read as '1'   |                   |

| '0' = Bit is cleared |                                                                                                                                                   | '1' = Bit is set                                                              |                                                        | •                                       | lank or after Bulk E | rase              |

| bit is cleared       |                                                                                                                                                   | 1 Dit io oct                                                                  |                                                        |                                         |                      |                   |

| bit 13               | 1 = Fail-Safe Clo                                                                                                                                 | fe Clock Monitor En<br>ock Monitor is enable<br>ock Monitor is disabl         | ed                                                     |                                         |                      |                   |

| bit 12               | 1 = Internal/Exte                                                                                                                                 | xternal Switchover b<br>rnal Switchover moo<br>rnal Switchover moo            | de is enabled                                          |                                         |                      |                   |

| bit 11               | 1 = CLKOUT fu                                                                                                                                     | ock Out Enable bit<br>nction is disabled. I<br>nction is enabled or           |                                                        | ction on RA6/CLKOU                      | TL                   |                   |

| bit 10-9             | 11 = BOR enable<br>10 = BOR enable                                                                                                                | ed during operation<br>lled by SBOREN bi                                      | and disabled in Sle                                    |                                         |                      |                   |

| bit 8                |                                                                                                                                                   | Protection bit <sup>(2)</sup><br>y code protection is<br>y code protection is |                                                        |                                         |                      |                   |

| bit 7                | <b>CP</b> : Code Protection bit <sup>(3)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled |                                                                               |                                                        |                                         |                      |                   |

| bit 6                | MCLRE: RE3/MG<br>If LVP bit = 1:<br>This bit is igr<br>If LVP bit = 0:<br>1 = RE3/MC                                                              | CLR/VPP Pin Function                                                          | on Select bit<br>is <del>MCLR</del> ; Wea <u>k pul</u> | I-up enabled.<br>R internally disabled; | Weak pull-up unde    | r control of WPUE |

| bit 5                | bit<br><b>PWRTE:</b> Power-<br>1 = PWRT disal<br>0 = PWRT enab                                                                                    |                                                                               | (1)                                                    |                                         |                      |                   |

| bit 4-3              | WDTE<1:0>: Wa<br>11 = WDT enabl<br>10 = WDT enabl                                                                                                 | atchdog Timer Enab                                                            | d disabled in Slee                                     |                                         |                      |                   |

3: The entire program memory will be erased when the code protection is turned off.

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See Section 7.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

### 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is 3 or 4 instruction cycles. For asynchronous interrupts, the latency is 3 to 5 instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

#### 7.6.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 7-2.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

#### **REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1**

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE  | TMR2IE  | TMR1IE  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:                                              |                                                                                                                       |                                |                                                       |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------|--|--|--|

| R = Readab                                           | le bit                                                                                                                | W = Writable bit               | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is un                                        | changed                                                                                                               | x = Bit is unknown             | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is se                                      | et                                                                                                                    |                                |                                                       |  |  |  |

| bit 7                                                |                                                                                                                       | Timer1 Gate Interrupt Enab     | lo bit                                                |  |  |  |

|                                                      |                                                                                                                       | s the Timer1 Gate Acquisition  |                                                       |  |  |  |

|                                                      |                                                                                                                       | es the Timer1 Gate Acquisition |                                                       |  |  |  |

| bit 6                                                |                                                                                                                       | Converter (ADC) Interrupt E    | -                                                     |  |  |  |

|                                                      |                                                                                                                       | s the ADC interrupt            |                                                       |  |  |  |

|                                                      | 0 = Disable                                                                                                           | es the ADC interrupt           |                                                       |  |  |  |

| bit 5                                                | RCIE: USA                                                                                                             | RT Receive Interrupt Enable    | e bit                                                 |  |  |  |

|                                                      |                                                                                                                       | s the USART receive interru    | •                                                     |  |  |  |

|                                                      | 0 = Disables the USART receive interrupt                                                                              |                                |                                                       |  |  |  |

| bit 4                                                | TXIE: USART Transmit Interrupt Enable bit                                                                             |                                |                                                       |  |  |  |

|                                                      | <ul> <li>1 = Enables the USART transmit interrupt</li> <li>0 = Disables the USART transmit interrupt</li> </ul>       |                                |                                                       |  |  |  |

| bit 3                                                | SSPIE: Synchronous Serial Port (MSSP) Interrupt Enable bit                                                            |                                |                                                       |  |  |  |

|                                                      | •                                                                                                                     | s the MSSP interrupt           |                                                       |  |  |  |

|                                                      |                                                                                                                       | es the MSSP interrupt          |                                                       |  |  |  |

| bit 2                                                | CCP1IE: C                                                                                                             | CP1 Interrupt Enable bit       |                                                       |  |  |  |

|                                                      |                                                                                                                       | s the CCP1 interrupt           |                                                       |  |  |  |

|                                                      | 0 = Disable                                                                                                           | es the CCP1 interrupt          |                                                       |  |  |  |

| bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit |                                                                                                                       |                                |                                                       |  |  |  |

|                                                      | <ol> <li>Enables the Timer2 to PR2 match interrupt</li> <li>D = Disables the Timer2 to PR2 match interrupt</li> </ol> |                                |                                                       |  |  |  |

| bit 0                                                | TMR1IE: T                                                                                                             | imer1 Overflow Interrupt En    | able bit                                              |  |  |  |

|                                                      | 1 = Enable                                                                                                            | s the Timer1 overflow interru  | ıpt                                                   |  |  |  |

|                                                      | 0 = Disable                                                                                                           | es the Timer1 overflow interr  | upt                                                   |  |  |  |

#### 7.6.7 PIR3 REGISTER

The PIR3 register contains the interrupt flag bits, as shown in Register 7-7.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| _       | CCP5IF  | CCP4IF  | CCP3IF  | TMR6IF  | —       | TMR4IF  | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

| bit 7 | Unimplemented: Read as '0'                   |

|-------|----------------------------------------------|

| bit 6 | CCP5IF: CCP5 Interrupt Flag bit              |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 5 | CCP4IF: CCP4 Interrupt Flag bit              |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 4 | CCP3IF: CCP3 Interrupt Flag bit              |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 3 | TMR6IF: TMR6 to PR6 Match Interrupt Flag bit |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 2 | Unimplemented: Read as '0'                   |

| bit 1 | TMR4IF: TMR4 to PR4 Match Interrupt Flag bit |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 0 | Unimplemented: Read as '0'                   |

|       |                                              |

NOTES:

| R/W-0/0          | R/W-0/0                                                                                                                       | R/W-0/0          | R/W-0/0          | R/W-0/0           | R/W-0/0                 | R/W-0/0          | R/W-0/0      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------------|------------------|--------------|--|

| SRSPE            | SRSCKE                                                                                                                        | SRSC2E           | SRSC1E           | SRRPE             | SRRCKE                  | SRRC2E           | SRRC1E       |  |

| bit 7            |                                                                                                                               |                  |                  |                   |                         |                  | bit 0        |  |

|                  |                                                                                                                               |                  |                  |                   |                         |                  |              |  |

| Legend:          |                                                                                                                               |                  |                  |                   |                         |                  |              |  |

| R = Readable     | bit                                                                                                                           | W = Writable     | bit              |                   | nented bit, read        |                  |              |  |

| u = Bit is unch  | anged                                                                                                                         | x = Bit is unki  |                  | -n/n = Value a    | at POR and BO           | R/Value at all o | other Resets |  |

| '1' = Bit is set |                                                                                                                               | '0' = Bit is cle | ared             |                   |                         |                  |              |  |

| 1. 1. 7          |                                                                                                                               |                  |                  |                   |                         |                  |              |  |

| bit 7            |                                                                                                                               | •                | al Set Enable b  |                   |                         |                  |              |  |

|                  | <ol> <li>SR Latch is set when the SRI pin is high.</li> <li>SRI pin has no effect on the set input of the SR Latch</li> </ol> |                  |                  |                   |                         |                  |              |  |

| bit 6            | SRSCKE: SF                                                                                                                    | R Latch Set Clo  | ock Enable bit   |                   |                         |                  |              |  |

|                  |                                                                                                                               |                  | s pulsed with S  |                   |                         |                  |              |  |

|                  | 0 = SRCLK has no effect on the set input of the SR Latch                                                                      |                  |                  |                   |                         |                  |              |  |

| bit 5            |                                                                                                                               | R Latch C2 Set   |                  |                   |                         |                  |              |  |

|                  |                                                                                                                               |                  |                  | ator output is hi | gh<br>of the SR Latch   | _                |              |  |

| bit 4            | •                                                                                                                             | R Latch C1 Set   |                  | in the set input  | of the SK Lato          | 1                |              |  |

| DIL 4            |                                                                                                                               |                  |                  | ator output is hi | ab                      |                  |              |  |

|                  |                                                                                                                               |                  |                  |                   | of the SR Latch         | า                |              |  |

| bit 3            | •                                                                                                                             |                  | al Reset Enabl   | •                 |                         |                  |              |  |

|                  |                                                                                                                               | •                | the SRI pin is   |                   |                         |                  |              |  |

|                  | 0 = SRI pin has no effect on the reset input of the SR Latch                                                                  |                  |                  |                   |                         |                  |              |  |

| bit 2            | SRRCKE: SR Latch Reset Clock Enable bit                                                                                       |                  |                  |                   |                         |                  |              |  |

|                  |                                                                                                                               |                  | n is pulsed with |                   |                         |                  |              |  |

|                  |                                                                                                                               |                  | •                | ut of the SR La   | tch                     |                  |              |  |

| bit 1            |                                                                                                                               | R Latch C2 Res   |                  |                   |                         |                  |              |  |

|                  |                                                                                                                               |                  |                  | arator output is  | high<br>ut of the SR La | tch              |              |  |

| bit 0            | •                                                                                                                             | R Latch C1 Res   |                  |                   |                         |                  |              |  |

| Dit U            |                                                                                                                               |                  |                  | arator output is  | hiah                    |                  |              |  |

|                  |                                                                                                                               |                  |                  |                   | ut of the SR La         | tch              |              |  |

|                  |                                                                                                                               | -                |                  |                   |                         |                  |              |  |

#### REGISTER 19-2: SRCON1: SR LATCH CONTROL 1 REGISTER

| Name   | Bit 7  | Bit 6  | Bit 5     | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|-----------|--------|--------|--------|--------|--------|---------------------|

| ANSELA | —      | _      | ANSA5     | ANSA4  | ANSA3  | ANSA2  | ANSA1  | ANSA0  | 134                 |

| SRCON0 | SRLEN  | S      | RCLK<2:0> | •      | SRQEN  | SRNQEN | SRPS   | SRPR   | 189                 |

| SRCON1 | SRSPE  | SRSCKE | SRSC2E    | SRSC1E | SRRPE  | SRRCKE | SRRC2E | SRRC1E | 190                 |

| TRISA  | TRISA7 | TRISA6 | TRISA5    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 133                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the SR Latch module.

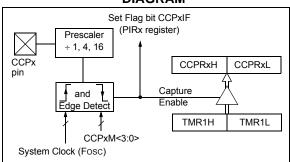

### 23.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, ECCP3, CCP4 and CCP5.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 23-1 shows a simplified diagram of the Capture operation.

#### 23.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON register. Refer to **Section 12.1 "Alternate Pin Function"** for more details.

Note: If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 23-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 23.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 23.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

### 23.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 23-1 demonstrates the code to perform this function.

#### EXAMPLE 23-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL CCPxCON  | ;Set Bank bits to point |

|------------------|-------------------------|

|                  | ;to CCPxCON             |

| CLRF CCPxCON     | ;Turn CCP module off    |

| MOVLW NEW_CAPT_P | 5;Load the W reg with   |

|                  | ;the new prescaler      |

|                  | ;move value and CCP ON  |

| MOVWF CCPxCON    | ;Load CCPxCON with this |

|                  | ;value                  |

### 23.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

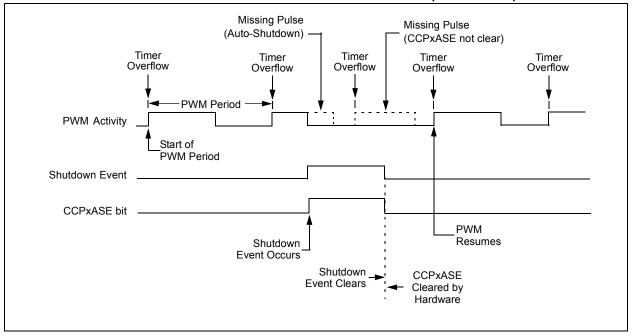

#### 23.4.4 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the PWMxCON register.

If auto-restart is enabled, the CCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCPxASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 23-15: PWM AUTO-SHUTDOWN WITH AUTO-RESTART (PXRSEN = 1)

| FIGURE 24-9: | SPI MODE WAVEFORM | (SLAVE MODE WITH CKE = 0) |  |

|--------------|-------------------|---------------------------|--|

|              |                   |                           |  |

|                                                | ۱.<br>۲ |                                       |                                       |                                                                    |             |                  |                    |                                  |                   |                           | <br>{(                       |

|------------------------------------------------|---------|---------------------------------------|---------------------------------------|--------------------------------------------------------------------|-------------|------------------|--------------------|----------------------------------|-------------------|---------------------------|------------------------------|

| SCK<br>(38 <sup>2</sup> = <u>0</u><br>CKE = 0) | -       |                                       |                                       |                                                                    |             |                  |                    |                                  |                   |                           | 4<br>3<br>4<br>3<br><u>4</u> |

|                                                |         | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | ·<br>· · · · · · · · · · · · · · · · · · ·                         | -<br>       | ;<br>;<br>;      |                    |                                  |                   | ·<br>•<br>•               | (<br>()<br>                  |

| 80X<br>(389 * 5<br>(389 * 6)                   |         |                                       |                                       |                                                                    |             |                  |                    |                                  |                   |                           |                              |

| VANDER EN<br>SERVERIE<br>VIERE                 |         |                                       | : •<br>; •<br>; •                     | د ،<br>د<br>د                                                      | ,<br>,<br>, | <<br>;<br>;<br>; | c<br>s<br>s        | ><br>-<br>-<br>                  | , ,<br>, ,<br>, , | ,<br>;<br>;<br>,          |                              |

| \$920                                          |         | K ber                                 |                                       | K bë s                                                             | X 338.4     | X 288.3          | x<br>Xana z        | X 68                             | X                 | 68 G                      | 2,<br>* 15,<br>3,2<br>*      |

| - 903                                          |         |                                       |                                       |                                                                    |             |                  |                    | //////////////////////////////// |                   |                           | 7<br>3<br>4                  |

| ingni<br>Sæmpie                                |         | 1981 (?<br>                           |                                       |                                                                    | 4-          |                  | ;<br>;<br>;;<br>;; | . 49.<br>                        | · · ·             | 2 * /<br>:<br>:<br>:<br>: |                              |

| gi Salihili<br>Internapa<br>Pilang             |         | :<br>:<br>:<br>:                      | · · · · · · · · · · · · · · · · · · · | > 3<br>> 3<br>> 3<br>> 3<br>> 3<br>> 3<br>> 3<br>> 3<br>> 3<br>> 3 |             |                  | ><br>><br><<br><   | •<br>•<br>•<br>•                 | · · ·             |                           |                              |

| - 798<br>SSPSR 20<br>SSPSR 20                  |         | · · · · · · · · · · · · · · · · · · · | , , , , , , , , , , , , , , , , , , , | <                                                                  |             | ;<br>;<br>;      | -<br>s<br>s<br>5   | ,<br>;<br>;                      | · :               | ц.                        |                              |

| -<br>Vaile Collision<br>detection scave        |         |                                       |                                       |                                                                    |             |                  |                    |                                  | ·                 |                           |                              |

#### FIGURE 24-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| SS<br>New Optional                 |             |                                                             |            | /        |

|------------------------------------|-------------|-------------------------------------------------------------|------------|----------|

| SCK<br>(CKP = <u>0</u><br>CKE = 1) |             | ļ                                                           |            |          |

| SCK<br>(CKP = 1<br>CKE = 1)        |             |                                                             |            |          |

| Write to<br>SSPBUF                 |             | 1 1 1<br>1 1 1<br>1 1 1<br>1 1 1<br>1 1 1<br>1 1 1<br>1 1 1 |            |          |

| SDO                                | bit 7 bit 6 | bit 5 bit 4 bit                                             |            |          |

| SDI                                | bit 7       |                                                             |            | bit 0    |

| Input<br>Sample                    | <u> </u>    | <u>↑</u> ↑ ↑                                                | <u>↑</u> ↑ | <b>↑</b> |

| SSPIF<br>Interrupt<br>Flag         |             |                                                             |            |          |

| SSPSR to<br>SSPBUF                 |             | 1 1 1<br>1 1 1<br>1 1 1<br>1 1                              |            |          |

| Wite Collision                     |             |                                                             |            |          |

## 25.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

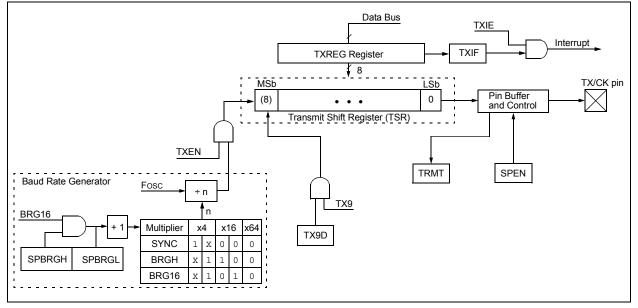

Block diagrams of the EUSART transmitter and receiver are shown in Figure 25-1 and Figure 25-2.

#### FIGURE 25-1: EUSART TRANSMIT BLOCK DIAGRAM

|        |                | <b>SYNC</b> = 0, <b>BRGH</b> = 1, <b>BRG16</b> = 0 |                             |                |            |                             |                |            |                             |                  |            |                             |

|--------|----------------|----------------------------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000                                          | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —              | _                                                  | —                           | _              |            | _                           |                |            | _                           | 300              | 0.16       | 207                         |

| 1200   | —              | —                                                  | —                           | 1202           | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16                                               | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16                                               | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00       | 23                          | —                | _          | _                           |

| 10417  | 10417          | 0.00                                               | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231          | 0.16                                               | 25                          | 19.23k         | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | _                | _          | _                           |

| 57.6k  | 55556          | -3.55                                              | 8                           | —              | _          | _                           | 57.60k         | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | —              | _                                                  | —                           | —              | _          | —                           | 115.2k         | 0.00       | 1                           | —                | _          | —                           |

## TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                |            |                             |                |            |                             |                |                    |                             |  |

|--------|----------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc           | : = 32.00                     | 0 MHz                       | Fosc           | = 20.00    | 0 MHz                       | Fosc           | : = 18.43  | 2 MHz                       | Fosc           | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0          | 0.00                          | 6666                        | 300.0          | -0.01      | 4166                        | 300.0          | 0.00       | 3839                        | 300.0          | 0.00               | 2303                        |  |

| 1200   | 1200           | -0.02                         | 3332                        | 1200           | -0.03      | 1041                        | 1200           | 0.00       | 959                         | 1200           | 0.00               | 575                         |  |

| 2400   | 2401           | -0.04                         | 832                         | 2399           | -0.03      | 520                         | 2400           | 0.00       | 479                         | 2400           | 0.00               | 287                         |  |

| 9600   | 9615           | 0.16                          | 207                         | 9615           | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417          | 0.00                          | 191                         | 10417          | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k         | 0.16                          | 103                         | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 57.14k         | -0.79                         | 34                          | 56.818         | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 117.6k         | 2.12                          | 16                          | 113.636        | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00               | 5                           |  |

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                |            |                             |                |            |                             |                  |            |                             |

|--------|----------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000                     | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9          | -0.02                         | 1666                        | 300.1          | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 300.5            | 0.16       | 207                         |

| 1200   | 1199           | -0.08                         | 416                         | 1202           | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16                          | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16                          | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00       | 23                          | —                | _          | _                           |

| 10417  | 10417          | 0.00                          | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19.23k         | 0.16                          | 25                          | 19.23k         | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | —                | _          | _                           |

| 57.6k  | 55556          | -3.55                         | 8                           | —              | _          | —                           | 57.60k         | 0.00       | 3                           | —                | —          | —                           |

| 115.2k | —              | _                             | —                           | _              | _          | —                           | 115.2k         | 0.00       | 1                           | _                | _          | —                           |

### 25.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRGL register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 25.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 25-7), and asynchronously if the device is in Sleep mode (Figure 25-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 25.3.3.1 Special Considerations

Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### <u>WUE Bit</u>

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| SEn                                     | SEn     | SEn               | SEn                                                   | SEn                                | SEn     | SEn     | SEn     |  |

| bit 7                                   |         |                   |                                                       |                                    |         |         | bit 0   |  |

|                                         |         |                   |                                                       |                                    |         |         |         |  |

| Legend:                                 |         |                   |                                                       |                                    |         |         |         |  |

| R = Readable b                          | oit     | W = Writable I    | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

bit 7-0 SEn: Segment Enable bits 1 = Segment function of the pin is enabled 0 = I/O function of the pin is enabled

#### REGISTER 27-6: LCDDATAn: LCD DATA REGISTERS

| R/W-x/u   |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| SEGx-COMy |

| bit 7     |           |           |           |           |           |           | bit 0     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SEGx-COMy: Pixel On bits

1 = Pixel on (dark) 0 = Pixel off (clear)

NOTES:

| ΜΟΥΨΙ            | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                                                 |

| Operation:       | $\label{eq:W} \begin{split} W &\rightarrow INDFn \\ \text{Effective address is determined by} \\ \bullet \ FSR + 1 \ (\text{preincrement}) \\ \bullet \ FSR + 1 \ (\text{predecrement}) \\ \bullet \ FSR + k \ (\text{relative offset}) \\ \text{After the Move, the FSR value will be} \\ \text{either:} \\ \bullet \ FSR + 1 \ (\text{all increments}) \\ \bullet \ FSR + 1 \ (\text{all increments}) \\ \text{Unchanged} \end{split}$ |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP     |  |

|---------|--|

| Syntax: |  |

| Syntax:          | [label] NOP   |

|------------------|---------------|

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

**No Operation**

| OPTION           | Load OPTION_REG Register with W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                            |

| Operands:        | None                                                                                                      |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to<br>OPTION_REG register.                                                      |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | OPTION                                                                                                    |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| RESET            | Software Reset                                                                   |

|------------------|----------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                    |

| Operands:        | None                                                                             |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.             |

| Status Affected: | None                                                                             |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |

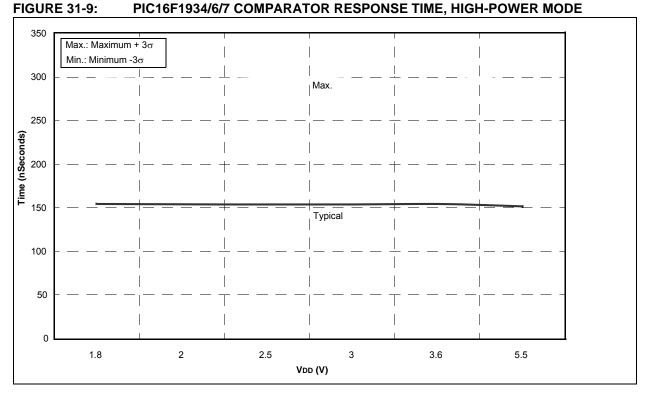

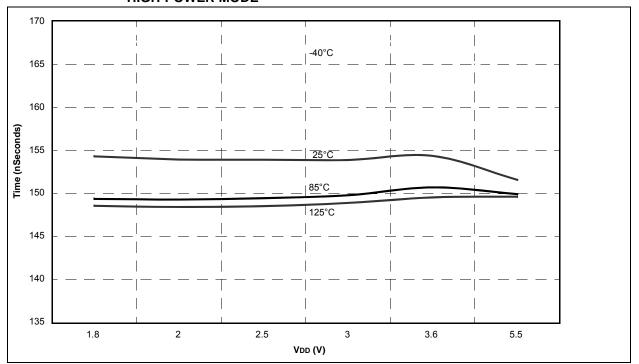

FIGURE 31-10: TYPICAL COMPARATOR RESPONSE TIME OVER TEMPERATURE, HIGH-POWER MODE

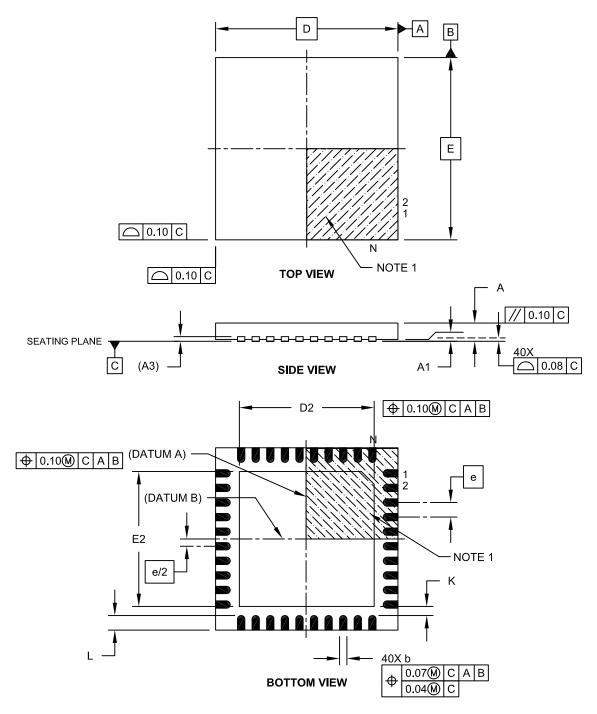

### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2