Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1936t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE 3-11:PIC16(L)F1934/6/7 MEMORYMAP, BANK 31

|      |                                                             | Bank 31                      |  |  |  |

|------|-------------------------------------------------------------|------------------------------|--|--|--|

|      | F8Ch                                                        |                              |  |  |  |

|      |                                                             | Unimplemented<br>Read as '0' |  |  |  |

|      | FE3h                                                        |                              |  |  |  |

|      | FE4h                                                        | STATUS_SHAD                  |  |  |  |

|      | FE5h                                                        | WREG_SHAD                    |  |  |  |

|      | FE6h                                                        | BSR_SHAD                     |  |  |  |

|      | FE7h                                                        | PCLATH_SHAD                  |  |  |  |

|      | FE8h                                                        | FSR0L_SHAD                   |  |  |  |

|      | FE9h                                                        | FSR0H_SHAD                   |  |  |  |

|      | FEAh                                                        | FSR1L_SHAD                   |  |  |  |

|      | FEBh                                                        | FSR1H_SHAD                   |  |  |  |

|      | FECh                                                        | —                            |  |  |  |

|      | FEDh                                                        | STKPTR                       |  |  |  |

|      | FEEh                                                        | TOSL                         |  |  |  |

|      | FEFh                                                        | TOSH                         |  |  |  |

| Lege | Legend: = Unimplemented data memory locations, read as '0'. |                              |  |  |  |

# 3.2.6 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device            | Bank(s) | Page No. |

|-------------------|---------|----------|

|                   | 0       | 39       |

|                   | 1       | 40       |

|                   | 2       | 41       |

|                   | 3       | 42       |

|                   | 4       | 43       |

|                   | 5       | 44       |

| PIC16(L)F1934/6/7 | 6       | 45       |

|                   | 7       | 46       |

|                   | 8       | 47       |

|                   | 9-14    | 48       |

|                   | 15      | 49       |

|                   | 16-30   | 51       |

|                   | 31      | 52       |

| Address                | Name         | Bit 7                       | Bit 6          | Bit 5           | Bit 4           | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------------|-----------------------------|----------------|-----------------|-----------------|---------------|-------------|---------|---------|----------------------|---------------------------------|

| Bank 5                 |              |                             |                |                 |                 |               |             |         |         |                      |                                 |

| 280h <sup>(2)</sup>    | INDF0        | Addressing<br>(not a physi  |                | ses contents o  | of FSR0H/FSR    | 0L to address | data memory | /       |         | XXXX XXXX            | XXXX XXXX                       |

| 281h <sup>(2)</sup>    | INDF1        | Addressing<br>(not a physic |                | ses contents o  | of FSR1H/FSR    | 1L to address | data memory | /       |         | XXXX XXXX            | XXXX XXXX                       |

| 282h <sup>(2)</sup>    | PCL          | Program Co                  | ounter (PC) Le | ast Significant | t Byte          |               |             |         |         | 0000 0000            | 0000 0000                       |

| 283h <sup>(2)</sup>    | STATUS       | _                           | _              | _               | TO              | PD            | Z           | DC      | С       | 1 1000               | q quuu                          |

| 284h <sup>(2)</sup>    | FSR0L        | Indirect Data               | a Memory Add   | dress 0 Low Po  | ointer          |               |             |         |         | 0000 0000            | uuuu uuuu                       |

| 285h <sup>(2)</sup>    | FSR0H        | Indirect Data               | a Memory Add   | dress 0 High P  | ointer          |               |             |         |         | 0000 0000            | 0000 0000                       |

| 286h <sup>(2)</sup>    | FSR1L        | Indirect Data               | a Memory Ado   | dress 1 Low Po  | ointer          |               |             |         |         | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(2)</sup>    | FSR1H        | Indirect Data               | a Memory Add   | dress 1 High P  | ointer          |               |             |         |         | 0000 0000            | 0000 0000                       |

| 288h <sup>(2)</sup>    | BSR          | _                           | _              | _               |                 | E             | 3SR<4:0>    |         |         | 0 0000               | 0 0000                          |

| 289h <sup>(2)</sup>    | WREG         | Working Re                  | gister         |                 |                 |               |             |         |         | 0000 0000            | uuuu uuuu                       |

| 28Ah <sup>(1, 2)</sup> | PCLATH       | _                           | Write Buffer f | or the upper 7  | bits of the Pro | gram Counter  | -           |         |         | -000 0000            | -000 0000                       |

| 28Bh <sup>(2)</sup>    | INTCON       | GIE                         | PEIE           | TMR0IE          | INTE            | IOCIE         | TMR0IF      | INTF    | IOCIF   | 0000 0000            | 0000 0000                       |

| 28Ch                   | —            | Unimplemer                  | nted           |                 |                 |               |             |         |         | —                    | —                               |

| 28Dh                   | _            | Unimpleme                   | Unimplemented  |                 |                 |               |             |         |         |                      | _                               |

| 28Eh                   | _            | Unimpleme                   | Unimplemented  |                 |                 |               |             |         |         |                      | _                               |

| 28Fh                   | —            | Unimplemer                  | Jnimplemented  |                 |                 |               |             |         |         | _                    | _                               |

| 290h                   | —            | Unimplemer                  | nted           |                 |                 |               |             |         |         | _                    | _                               |

| 291h                   | CCPR1L       | Capture/Co                  | mpare/PWM F    | Register 1 (LSE | 3)              |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 292h                   | CCPR1H       | Capture/Col                 | mpare/PWM F    | Register 1 (MS  | B)              |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 293h                   | CCP1CON      | P1M                         | <1:0>          | DC1B            | 8<1:0>          |               | CCP1M       | <3:0>   |         | 0000 0000            | 0000 0000                       |

| 294h                   | PWM1CON      | P1RSEN                      |                |                 | Р               | 1DC<6:0>      |             |         |         | 0000 0000            | 0000 0000                       |

| 295h                   | CCP1AS       | CCP1ASE                     |                | CCP1AS<2:0>     | >               | PSS1A         | C<1:0>      | PSS1E   | D<1:0>  | 0000 0000            | 0000 0000                       |

| 296h                   | PSTR1CON     | _                           | —              | —               | STR1SYNC        | STR1D         | STR1C       | STR1B   | STR1A   | 0 0001               | 0 0001                          |

| 297h                   | _            | Unimpleme                   | nted           |                 |                 |               |             |         |         | _                    | _                               |

| 298h                   | CCPR2L       | Capture/Co                  | mpare/PWM F    | Register 2 (LSI | 3)              |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 299h                   | CCPR2H       | Capture/Col                 | mpare/PWM F    | Register 2 (MS  | iB)             |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 29Ah                   | CCP2CON      | P2M                         | <1:0>          | DC2E            | 3<1:0>          |               | CCP2M       | <3:0>   |         | 0000 0000            | 0000 0000                       |

| 29Bh                   | PWM2CON      | P2RSEN                      |                | 1               | Р               | 2DC<6:0>      |             |         |         | 0000 0000            | 0000 0000                       |

| 29Ch                   | CCP2AS       | CCP2ASE                     |                | CCP2AS<2:0>     | >               | PSS2A         | C<1:0>      | PSS2E   | D<1:0>  | 0000 0000            | 0000 0000                       |

| 29Dh                   | PSTR2CON     | _                           | —              |                 | STR2SYNC        | STR2D         | STR2C       | STR2B   | STR2A   | 0 0001               | 0 0001                          |

| 29Eh                   | CCPTMRS<br>0 | C4TSEL1                     | C4TSEL0        | C3TSEL1         | C3TSEL0         | C2TSEL1       | C2TSEL0     | C1TSEL1 | C1TSEL0 | 0000 0000            | 0000 0000                       |

| 29Fh                   | CCPTMRS<br>1 | —                           | —              | —               | —               | —             | —           | C5TSE   | L<1:0>  | 00                   | 00                              |

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

4: Unimplemented, read as '1'.

NOTES:

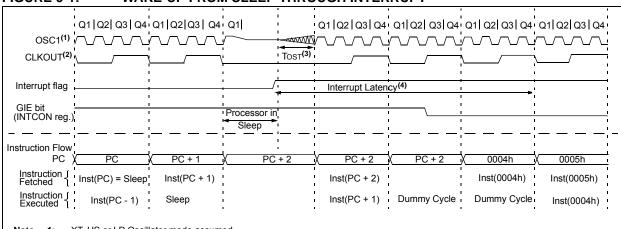

# 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

#### FIGURE 9-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP Oscillator mode assumed.

2: CLKOUT is not available in XT, HS, or LP Oscillator modes, but shown here for timing reference.

3: Tost = 1024 Tosc (drawing not to scale). This delay applies only to XT, HS or LP Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

# TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|--------|------------|--------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE | INTE       | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |

| IOCBF  | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4     | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 152                 |

| IOCBN  | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4     | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 152                 |

| IOCBP  | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4     | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 152                 |

| PIE1   | TMR1GIE | ADIE   | RCIE   | TXIE       | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 99                  |

| PIE2   | OSFIE   | C2IE   | C1IE   | EEIE       | BCLIE  | LCDIE  | _      | CCP2IE | 100                 |

| PIE3   | —       | CCP5IE | CCP4IE | CCP3IE     | TMR6IE | —      | TMR4IE | —      | 101                 |

| PIR1   | TMR1GIF | ADIF   | RCIF   | TXIF       | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 102                 |

| PIR2   | OSFIF   | C2IF   | C1IF   | EEIF       | BCLIF  | LCDIF  | _      | CCP2IF | 103                 |

| PIR3   | —       | CCP5IF | CCP4IF | CCP3IF     | TMR6IF | —      | TMR4IF | —      | 104                 |

| STATUS | _       | _      | _      | TO         | PD     | Z      | DC     | С      | 29                  |

| WDTCON | —       | —      |        | WDTPS<4:0> |        |        |        |        | 113                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used in Power-down mode.

# 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

# 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

#### EXAMPLE 11-3: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI: PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSEL

EEADRL

; Select Bank for EEPRO

MOVLW

PROG_ADDR_LO

;

MOVWF

EEADRL

; Store LSB of address

MOVLW

PROG_ADDR_HI

;

BANKSEL EEADRL

; Select Bank for EEPROM registers

MOVWL EEADRH

; Store MSB of address

EECON1,CFGS ; Do not select Configuration Space

EECON1,EEPGD ; Select Program Memory

BCF

EECON1,CFGS

BSF

INTCON,GIE ; Disable interrupts

BCF

BSF

EECON1,RD

; Initiate read

NOP

; Executed (Figure 11-1)

NOP

; Ignored (Figure 11-1)

BSF

INTCON, GIE

; Restore interrupts

MOVF

EEDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO ; Store in user location

EEDATH,W ; Get MSB of word

PROG_DATA_HI ; Store in user location

MOVE

MOVWF

```

| R/W-0/0                            | R/W-0/0                                                                                                                                                          | R/W-0/0                       | R/W/HC-0/0                 | R/W-x/q           | R/W-0/0           | R/S/HC-0/0             | R/S/HC-0/0      |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------|-------------------|-------------------|------------------------|-----------------|--|--|

| EEPGD                              | CFGS                                                                                                                                                             | LWLO                          | FREE                       | WRERR             | WREN              | WR                     | RD              |  |  |

| bit 7                              |                                                                                                                                                                  |                               |                            |                   |                   |                        | bit C           |  |  |

| Logondi                            |                                                                                                                                                                  |                               |                            |                   |                   |                        |                 |  |  |

| Legend:<br>R = Readable            | hit                                                                                                                                                              | W = Writable                  | hit                        | II – Unimplo      | monted hit rea    | d oo 'O'               |                 |  |  |

|                                    |                                                                                                                                                                  | x = Bit is unk                |                            | •                 | mented bit, read  | R/Value at all c       | than Basata     |  |  |

| S = Bit can or<br>'1' = Bit is set | •                                                                                                                                                                |                               |                            |                   |                   |                        | Inel Resels     |  |  |

| I = DILIS SEL                      |                                                                                                                                                                  | '0' = Bit is cle              | areu                       |                   | eared by hardw    | Vale                   |                 |  |  |

| bit 7                              | EEPGD: Flas                                                                                                                                                      | sh Program/Da                 | ta EEPROM M                | emory Select      | bit               |                        |                 |  |  |

|                                    |                                                                                                                                                                  | s program spa<br>s data EEPRO | ce Flash memo<br>M memory  | ory               |                   |                        |                 |  |  |

| bit 6                              |                                                                                                                                                                  |                               | EEPROM or C                | Configuration     | Select bit        |                        |                 |  |  |

|                                    | 1 = Accesse                                                                                                                                                      | s Configuration               | n, User ID and             | Device ID Reg     | gisters           |                        |                 |  |  |

|                                    |                                                                                                                                                                  | -                             | m or data EEP              | ROM Memory        | /                 |                        |                 |  |  |

| bit 5                              |                                                                                                                                                                  | Write Latches                 | •                          |                   |                   |                        |                 |  |  |

|                                    |                                                                                                                                                                  |                               |                            |                   | EPGD = 1 (prog    |                        |                 |  |  |

|                                    |                                                                                                                                                                  | next WR con ated.             | nmand does no              | ot initiate a w   | rite; only the p  | program memo           | y latches are   |  |  |

|                                    |                                                                                                                                                                  |                               | mand writes a v            | alue from EEI     | DATH:EEDATL       | into program m         | emory latche    |  |  |

|                                    |                                                                                                                                                                  |                               |                            |                   | program memo      |                        | 2               |  |  |

|                                    | If CFGS = 0 a                                                                                                                                                    | and EEPGD =                   | 0: (Accessing of           | data EEPRON       | 1)                |                        |                 |  |  |

|                                    |                                                                                                                                                                  |                               |                            |                   | é to the data El  | EPROM.                 |                 |  |  |

| bit 4                              | FREE: Progr                                                                                                                                                      | am Flash Eras                 | e Enable bit               |                   |                   |                        |                 |  |  |

|                                    | <u>If CFGS = 1</u>                                                                                                                                               | (Configuration                | <u>space)</u> OR <u>CF</u> | GS = 0 and E      | EPGD = 1 (prog    | gram Flash):           |                 |  |  |

|                                    |                                                                                                                                                                  |                               | operation on t             | he next WR c      | ommand (clear     | ed by hardware         | after comple    |  |  |

|                                    |                                                                                                                                                                  | of erase).<br>forms a write o | peration on the            | next WR con       | nmand.            |                        |                 |  |  |

|                                    |                                                                                                                                                                  |                               |                            |                   |                   |                        |                 |  |  |

|                                    |                                                                                                                                                                  |                               | <u>0:</u> (Accessing       |                   |                   | and a write av         |                 |  |  |

| hit 0                              | -                                                                                                                                                                |                               |                            | will initiate boi | n a erase cycle   | and a write cyo        | le.             |  |  |

| bit 3                              |                                                                                                                                                                  | PROM Error F                  | •                          | ram or oraco      | soquence atte     | mot or tormina         | tion (hit is so |  |  |

|                                    | 1 = Condition indicates an improper program or erase sequence attempt or termination (bit is set<br>automatically on any set attempt (write '1') of the WR bit). |                               |                            |                   |                   |                        |                 |  |  |

|                                    |                                                                                                                                                                  |                               | operation comp             |                   |                   |                        |                 |  |  |

| bit 2                              | WREN: Prog                                                                                                                                                       | ram/Erase Ena                 | able bit                   |                   |                   |                        |                 |  |  |

|                                    |                                                                                                                                                                  | rogram/erase o                |                            |                   |                   |                        |                 |  |  |

|                                    | -                                                                                                                                                                |                               | rasing of progra           | am Flash and      | data EEPROM       |                        |                 |  |  |

| bit 1                              | WR: Write Co                                                                                                                                                     |                               |                            |                   | , .               |                        |                 |  |  |

|                                    |                                                                                                                                                                  |                               |                            |                   | n/erase operation | on.<br>operation is co | mnlete          |  |  |

|                                    |                                                                                                                                                                  |                               | e set (not cleare          |                   |                   |                        | inpiete.        |  |  |

|                                    |                                                                                                                                                                  |                               |                            |                   | OM is complete    | e and inactive.        |                 |  |  |

| bit 0                              | RD: Read Co                                                                                                                                                      | ontrol bit                    |                            |                   |                   |                        |                 |  |  |

|                                    |                                                                                                                                                                  |                               |                            |                   |                   | one cycle. RD          | is cleared in   |  |  |

|                                    |                                                                                                                                                                  |                               | an only be set             |                   |                   |                        |                 |  |  |

|                                    |                                                                                                                                                                  | i miliale a prog              | ram Flash or d             | αια ΕΕΓΚΟΙΝ       | udia iedu.        |                        |                 |  |  |

# REGISTER 11-5: EECON1: EEPROM CONTROL 1 REGISTER

# 13.6 Interrupt-On-Change Registers

#### REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER

|                 |         | 0' = Bit is clear |         |                                                       | at FOR and BO    | rv value at all c | iner Reseis |  |

|-----------------|---------|-------------------|---------|-------------------------------------------------------|------------------|-------------------|-------------|--|

| u = Bit is unch | anged   | x = Bit is unkr   | NOWD    | -n/n = Value at POR and BOR/Value at all other Resets |                  |                   |             |  |

| R = Readable    | bit     | W = Writable      | bit     | U = Unimpler                                          | nented bit, read | as '0'            |             |  |

| Legend:         |         |                   |         |                                                       |                  |                   |             |  |

|                 |         |                   |         |                                                       |                  |                   |             |  |

| bit 7           | •       | •                 | •       |                                                       |                  |                   | bit 0       |  |

| IOCBP7          | IOCBP6  | IOCBP5            | IOCBP4  | IOCBP3                                                | IOCBP2           | IOCBP1            | IOCBP0      |  |

| R/W-0/0         | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0          | R/W-0/0           | R/W-0/0     |  |

bit 7-0

IOCBP<7:0>: Interrupt-on-Change Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 IOCBN<7:0>: Interrupt-on-Change Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

# REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCBF<7:0>: Interrupt-on-Change Flag bits

- 1 = An enabled change was detected on the associated pin.

Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

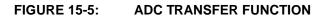

# 15.2 ADC Operation

# 15.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 15.2.6 "A/D Conver-     |

|       | sion Procedure".                         |

# 15.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 15.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

# 15.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

# 15.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 15-2: SPECIAL EVENT TRIGGER

| Device            | CCPx/ECCPx |  |  |  |  |  |

|-------------------|------------|--|--|--|--|--|

| PIC16(L)F1934/6/7 | CCP5       |  |  |  |  |  |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 23.0 "Capture/Compare/PWM Modules" for more information.

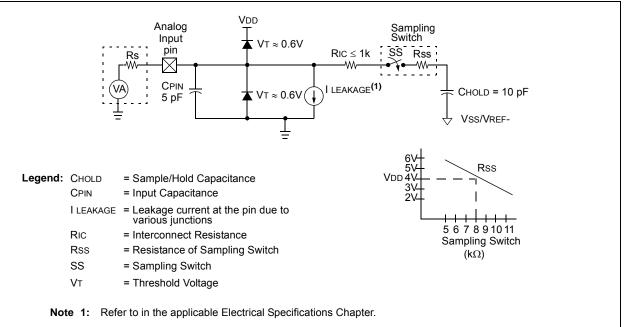

# FIGURE 15-4: ANALOG INPUT MODEL

#### 23.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

| Name                 | Bit 7                                          | Bit 6          | Bit 5                                                        | Bit 4                                             | Bit 3      | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|------------------------------------------------|----------------|--------------------------------------------------------------|---------------------------------------------------|------------|-----------------------|-----------------------|-----------------------|---------------------|

| APFCON               | _                                              | CCP3SEL        | T1GSEL                                                       | P2BSEL                                            | SRNQSEL    | C2OUTSEL              | SSSEL                 | CCP2SEL               | 131                 |

| CCPxCON              | N PxM<1:0> <sup>(1)</sup> DCxB<1:0> CCPxM<3:0> |                |                                                              |                                                   |            |                       |                       |                       |                     |

| CCPRxL               | Capture/Compare/PWM Register x Low Byte (LSB)  |                |                                                              |                                                   |            |                       |                       |                       | 212                 |

| CCPRxH               | Capture/Co                                     | mpare/PWM      | Register x I                                                 | High Byte (M                                      | ISB)       |                       |                       |                       | 212                 |

| INTCON               | GIE                                            | PEIE           | TMR0IE                                                       | INTE                                              | IOCIE      | TMR0IF                | INTF                  | IOCIF                 | 98                  |

| PIE1                 | TMR1GIE                                        | ADIE           | RCIE                                                         | TXIE                                              | SSPIE      | CCP1IE                | TMR2IE                | TMR1IE                | 99                  |

| PIE2                 | OSFIE                                          | C2IE           | C1IE                                                         | EEIE                                              | BCLIE      | LCDIE                 | _                     | CCP2IE                | 100                 |

| PIE3                 | —                                              | CCP5IE         | CCP4IE                                                       | CCP3IE                                            | TMR6IE     | _                     | TMR4IE                | _                     | 101                 |

| PIR1                 | TMR1GIF                                        | ADIF           | RCIF                                                         | TXIF                                              | SSPIF      | CCP1IF                | TMR2IF                | TMR1IF                | 102                 |

| PIR2                 | OSFIF                                          | C2IF           | C1IF                                                         | EEIF                                              | BCLIF      | LCDIF                 | _                     | CCP2IF                | 103                 |

| PIR3                 | —                                              | CCP5IF         | CCP4IF                                                       | CCP3IF                                            | TMR6IF     | _                     | TMR4IF                | —                     | 104                 |

| T1CON                | TMR1C                                          | S<1:0>         | T1CKPS<1:0>                                                  |                                                   | T1OSCEN    | T1SYNC                | _                     | TMR10N                | 203                 |

| T1GCON               | TMR1GE                                         | T1GPOL         | T1GTM                                                        | T1GSPM                                            | T1GGO/DONE | T1GVAL                | T1GSS<1:0>            |                       | 204                 |

| TMR1L                | Holding Reg                                    | gister for the | r for the Least Significant Byte of the 16-bit TMR1 Register |                                                   |            |                       | 199                   |                       |                     |

| TMR1H                | Holding Reg                                    | gister for the | Most Signifi                                                 | Most Significant Byte of the 16-bit TMR1 Register |            |                       |                       |                       | 199                 |

| TRISA                | TRISA7                                         | TRISA6         | TRISA5                                                       | TRISA4                                            | TRISA3     | TRISA2                | TRISA1                | TRISA0                | 133                 |

| TRISB                | TRISB7                                         | TRISB6         | TRISB5                                                       | TRISB4                                            | TRISB3     | TRISB2                | TRISB1                | TRISB0                | 138                 |

| TRISC                | TRISC7                                         | TRISC6         | TRISC5                                                       | TRISC4                                            | TRISC3     | TRISC2                | TRISC1                | TRISC0                | 142                 |

| TRISD <sup>(2)</sup> | TRISD7                                         | TRISD6         | TRISD5                                                       | TRISD4                                            | TRISD3     | TRISD2                | TRISD1                | TRISD0                | 145                 |

| TRISE                |                                                |                |                                                              | —                                                 | _(3)       | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 148                 |

| <b>TABLE 23-2:</b> | SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE |

|--------------------|----------------------------------------------|

|                    |                                              |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode.

Note 1: Applies to ECCP modules only.

2: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

3: Unimplemented, read as '1'.

#### 24.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

| Name                                                            | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3         | Bit 2            | Bit 1  | Bit 0   | Register<br>on Page |

|-----------------------------------------------------------------|---------|---------|--------|--------|---------------|------------------|--------|---------|---------------------|

| ANSELA                                                          | —       |         | ANSA5  | ANSA4  | ANSA3         | ANSA3 ANSA2      |        | ANSA0   | 134                 |

| APFCON                                                          | —       | CCP3SEL | T1GSEL | P2BSEL | SRNQSEL       | SRNQSEL C2OUTSEL |        | CCP2SEL | 131                 |

| INTCON                                                          | GIE     | PEIE    | TMR0IE | INTE   | IOCIE         | DCIE TMR0IF      |        | IOCIF   | 98                  |

| PIE1                                                            | TMR1GIE | ADIE    | RCIE   | TXIE   | SSP1IE        | SSP1IE CCP1IE    |        | TMR1IE  | 99                  |

| PIR1                                                            | TMR1GIF | ADIF    | RCIF   | TXIF   | SSP1IF CCP1IF |                  | TMR2IF | TMR1IF  | 102                 |

| SSPBUF Synchronous Serial Port Receive Buffer/Transmit Register |         |         |        |        |               |                  |        |         | 243*                |

| SSPCON1                                                         | WCOL    | SSPOV   | SSPEN  | CKP    | CKP SSPM<3:0> |                  |        |         | 287                 |

| SSPCON3                                                         | ACKTIM  | PCIE    | SCIE   | BOEN   | SDAHT         | SBCDE            | AHEN   | DHEN    | 289                 |

| SSPSTAT                                                         | SMP     | CKE     | D/A    | Р      | S             | R/W              | UA     | BF      | 286                 |

| TRISA                                                           | TRISA7  | TRISA6  | TRISA5 | TRISA4 | TRISA3 TRISA2 |                  | TRISA1 | TRISA0  | 133                 |

| TRISC                                                           | TRISC7  | TRISC6  | TRISC5 | TRISC4 | TRISC3 TRISB2 |                  | TRISC1 | TRISC0  | 142                 |

#### TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Page provides register information.

#### 24.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPIF interrupt is set.

Figure 24-18 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- 2. Master sends Start condition; the S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCL line the CKP bit is cleared and SSPIF interrupt is generated.

- 4. Slave software clears SSPIF.

- Slave software reads ACKTIM bit of SSPCON3 register, and R/W and D/A of the SSPSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets ACKDT bit of the SSPCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPIF.

- 12. Slave loads value to transmit to the master into SSPBUF setting the BF bit.

Note: SSPBUF cannot be loaded until after the ACK.

13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

## 25.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

#### 25.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 25.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is

set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 25.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the 8 Least Significant bits from the RCREG.

# 25.4.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

## 27.4 LCD Bias Internal Reference Ladder

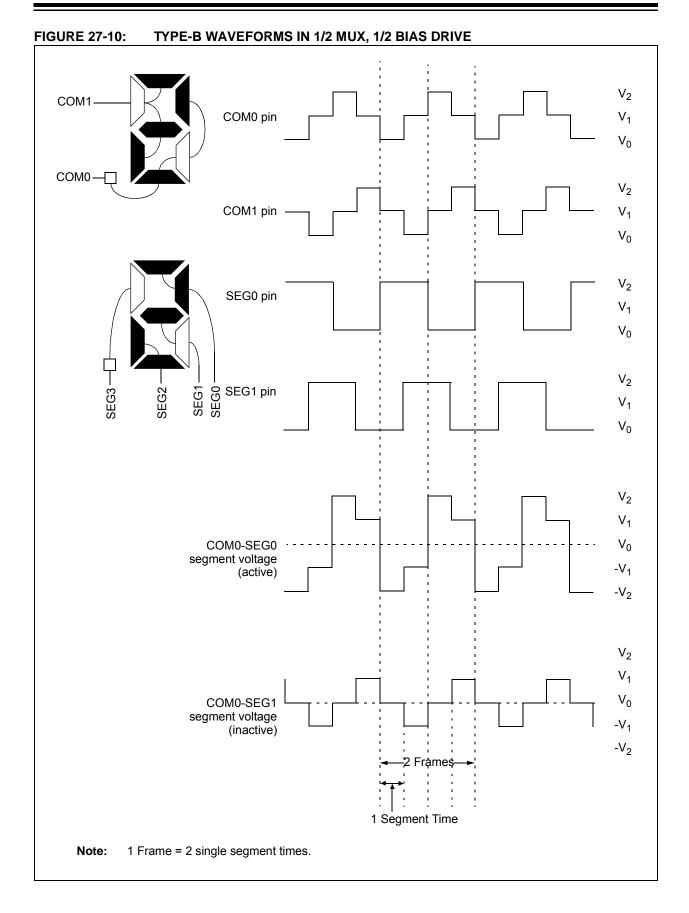

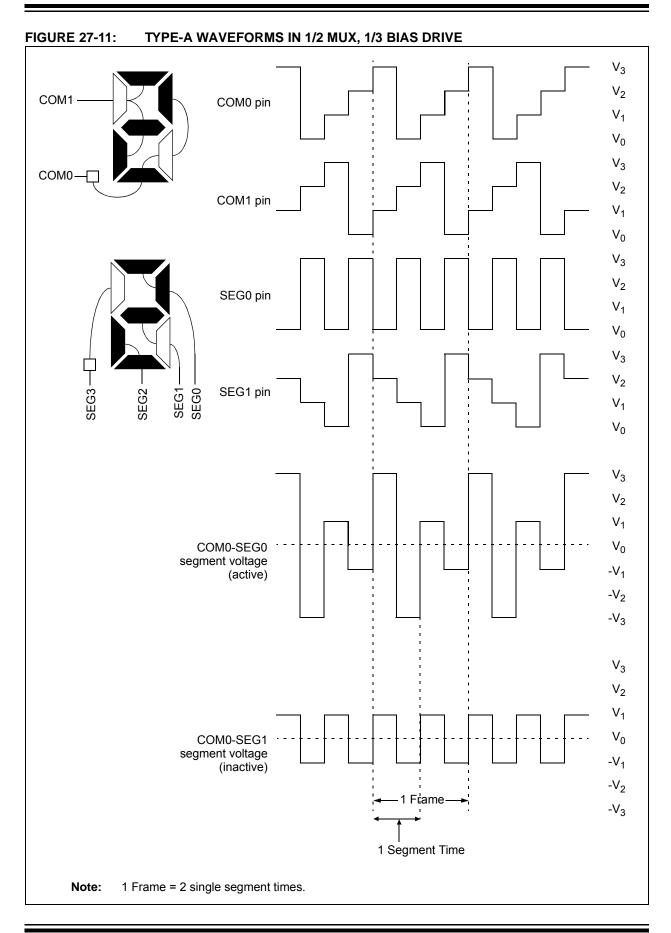

The internal reference ladder can be used to divide the LCD bias voltage two or three equally spaced voltages that will be supplied to the LCD segment pins. To create this, the reference ladder consists of three matched resistors. Refer to Figure 27-3.

#### 27.4.1 BIAS MODE INTERACTION

When in 1/2 Bias mode (BIASMD = 1), then the middle resistor of the ladder is shorted out so that only two voltages are generated. The current consumption of the ladder is higher in this mode, with the one resistor removed.

TABLE 27-3:LCD INTERNAL LADDERPOWER MODES (1/3 BIAS)

| Power<br>Mode |          |        |

|---------------|----------|--------|

| Low           | 3 Mohm   | 1 µA   |

| Medium        | 300 kohm | 10 µA  |

| High 30 kohm  |          | 100 µA |

# 27.4.2 POWER MODES

The internal reference ladder may be operated in one of three power modes. This allows the user to trade off LCD contrast for power in the specific application. The larger the LCD glass, the more capacitance is present on a physical LCD segment, requiring more current to maintain the same contrast level.

Three different power modes are available, LP, MP and HP. The internal reference ladder can also be turned off for applications that wish to provide an external ladder or to minimize power consumption. Disabling the internal reference ladder results in all of the ladders being disconnected, allowing external voltages to be supplied.

Whenever the LCD module is inactive (LCDA = 0), the internal reference ladder will be turned off.

# TABLE 30-8: PIC16(L)F1934/6/7 A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature Tested at 25°C |      |                                                   |      |      |      |       |                                                                     |  |  |

|-------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|--|--|

| Param<br>No.                                                                                    | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                          |  |  |

| AD01                                                                                            | NR   | Resolution                                        |      | _    | 10   | bit   |                                                                     |  |  |

| AD02                                                                                            | EIL  | Integral Error                                    | _    | _    | ±1.7 | LSb   | VREF = 3.0V                                                         |  |  |

| AD03                                                                                            | Edl  | Differential Error                                |      |      | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |  |  |

| AD04                                                                                            | EOFF | Offset Error                                      | _    | _    | ±2.5 | LSb   | VREF = 3.0V                                                         |  |  |

| AD05                                                                                            | Egn  | Gain Error                                        | _    | _    | ±2.0 | LSb   | VREF = 3.0V                                                         |  |  |

| AD06                                                                                            | VREF | Reference Voltage <sup>(3)</sup>                  | 1.8  | _    | Vdd  | V     | VREF = (VREF+ minus VREF-) ( <b>Note 5</b> )                        |  |  |

| AD07                                                                                            | VAIN | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                     |  |  |

| AD08                                                                                            | ZAIN | Recommended Impedance of<br>Analog Voltage Source |      |      | 10   | kΩ    | Can go higher if external 0.01µF capacitor is present on input pin. |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: ADC VREF is from external VREF, VDD pin or FVR, whichever is selected as reference input.

4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

5: FVR voltage selected must be 2.048V or 4.096V.

#### TABLE 30-9: PIC16(L)F1934/6/7 A/D CONVERSION REQUIREMENTS

|              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                                 |            |         |            |          |                                           |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------|---------|------------|----------|-------------------------------------------|--|--|

| Param<br>No. | Sym.                                                                                                                 | Characteristic                                                  | Min.       | Тур†    | Max.       | Units    | Conditions                                |  |  |

| AD130*       | Tad                                                                                                                  | A/D Clock Period<br>A/D Internal RC Oscillator<br>Period        | 1.0<br>1.0 | <br>2.5 | 9.0<br>6.0 | μs<br>μs | Tosc-based<br>ADCS<1:0> = 11 (ADRC mode)  |  |  |

| AD131        | TCNV                                                                                                                 | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | —          | 11      | —          | Tad      | Set GO/DONE bit to conversion<br>complete |  |  |

| AD132*       | TACQ                                                                                                                 | Acquisition Time                                                | —          | 5.0     | —          | μS       |                                           |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.