Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1937-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 28/40/44-Pin Flash-Based, 8-Bit CMOS Microcontrollers with LCD Driver with nanoWatt XLP Technology

#### **Devices Included In This Data Sheet:**

- PIC16F1934

- PIC16LF1934

- PIC16F1936 PIC16LF1936

- PIC16F1937 PIC16LF1937

#### Other PIC16(L)F193X Devices Available:

- PIC16(L)F1933 (DS41575)

- PIC16(L)F1938/9 (DS41574)

### Note: PIC16(L)F193X devices referred to in this data sheet apply to PIC16(L)F1934/6/7.

#### **High-Performance RISC CPU:**

- Only 49 Instructions to Learn:

- All single-cycle instructions except branches

- Operating Speed:

- DC 32 MHz oscillator/clock input

- DC 125 ns instruction cycle

- Up to 16K x 14 Words of Flash Program Memory

- Up to 1024 Bytes of Data Memory (RAM)

- Interrupt Capability with Automatic Context Saving

- 16-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes

- · Processor Read Access to Program Memory

- Pinout Compatible to other 28/40/44-pin PIC16CXXX and PIC16FXXX Microcontrollers

#### **Special Microcontroller Features:**

- Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range from 32 MHz to 31 kHz

- Power-Saving Sleep mode

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Selectable between two trip points

- Disable in Sleep option

- Multiplexed Master Clear with Pull-up/Input Pin

- Programmable Code Protection

- High Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

- Wide Operating Voltage Range:

- 1.8V-5.5V (PIC16F193X)

- 1.8V-3.6V (PIC16LF193X)

#### PIC16LF193X Low-Power Features:

- Standby Current:

- 60 nÅ @ 1.8V, typical

- Operating Current:

- 7.0 μA @ 32 kHz, 1.8V, typical (PIC16LF193X)

- 150 μA @ 1 MHz, 1.8V, typical (PIC16LF193X)

- Timer1 Oscillator Current:

- 600 nA @ 32 kHz, 1.8V, typical

- · Low-Power Watchdog Timer Current:

- 500 nA @ 1.8V, typical (PIC16LF193X)

#### **Peripheral Features:**

- Up to 35 I/O Pins and 1 Input-only Pin:

- High-current source/sink for direct LED drive

- Individually programmable interrupt-on-pin change pins

- Individually programmable weak pull-ups

- Integrated LCD Controller:

- Up to 96 segments

- Variable clock input

- Contrast control

- Internal voltage reference selections

- Capacitive Sensing module (mTouch<sup>™</sup>)

- Up to 16 selectable channels

- · A/D Converter:

- 10-bit resolution and up to 14 channels

- Selectable 1.024/2.048/4.096V voltage reference

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1

- Dedicated low-power 32 kHz oscillator driver

- 16-bit timer/counter with prescaler

- External Gate Input mode with toggle and single shot modes

- Interrupt-on-gate completion

- Timer2, 4, 6: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

- Two Capture, Compare, PWM modules (CCP)

- 16-bit Capture, max. resolution 125 ns

- 16-bit Compare, max. resolution 125 ns

- 10-bit PWM, max. frequency 31.25 kHz

- Three Enhanced Capture, Compare, PWM modules (ECCP)

- 3 PWM time-base options

- Auto-shutdown and auto-restart

- PWM steering

- Programmable dead-band delay

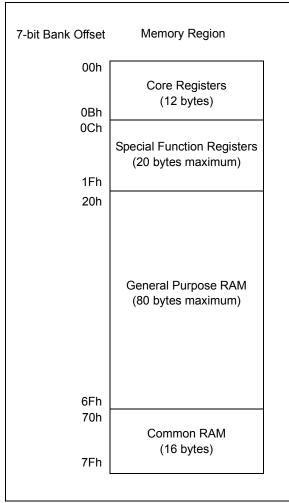

#### 3.2.2 SPECIAL FUNCTION REGISTER

The Special Function Registers (SFR) are registers used by the application to control the desired operation of peripheral functions in the device. The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.2.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

#### 3.2.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.5.2** "**Linear Data Memory**" for more information.

#### 3.2.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

#### 3.2.5 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-2.

#### TABLE 3-2: MEMORY MAP TABLES

| Device      | Banks | Table No.             |

|-------------|-------|-----------------------|

| PIC16F1934  | 0-7   | Table 3-3             |

| PIC16LF1934 | 8-15  | Table 3-4, Table 3-10 |

|             | 16-23 | Table 3-7             |

|             | 23-31 | Table 3-8, Table 3-11 |

| PIC16F1936  | 0-7   | Table 3-5             |

| PIC16LF1936 | 8-15  | Table 3-6, Table 3-9  |

|             | 16-23 | Table 3-7             |

|             | 23-31 | Table 3-8, Table 3-11 |

| PIC16F1937  | 0-7   | Table 3-5             |

| PIC16LF1937 | 8-15  | Table 3-6, Table 3-10 |

|             | 16-23 | Table 3-7             |

|             | 23-31 | Table 3-8, Table 3-11 |

| TABLE                            | 3-1Z. C                                                                                                         | SPECIAL                                     | FUNCTIC                                                  | IN REGIS        | DIER SUN     | INIART (C      |            | בט)   |       |               |      |                     |      |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----------------|--------------|----------------|------------|-------|-------|---------------|------|---------------------|------|

| Address                          | Name                                                                                                            | Bit 7                                       | Bit 6                                                    | Bit 5           | Bit 4        | Bit 3          | Bit 2      | Bit 1 | Bit 0 | Value<br>POR, |      | Value<br>oth<br>Res | ner  |

| Banks 1                          | 6-30                                                                                                            |                                             |                                                          |                 |              |                |            |       |       |               |      |                     |      |

| x00h/<br>x80h <sup>(2)</sup>     | INDF0                                                                                                           | Addressing<br>(not a physi                  |                                                          | ses contents o  | of FSR0H/FSF | R0L to address | data memor | ý     |       | xxxx          | xxxx | xxxx                | xxxx |

| x00h/<br>x81h <sup>(2)</sup>     | INDF1 Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                                             |                                                          |                 |              |                |            | xxxx  | XXXX  | xxxx          | xxxx |                     |      |

| x02h/<br>x82h <sup>(2)</sup>     | PCL                                                                                                             | Program Co                                  | ounter (PC) Le                                           | ast Significant | t Byte       |                |            |       |       | 0000          | 0000 | 0000                | 0000 |

| x03h/<br>x83h <sup>(2)</sup>     | STATUS                                                                                                          | -                                           | —                                                        | _               | TO           | PD             | Z          | DC    | С     | 1             | 1000 | d                   | quuu |

| x04h/<br>x84h <sup>(2)</sup>     | FSR0L                                                                                                           | Indirect Data Memory Address 0 Low Pointer  |                                                          |                 |              |                |            |       | 0000  | 0000          | uuuu | uuuu                |      |

| x05h/<br>x85h <b>(2)</b>         | FSR0H                                                                                                           | Indirect Dat                                | Indirect Data Memory Address 0 High Pointer              |                 |              |                |            |       |       | 0000          | 0000 | 0000                | 0000 |

| x06h/<br>x86h <sup>(2)</sup>     | FSR1L                                                                                                           | Indirect Dat                                | Indirect Data Memory Address 1 Low Pointer               |                 |              |                |            |       |       | 0000          | 0000 | uuuu                | uuuu |

| x07h/<br>x87h <sup>(2)</sup>     | FSR1H                                                                                                           | Indirect Data Memory Address 1 High Pointer |                                                          |                 |              |                |            |       | 0000  | 0000          | 0000 | 0000                |      |

| x08h/<br>x88h <b>(2)</b>         | BSR                                                                                                             | _                                           | —                                                        | —               |              |                | BSR<4:0>   |       |       | 0             | 0000 | 0                   | 0000 |

| x09h/<br>x89h <sup>(2)</sup>     | WREG                                                                                                            | Working Re                                  | gister                                                   |                 |              |                |            |       |       | 0000          | 0000 | uuuu                | uuuu |

| x0Ah/<br>x8Ah <sup>(1),(2)</sup> | PCLATH                                                                                                          | -                                           | Write Buffer for the upper 7 bits of the Program Counter |                 |              |                |            |       | -000  | 0000          | -000 | 0000                |      |

| x0Bh/<br>x8Bh <sup>(2)</sup>     | INTCON                                                                                                          | GIE                                         | PEIE                                                     | TMR0IE          | INTE         | IOCIE          | TMR0IF     | INTF  | IOCIF | 0000          | 0000 | 0000                | 0000 |

| x0Ch/<br>x8Ch                    | —                                                                                                               | Unimpleme                                   | nted                                                     |                 |              |                |            |       |       | -             | -    | _                   | -    |

| x1Fh/<br>x9Fh                    |                                                                                                                 |                                             |                                                          |                 |              |                |            |       |       |               |      |                     |      |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

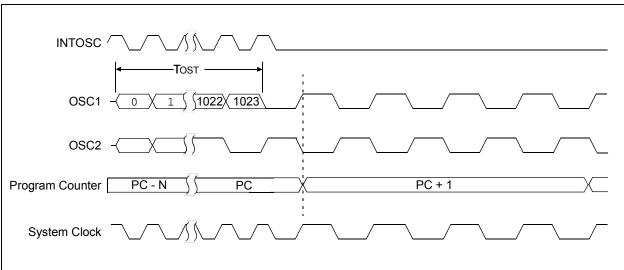

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

#### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

#### FIGURE 5-8: TWO-SPEED START-UP

#### 7.6.7 PIR3 REGISTER

The PIR3 register contains the interrupt flag bits, as shown in Register 7-7.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| _       | CCP5IF  | CCP4IF  | CCP3IF  | TMR6IF  | —       | TMR4IF  | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

| bit 7 | Unimplemented: Read as '0'                   |

|-------|----------------------------------------------|

| bit 6 | CCP5IF: CCP5 Interrupt Flag bit              |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 5 | CCP4IF: CCP4 Interrupt Flag bit              |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 4 | CCP3IF: CCP3 Interrupt Flag bit              |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 3 | TMR6IF: TMR6 to PR6 Match Interrupt Flag bit |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 2 | Unimplemented: Read as '0'                   |

| bit 1 | TMR4IF: TMR4 to PR4 Match Interrupt Flag bit |

|       | 1 = Interrupt is pending                     |

|       | 0 = Interrupt is not pending                 |

| bit 0 | Unimplemented: Read as '0'                   |

|       |                                              |

NOTES:

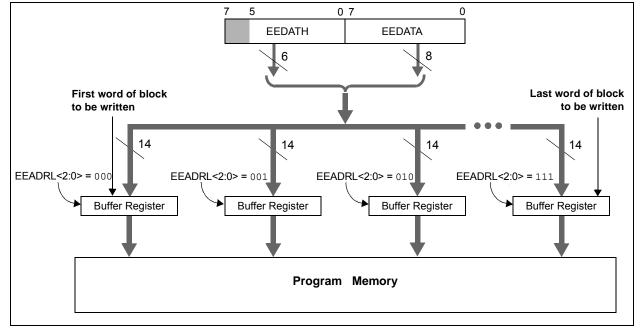

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the write operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the write takes place (i.e., the last word of the block write). This is not Sleep mode as the clocks and peripherals will

continue to run. The processor does not stall when LWLO = 1, loading the write latches. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

| R/W-x/u                               | R/W-x/u                                 | R/W-x/u | R/W-x/u                            | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|---------------------------------------|-----------------------------------------|---------|------------------------------------|-------------------------------------------------------|---------|---------|---------|--|

| RD7                                   | RD6                                     | RD5     | RD4                                | RD3                                                   | RD2     | RD1     | RD0     |  |

| bit 7                                 |                                         |         |                                    | •                                                     |         | •       | bit 0   |  |

|                                       |                                         |         |                                    |                                                       |         |         |         |  |

| Legend:                               |                                         |         |                                    |                                                       |         |         |         |  |

| R = Readable bit W = Writable bit     |                                         |         | U = Unimplemented bit, read as '0' |                                                       |         |         |         |  |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |         |                                    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared |                                         |         |                                    |                                                       |         |         |         |  |

bit 7-0 **RD<7:0>:** PORTD General Purpose I/O Pin bits 1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: PORTD is not implemented on PIC16(L)F1936 devices, read as '0'.

#### REGISTER 12-15: TRISD: PORTD TRI-STATE REGISTER<sup>(1)</sup>

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISD<7:0>: PORTD Tri-State Control bits

- 1 = PORTD pin configured as an input (tri-stated)

- 0 = PORTD pin configured as an output

Note 1: TRISD is not implemented on PIC16(L)F1936 devices, read as '0'.

2: PORTD implemented on PIC16(L)F1934/7 devices only.

#### REGISTER 12-16: LATD: PORTD DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   |

| bit 7   |         |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATD<7:0>: PORTD Output Latch Value bits<sup>(1,2)</sup>

- **Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

- 2: PORTD implemented on PIC16(L)F1934/7 devices only.

NOTES:

#### 14.3 FVR Control Registers

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 R-q/q                                  | R/W-0/0                                                                                                             | R/W-0/0                                            | R/W-0/0                                                     | R/W-0/0                                                     | R/W-0/0                                                  | R/W-0/0      |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|--------------|

| FVREN FVRRDY <sup>(1)</sup>                    | TSEN                                                                                                                | TSRNG                                              | CDAF                                                        | /R<1:0>                                                     | ADFVI                                                    | R<1:0>       |

| bit 7                                          |                                                                                                                     |                                                    | ·                                                           |                                                             |                                                          | bit (        |

|                                                |                                                                                                                     |                                                    |                                                             |                                                             |                                                          |              |

| Legend:                                        |                                                                                                                     |                                                    |                                                             |                                                             |                                                          |              |

| R = Readable bit                               | W = Writable                                                                                                        | bit                                                | U = Unimplen                                                | nented bit, read                                            | as '0'                                                   |              |

| u = Bit is unchanged                           | x = Bit is unkr                                                                                                     | nown                                               | -n/n = Value a                                              | at POR and BOI                                              | R/Value at all c                                         | other Resets |

| 1' = Bit is set                                | '0' = Bit is clea                                                                                                   | ared                                               | q = Value dep                                               | ends on condit                                              | on                                                       |              |

| 0 = Fixed V                                    | ed Voltage Refe<br>oltage Referenc<br>oltage Referenc                                                               | e is disabled                                      | bit                                                         |                                                             |                                                          |              |

| 0 = Fixed V                                    | ixed Voltage Ref<br>oltage Referenc<br>oltage Referenc                                                              | e output is no                                     | t ready or not e                                            | nabled                                                      |                                                          |              |

| 0 = Temper                                     | perature Indicato<br>ature Indicator is<br>ature Indicator is                                                       | s disabled                                         | )                                                           |                                                             |                                                          |              |

| 0 = VOUT =                                     | mperature Indica<br>VDD - 2VT (Low<br>VDD - 4VT (High                                                               | Range)                                             | election bit <sup>(3)</sup>                                 |                                                             |                                                          |              |

| 00 = Compa<br>01 = Compa<br>10 = Compa         | :0>: Comparator<br>arator and DAC F<br>arator and DAC F<br>arator and DAC F<br>arator and DAC F<br>arator and DAC F | Fixed Voltage<br>Fixed Voltage<br>Fixed Voltage    | Reference Per<br>Reference Per<br>Reference Per             | ipheral output is<br>ipheral output is<br>ipheral output is | s off.<br>s 1x (1.024V)<br>s 2x (2.048V) <mark>(2</mark> |              |

| 00 = ADC F<br>01 = ADC F<br>10 = ADC F         | ADC Fixed V<br>ixed Voltage Rei<br>ixed Voltage Rei<br>ixed Voltage Rei<br>ixed Voltage Rei<br>ixed Voltage Rei     | ference Peripl<br>ference Peripl<br>ference Peripl | heral output is o<br>heral output is f<br>heral output is 2 | off.<br>1x (1.024V)<br>2x (2.048V) <b><sup>(2)</sup></b>    |                                                          |              |

| Note 1: FVRRDY is alway<br>2: Fixed Voltage Re | •                                                                                                                   | •                                                  | IC16F1934/6/7                                               | ).                                                          |                                                          |              |

3: See Section 16.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | R<1:0> | ADFV  | R<1:0> | 156                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

| R/W-0/0          | R/W-0/0       | R/W-0/0          | R/W-0/0                             | R/W-0/0                | R/W-0/0                 | R/W-0/0          | R/W-0/0      |

|------------------|---------------|------------------|-------------------------------------|------------------------|-------------------------|------------------|--------------|

| SRSPE            | SRSCKE        | SRSC2E           | SRSC1E                              | SRRPE                  | SRRCKE                  | SRRC2E           | SRRC1E       |

| bit 7            |               |                  |                                     |                        |                         |                  | bit 0        |

|                  |               |                  |                                     |                        |                         |                  |              |

| Legend:          |               |                  |                                     |                        |                         |                  |              |

| R = Readable     | bit           | W = Writable     | bit                                 |                        | nented bit, read        |                  |              |

| u = Bit is unch  | anged         | x = Bit is unki  |                                     | -n/n = Value a         | at POR and BO           | R/Value at all o | other Resets |

| '1' = Bit is set |               | '0' = Bit is cle | ared                                |                        |                         |                  |              |

| 1. 1. 7          |               |                  |                                     |                        |                         |                  |              |

| bit 7            |               | •                | al Set Enable b                     |                        |                         |                  |              |

|                  |               |                  | ne SRI pin is hi<br>n the set input | gn.<br>of the SR Latcł | า                       |                  |              |

| bit 6            | SRSCKE: SF    | R Latch Set Clo  | ock Enable bit                      |                        |                         |                  |              |

|                  |               |                  | s pulsed with S                     |                        |                         |                  |              |

|                  | 0 = SRCLK h   | has no effect o  | n the set input                     | of the SR Latcl        | า                       |                  |              |

| bit 5            |               | R Latch C2 Set   |                                     |                        |                         |                  |              |

|                  |               |                  |                                     | ator output is hi      | gh<br>of the SR Latch   | _                |              |

| bit 4            | •             | R Latch C1 Set   |                                     | in the set input       | of the SK Lato          | 1                |              |

| DIL 4            |               |                  |                                     | ator output is hi      | ab                      |                  |              |

|                  |               |                  |                                     |                        | of the SR Latch         | า                |              |

| bit 3            | •             |                  | al Reset Enabl                      | •                      |                         |                  |              |

|                  |               | •                | the SRI pin is                      |                        |                         |                  |              |

|                  | 0 = SRI pin h | nas no effect or | n the reset inpu                    | ut of the SR Lat       | tch                     |                  |              |

| bit 2            | SRRCKE: SF    | R Latch Reset    | Clock Enable b                      | oit                    |                         |                  |              |

|                  |               |                  | n is pulsed with                    |                        |                         |                  |              |

|                  |               |                  | •                                   | ut of the SR La        | tch                     |                  |              |

| bit 1            |               | R Latch C2 Res   |                                     |                        |                         |                  |              |

|                  |               |                  |                                     | arator output is       | high<br>ut of the SR La | tch              |              |

| bit 0            | •             | R Latch C1 Res   |                                     |                        |                         |                  |              |

| Dit U            |               |                  |                                     | arator output is       | hiah                    |                  |              |

|                  |               |                  |                                     |                        | ut of the SR La         | tch              |              |

|                  |               | -                |                                     |                        |                         |                  |              |

#### REGISTER 19-2: SRCON1: SR LATCH CONTROL 1 REGISTER

| Name   | Bit 7  | Bit 6  | Bit 5     | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|-----------|--------|--------|--------|--------|--------|---------------------|

| ANSELA | —      | _      | ANSA5     | ANSA4  | ANSA3  | ANSA2  | ANSA1  | ANSA0  | 134                 |

| SRCON0 | SRLEN  | S      | RCLK<2:0> | •      | SRQEN  | SRNQEN | SRPS   | SRPR   | 189                 |

| SRCON1 | SRSPE  | SRSCKE | SRSC2E    | SRSC1E | SRRPE  | SRRCKE | SRRC2E | SRRC1E | 190                 |

| TRISA  | TRISA7 | TRISA6 | TRISA5    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 133                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the SR Latch module.

#### 22.5 Timer2/4/6 Control Register

#### REGISTER 22-1: TXCON: TIMER2/TIMER4/TIMER6 CONTROL REGISTER

| U-0            | R/W-0/0                    | R/W-0/0                     | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|----------------------------|-----------------------------|-----------------|----------------|------------------|------------------|--------------|

|                |                            | TOUTP                       | S<3:0>          |                | TMRxON           | TxCKP            | S<1:0>       |

| oit 7          |                            |                             |                 |                |                  |                  | bit (        |

|                |                            |                             |                 |                |                  |                  |              |

| _egend:        |                            |                             |                 |                |                  |                  |              |

| R = Readab     | le bit                     | W = Writable                | bit             | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is un  | changed                    | x = Bit is unkr             | nown            | -n/n = Value   | at POR and BO    | R/Value at all o | other Resets |

| 1' = Bit is se | et                         | '0' = Bit is clea           | ared            |                |                  |                  |              |

| oit 7          | Unimpleme                  | ented: Read as '            | 0'              |                |                  |                  |              |

| oit 6-3        | TOUTPS<3                   | :0>: Timer Outpu            | ut Postscaler S | Select bits    |                  |                  |              |

|                | 0000 = 1:1                 |                             |                 |                |                  |                  |              |

|                | 0001 = 1:2                 | Postscaler                  |                 |                |                  |                  |              |

|                | 0010 = 1:3                 |                             |                 |                |                  |                  |              |

|                | 0011 = 1:4                 |                             |                 |                |                  |                  |              |

|                | 0100 = 1:5                 |                             |                 |                |                  |                  |              |

|                | 0101 = 1:6<br>0110 = 1:7   |                             |                 |                |                  |                  |              |

|                | 0111 = <b>1</b> :8         |                             |                 |                |                  |                  |              |

|                | 1000 = 1:9                 |                             |                 |                |                  |                  |              |

|                | 1001 = 1:10                |                             |                 |                |                  |                  |              |

|                | 1010 <b>= 1:11</b>         | Postscaler                  |                 |                |                  |                  |              |

|                | 1011 <b>= 1:12</b>         |                             |                 |                |                  |                  |              |

|                | 1100 = 1:13                |                             |                 |                |                  |                  |              |

|                | 1101 = 1:14                |                             |                 |                |                  |                  |              |

|                | 1110 = 1:15<br>1111 = 1:16 |                             |                 |                |                  |                  |              |

| oit 2          |                            | imerx On bit                |                 |                |                  |                  |              |

|                | 1 = Timerx                 |                             |                 |                |                  |                  |              |

|                | 0 = Timerx                 |                             |                 |                |                  |                  |              |

| oit 1-0        | TxCKPS<1:                  | : <b>0&gt;:</b> Timer2-type | Clock Presca    | le Select bits |                  |                  |              |

|                | 00 = Presca                | ler is 1                    |                 |                |                  |                  |              |

|                | 01 = Presca                |                             |                 |                |                  |                  |              |

|                | 10 = Presca                |                             |                 |                |                  |                  |              |

|                | 11 = Presca                | ler is 64                   |                 |                |                  |                  |              |

#### 23.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 23-4.

#### EQUATION 23-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

#### TABLE 23-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 23-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

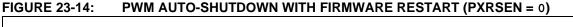

#### 23.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the CCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- A logic '1' on a Comparator (Cx) output

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the CCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 23.4.4 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the CCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

- Note 1: The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.

- Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

- 4: Prior to an auto-shutdown event caused by a comparator output or INT pin event, a software shutdown can be triggered in firmware by setting the CCPxASE bit of the CCPxAS register to '1'. The Auto-Restart feature tracks the active status of a shutdown caused by a comparator output or INT pin event only. If it is enabled at this time, it will immediately clear this bit and restart the ECCP module at the beginning of the next PWM period.

| U-0            | U-0              | U-0              | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0        | R/W-1/1      |

|----------------|------------------|------------------|------------------|-----------------|-------------------|----------------|--------------|

| —              | —                |                  | STRxSYNC         | STRxD           | STRxC             | STRxB          | STRxA        |

| bit 7          | -                |                  |                  |                 |                   |                | bit 0        |

|                |                  |                  |                  |                 |                   |                |              |

| Legend:        |                  |                  |                  |                 |                   |                |              |

| R = Readab     | ole bit          | W = Writable     | bit              | U = Unimpler    | mented bit, read  | l as '0'       |              |

| u = Bit is un  | nchanged         | x = Bit is unk   | nown             | -n/n = Value a  | at POR and BO     | R/Value at all | other Resets |

| '1' = Bit is s | et               | '0' = Bit is cle | eared            |                 |                   |                |              |

|                |                  |                  |                  |                 |                   |                |              |

| bit 7-5        | Unimplemen       | ted: Read as     | '0'              |                 |                   |                |              |

| bit 4          | STRxSYNC:        | Steering Sync    | bit              |                 |                   |                |              |

|                |                  | 0 1              | occurs on next   |                 |                   |                |              |

|                | •                | •                | occurs at the b  | eginning of the | e instruction cyc | le boundary    |              |

| bit 3          |                  | ring Enable bi   |                  |                 |                   |                |              |

|                | •                |                  | waveform with p  | olarity control | from CCPxM<1      | 1:0>           |              |

|                |                  | s assigned to    |                  |                 |                   |                |              |

| bit 2          |                  | ring Enable bi   |                  |                 |                   |                |              |

|                | •                |                  | waveform with p  | olarity control | from CCPxM<1      | 1:0>           |              |

| 1.11.4         | •                | s assigned to    | •                |                 |                   |                |              |

| bit 1          |                  | ring Enable bi   |                  |                 |                   |                |              |

|                | •                |                  | vaveform with p  | olarity control | from CCPXM<1      | 1:0>           |              |

| 1.11.0         |                  | s assigned to p  |                  |                 |                   |                |              |

| bit 0          |                  | ring Enable bi   |                  |                 |                   |                |              |

|                | •                |                  | vaveform with p  | olarity control | Trom CCPXM<1      | :0>            |              |

|                | 0 = PXA pin is   | s assigned to p  | Joit pin         |                 |                   |                |              |

| Note 1: 1      | The PWM Steering | n mode is ava    | ilahle only wher | the CCPxCO      | N register hits ( | CPxM<3.2> =    | = 11 and     |

#### **REGISTER 23-6: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

Note 1: The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

#### 25.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

#### 25.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 25.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is

set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 25.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the 8 Least Significant bits from the RCREG.

### 25.4.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

|                                      |                                                                                                                                                                   |                                                                                                                                                                                                                               | U-0                                | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0/0          | R/W-1/1               | R/W-1/1          |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|------------------|

| R/W-0/0                              | R/W-0/0                                                                                                                                                           | R/C-0/0                                                                                                                                                                                                                       | 0-0                                | 11/00-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10.00 0/0        |                       |                  |

| LCDEN                                | SLPEN                                                                                                                                                             | WERR                                                                                                                                                                                                                          |                                    | CS<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | :1:0>            | LMUX                  | <1:0>            |

| bit 7                                |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       | bit (            |

|                                      |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |

| Legend:                              |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |

| R = Readable                         | e bit                                                                                                                                                             | W = Writable bit                                                                                                                                                                                                              |                                    | U = Unimplen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nented bit, read | l as '0'              |                  |

| u = Bit is unch                      | nanged                                                                                                                                                            | x = Bit is unknow                                                                                                                                                                                                             | vn                                 | -n/n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t POR and BO     | R/Value at all c      | other Resets     |

| '1' = Bit is set                     |                                                                                                                                                                   | '0' = Bit is cleare                                                                                                                                                                                                           | d                                  | C = Only clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rable bit        |                       |                  |

|                                      |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |

| bit 7                                |                                                                                                                                                                   | Driver Enable bit                                                                                                                                                                                                             |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |

|                                      | -                                                                                                                                                                 | er module is enab                                                                                                                                                                                                             |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |

| bit 6                                |                                                                                                                                                                   | er module is disat                                                                                                                                                                                                            |                                    | - hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                       |                  |