#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1937-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-11:PIC16(L)F1934/6/7 MEMORYMAP, BANK 31

|      | Bank 31                                                     |                              |  |  |  |  |  |  |

|------|-------------------------------------------------------------|------------------------------|--|--|--|--|--|--|

|      | F8Ch                                                        |                              |  |  |  |  |  |  |

|      |                                                             | Unimplemented<br>Read as '0' |  |  |  |  |  |  |

|      | FE3h                                                        |                              |  |  |  |  |  |  |

|      | FE4h                                                        | STATUS_SHAD                  |  |  |  |  |  |  |

|      | FE5h                                                        | WREG_SHAD                    |  |  |  |  |  |  |

| FE6h |                                                             | BSR_SHAD                     |  |  |  |  |  |  |

| FE7h |                                                             | PCLATH_SHAD                  |  |  |  |  |  |  |

|      | FE8h                                                        | FSR0L_SHAD                   |  |  |  |  |  |  |

|      | FE9h                                                        | FSR0H_SHAD                   |  |  |  |  |  |  |

|      | FEAh                                                        | FSR1L_SHAD                   |  |  |  |  |  |  |

|      | FEBh                                                        | FSR1H_SHAD                   |  |  |  |  |  |  |

|      | FECh                                                        | —                            |  |  |  |  |  |  |

|      | FEDh                                                        | STKPTR                       |  |  |  |  |  |  |

|      | FEEh                                                        | TOSL                         |  |  |  |  |  |  |

|      | FEFh                                                        | TOSH                         |  |  |  |  |  |  |

| Lege | Legend: = Unimplemented data memory locations, read as '0'. |                              |  |  |  |  |  |  |

# 3.2.6 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device            | Bank(s) | Page No. |

|-------------------|---------|----------|

|                   | 0       | 39       |

|                   | 1       | 40       |

|                   | 2       | 41       |

|                   | 3       | 42       |

|                   | 4       | 43       |

|                   | 5       | 44       |

| PIC16(L)F1934/6/7 | 6       | 45       |

|                   | 7       | 46       |

|                   | 8       | 47       |

|                   | 9-14    | 48       |

|                   | 15      | 49       |

|                   | 16-30   | 51       |

|                   | 31      | 52       |

#### **REGISTER 4-2: CONFIGURATION WORD 2**

| R/P-1/1            | R/P-1/1              | U-1 | R/P-1/1 | R/P-1/1 | R/P-1/1 | U-1   |

|--------------------|----------------------|-----|---------|---------|---------|-------|

| LVP <sup>(1)</sup> | DEBUG <sup>(3)</sup> | _   | BORV    | STVREN  | PLLEN   | —     |

| bit 13             |                      |     |         |         |         | bit 7 |

| U-1   | R/P-1/1                    | R/P-1/1 | U-1 | U-1 | R/P-1/1 | R/P-1/1 |

|-------|----------------------------|---------|-----|-----|---------|---------|

| —     | VCAPEN<1:0> <sup>(2)</sup> |         | —   | —   | WRT1    | WRT0    |

| bit 6 |                            |         |     |     |         | bit 0   |

| Legend:                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                |                                                                                                                                          |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| R = Readable b                                                                                                                                                                                                                                               | t P = Programmable bit                                                                                                                                                                                                                         | U = Unimplemented bit, read as '1'                                                                                                       |  |  |  |  |  |

| '0' = Bit is cleare                                                                                                                                                                                                                                          | ed '1' = Bit is set                                                                                                                                                                                                                            | -n = Value when blank or after Bulk Erase                                                                                                |  |  |  |  |  |

| bit 13                                                                                                                                                                                                                                                       | <b>LVP:</b> Low-Voltage Programming Enable bit<br>1 = Low-voltage programming enabled<br>0 = High-voltage on MCLR/VPP must be use                                                                                                              |                                                                                                                                          |  |  |  |  |  |

| bit 12 <b>DEBUG:</b> In-Circuit Debugger Mode bit <sup>(3)</sup><br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger |                                                                                                                                                                                                                                                |                                                                                                                                          |  |  |  |  |  |

| bit 11                                                                                                                                                                                                                                                       | Unimplemented: Read as '1'                                                                                                                                                                                                                     |                                                                                                                                          |  |  |  |  |  |

| bit 10                                                                                                                                                                                                                                                       | <b>BORV:</b> Brown-out Reset Voltage Selection 1<br>1 = Brown-out Reset voltage set to 1.9V<br>0 = Brown-out Reset voltage set to 2.5V                                                                                                         | bit                                                                                                                                      |  |  |  |  |  |

| bit 9 STVREN: Stack Overflow/Underflow Reset Enable bit<br>1 = Stack Overflow or Underflow will cause a Reset<br>0 = Stack Overflow or Underflow will not cause a Reset                                                                                      |                                                                                                                                                                                                                                                |                                                                                                                                          |  |  |  |  |  |

| bit 8                                                                                                                                                                                                                                                        | <b>PLLEN:</b> PLL Enable bit<br>1 = 4xPLL enabled<br>0 = 4xPLL disabled                                                                                                                                                                        |                                                                                                                                          |  |  |  |  |  |

| bit 7-6                                                                                                                                                                                                                                                      | Unimplemented: Read as '1'                                                                                                                                                                                                                     |                                                                                                                                          |  |  |  |  |  |

| bit 5-4                                                                                                                                                                                                                                                      | VCAPEN<1:0>: Voltage Regulator Capacito<br>00 = VCAP functionality is enabled on RA0<br>01 = VCAP functionality is enabled on RA5<br>10 = VCAP functionality is enabled on RA6<br>11 = No capacitor on VCAP pin                                | or Enable bits <sup>(2)</sup>                                                                                                            |  |  |  |  |  |

| bit 3-2                                                                                                                                                                                                                                                      | Unimplemented: Read as '1'                                                                                                                                                                                                                     |                                                                                                                                          |  |  |  |  |  |

| bit 1-0                                                                                                                                                                                                                                                      | 01 = 000h to 7FFh write-protected, 80<br>00 = 000h to FFFh write-protected, no<br><u>8 kW Flash memory (PIC16(L)F1936 and P</u><br>11 = Write protection off<br>10 = 000h to 1FFh write-protected, 20<br>01 = 000h to FFFh write-protected, 10 | 0h to FFFh may be modified by EECON control<br>0h to FFFh may be modified by EECON control<br>addresses may be modified by EECON control |  |  |  |  |  |

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

- **2:** Reads as '11' on PIC16LF193X only.

- **3:** The DEBUG bit in Configuration Word is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

#### 7.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 7-3.

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 |

|---------|---------|---------|---------|---------|---------|-----|---------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCLIE   | LCDIE   | —   | CCP2IE  |

| bit 7   |         |         |         |         |         |     | bit 0   |

| Legend:        |                         |                                                                                          |                                                       |

|----------------|-------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------|

| R = Readat     | ole bit                 | W = Writable bit                                                                         | U = Unimplemented bit, read as '0'                    |

| u = Bit is ur  | nchanged                | x = Bit is unknown                                                                       | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is s | et                      | '0' = Bit is cleared                                                                     |                                                       |

| bit 7          | OSFIE: Os               | cillator Fail Interrupt Enable                                                           | bit                                                   |

|                |                         | es the Oscillator Fail interrup<br>es the Oscillator Fail interrup                       |                                                       |

| bit 6          | C2IE: Com               | parator C2 Interrupt Enable                                                              | bit                                                   |

|                |                         | es the Comparator C2 interrules the Comparator C2 interrules the Comparator C2 interr    | •                                                     |

| bit 5          | C1IE: Com               | parator C1 Interrupt Enable                                                              | bit                                                   |

|                |                         | es the Comparator C1 interrunt the Comparator C1 interrunt the Comparator C1 interr      | 1                                                     |

| bit 4          | EEIE: EEP               | ROM Write Completion Inter                                                               | rrupt Enable bit                                      |

|                |                         | es the EEPROM Write Comp<br>es the EEPROM Write Com                                      | •                                                     |

| bit 3          | 1 = Enable              | SP Bus Collision Interrupt E<br>the MSSP Bus Collision Ir<br>es the MSSP Bus Collision I | nterrupt                                              |

| bit 2          | LCDIE: LC<br>1 = Enable | D Module Interrupt Enable b<br>the LCD module interrupt<br>the LCD module interrupt      | Dit                                                   |

| bit 1          |                         | ented: Read as '0'                                                                       |                                                       |

| bit 0          | CCP2IE: C               | CP2 Interrupt Enable bit                                                                 |                                                       |

|                |                         | es the CCP2 interrupt<br>es the CCP2 interrupt                                           |                                                       |

# 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

## 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

# 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

- Capacitive Sensing module (CSM)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

# EQUATION 17-1: DAC OUTPUT VOLTAGE

# $\frac{IF DACEN = 1}{Vout}$ $Vout = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE \frac{IF DACEN = 0 \& DACLPS = 1 \& DACR[4:0] = 11111}{Vout}$ Vout = VSOURCE + $\frac{IF DACEN = 0 \& DACLPS = 0 \& DACR[4:0] = 00000}{Vout}$ Vout = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE - = VSS

# 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in the applicable Electrical Specifications chapter.

# 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the following equations:

# 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

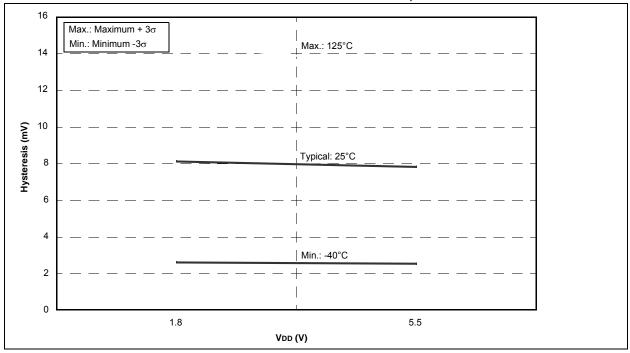

## 18.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See the applicable Electrical Specifications Chapter for more information.

# 18.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 21.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 18.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from either comparator, C1 or C2, can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 18-2) and the Timer1 Block Diagram (Figure 22-1) for more information.

## **18.5** Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

# 18.6 Comparator Positive Input Selection

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- CxIN+ analog pin

- DAC

- FVR (Fixed Voltage Reference)

- · Vss (Ground)

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

| R/W-0/0          | R/W-0/0                                                  | R/W-0/0          | R/W-0/0                             | R/W-0/0                | R/W-0/0                 | R/W-0/0          | R/W-0/0      |  |  |

|------------------|----------------------------------------------------------|------------------|-------------------------------------|------------------------|-------------------------|------------------|--------------|--|--|

| SRSPE            | SRSCKE                                                   | SRSC2E           | SRSC1E                              | SRRPE                  | SRRCKE                  | SRRC2E           | SRRC1E       |  |  |

| bit 7            |                                                          |                  |                                     |                        |                         |                  | bit 0        |  |  |

|                  |                                                          |                  |                                     |                        |                         |                  |              |  |  |

| Legend:          |                                                          |                  |                                     |                        |                         |                  |              |  |  |

| R = Readable     | bit                                                      | W = Writable     | bit                                 |                        | nented bit, read        |                  |              |  |  |

| u = Bit is unch  | anged                                                    | x = Bit is unki  |                                     | -n/n = Value a         | at POR and BO           | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |                                                          | '0' = Bit is cle | ared                                |                        |                         |                  |              |  |  |

| 1. 1. 7          |                                                          |                  |                                     |                        |                         |                  |              |  |  |

| bit 7            |                                                          | •                | al Set Enable b                     |                        |                         |                  |              |  |  |

|                  |                                                          |                  | ne SRI pin is hi<br>n the set input | gn.<br>of the SR Latcł | า                       |                  |              |  |  |

| bit 6            | SRSCKE: SF                                               | R Latch Set Clo  | ock Enable bit                      |                        |                         |                  |              |  |  |

|                  | 1 = Set input of SR Latch is pulsed with SRCLK           |                  |                                     |                        |                         |                  |              |  |  |

|                  | 0 = SRCLK has no effect on the set input of the SR Latch |                  |                                     |                        |                         |                  |              |  |  |

| bit 5            |                                                          | R Latch C2 Set   |                                     |                        |                         |                  |              |  |  |

|                  |                                                          |                  |                                     | ator output is hi      | gh<br>of the SR Latch   | _                |              |  |  |

| bit 4            | •                                                        | R Latch C1 Set   |                                     | in the set input       | of the SK Lato          | 1                |              |  |  |

| DIL 4            |                                                          |                  |                                     | ator output is hi      | ab                      |                  |              |  |  |

|                  |                                                          |                  |                                     |                        | of the SR Latch         | า                |              |  |  |

| bit 3            | •                                                        |                  | al Reset Enabl                      | •                      |                         |                  |              |  |  |

|                  |                                                          | •                | the SRI pin is                      |                        |                         |                  |              |  |  |

|                  | 0 = SRI pin h                                            | nas no effect or | n the reset inpu                    | ut of the SR Lat       | tch                     |                  |              |  |  |

| bit 2            | SRRCKE: SF                                               | R Latch Reset    | Clock Enable b                      | oit                    |                         |                  |              |  |  |

|                  |                                                          |                  | n is pulsed with                    |                        |                         |                  |              |  |  |

|                  |                                                          |                  | •                                   | ut of the SR La        | tch                     |                  |              |  |  |

| bit 1            |                                                          | R Latch C2 Res   |                                     |                        |                         |                  |              |  |  |

|                  |                                                          |                  |                                     | arator output is       | high<br>ut of the SR La | tch              |              |  |  |

| bit 0            | •                                                        | R Latch C1 Res   |                                     |                        |                         |                  |              |  |  |

| Dit U            |                                                          |                  |                                     | arator output is       | hiah                    |                  |              |  |  |

|                  |                                                          |                  |                                     |                        | ut of the SR La         | tch              |              |  |  |

|                  |                                                          | -                |                                     |                        |                         |                  |              |  |  |

### REGISTER 19-2: SRCON1: SR LATCH CONTROL 1 REGISTER

| Name   | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|------------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA | —      | _          | ANSA5  | ANSA4  | ANSA3  | ANSA2  | ANSA1  | ANSA0  | 134                 |

| SRCON0 | SRLEN  | SRCLK<2:0> |        |        | SRQEN  | SRNQEN | SRPS   | SRPR   | 189                 |

| SRCON1 | SRSPE  | SRSCKE     | SRSC2E | SRSC1E | SRRPE  | SRRCKE | SRRC2E | SRRC1E | 190                 |

| TRISA  | TRISA7 | TRISA6     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 133                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the SR Latch module.

| Name    | Bit 7        | Bit 6           | Bit 5          | Bit 4          | Bit 3          | Bit 2    | Bit 1      | Bit 0  | Register<br>on Page |

|---------|--------------|-----------------|----------------|----------------|----------------|----------|------------|--------|---------------------|

| ANSELB  | —            | —               | ANSB5          | ANSB4          | ANSB3          | ANSB2    | ANSB1      | ANSB0  | 139                 |

| CCP1CON | P1M          | <1:0>           | DC1B           | <1:0>          |                | CCP1N    | 1<3:0>     |        | 234                 |

| CCP2CON | P2M          | <1:0>           | DC2B           | <1:0>          |                | CCP2N    | 1<3:0>     |        | 234                 |

| INTCON  | GIE          | PEIE            | TMR0IE         | INTE           | IOCIE          | TMR0IF   | INTF       | IOCIF  | 98                  |

| PIE1    | TMR1GIE      | ADIE            | RCIE           | TXIE           | SSPIE          | CCP1IE   | TMR2IE     | TMR1IE | 99                  |

| PIR1    | TMR1GIF      | ADIF            | RCIF           | TXIF           | SSPIF          | CCP1IF   | TMR2IF     | TMR1IF | 102                 |

| TMR1H   | Holding Regi | ster for the M  | ost Significan | t Byte of the  | 16-bit TMR1 F  | Register |            |        | 199*                |

| TMR1L   | Holding Regi | ster for the Le | east Significa | nt Byte of the | 16-bit TMR1    | Register |            |        | 199*                |

| TRISB   | TRISB7       | TRISB6          | TRISB5         | TRISB4         | TRISB3         | TRISB2   | TRISB1     | TRISB0 | 138                 |

| TRISC   | TRISC7       | TRISC6          | TRISC5         | TRISC4         | TRISC3         | TRISC2   | TRISC1     | TRISC0 | 142                 |

| T1CON   | TMR1C        | S<1:0>          | T1CKPS<1:0>    |                | T1OSCEN        | T1SYNC   | _          | TMR10N | 203                 |

| T1GCON  | TMR1GE       | T1GPOL          | T1GTM          | T1GSPM         | T1GGO/<br>DONE | T1GVAL   | T1GSS<1:0> |        | 204                 |

| TABLE 21-5: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

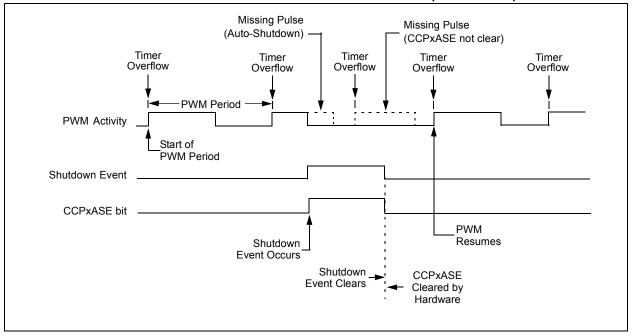

#### 23.4.4 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the PWMxCON register.

If auto-restart is enabled, the CCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCPxASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 23-15: PWM AUTO-SHUTDOWN WITH AUTO-RESTART (PXRSEN = 1)

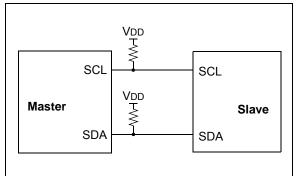

# 24.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit Bus  $(I^2C)$  is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCL)

- Serial Data (SDA)

Figure 24-11 shows the block diagram of the MSSP module when operating in  $I^2C$  Mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 24-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 24-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

# PIC16(L)F1934/6/7

| R/W-0/0          | R-0/0                                                                               | R/W-0/0                                                   | R/S/HS-0/0                                          | R/S/HS-0/0                 | R/S/HS-0/0                                   | R/S/HS-0/0       | R/W/HS-0/0    |

|------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------|----------------------------|----------------------------------------------|------------------|---------------|

| GCEN             | ACKSTAT                                                                             | ACKDT                                                     | ACKEN                                               | RCEN                       | PEN                                          | RSEN             | SEN           |

| bit 7            |                                                                                     |                                                           |                                                     |                            |                                              |                  | bit 0         |

|                  |                                                                                     |                                                           |                                                     |                            |                                              |                  |               |

| Legend:          |                                                                                     |                                                           |                                                     |                            |                                              |                  |               |

| R = Readable     | e bit                                                                               | W = Writable                                              | bit                                                 | U = Unimpler               | nented bit, read                             | l as '0'         |               |

| u = Bit is unc   | hanged                                                                              | x = Bit is unk                                            | nown                                                |                            | at POR and BO                                |                  | other Resets  |

| '1' = Bit is set | t                                                                                   | '0' = Bit is cle                                          | ared                                                | HC = Cleared               | by hardware                                  | S = User set     |               |

| bit 7            | 1 = Enable in                                                                       |                                                           | •                                                   | • •                        | or 00h) is receiv                            | ed in the SSPS   | SR            |

| bit 6            | 1 = Acknowle                                                                        | cknowledge Si<br>edge was not r<br>edge was recei         |                                                     | mode only)                 |                                              |                  |               |

| bit 5            | <u>In Receive m</u>                                                                 | ode:<br>itted when the<br>owledge                         | i bit (in I <sup>2</sup> C mod<br>user initiates a  | • •                        | e sequence at t                              | the end of a rea | ceive         |

| bit 4            | In Master Re<br>1 = Initiate /<br>Automati                                          | ceive mode:                                               | sequence on<br>by hardware.                         | ·                          | ter mode only)<br>CL pins, and               | transmit ACk     | (DT data bit. |

| bit 3            | 1 = Enables I                                                                       | Receive mode                                              | (in I <sup>2</sup> C Master<br>for I <sup>2</sup> C | mode only)                 |                                              |                  |               |

| bit 2            | SCKMSSP R                                                                           | ondition Enable<br>elease Contro                          |                                                     |                            | /)<br>atically cleared                       | by hardware.     |               |

| bit 1            | RSEN: Repe<br>1 = Initiate R                                                        | ated Start Con                                            | condition on S                                      | -                          | ster mode only)<br>ins. Automatica           | lly cleared by h | nardware.     |

| bit 0            | In Master mo<br>1 = Initiate St<br>0 = Start cond<br>In Slave mod<br>1 = Clock stre | <u>de:</u><br>art condition o<br>dition Idle<br><u>e:</u> | bled for both sla                                   | L pins. Automa             | nly)<br>atically cleared<br>nd slave receive | -                | ed)           |

| Note 1: Fo       | or bits ACKEN, F                                                                    | RCEN. PEN. R                                              | SEN. SEN: If t                                      | he I <sup>2</sup> C module | is not in the Idl                            | e mode. this bi  | t mav not be  |

#### REGISTER 24-3: SSPCON2: SSP CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| DATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | —                             | _          | —                           | _                |            | _                           |                   | _          | _                           | 300              | 0.16       | 207                         |  |

| 1200   | —                             | —          | —                           | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | —                | _          | _                           |  |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |

| 19.2k  | 19231                         | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00       | 11                          | —                | _          | _                           |  |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |  |

| 115.2k | —                             | _          | —                           | —                | _          | —                           | 115.2k            | 0.00       | 1                           | —                | _          | —                           |  |

# TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|         | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|---------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD    | Fosc = 32.000 MHz             |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

| RATE Ac | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300     | 300.0                         | 0.00       | 6666                        | 300.0             | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.0              | 0.00       | 2303                        |  |

| 1200    | 1200                          | -0.02      | 3332                        | 1200              | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200               | 0.00       | 575                         |  |

| 2400    | 2401                          | -0.04      | 832                         | 2399              | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2400               | 0.00       | 287                         |  |

| 9600    | 9615                          | 0.16       | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |  |

| 10417   | 10417                         | 0.00       | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |  |

| 19.2k   | 19.23k                        | 0.16       | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |  |

| 57.6k   | 57.14k                        | -0.79      | 34                          | 56.818            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |  |

| 115.2k  | 117.6k                        | 2.12       | 16                          | 113.636           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |  |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| DATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5            | 0.16       | 207                         |  |

| 1200   | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | —                | _          | _                           |  |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          | —                | _          | _                           |  |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |  |

| 115.2k | —                             | _          | _                           | _                | _          | _                           | 115.2k            | 0.00       | 1                           | _                | _          | —                           |  |

# 25.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 25.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 25.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 25.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 25.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

# PIC16(L)F1934/6/7

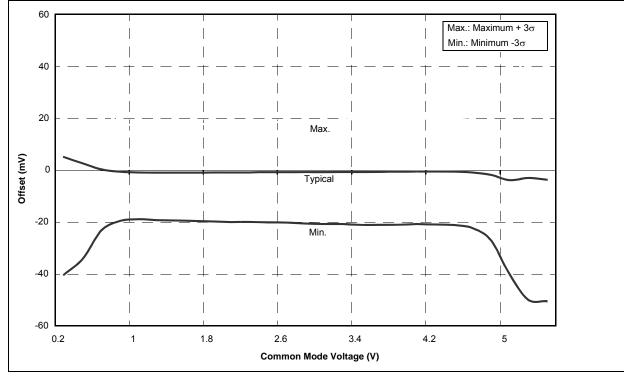

FIGURE 31-7: PIC16F1934/6/7 COMPARATOR HYSTERESIS, LOW-POWER MODE

## 32.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 32.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 32.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 32.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 32.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

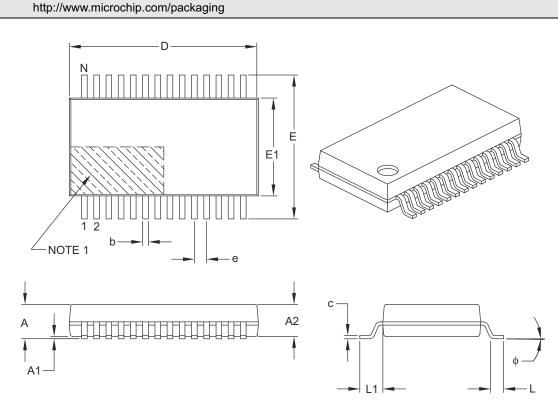

For the most current package drawings, please see the Microchip Packaging Specification located at

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | Units            | MILLIMETERS |          |       |  |  |

|--------------------------|------------------|-------------|----------|-------|--|--|

|                          | Dimension Limits | MIN         | NOM      | MAX   |  |  |

| Number of Pins           | N                |             | 28       |       |  |  |

| Pitch                    | е                |             | 0.65 BSC |       |  |  |

| Overall Height           | А                | -           | -        | 2.00  |  |  |

| Molded Package Thickness | A2               | 1.65        | 1.75     | 1.85  |  |  |

| Standoff                 | A1               | 0.05        | -        | -     |  |  |

| Overall Width            | E                | 7.40        | 7.80     | 8.20  |  |  |

| Molded Package Width     | E1               | 5.00        | 5.30     | 5.60  |  |  |

| Overall Length           | D                | 9.90        | 10.20    | 10.50 |  |  |

| Foot Length              | L                | 0.55        | 0.75     | 0.95  |  |  |

| Footprint                | L1               |             | 1.25 REF |       |  |  |

| Lead Thickness           | С                | 0.09        | -        | 0.25  |  |  |

| Foot Angle               | ф                | 0°          | 4°       | 8°    |  |  |

| Lead Width               | b                | 0.22        | -        | 0.38  |  |  |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

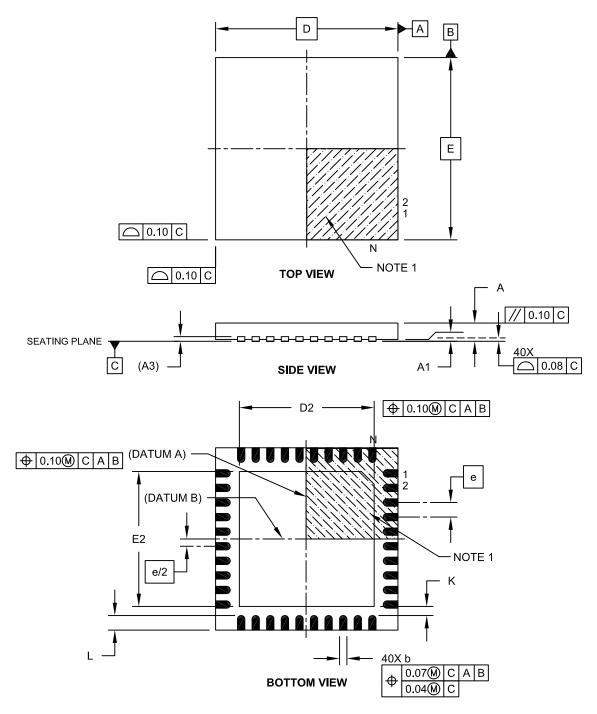

## 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2

# PIC16(L)F1934/6/7

NOTES:

# PIC16(L)F1934/6/7

NOTES: