Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| 2 0 0 0 0 0 0              |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 14x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1937t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-3: PIC16(L)F1934 MEMORY MAP, BANKS 0-7

|      | BANK 0                         | •    | BANK 1                                     |      | BANK 2                                     |      | BANK 3                       |      | BANK 4                       |      | BANK 5                       |      | BANK 6                       |      | BANK 7                       |

|------|--------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|

| 000h | INDF0                          | 080h | INDF0                                      | 100h | INDF0                                      | 180h | INDF0                        | 200h | INDF0                        | 280h | INDF0                        | 300h | INDF0                        | 380h | INDF0                        |

| 001h | INDF1                          | 081h | INDF1                                      | 101h | INDF1                                      | 181h | INDF1                        | 201h | INDF1                        | 281h | INDF1                        | 301h | INDF1                        | 381h | INDF1                        |

| 002h | PCL                            | 082h | PCL                                        | 102h | PCL                                        | 182h | PCL                          | 202h | PCL                          | 282h | PCL                          | 302h | PCL                          | 382h | PCL                          |

| 003h | STATUS                         | 083h | STATUS                                     | 103h | STATUS                                     | 183h | STATUS                       | 203h | STATUS                       | 283h | STATUS                       | 303h | STATUS                       | 383h | STATUS                       |

| 004h | FSR0L                          | 084h | FSR0L                                      | 104h | FSR0L                                      | 184h | FSR0L                        | 204h | FSR0L                        | 284h | FSR0L                        | 304h | FSR0L                        | 384h | FSR0L                        |

| 005h | FSR0H                          | 085h | FSR0H                                      | 105h | FSR0H                                      | 185h | FSR0H                        | 205h | FSR0H                        | 285h | FSR0H                        | 305h | FSR0H                        | 385h | FSR0H                        |

| 006h | FSR1L                          | 086h | FSR1L                                      | 106h | FSR1L                                      | 186h | FSR1L                        | 206h | FSR1L                        | 286h | FSR1L                        | 306h | FSR1L                        | 386h | FSR1L                        |

| 007h | FSR1H                          | 087h | FSR1H                                      | 107h | FSR1H                                      | 187h | FSR1H                        | 207h | FSR1H                        | 287h | FSR1H                        | 307h | FSR1H                        | 387h | FSR1H                        |

| 008h | BSR                            | 088h | BSR                                        | 108h | BSR                                        | 188h | BSR                          | 208h | BSR                          | 288h | BSR                          | 308h | BSR                          | 388h | BSR                          |

| 009h | WREG                           | 089h | WREG                                       | 109h | WREG                                       | 189h | WREG                         | 209h | WREG                         | 289h | WREG                         | 309h | WREG                         | 389h | WREG                         |

| 00Ah | PCLATH                         | 08Ah | PCLATH                                     | 10Ah | PCLATH                                     | 18Ah | PCLATH                       | 20Ah | PCLATH                       | 28Ah | PCLATH                       | 30Ah | PCLATH                       | 38Ah | PCLATH                       |

| 00Bh | INTCON                         | 08Bh | INTCON                                     | 10Bh | INTCON                                     | 18Bh | INTCON                       | 20Bh | INTCON                       | 28Bh | INTCON                       | 30Bh | INTCON                       | 38Bh | INTCON                       |

| 00Ch | PORTA                          | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                       | 20Ch | —                            | 28Ch | —                            | 30Ch | —                            | 38Ch | _                            |

| 00Dh | PORTB                          | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                       | 20Dh | WPUB                         | 28Dh | —                            | 30Dh | —                            | 38Dh | —                            |

| 00Eh | PORTC                          | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | _                            | 20Eh |                              | 28Eh | —                            | 30Eh | —                            | 38Eh | _                            |

| 00Fh | PORTD <sup>(1)</sup>           | 08Fh | TRISD <sup>(1)</sup>                       | 10Fh | LATD <sup>(1)</sup>                        | 18Fh | ANSELD <sup>(1)</sup>        | 20Fh | _                            | 28Fh | —                            | 30Fh | —                            | 38Fh | _                            |

| 010h | PORTE                          | 090h | TRISE                                      | 110h | LATE <sup>(1)</sup>                        | 190h | ANSELE <sup>(1)</sup>        | 210h | WPUE                         | 290h | —                            | 310h | —                            | 390h |                              |

| 011h | PIR1                           | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | EEADRL                       | 211h | SSPBUF                       | 291h | CCPR1L                       | 311h | CCPR3L                       | 391h | _                            |

| 012h | PIR2                           | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | EEADRH                       | 212h | SSPADD                       | 292h | CCPR1H                       | 312h | CCPR3H                       | 392h | _                            |

| 013h | PIR3                           | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | EEDATL                       | 213h | SSPMSK                       | 293h | CCP1CON                      | 313h | CCP3CON                      | 393h | —                            |

| 014h | —                              | 094h | _                                          | 114h | CM2CON1                                    | 194h | EEDATH                       | 214h | SSPSTAT                      | 294h | PWM1CON                      | 314h | PWM3CON                      | 394h | IOCBP                        |

| 015h | TMR0                           | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | EECON1                       | 215h | SSPCON1                      | 295h | CCP1AS                       | 315h | CCP3AS                       | 395h | IOCBN                        |

| 016h | TMR1L                          | 096h | PCON                                       | 116h | BORCON                                     | 196h | EECON2                       | 216h | SSPCON2                      | 296h | PSTR1CON                     | 316h | PSTR3CON                     | 396h | IOCBF                        |

| 017h | TMR1H                          | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | _                            | 217h | SSPCON3                      | 297h | —                            | 317h | —                            | 397h | _                            |

| 018h | T1CON                          | 098h | OSCTUNE                                    | 118h | DACCON0                                    | 198h | —                            | 218h | _                            | 298h | CCPR2L                       | 318h | CCPR4L                       | 398h | _                            |

| 019h | T1GCON                         | 099h | OSCCON                                     | 119h | DACCON1                                    | 199h | RCREG                        | 219h | —                            | 299h | CCPR2H                       | 319h | CCPR4H                       | 399h | _                            |

| 01Ah | TMR2                           | 09Ah | OSCSTAT                                    | 11Ah | SRCON0                                     | 19Ah | TXREG                        | 21Ah | _                            | 29Ah | CCP2CON                      | 31Ah | CCP4CON                      | 39Ah |                              |

| 01Bh | PR2                            | 09Bh | ADRESL                                     | 11Bh | SRCON1                                     | 19Bh | SPBRGL                       | 21Bh | —                            | 29Bh | PWM2CON                      | 31Bh | —                            | 39Bh | _                            |

| 01Ch | T2CON                          | 09Ch | ADRESH                                     | 11Ch | —                                          | 19Ch | SPBRGH                       | 21Ch | —                            | 29Ch | CCP2AS                       | 31Ch | CCPR5L                       | 39Ch | —                            |

| 01Dh | —                              | 09Dh | ADCON0                                     | 11Dh | APFCON                                     | 19Dh | RCSTA                        | 21Dh |                              | 29Dh | PSTR2CON                     | 31Dh | CCPR5H                       | 39Dh | —                            |

| 01Eh | CPSCON0                        | 09Eh | ADCON1                                     | 11Eh | _                                          | 19Eh | TXSTA                        | 21Eh |                              | 29Eh | CCPTMRS0                     | 31Eh | CCP5CON                      | 39Eh | —                            |

| 01Fh | CPSCON1                        | 09Fh | —                                          | 11Fh | _                                          | 19Fh | BAUDCTR                      | 21Fh | —                            | 29Fh | CCPTMRS1                     | 31Fh | —                            | 39Fh |                              |

| 020h |                                | 0A0h |                                            | 120h |                                            | 1A0h |                              | 220h |                              | 2A0h |                              | 320h |                              | 3A0h |                              |

| 06Fh | General<br>Purpose<br>Register | 0EFh | General<br>Purpose<br>Register<br>80 Bytes | 16Fh | General<br>Purpose<br>Register<br>80 Bytes | 1EFh | Unimplemented<br>Read as '0' | 26Fh | Unimplemented<br>Read as '0' | 2EFh | Unimplemented<br>Read as '0' | 36Fh | Unimplemented<br>Read as '0' | 3EFh | Unimplemented<br>Read as '0' |

| 070h | 96 Bytes                       | 0F0h |                                            | 170h |                                            | 1F0h |                              | 270h |                              | 2F0h |                              | 370h |                              | 3F0h |                              |

|      |                                |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |

| 07Fh |                                | 0FFh |                                            | 17Fh |                                            | 1FFh |                              | 27Fh |                              | 2FFh |                              | 37Fh |                              | 3FFh |                              |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Not available on PIC16(L)F1936.

| Address                | Name   | Bit 7                      | Bit 6                                     | Bit 5                     | Bit 4           | Bit 3          | Bit 2       | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|----------------------------|-------------------------------------------|---------------------------|-----------------|----------------|-------------|-------|---------|----------------------|---------------------------------|

| Bank 8                 |        |                            |                                           |                           |                 |                |             |       |         |                      |                                 |

| 400h <sup>(2)</sup>    | INDF0  | Addressing<br>(not a physi |                                           | ses contents o            | of FSR0H/FSF    | ROL to address | data memory | /     |         | XXXX XXXX            | XXXX XXXX                       |

| 401h <sup>(2)</sup>    | INDF1  | Addressing<br>(not a physi |                                           | ses contents o            | of FSR1H/FSF    | R1L to address | data memory | /     |         | XXXX XXXX            | XXXX XXXX                       |

| 402h <sup>(2)</sup>    | PCL    | Program Co                 | ounter (PC) Le                            | ast Significant           | t Byte          |                |             |       |         | 0000 0000            | 0000 0000                       |

| 403h <sup>(2)</sup>    | STATUS | _                          | _                                         | —                         | TO              | PD             | Z           | DC    | С       | 1 1000               | q quuu                          |

| 404h <sup>(2)</sup>    | FSR0L  | Indirect Data              | ndirect Data Memory Address 0 Low Pointer |                           |                 |                |             |       |         | 0000 0000            | uuuu uuuu                       |

| 405h <sup>(2)</sup>    | FSR0H  | Indirect Data              | a Memory Add                              | lress 0 High P            | ointer          |                |             |       |         | 0000 0000            | 0000 0000                       |

| 406h <sup>(2)</sup>    | FSR1L  | Indirect Data              | a Memory Add                              | ory Address 1 Low Pointer |                 |                |             |       |         |                      | uuuu uuuu                       |

| 407h <sup>(2)</sup>    | FSR1H  | Indirect Date              | a Memory Add                              | Iress 1 High P            | ointer          |                |             |       |         | 0000 0000            | 0000 0000                       |

| 408h <sup>(2)</sup>    | BSR    | _                          | —                                         | —                         |                 | E              | BSR<4:0>    |       |         | 0 0000               | 0 0000                          |

| 409h <sup>(2)</sup>    | WREG   | Working Re                 | gister                                    |                           |                 |                |             |       |         | 0000 0000            | uuuu uuuu                       |

| 40Ah <sup>(1, 2)</sup> | PCLATH | _                          | Write Buffer f                            | or the upper 7            | bits of the Pre | ogram Counter  | r           |       |         | -000 0000            | -000 0000                       |

| 40Bh <sup>(2)</sup>    | INTCON | GIE                        | PEIE                                      | TMR0IE                    | INTE            | IOCIE          | TMR0IF      | INTF  | IOCIF   | 0000 0000            | 0000 0000                       |

| 40Ch                   |        | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 40Dh                   | _      | Unimpleme                  | Jnimplemented                             |                           |                 |                |             |       |         | _                    | _                               |

| 40Eh                   | _      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 40Fh                   | _      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 410h                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 411h                   | _      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 412h                   | _      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 413h                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 414h                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 415h                   | TMR4   | Timer4 Mod                 | ule Register                              |                           |                 |                |             |       |         | 0000 0000            | 0000 0000                       |

| 416h                   | PR4    | Timer4 Peri                | od Register                               |                           |                 |                |             |       |         | 1111 1111            | 1111 1111                       |

| 417h                   | T4CON  | _                          |                                           | T4OUT                     | PS<3:0>         |                | TMR40N      | T4CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 418h                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | —                               |

| 419h                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

| 41Ah                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | —                               |

| 41Bh                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | —                               |

| 41Ch                   | TMR6   | Timer6 Mod                 | ule Register                              |                           |                 |                |             |       |         | 0000 0000            | 0000 0000                       |

| 41Dh                   | PR6    | Timer6 Peri                | od Register                               |                           |                 |                |             |       |         | 1111 1111            | 1111 1111                       |

| 41Eh                   | T6CON  | _                          |                                           | T6OUT                     | PS<3:0>         |                | TMR6ON      | T6CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 41Fh                   | —      | Unimpleme                  | nted                                      |                           |                 |                |             |       |         | _                    | _                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

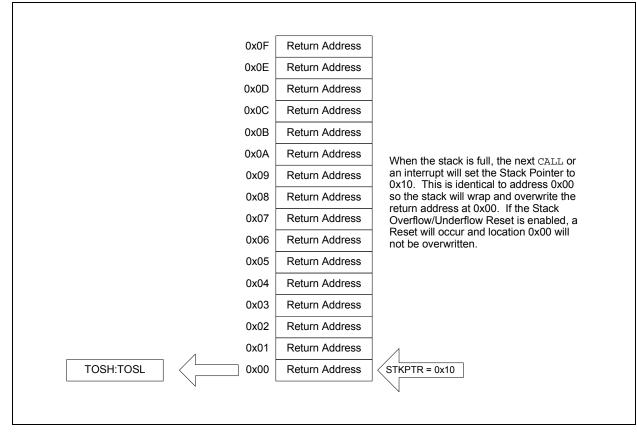

FIGURE 3-8: ACCESSING THE STACK EXAMPLE 4

## 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Word 2 is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

## 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

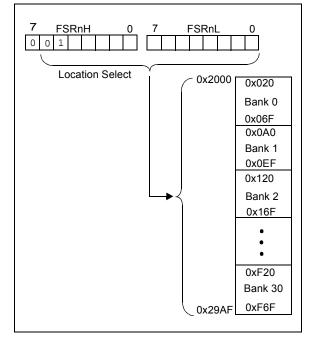

## 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

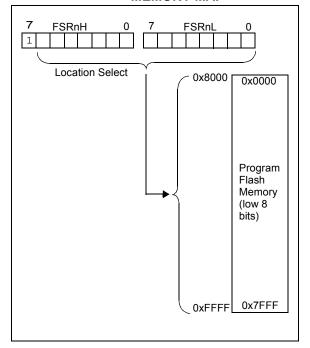

## 3.5.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower 8 bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

## **REGISTER 4-1: CONFIGURATION WORD 1 (CONTINUED)**

- bit 2-0

- FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode: CLKIN on RA7/OSC1/CLKIN

- 110 = ECM: External Clock, Medium-Power mode: CLKIN on RA7/OSC1/CLKIN

- 101 = ECL: External Clock, Low-Power mode: CLKIN on RA7/OSC1/CLKIN

- 100 = INTOSC oscillator: I/O function on RA7/OSC1/CLKIN

- 011 = EXTRC oscillator: RC function on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT pin and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT pin and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT pin and RA7/OSC1/CLKIN

- Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire data EEPROM will be erased when the code protection is turned off during an erase.

- 3: The entire program memory will be erased when the code protection is turned off.

## 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4X PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Word 1 must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Word 1 (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4xPLL, or the PLLEN bit of the Configuration Word 2 must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Word 2, the 4xPLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

## 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables in the applicable Electrical Specifications Chapter.

## 7.6.6 PIR2 REGISTER

The PIR2 register contains the interrupt flag bits, as shown in Register 7-6.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 |

|---------|---------|---------|---------|---------|---------|-----|---------|

| OSFIF   | C2IF    | C1IF    | EEIF    | BCLIF   | LCDIF   |     | CCP2IF  |

| bit 7   |         |         |         |         |         |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | <b>OSFIF:</b> Oscillator Fail Interrupt Flag<br>1 = Interrupt is pending<br>0 = Interrupt is not pending |

|-------|----------------------------------------------------------------------------------------------------------|

| bit 6 | <b>C2IF:</b> Comparator C2 Interrupt Flag<br>1 = Interrupt is pending                                    |

|       | 0 = Interrupt is not pending                                                                             |

| bit 5 | C1IF: Comparator C1 Interrupt Flag                                                                       |

|       | 1 = Interrupt is pending                                                                                 |

|       | 0 = Interrupt is not pending                                                                             |

| bit 4 | EEIF: EEPROM Write Completion Interrupt Flag bit                                                         |

|       | 1 = Interrupt is pending                                                                                 |

|       | 0 = Interrupt is not pending                                                                             |

| bit 3 | BCLIF: MSSP Bus Collision Interrupt Flag bit                                                             |

|       | 1 = Interrupt is pending                                                                                 |

|       | 0 = Interrupt is not pending                                                                             |

| bit 2 | LCDIF: LCD Module Interrupt Flag bit                                                                     |

|       | 1 = Interrupt is pending                                                                                 |

|       | 0 = Interrupt is not pending                                                                             |

| bit 1 | Unimplemented: Read as '0'                                                                               |

| bit 0 | CCP2IF: CCP2 Interrupt Flag bit                                                                          |

|       | 1 = Interrupt is pending                                                                                 |

|       | 0 = Interrupt is not pending                                                                             |

|       |                                                                                                          |

| W-0/0            | W-0/0    | W-0/0             | W-0/0     | W-0/0             | W-0/0            | W-0/0            | W-0/0       |

|------------------|----------|-------------------|-----------|-------------------|------------------|------------------|-------------|

|                  |          |                   | EEPROM Co | ontrol Register 2 |                  |                  |             |

| bit 7            |          |                   |           | -                 |                  |                  | bit 0       |

|                  |          |                   |           |                   |                  |                  |             |

| Legend:          |          |                   |           |                   |                  |                  |             |

| R = Readable     | bit      | W = Writable      | bit       | U = Unimplen      | nented bit, read | as '0'           |             |

| S = Bit can onl  | y be set | x = Bit is unkr   | nown      | -n/n = Value a    | t POR and BO     | R/Value at all c | ther Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared      |                   |                  |                  |             |

### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to **Section 11.2.2** "Writing to the Data EEPROM Memory" for more information.

## TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7            | Bit 6 | Bit 5     | Bit 4          | Bit 3          | Bit 2           | Bit 1 | Bit 0  | Register on<br>Page |

|--------|------------------|-------|-----------|----------------|----------------|-----------------|-------|--------|---------------------|

| EECON1 | EEPGD            | CFGS  | LWLO      | FREE           | WRERR          | WREN            | WR    | RD     | 127                 |

| EECON2 |                  |       | EEPROM Co | ontrol Registe | r 2 (not a phy | sical register) |       |        | 115*                |

| EEADRL | EEADRL<7:0>      |       |           |                |                |                 |       |        |                     |

| EEADRH | _                |       |           |                | EEADRH<6:0     | )               |       |        | 126                 |

| EEDATL | —     EEADRH<6:0 |       |           |                |                |                 |       |        | 126                 |

| EEDATH | _                | _     |           |                | EEDAT          | H<5:0>          |       |        | 126                 |

| INTCON | GIE              | PEIE  | TMR0IE    | INTE           | IOCIE          | TMR0IF          | INTF  | IOCIF  | 98                  |

| PIE2   | OSFIE            | C2IE  | C1IE      | EEIE           | BCLIE          | LCDIE           | _     | CCP2IE | 100                 |

| PIR2   | OSFIF            | C2IF  | C1IF      | EEIF           | BCLIF          | LCDIF           | —     | CCP2IF | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the data EEPROM module.

\* Page provides register information.

## 12.4 PORTC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 12-12). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 12-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 12-12) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

## 12.4.1 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 12-7.

| Pin Name | Function Priority <sup>(1)</sup>                                          |

|----------|---------------------------------------------------------------------------|

| RC0      | T1OSO (Timer1 Oscillator)<br>CCP2/P2B<br>RC0                              |

| RC1      | T1OSI (Timer1 Oscillator)<br>CCP2/P2A<br>RC1                              |

| RC2      | SEG3 (LCD)<br>CCP1/P1A<br>RC2                                             |

| RC3      | SEG6 (LCD)<br>SCL (MSSP)<br>SCK (MSSP)<br>RC3                             |

| RC4      | SEG11 (LCD)<br>SDA (MSSP)<br>RC4                                          |

| RC5      | SEG10 (LCD)<br>SDO (MSSP)<br>RC5                                          |

| RC6      | ISEG9 (LCD)<br>TX (EUSART)<br>CK (EUSART)<br>CCP3/P3A, 28-pin only<br>RC6 |

| RC7      | SEG8 (LCD)<br>DT (EUSART)<br>CCP3/P3B, 28 pin only<br>RC7                 |

TABLE 12-7: PORTC OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

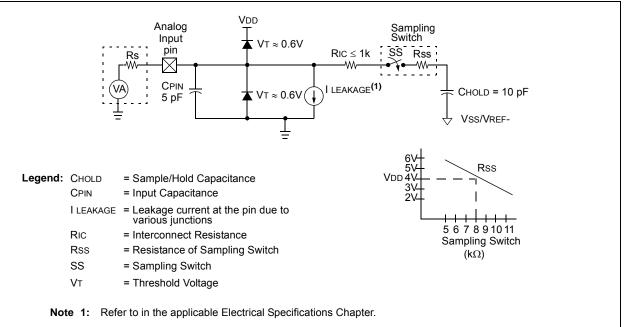

## FIGURE 15-4: ANALOG INPUT MODEL

# 20.2 Option and Timer0 Control Register

## REGISTER 20-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1         | R/W-1/1                       | R/W-1/1                                | R/W-1/1    | R/W-1/1                            | R/W-1/1       | R/W-1/1          | R/W-1/1      |  |  |  |

|-----------------|-------------------------------|----------------------------------------|------------|------------------------------------|---------------|------------------|--------------|--|--|--|

| WPUEN           | INTEDG                        | TMR0CS                                 | TMR0SE     | PSA                                |               | PS<2:0>          |              |  |  |  |

| oit 7           |                               |                                        |            |                                    |               |                  | bit 0        |  |  |  |

|                 |                               |                                        |            |                                    |               |                  |              |  |  |  |

| Legend:         |                               |                                        |            |                                    |               |                  |              |  |  |  |

| R = Readable    | bit                           | W = Writable                           | bit        | U = Unimplemented bit, read as '0' |               |                  |              |  |  |  |

| u = Bit is unch | •                             | x = Bit is unkr                        |            | -n/n = Value a                     | at POR and BO | R/Value at all c | other Resets |  |  |  |

| 1' = Bit is set |                               | '0' = Bit is clea                      | ared       |                                    |               |                  |              |  |  |  |

| bit 7           | WPUEN: We                     | ak Pull-up Enal                        | ble bit    |                                    |               |                  |              |  |  |  |

|                 |                               | pull-ups are dis<br>Il-ups are enabl   |            |                                    |               |                  |              |  |  |  |

| oit 6           | INTEDG: Inte                  | errupt Edge Sel                        | ect bit    |                                    |               |                  |              |  |  |  |

|                 |                               | on rising edge on falling edge         |            |                                    |               |                  |              |  |  |  |

| oit 5           | TMR0CS: Tir                   | imer0 Clock Source Select bit          |            |                                    |               |                  |              |  |  |  |

|                 | 1 = Transition on TOCKI pin   |                                        |            |                                    |               |                  |              |  |  |  |

|                 |                               | nstruction cycle                       | -          | 4)                                 |               |                  |              |  |  |  |

| oit 4           |                               | : Timer0 Source Edge Select bit        |            |                                    |               |                  |              |  |  |  |

|                 |                               | it on high-to-lov<br>it on low-to-high |            |                                    |               |                  |              |  |  |  |

| oit 3           | PSA: Prescaler Assignment bit |                                        |            |                                    |               |                  |              |  |  |  |

|                 |                               | r is not assigne<br>r is assigned to   |            |                                    |               |                  |              |  |  |  |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pre     | escaler Rate Se                        | elect bits |                                    |               |                  |              |  |  |  |

|                 | Bit                           | Value Timer0                           | Rate       |                                    |               |                  |              |  |  |  |

|                 |                               | 000 1:2                                |            |                                    |               |                  |              |  |  |  |

|                 |                               |                                        |            |                                    |               |                  |              |  |  |  |

|                 |                               | 010 1:8<br>011 1:1                     |            |                                    |               |                  |              |  |  |  |

|                 |                               | 1:3                                    |            |                                    |               |                  |              |  |  |  |

|                 |                               | 1:6                                    |            |                                    |               |                  |              |  |  |  |

|                 |                               |                                        |            |                                    |               |                  |              |  |  |  |

|                 | -                             | 111 <b>1</b> :2                        | 00         |                                    |               |                  |              |  |  |  |

## TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7      | Bit 6         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|------------|---------------|--------|--------|--------|--------|---------|--------|---------------------|

| CPSCON0    | CPSON      | _             | —      | _      | CPSRN  | G<1:0> | CPSOUT  | TOXCS  | 323                 |

| INTCON     | GIE        | PEIE          | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 98                  |

| OPTION_REG | WPUEN      | INTEDG        | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 193                 |

| TMR0       | Timer0 Mod | lule Register |        |        |        |        |         |        | 191*                |

| TRISA      | TRISA7     | TRISA6        | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 133                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

Page provides register information.

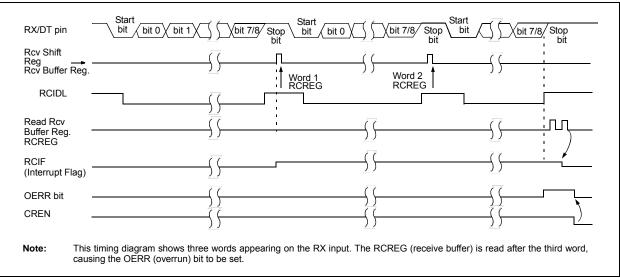

- 25.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

## FIGURE 25-5: ASYNCHRONOUS RECEPTION

| Name    | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                       | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 302                 |

| INTCON  | GIE                          | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |

| PIE1    | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 99                  |

| PIR1    | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 102                 |

| RCREG   | EUSART Receive Data Register |        |        |        |        |        |        |        | 296*                |

| RCSTA   | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 301                 |

| SPBRGL  | BRG<7:0>                     |        |        |        |        |        |        |        | 303*                |

| SPBRGH  | BRG<15:8>                    |        |        |        |        |        |        | 303*   |                     |

| TRISC   | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 142                 |

| TXSTA   | CSRC                         | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 300                 |

## TABLE 25-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

## 26.7.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note AN1103, "*Software Handling for Capacitive Sensing*" (DS01103) for more detailed information on the software required for CPS module.

| Note: | For more information on general capacitive<br>sensing refer to Application Notes:     |

|-------|---------------------------------------------------------------------------------------|

|       | <ul> <li>AN1101, "Introduction to Capacitive<br/>Sensing" (DS01101)</li> </ul>        |

|       | <ul> <li>AN1102, "Layout and Physical<br/>Design Guidelines for Capacitive</li> </ul> |

Sensing" (DS01102)

# 26.8 Operation during Sleep

The capacitive sensing oscillator will continue to run as long as the module is enabled, independent of the part being in Sleep. In order for the software to determine if a frequency change has occurred, the part must be awake. However, the part does not have to be awake when the timer resource is acquiring counts.

Note: Timer0 does not operate when in Sleep, and therefore cannot be used for capacitive sense measurements in Sleep.

# 30.2 DC Characteristics: PIC16(L)F1934/6/7-I/E (Industrial, Extended)

| PIC16LF1934/36/37 |                                    |      | Operating temperature |      |       | itions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                 |  |  |

|-------------------|------------------------------------|------|-----------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| PIC16F1934/36/37  |                                    |      |                       |      |       |                                                                                                                               | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended   |  |  |

| Param Device      |                                    |      | Turt                  |      | 11    | Conditions                                                                                                                    |                                                                                 |  |  |

| No.               | Characteristics                    | Min. | Тур†                  | Max. | Units | Vdd                                                                                                                           | Note                                                                            |  |  |

|                   | Supply Current (IDD) <sup>(1</sup> | , 2) |                       |      |       |                                                                                                                               |                                                                                 |  |  |

| D009              | LDO Regulator                      | -    | 350                   | —    | μA    | _                                                                                                                             | HS, EC OR INTOSC/INTOSCIO (8-16 MHz)<br>Clock modes with all VCAP pins disabled |  |  |

|                   |                                    |      | 50                    | _    | μΑ    | _                                                                                                                             | All VCAP pins disabled                                                          |  |  |

|                   |                                    |      | 30                    | —    | μA    | _                                                                                                                             | VCAP enabled on RA0, RA5 or RA6                                                 |  |  |

|                   |                                    | _    | 5                     | —    | μΑ    | _                                                                                                                             | LP Clock mode and Sleep (requires FVR and BOR to be disabled)                   |  |  |

| D010              |                                    |      | 7.0                   | 16   | μA    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |

|                   |                                    | —    | 9.0                   | 20   | μA    | 3.0                                                                                                                           | LP Oscillator mode (Note 4),<br>-40°C $\leq$ Ta $\leq$ +85°C                    |  |  |

| D010              |                                    |      | 29                    | 63   | μA    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |

|                   |                                    |      | 37                    | 74   | μA    | 3.0                                                                                                                           | LP Oscillator mode (Note 4, 5),<br>$-40^{\circ}C \le TA \le +85^{\circ}C$       |  |  |

|                   |                                    |      | 40                    | 79   | μΑ    | 5.0                                                                                                                           |                                                                                 |  |  |

| D010A             |                                    |      | 7.0                   | 23   | μA    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |

|                   |                                    | —    | 9.0                   | 27   | μA    | 3.0                                                                                                                           | LP Oscillator mode <b>(Note 4)</b><br>-40°C ≤ TA ≤ +125°C                       |  |  |

| D010A             |                                    |      | 29                    | 68   | μA    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |

|                   |                                    |      | 37                    | 88   | μA    | 3.0                                                                                                                           | LP Oscillator mode (Note 4, 5)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$       |  |  |

|                   |                                    |      | 40                    | 95   | μΑ    | 5.0                                                                                                                           | $-40.0 \leq 14 \leq +125.0$                                                     |  |  |

| D011              |                                    | _    | 140                   | 200  | μΑ    | 1.8                                                                                                                           | Fosc = 1 MHz                                                                    |  |  |

|                   |                                    | _    | 250                   | 330  | μΑ    | 3.0                                                                                                                           | XT Oscillator mode                                                              |  |  |

| D011              |                                    | _    | 160                   | 260  | μΑ    | 1.8                                                                                                                           | Fosc = 1 MHz                                                                    |  |  |

|                   |                                    | —    | 280                   | 480  | μΑ    | 3.0                                                                                                                           | XT Oscillator mode (Note 5)                                                     |  |  |

|                   |                                    | -    | 390                   | 690  | μA    | 5.0                                                                                                                           |                                                                                 |  |  |

| D012              |                                    | _    | 430                   | 650  | μA    | 1.8                                                                                                                           | Fosc = 4 MHz                                                                    |  |  |

|                   |                                    | —    | 750                   | 1000 | μΑ    | 3.0                                                                                                                           | XT Oscillator mode                                                              |  |  |

| D012              |                                    | —    | 450                   | 700  | μΑ    | 1.8                                                                                                                           | Fosc = 4 MHz                                                                    |  |  |

|                   |                                    | _    | 770                   | 1100 | μA    | 3.0                                                                                                                           | XT Oscillator mode (Note 5)                                                     |  |  |

|                   | _                                  |      | 930                   | 1300 | μA    | 5.0                                                                                                                           |                                                                                 |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: FVR and BOR are disabled.

- 5: 0.1  $\mu$ F capacitor on VCAP (RA0).

- 6: 8 MHz crystal oscillator with 4x PLL enabled.

| Operating    | <b>Operating Conditions:</b> 1.8V < VDD < 5.5V, -40°C < TA < +125°C (unless otherwise stated). |                                            |      |      |      |       |                 |  |

|--------------|------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|-------|-----------------|--|

| Param<br>No. | Sym.                                                                                           | Characteristics                            | Min. | Тур. | Max. | Units | Comments        |  |

| CM01         | VIOFF                                                                                          | Input Offset Voltage                       | _    | ±7.5 | ±60  | mV    | High-Power mode |  |

| CM02         | VICM                                                                                           | Input Common Mode Voltage                  | 0    | _    | Vdd  | V     |                 |  |

| CM03         | CMRR                                                                                           | Common Mode Rejection Ratio                | _    | 50   | _    | dB    |                 |  |

| CM04A        |                                                                                                | Response Time Rising Edge                  | _    | 400  | 800  | ns    | High-Power mode |  |

| CM04B        | TRESP                                                                                          | Response Time Falling Edge                 | —    | 200  | 400  | ns    | High-Power mode |  |

| CM04C        | TRESP                                                                                          | Response Time Rising Edge                  | _    | 1200 | _    | ns    | Low-Power mode  |  |

| CM04D        | 1                                                                                              | Response Time Falling Edge                 | _    | 550  | _    | ns    | Low-Power mode  |  |

| CM05         | Тмс2о∨                                                                                         | Comparator Mode Change to<br>Output Valid* | _    | _    | 10   | μs    |                 |  |

| CM06         | CHYSTER                                                                                        | Comparator Hysteresis                      | —    | 45   | —    | mV    | Hysteresis on   |  |

## **TABLE 30-10: COMPARATOR SPECIFICATIONS**

These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

2: Comparator Hysteresis is available when the CxHYS bit of the CMxCON0 register is enabled.

# TABLE 30-11: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| <b>Operating Conditions:</b> 2.5V < VDD < 5.5V, -40°C < TA < +125°C (unless otherwise stated). |                                                     |                              |      |        |       |       |          |  |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------|------|--------|-------|-------|----------|--|

| Param<br>No.                                                                                   | Sym.                                                | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |  |

| DAC01*                                                                                         | CLSB                                                | Step Size                    | _    | VDD/32 |       | V     |          |  |

| DAC02*                                                                                         | CACC                                                | Absolute Accuracy            | —    | —      | ± 1/2 | LSb   |          |  |

| DAC03*                                                                                         | CR                                                  | Unit Resistor Value (R)      | —    | 5000   |       | Ω     |          |  |

| DAC04*                                                                                         | CST                                                 | Settling Time <sup>(1)</sup> | _    | _      | 10    | μS    |          |  |

| *                                                                                              | * These parameters are characterized but not tested |                              |      |        |       |       |          |  |

These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

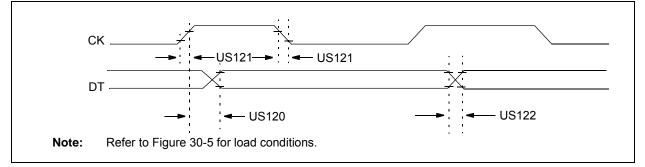

#### FIGURE 30-14: **USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING**

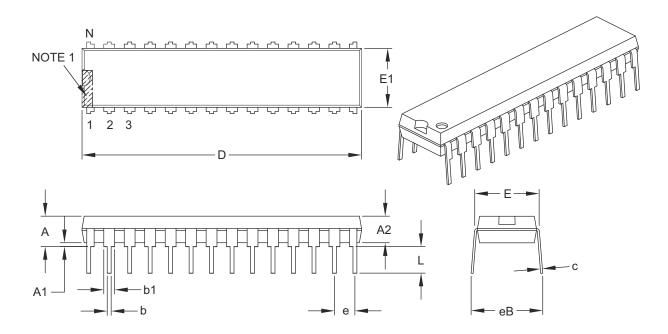

## 33.2 Package Details

The following sections give the technical details of the packages.

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            | INCHES |          |       |  |

|----------------------------|------------------|--------|----------|-------|--|

|                            | Dimension Limits |        | NOM      | MAX   |  |

| Number of Pins             | N                |        | 28       |       |  |

| Pitch                      | е                |        | .100 BSC |       |  |

| Top to Seating Plane       | A                | -      | -        | .200  |  |

| Molded Package Thickness   | A2               | .120   | .135     | .150  |  |

| Base to Seating Plane      | A1               | .015   | -        | -     |  |

| Shoulder to Shoulder Width | E                | .290   | .310     | .335  |  |

| Molded Package Width       | E1               | .240   | .285     | .295  |  |

| Overall Length             | D                | 1.345  | 1.365    | 1.400 |  |

| Tip to Seating Plane       | L                | .110   | .130     | .150  |  |

| Lead Thickness             | С                | .008   | .010     | .015  |  |

| Upper Lead Width           | b1               | .040   | .050     | .070  |  |

| Lower Lead Width           | b                | .014   | .018     | .022  |  |

| Overall Row Spacing §      | eB               | _      | _        | .430  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (12/2008)

Original release

## Revision B (04/2009)

Revised data sheet title; Revised Features section.

# Revision C (10/2009)

Added PIC16L/LF1933/34. General updates.

# Revision D (12/2009)

General updates.

# Revision E (5/2011)

Separated 193X data sheet into three separate data sheets. Added Characterization Data.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{0}}$  devices to the PIC16(L)F1934/6/7 family of devices.

## B.1 PIC16F917 to PIC16F1937

## TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F917         | PIC16F1937          |

|---------------------------------------|-------------------|---------------------|

| Max. Operating Speed                  | 20 MHz            | 32 MHz              |

| Max. Program<br>Memory (Words)        | 8K                | 8K                  |

| Max. SRAM (Bytes)                     | 368               | 512                 |

| A/D Resolution                        | 10-bit            | 10-bit              |

| Timers (8/16-bit)                     | 2/1               | 4/1                 |

| Oscillator Modes                      | 4                 | 8                   |

| Brown-out Reset                       | Y                 | Y                   |

| Internal Pull-ups                     | RB<7:0>           | RB<7:0>             |

| Interrupt-on-change                   | RB<7:4>           | RB<7:0>             |

| Comparator                            | 2                 | 2                   |

| AUSART/EUSART                         | 1/0               | 0/1                 |

| Extended WDT                          | Y                 | Y                   |

| Software Control<br>Option of WDT/BOR | N                 | Y                   |

| INTOSC Frequencies                    | 30 kHz -<br>8 MHz | 500 kHz -<br>32 MHz |

| Clock Switching                       | Y                 | Y                   |

| Capacitive Sensing                    | N                 | Y                   |

| CCP/ECCP                              | 2/0               | 2/3                 |

| Enhanced PIC16 CPU                    | Ν                 | Y                   |

| MSSP/SSP                              | 0/1               | 1/0                 |

| LCD                                   | Y                 | Y                   |

NOTES: