Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 169-UFBGA                                                                           |

| Supplier Device Package    | 169-UFBGA (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437aih6tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode: MR operates in normal mode (default mode of MR in stop mode) MR operates in under-drive mode (reduced leakage mode).

LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to Table 3 for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 22: Power supply scheme* and *Table 19: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. - means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

# 3.18.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 17: General operating conditions*. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 22: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

# 3.42 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.43 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F43x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|         |         |          | Pin nı   | ımber   | -        |         |          |                                                      |          |                 |       |                                                                                       |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| -       | -       | C11      | D14      | 132     | -        | 155     | D14      | PI1                                                  | I/O      | FT              | -     | SPI2_SCK/I2S2_CK <sup>(7)</sup> ,<br>FMC_D25, DCMI_D8,<br>LCD_G6, EVENTOUT            | -                       |

| -       | -       | B12      | C14      | 133     | -        | 156     | C14      | PI2                                                  | I/O      | FT              | -     | TIM8_CH4,<br>SPI2_MISO,<br>I2S2ext_SD, FMC_D26,<br>DCMI_D9, LCD_G7,<br>EVENTOUT       | -                       |

| -       | -       | A12      | C13      | 134     | -        | 157     | C13      | PI3                                                  | I/O      | FT              | -     | TIM8_ETR,<br>SPI2_MOSI/I2S2_SD,<br>FMC_D27, DCMI_D10,<br>EVENTOUT                     | -                       |

| -       | -       | D11      | D9       | 135     | F5       | -       | F9       | $V_{SS}$                                             | S        |                 | -     | -                                                                                     | -                       |

| -       | -       | D3       | C9       | 136     | A1       | 158     | E10      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                     | -                       |

| 76      | 109     | A11      | A14      | 137     | B1       | 159     | A14      | PA14<br>(JTCK-<br>SWCLK)                             | I/O      | FT              | -     | JTCK-SWCLK/<br>EVENTOUT                                                               | -                       |

| 77      | 110     | B11      | A13      | 138     | C2       | 160     | A13      | PA15<br>(JTDI)                                       | I/O      | FT              | -     | JTDI,<br>TIM2_CH1/TIM2_ETR,<br>SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>EVENTOUT             | -                       |

| 78      | 111     | C10      | B14      | 139     | A2       | 161     | B14      | PC10                                                 | I/O      | FT              | -     | SPI3_SCK/I2S3_CK,<br>USART3_TX,<br>UART4_TX, SDI0_D2,<br>DCMI_D8, LCD_R2,<br>EVENTOUT | -                       |

| 79      | 112     | B10      | B13      | 140     | B2       | 162     | B13      | PC11                                                 | I/O      | FT              | -     | I2S3ext_SD,<br>SPI3_MISO,<br>USART3_RX,<br>UART4_RX, SDIO_D3,<br>DCMI_D4, EVENTOUT    | -                       |

| 80      | 113     | A10      | A12      | 141     | C3       | 163     | A12      | PC12                                                 | I/O      | FT              | -     | SPI3_MOSI/I2S3_SD,<br>USART3_CK,<br>UART5_TX, SDIO_CK,<br>DCMI_D9, EVENTOUT           | -                       |

| 81      | 114     | D9       | B12      | 142     | B3       | 164     | B12      | PD0                                                  | I/O      | FT              | -     | CAN1_RX, FMC_D2,<br>EVENTOUT                                                          | -                       |

| Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued) |

|----------------------------------------------------------------------------|

|                                                                            |

| Pin name | CF    | NOR/PSRAM/ | NOR/PSRAM | NAND16 | SDRAM  |

|----------|-------|------------|-----------|--------|--------|

|          |       | SRAM       | Mux       |        |        |

| PF6      | NIORD |            |           |        |        |

| PF7      | NREG  |            |           |        |        |

| PF8      | NIOWR |            |           |        |        |

| PF9      | CD    |            |           |        |        |

| PF10     | INTR  |            |           |        |        |

| PG6      |       |            |           | INT2   |        |

| PG7      |       |            |           | INT3   |        |

| PE0      |       | NBL0       | NBL0      |        | NBL0   |

| PE1      |       | NBL1       | NBL1      |        | NBL1   |

| PI4      |       | NBL2       |           |        | NBL2   |

| PI5      |       | NBL3       |           |        | NBL3   |

| PG8      |       |            |           |        | SDCLK  |

| PC0      |       |            |           |        | SDNWE  |

| PF11     |       |            |           |        | SDNRAS |

| PG15     |       |            |           |        | SDNCAS |

| PH2      |       |            |           |        | SDCKE0 |

| PH3      |       |            |           |        | SDNE0  |

| PH6      |       |            |           |        | SDNE1  |

| PH7      |       |            |           |        | SDCKE1 |

| PH5      |       |            |           |        | SDNWE  |

| PC2      |       |            |           |        | SDNE0  |

| PC3      |       |            |           |        | SDCKE0 |

| PB5      |       |            |           |        | SDCKE1 |

| PB6      |       |            |           |        | SDNE1  |

Table 11. FMC pin definition (continued)

577

DocID024244 Rev 10

|           |      |     |        | Table 1      | 2. STM3          | 32F43         | 7xx and                   | d STM32         | 2F439xx                 | alternate                  | function                       | mapping                 | (continu         | ued)                 |                |        |              |

|-----------|------|-----|--------|--------------|------------------|---------------|---------------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|------------------|----------------------|----------------|--------|--------------|

|           |      | AF0 | AF1    | AF2          | AF3              | AF4           | AF5                       | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11             | AF12                 | AF13           | AF14   | AF15         |

| P         | ort  | SYS | TIM1/2 | TIM3/4/5     | TIM8/9/<br>10/11 | l2C1/<br>2/3  | SPI1/2/<br>3/4/5/6        | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН              | FMC/SDIO<br>/OTG2_FS | DCMI           | LCD    | SYS          |

|           | PH7  | -   | -      | -            | -                | I2C3_<br>SCL  | SPI5_<br>MISO             | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>RXD3 | FMC_<br>SDCKE1       | DCMI_<br>D9    | -      | -            |

|           | PH8  | -   | -      | -            | -                | I2C3_<br>SDA  | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_D16              | DCMI_<br>HSYNC | LCD_R2 | EVEN<br>TOUT |

|           | PH9  | -   | -      | -            | -                | I2C3_<br>SMBA | -                         | -               | -                       | -                          | TIM12_CH2                      | -                       | -                | FMC_D17              | DCMI_<br>D0    | LCD_R3 | EVEN<br>TOUT |

|           | PH10 | -   | -      | TIM5_<br>CH1 | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_D18              | DCMI_<br>D1    | LCD_R4 | EVEN<br>TOUT |

| Port<br>H | PH11 | -   | -      | TIM5_<br>CH2 | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_D19              | DCMI_<br>D2    | LCD_R5 | EVEN<br>TOUT |

|           | PH12 | -   | -      | TIM5_<br>CH3 | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_D20              | DCMI_<br>D3    | LCD_R6 | EVEN<br>TOUT |

|           | PH13 | -   | -      | -            | TIM8_<br>CH1N    | -             | -                         | -               | -                       | -                          | CAN1_TX                        | -                       | -                | FMC_D21              | -              | LCD_G2 | EVEN<br>TOUT |

|           | PH14 | -   | -      | -            | TIM8_<br>CH2N    | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_D22              | DCMI_<br>D4    | LCD_G3 | EVEN<br>TOUT |

|           | PH15 | -   | -      | -            | TIM8_<br>CH3N    | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_D23              | DCMI_<br>D11   | LCD_G4 | EVEN<br>TOUT |

|           | P10  | -   | -      | TIM5_<br>CH4 | -                | -             | SPI2_<br>NSS/I2<br>S2_WS  | -               | -                       | -                          | -                              | -                       | -                | FMC_D24              | DCMI_<br>D13   | LCD_G5 | EVEN<br>TOUT |

|           | PI1  | -   | -      | -            | -                | -             | SPI2_<br>SCK/I2<br>S2_CK  | -               | -                       | -                          | -                              | -                       | -                | FMC_D25              | DCMI_<br>D8    | LCD_G6 | EVEN<br>TOUT |

|           | PI2  | -   | -      | -            | TIM8_<br>CH4     | -             | SPI2_<br>MISO             | I2S2ext_<br>SD  | -                       | -                          | -                              | -                       | -                | FMC_D26              | DCMI_<br>D9    | LCD_G7 | EVEN<br>TOUT |

| Port I    | PI3  | -   | -      | -            | TIM8_<br>ETR     | -             | SPI2_M<br>OSI/I2S<br>2_SD |                 |                         |                            |                                |                         |                  | FMC_D27              | DCMI_D<br>10   |        | EVEN<br>TOUT |

|           | PI4  | -   | -      | -            | TIM8_<br>BKIN    | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_<br>NBL2         | DCMI_D<br>5    | LCD_B4 | EVEN<br>TOUT |

|           | PI5  | -   | -      | -            | TIM8_<br>CH1     | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_<br>NBL3         | DCMI_<br>VSYNC | LCD_B5 | EVEN<br>TOUT |

|           | PI6  | -   | -      | -            | TIM8_<br>CH2     | -             | -                         | -               | -                       | -                          | -                              | -                       | -                | FMC_D28              | DCMI_<br>D6    | LCD_B6 | EVEN<br>TOUT |

# STM32F437xx and STM32F439xx

Pinouts and pin description

82/240

| Symbol          | Parameter                                                          | Conditions <sup>(1)</sup>            | Min   | Тур | Мах                       | Unit |

|-----------------|--------------------------------------------------------------------|--------------------------------------|-------|-----|---------------------------|------|

|                 | Input voltage on RST and FT                                        | 2 V ≤V <sub>DD</sub> ≤3.6 V          | - 0.3 | -   | 5.5                       |      |

|                 | pins <sup>(7)</sup>                                                | V <sub>DD</sub> ≤2 V                 | - 0.3 | -   | 5.2                       |      |

| V <sub>IN</sub> | Input voltage on TTa pins                                          |                                      | - 0.3 | -   | V <sub>DDA</sub> +<br>0.3 | V    |

|                 | Input voltage on BOOT0 pin                                         |                                      | 0     | -   | 9                         |      |

|                 |                                                                    | LQFP100                              | -     | -   | 465                       |      |

|                 |                                                                    | WLCSP143                             | -     | -   | 641                       |      |

| D_              | Power dissipation at $T_A = 85 \degree C$                          | LQFP144                              | -     | -   | 500                       |      |

|                 |                                                                    | UFBGA169                             | -     | -   | 385                       | m\// |

| $P_D$           | for suffix 6 or $T_A = 105 \text{ °C}$ for suffix 7 <sup>(8)</sup> | LQFP176                              | -     | -   | 526                       | mW   |

|                 |                                                                    | UFBGA176                             | -     | -   | 513                       |      |

|                 |                                                                    | LQFP208                              | -     | -   | 1053                      |      |

|                 |                                                                    | TFBGA216                             | -     | -   | 690                       |      |

|                 | Ambient temperature for 6 suffix                                   | Maximum power dissipation            | - 40  |     | 85                        | °C   |

| т.              | version                                                            | Low power dissipation <sup>(9)</sup> | - 40  |     | 105                       |      |

| ΤΑ              | Ambient temperature for 7 suffix                                   | Maximum power dissipation            | - 40  |     | 105                       | °C   |

|                 | version                                                            | Low power dissipation <sup>(9)</sup> | - 40  |     | 125                       |      |

| ТJ              | lunction tomporature range                                         | 6 suffix version                     | - 40  |     | 105                       | °C   |

| IJ              | Junction temperature range                                         | 7 suffix version                     | - 40  |     | 125                       |      |

Table 17. General operating conditions (continued)

1. The over-drive mode is not supported at the voltage ranges from 1.7 to 2.1 V.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

3. When the ADC is used, refer to *Table 74: ADC characteristics*.

4. If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF+} < 1.2$  V.

5. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

- 6. The over-drive mode is not supported when the internal regulator is OFF.

- 7. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

8. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

9. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

# 6.3.5 Reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                              | Parameter                  | Conditions                  | Min  | Тур  | Max  | Unit |

|-------------------------------------|----------------------------|-----------------------------|------|------|------|------|

|                                     |                            | PLS[2:0]=000 (rising edge)  | 2.09 | 2.14 | 2.19 | V    |

|                                     |                            | PLS[2:0]=000 (falling edge) | 1.98 | 2.04 | 2.08 | V    |

|                                     |                            | PLS[2:0]=001 (rising edge)  | 2.23 | 2.30 | 2.37 | V    |

|                                     |                            | PLS[2:0]=001 (falling edge) | 2.13 | 2.19 | 2.25 | V    |

|                                     |                            | PLS[2:0]=010 (rising edge)  | 2.39 | 2.45 | 2.51 | V    |

|                                     |                            | PLS[2:0]=010 (falling edge) | 2.29 | 2.35 | 2.39 | V    |

|                                     |                            | PLS[2:0]=011 (rising edge)  | 2.54 | 2.60 | 2.65 | V    |

| V                                   | Programmable voltage       | PLS[2:0]=011 (falling edge) | 2.44 | 2.51 | 2.56 | V    |

| V <sub>PVD</sub>                    | detector level selection   | PLS[2:0]=100 (rising edge)  | 2.70 | 2.76 | 2.82 | V    |

|                                     |                            | PLS[2:0]=100 (falling edge) | 2.59 | 2.66 | 2.71 | V    |

|                                     |                            | PLS[2:0]=101 (rising edge)  | 2.86 | 2.93 | 2.99 | V    |

|                                     |                            | PLS[2:0]=101 (falling edge) | 2.65 | 2.84 | 2.92 | V    |

|                                     | PLS[2:0]=110 (rising edge) | 2.96                        | 3.03 | 3.10 | V    |      |

|                                     |                            | PLS[2:0]=110 (falling edge) | 2.85 | 2.93 | 2.99 | V    |

|                                     |                            | PLS[2:0]=111 (rising edge)  | 3.07 | 3.14 | 3.21 | V    |

|                                     |                            | PLS[2:0]=111 (falling edge) | 2.95 | 3.03 | 3.09 | V    |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis             |                             | -    | 100  | -    | mV   |

|                                     | Power-on/power-down        | Falling edge                | 1.60 | 1.68 | 1.76 | V    |

| V <sub>POR/PDR</sub>                | reset threshold            | Rising edge                 | 1.64 | 1.72 | 1.80 | V    |

| V <sub>PDRhyst</sub> <sup>(1)</sup> | PDR hysteresis             |                             | -    | 40   | -    | mV   |

| M                                   | Brownout level 1           | Falling edge                | 2.13 | 2.19 | 2.24 | V    |

| V <sub>BOR1</sub>                   | threshold                  | Rising edge                 | 2.23 | 2.29 | 2.33 | V    |

| M                                   | Brownout level 2           | Falling edge                | 2.44 | 2.50 | 2.56 | V    |

| V <sub>BOR2</sub>                   | threshold                  | Rising edge                 | 2.53 | 2.59 | 2.63 | V    |

| V                                   | Brownout level 3           | Falling edge                | 2.75 | 2.83 | 2.88 | V    |

| V <sub>BOR3</sub>                   | threshold                  | Rising edge                 | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup> | BOR hysteresis             |                             | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub>               | POR reset temporization    |                             | 0.5  | 1.5  | 3.0  | ms   |

| Symbol                             | Deremeter                       | Conditions                  | £ (MU-)                   | VDD:              | =3.3 V          | VDD               | =1.7 V          | Unit      |

|------------------------------------|---------------------------------|-----------------------------|---------------------------|-------------------|-----------------|-------------------|-----------------|-----------|

| Symbol                             | Parameter                       | Conditions                  | f <sub>HCLK</sub> (MHz) - | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub> | I <sub>DD</sub> |           |

|                                    |                                 |                             | 180                       | 61.5              | 1.4             | -                 | -               |           |

|                                    |                                 |                             | 168                       | 59.4              | 1.3             | 59.4              | 1.0             |           |

|                                    |                                 |                             | 150                       | 53.9              | 1.3             | 53.9              | 1.0             |           |

|                                    |                                 |                             | 144                       | 49.0              | 1.3             | 49.0              | 1.0             |           |

|                                    |                                 | All Peripherals<br>enabled  | 120                       | 38.0              | 1.2             | 38.0              | 0.9             |           |

|                                    |                                 |                             | 90                        | 29.3              | 1.4             | 29.3              | 1.1             | -         |

|                                    | Supply surrent                  |                             | 60                        | 20.2              | 1.2             | 20.2              | 0.9             |           |

|                                    |                                 |                             | 30                        | 11.9              | 1.2             | 11.9              | 0.9             |           |

| 1 /1                               | Supply current<br>in Sleep mode |                             | 25                        | 10.4              | 1.2             | 10.4              | 0.9             |           |

| I <sub>DD12</sub> /I <sub>DD</sub> | from V <sub>12</sub> and        |                             | 180                       | 14.9              | 1.4             | -                 | -               | - mA<br>- |

|                                    | $V_{DD}$ supply                 |                             | 168                       | 14.0              | 1.3             | 14.0              | 1.0             |           |

|                                    |                                 |                             | 150                       | 12.6              | 1.3             | 12.6              | 1.0             |           |

|                                    |                                 |                             | 144                       | 11.5              | 1.3             | 11.5              | 1.0             |           |

|                                    |                                 | All Peripherals<br>disabled | 120                       | 8.7               | 1.2             | 8.7               | 0.9             |           |

|                                    |                                 | aloubiou                    | 90                        | 7.1               | 1.4             | 7.1               | 1.1             | -         |

|                                    |                                 |                             | 60                        | 5.0               | 1.2             | 5.0               | 0.9             |           |

|                                    |                                 |                             | 30                        | 3.1               | 1.2             | 3.1               | 0.9             |           |

|                                    |                                 |                             | 25                        | 2.8               | 1.2             | 2.8               | 0.9             |           |

| Table 33. Tyical current consumption in Sleep mode, regulator OFF <sup>(1)</sup> |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 56: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 35: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DD</sub> is the MCU supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

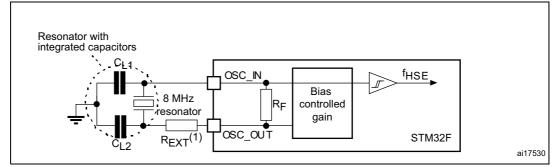

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 29*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                                     |                                         | ( LOL                         |       |      |      |      |

|-------------------------------------|-----------------------------------------|-------------------------------|-------|------|------|------|

| Symbol                              | Parameter                               | Conditions                    | Min   | Тур  | Max  | Unit |

| R <sub>F</sub>                      | Feedback resistor                       |                               | -     | 18.4 | -    | MΩ   |

| I <sub>DD</sub>                     | LSE current consumption                 |                               | -     | -    | 1    | μA   |

| ACC <sub>LSE</sub> <sup>(2)</sup>   | LSE accuracy                            |                               | - 500 | -    | 500  | ppm  |

| G <sub>m</sub> _crit_max            | Maximum critical crystal g <sub>m</sub> | Startup                       | -     | -    | 0.56 | μA/V |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | startup time                            | V <sub>DD</sub> is stabilized | -     | 2    | -    | s    |

Table 40. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. Refer to application note AN2867.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

# 6.3.13 Memory characteristics

### Flash memory

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter                      | Conditions                                         | Min | Тур | Max | Unit |

|-----------------|--------------------------------|----------------------------------------------------|-----|-----|-----|------|

|                 |                                | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V         | -   | 5   | -   |      |

| I <sub>DD</sub> | I <sub>DD</sub> Supply current | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V        | -   | 8   | -   | mA   |

|                 |                                | Write / Erase 32-bit mode, V <sub>DD</sub> = 3.3 V | -   | 12  | -   |      |

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 16   | 32                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 11   | 22                 | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |

### Table 48. Flash memory programming

# 6.3.15 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/ESDA/JEDEC JS-001 and ANSI/ESD S5.3.1 standards.

| Symbol                | Ratings                                            | Conditions                                                                                                        |    | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model) | T <sub>A</sub> = +25 °C conforming to<br>ANSI/ESDA/JEDEC JS-001                                                   |    | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device     | $T_A$ = +25 °C conforming to ANSI/ESD S5.3.1,<br>LQFP100/144/176, UFBGA169/176,<br>TFBGA176 and WLCSP143 packages | C3 | 250                             | V    |

| *ESD(CDM)             | model)                                             | $T_A = +25$ °C conforming to ANSI/ESD S5.3.1,<br>LQFP208 package                                                  | C3 | 250                             |      |

### Table 53. ESD absolute maximum ratings

1. Guaranteed by characterization results.

### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

|   | Symbol | Parameter             | Conditions                                    | Class      |

|---|--------|-----------------------|-----------------------------------------------|------------|

| ſ | LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

### Table 54. Electrical sensitivities

# 6.3.19 TIM timer characteristics

The parameters given in Table 60 are guaranteed by design.

Refer to Section 6.3.17: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter Conditions <sup>(3)</sup> Min         |                                                                      | Min | Max                     | Unit                 |  |

|------------------------|-------------------------------------------------|----------------------------------------------------------------------|-----|-------------------------|----------------------|--|

| t <sub>res(TIM)</sub>  | Timer resolution time                           | AHB/APBx prescaler=1<br>or 2 or 4, f <sub>TIMxCLK</sub> =<br>180 MHz | 1   | -                       | t <sub>TIMxCLK</sub> |  |

| ,                      |                                                 | AHB/APBx prescaler>4,<br>f <sub>TIMxCLK</sub> = 90 MHz               | 1   | -                       | t <sub>TIMxCLK</sub> |  |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 180 MHz                                       | 0   | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| Res <sub>TIM</sub>     | Timer resolution                                |                                                                      | -   | 16/32                   | bit                  |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count<br>with 32-bit counter   |                                                                      | -   | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |  |

| Table 60 | . TIMx | characteristics <sup>(1)(2)</sup> |

|----------|--------|-----------------------------------|

|----------|--------|-----------------------------------|

1. TIMx is used as a general term to refer to the TIM1 to TIM12 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 or APB2 is up to 180 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK = 4x PCLKx.

# 6.3.20 Communications interfaces

# I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0090 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 6.3.17: I/O port characteristics for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Max                | Unit |  |  |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|--|--|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |  |  |

| Table 61 | . I2C | analog | filter | characte | eristics <sup>(1)</sup> |

|----------|-------|--------|--------|----------|-------------------------|

|----------|-------|--------|--------|----------|-------------------------|

- 1. Guaranteed by design.

- 2. Spikes with widths below  $t_{AF(min)}$  are filtered.

- 3. Spikes with widths above  $t_{AF(max)}$  are not filtered

### **SPI interface characteristics**

Unless otherwise specified, the parameters given in *Table 62* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                    | Parameter                            | Conditions                                                   |                             | Min | Тур | Max               | Unit |

|-------------------------------------------|--------------------------------------|--------------------------------------------------------------|-----------------------------|-----|-----|-------------------|------|

|                                           |                                      | Master mode, SPI1/4/5/6,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V     |                             |     |     | 45                |      |

|                                           |                                      | Slave mode,                                                  | Receiver                    | -   | -   | 45                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | SPI clock frequency                  | SPI1/4/5/6,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V                  | Transmitter/<br>full-duplex |     |     | 38 <sup>(2)</sup> | MHz  |

|                                           |                                      | Master mode, SPI1/2/3/4/5/6,<br>1.7 V≤V <sub>DD</sub> ≤3.6 V |                             |     |     | 22.5              |      |

|                                           |                                      | Slave mode, SPI1/2/3/4/5/6,<br>1.7 V≤V <sub>DD</sub> ≤3.6 V  |                             |     | -   | -                 | 22.5 |

| Duty(SCK)                                 | Duty cycle of SPI clock<br>frequency | Slave mode                                                   |                             | 30  | 50  | 70                | %    |

Table 62. SPI dynamic characteristics<sup>(1)</sup>

# I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 63* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                             | Min    | Max                   | Unit |

|------------------------|--------------------------------|----------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256x8K | 256xFs <sup>(2)</sup> | MHz  |

| f                      | 129 clock froguency            | Master data: 32 bits                   | -      | 64xFs                 | MHz  |

| f <sub>CK</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -      | 64xFs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30     | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | 0      | 6                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 0      | -                     |      |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 1      | -                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 0      | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 7.5    | -                     |      |

| t <sub>su(SD_SR)</sub> |                                | Slave receiver                         | 2      | -                     |      |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 0      | -                     | ns   |

| t <sub>h(SD_SR)</sub>  |                                | Slave receiver                         | 0      | -                     |      |

| t <sub>v(SD_ST)</sub>  |                                | Slave transmitter (after enable edge)  | -      | 27                    |      |

| t <sub>h(SD_ST)</sub>  | Data output valid time         |                                        |        |                       |      |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -      | 20                    |      |

| t <sub>h(SD_MT)</sub>  | Data output hold time          | Master transmitter (after enable edge) | 2.5    | -                     |      |

| Table 63. I <sup>2</sup> S c | dynamic characteristics <sup>(1)</sup> |

|------------------------------|----------------------------------------|

|------------------------------|----------------------------------------|

1. Guaranteed by characterization results.

2. The maximum value of 256xFs is 45 MHz (APB1 maximum frequency).

Note: Refer to the I2S section of RM0090 reference manual for more details on the sampling frequency ( $F_S$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

DocID024244 Rev 10

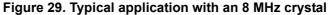

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.17 does not affect the ADC accuracy.

- 1. See also Table 76.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4. End point correlation line.

- E<sub>T</sub> = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

### **Electrical characteristics**

| Symbol                | Parameter                                                                             | Conditions | Min | Тур | Мах | Unit  | Comments                                                                                                                |  |

|-----------------------|---------------------------------------------------------------------------------------|------------|-----|-----|-----|-------|-------------------------------------------------------------------------------------------------------------------------|--|

| eysei                 |                                                                                       |            |     | .76 | max | ••••• |                                                                                                                         |  |

| t <sub>WAKEUP</sub> ( | Wakeup time from off<br>state (Setting the ENx<br>bit in the DAC Control<br>register) | -          | -   | 6.5 | 10  | μs    | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |  |

| PSRR+<br>(2)          | Power supply rejection<br>ratio (to V <sub>DDA</sub> ) (static<br>DC measurement)     | -          | -   | -67 | -40 | dB    | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |  |

# Table 85. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

2. Guaranteed by design.

The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization.

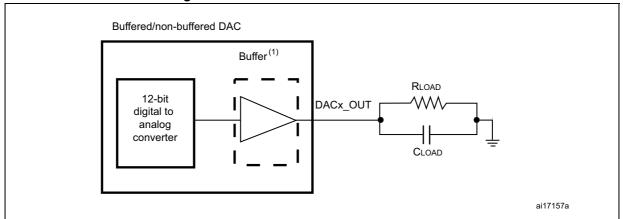

### Figure 54. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol                    | Parameter                                 | Min                     | Мах                   | Unit |

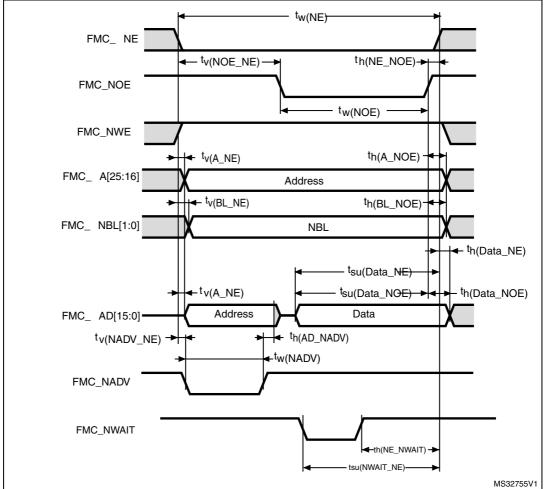

|---------------------------|-------------------------------------------|-------------------------|-----------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> +1   | 8T <sub>HCLK</sub> +2 | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> – 1  | 6T <sub>HCLK</sub> +2 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                     | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   |                       | ns   |

Table 89. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings  $^{(1)(2)}$

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

| Symbol                        | Parameter              | Min                      | Max                     | Unit |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 2                        | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |

| $t_{d(SDCLKL\_Add)}$          | Address valid time     | -                        | 1.5                     |      |

| t <sub>d(SDCLKL</sub> - SDNE) | Chip select valid time | -                        | 0.5                     | ns   |

| $t_{h(SDCLKL\_SDNE)}$         | Chip select hold time  | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                       |      |

# Table 102. SDRAM read timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

# Table 103. LPSDR SDRAM read timings<sup>(1)(2)</sup>

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |  |  |

|-------------------------------|------------------------|--------------------------|-------------------------|------|--|--|

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |  |  |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time  | 2.5                      | -                       |      |  |  |

| <sup>t</sup> h(SDCLKH_Data)   | Data input hold time   | 0                        | -                       |      |  |  |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                        | 1                       |      |  |  |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 1                       | ns   |  |  |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 1                        | -                       | 115  |  |  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time      | -                        | 1                       |      |  |  |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 1                        | -                       |      |  |  |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 1                       |      |  |  |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 1                        | -                       |      |  |  |

1. CL = 10 pF.

2. Guaranteed by characterization results.

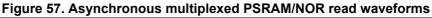

Figure 90. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.