Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Active                                                                              |

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, LCD, POR, PWM, WDT                                |

| Number of I/O              | 140                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 201-UFBGA                                                                           |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437igh6               |

|   | 3.22   | Timers       | and watchdogs                                             | . 33 |

|---|--------|--------------|-----------------------------------------------------------|------|

|   |        | 3.22.1       | Advanced-control timers (TIM1, TIM8)                      | . 35 |

|   |        | 3.22.2       | General-purpose timers (TIMx)                             | . 35 |

|   |        | 3.22.3       | Basic timers TIM6 and TIM7                                |      |

|   |        | 3.22.4       | Independent watchdog                                      |      |

|   |        | 3.22.5       | Window watchdog                                           |      |

|   |        | 3.22.6       | SysTick timer                                             |      |

|   | 3.23   |              | regrated circuit interface ( I <sup>2</sup> C)            |      |

|   | 3.24   |              | al synchronous/asynchronous receiver transmitters (USART) |      |

|   | 3.25   | <del>-</del> | eripheral interface (SPI)                                 |      |

|   | 3.26   |              | egrated sound (I <sup>2</sup> S)                          |      |

|   | 3.27   | Serial A     | Audio interface (SAI1)                                    | . 38 |

|   | 3.28   | Audio P      | PLL (PLLI2S)                                              | . 38 |

|   | 3.29   | Audio a      | nd LCD PLL(PLLSAI)                                        | . 38 |

|   | 3.30   | Secure       | digital input/output interface (SDIO)                     | . 39 |

|   | 3.31   | Etherne      | et MAC interface with dedicated DMA and IEEE 1588 support | . 39 |

|   | 3.32   | Controll     | ler area network (bxCAN)                                  | . 39 |

|   | 3.33   | Univers      | al serial bus on-the-go full-speed (OTG_FS)               | . 40 |

|   | 3.34   | Univers      | al serial bus on-the-go high-speed (OTG_HS)               | . 40 |

|   | 3.35   | Digital o    | camera interface (DCMI)                                   | . 41 |

|   | 3.36   | Cryptog      | raphic acceleration                                       | . 41 |

|   | 3.37   | Randon       | n number generator (RNG)                                  | . 41 |

|   | 3.38   | Genera       | I-purpose input/outputs (GPIOs)                           | . 41 |

|   | 3.39   | Analog-      | to-digital converters (ADCs)                              | . 42 |

|   | 3.40   | Temper       | ature sensor                                              | . 42 |

|   | 3.41   | Digital-t    | o-analog converter (DAC)                                  | . 42 |

|   | 3.42   | Serial w     | vire JTAG debug port (SWJ-DP)                             | . 43 |

|   | 3.43   | Embedo       | ded Trace Macrocell™                                      | . 43 |

| 4 | Pinou  | ıts and      | pin description                                           | . 44 |

| 5 | Memo   | ory map      | pping                                                     | . 85 |

| 6 | Electi | rical cha    | aracteristics                                             | . 90 |

|   | 6.1    | Parame       | eter conditions                                           | . 90 |

|   |        |              |                                                           |      |

# **List of figures**

| Figure 1.  | Compatible board design STM32F10xx/STM32F2xx/STM32F4xx                               |     |

|------------|--------------------------------------------------------------------------------------|-----|

|            | for LQFP100 package                                                                  | 17  |

| Figure 2.  | Compatible board design between STM32F10xx/STM32F2xx/STM32F4xx                       |     |

|            | for LQFP144 package                                                                  | 18  |

| Figure 3.  | Compatible board design between STM32F2xx and STM32F4xx                              |     |

|            | for LQFP176 and UFBGA176 packages                                                    | 18  |

| Figure 4.  | STM32F437xx and STM32F439xx block diagram                                            | 19  |

| Figure 5.  | STM32F437xx and STM32F439xx Multi-AHB matrix                                         |     |

| Figure 6.  | Power supply supervisor interconnection with internal reset OFF                      | 26  |

| Figure 7.  | PDR_ON control with internal reset OFF                                               | 27  |

| Figure 8.  | Regulator OFF                                                                        | 29  |

| Figure 9.  | Startup in regulator OFF: slow V <sub>DD</sub> slope                                 |     |

|            | - power-down reset risen after V <sub>CAP 1</sub> /V <sub>CAP 2</sub> stabilization  | 30  |

| Figure 10. | Startup in regulator OFF mode: fast $\overline{V}_{DD}$ slope                        |     |

|            | - power-down reset risen before V <sub>CAP_1</sub> /V <sub>CAP_2</sub> stabilization | 30  |

| Figure 11. | STM32F43x LQFP100 pinout                                                             | 44  |

| Figure 12. | STM32F43x WLCSP143 ballout                                                           |     |

| Figure 13. | STM32F43x LQFP144 pinout                                                             | 46  |

| Figure 14. | STM32F43x LQFP176 pinout                                                             | 47  |

| Figure 15. | STM32F43x LQFP208 pinout                                                             | 48  |

| Figure 16. | STM32F43x UFBGA169 ballout                                                           |     |

| Figure 17. | STM32F43x UFBGA176 ballout                                                           |     |

| Figure 18. | STM32F43x TFBGA216 ballout                                                           |     |

| Figure 19. | Memory map                                                                           | 85  |

| Figure 20. | Pin loading conditions                                                               |     |

| Figure 21. | Pin input voltage                                                                    |     |

| Figure 22. | Power supply scheme                                                                  |     |

| Figure 23. | Current consumption measurement scheme                                               |     |

| Figure 24. | External capacitor C <sub>EXT</sub>                                                  |     |

| Figure 25. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/backup RAM OFF)         |     |

| Figure 26. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/backup RAM ON)          |     |

| Figure 27. | High-speed external clock source AC timing diagram                                   |     |

| Figure 28. | Low-speed external clock source AC timing diagram                                    |     |

| Figure 29. | Typical application with an 8 MHz crystal                                            |     |

| Figure 30. | Typical application with a 32.768 kHz crystal                                        |     |

| Figure 31. | ACCHSI accuracy versus temperature                                                   |     |

| Figure 32. | ACC <sub>I SI</sub> versus temperature                                               |     |

| Figure 33. | PLL output clock waveforms in center spread mode                                     |     |

| Figure 34. | PLL output clock waveforms in down spread mode                                       |     |

| Figure 35. | FT I/O input characteristics                                                         |     |

| Figure 36. | I/O AC characteristics definition                                                    |     |

| Figure 37. | Recommended NRST pin protection                                                      |     |

| Figure 38. | SPI timing diagram - slave mode and CPHA = 0                                         |     |

| Figure 39. | SPI timing diagram - slave mode and CPHA = 1                                         |     |

| Figure 40. | SPI timing diagram - master mode                                                     |     |

| Figure 41. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>              | 148 |

| Figure 42. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>             | 148 |

| Figure 43  | SAI master timing waveforms                                                          | 150 |

### 3.11 Chrom-ART Accelerator™ (DMA2D)

The Chrom-Art Accelerator™ (DMA2D) is a graphic accelerator which offers advanced bit blitting, row data copy and pixel format conversion. It supports the following functions:

- Rectangle filling with a fixed color

- Rectangle copy

- Rectangle copy with pixel format conversion

- Rectangle composition with blending and pixel format conversion.

Various image format coding are supported, from indirect 4bpp color mode up to 32bpp direct color. It embeds dedicated memory to store color lookup tables.

An interrupt can be generated when an operation is complete or at a programmed watermark.

All the operations are fully automatized and are running independently from the CPU or the DMAs.

### 3.12 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 91 maskable interrupt channels plus the 16 interrupt lines of the Cortex<sup>®</sup>-M4 with FPU core.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

# 3.13 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 168 GPIOs can be connected to the 16 external interrupt lines.

# 3.14 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy over the full temperature range. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is

### 3.35 Digital camera interface (DCMI)

The devices embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbyte/s at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

### 3.36 Cryptographic acceleration

The devices embed a cryptographic accelerator. This cryptographic accelerator provides a set of hardware acceleration for the advanced cryptographic algorithms usually needed to provide confidentiality, authentication, data integrity and non repudiation when exchanging messages with a peer.

These algorithms consists of:

**Encryption/Decryption**

- DES/TDES (data encryption standard/triple data encryption standard): ECB (electronic codebook) and CBC (cipher block chaining) chaining algorithms, 64-, 128- or 192-bit key

- AES (advanced encryption standard): ECB, CBC, GCM, CCM, and CTR (counter mode) chaining algorithms, 128, 192 or 256-bit key

Universal hash

- SHA-1 and SHA-2 (secure hash algorithms)

- MD5

- HMAC

The cryptographic accelerator supports DMA request generation.

# 3.37 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

### 3.38 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

### 3.42 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 3.43 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F43x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

Table 9. Legend/abbreviations used in the pinout table

| Name                 | Abbreviation                                                     | Definition                                                                                         |  |  |  |  |  |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin name             |                                                                  | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |

|                      | S Supply pin                                                     |                                                                                                    |  |  |  |  |  |

| Pin type             | I                                                                | Input only pin                                                                                     |  |  |  |  |  |

|                      | I/O                                                              | Input / output pin                                                                                 |  |  |  |  |  |

|                      | FT 5 V tolerant I/O                                              |                                                                                                    |  |  |  |  |  |

| I/O structure        | TTa                                                              | 3.3 V tolerant I/O directly connected to ADC                                                       |  |  |  |  |  |

| 1/O structure        | В                                                                | Dedicated BOOT0 pin                                                                                |  |  |  |  |  |

|                      | RST                                                              | Bidirectional reset pin with weak pull-up resistor                                                 |  |  |  |  |  |

| Notes                | Unless otherwise                                                 | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |

| Alternate functions  | Functions selected                                               | d through GPIOx_AFR registers                                                                      |  |  |  |  |  |

| Additional functions | Functions directly selected/enabled through peripheral registers |                                                                                                    |  |  |  |  |  |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions

|         |         |          | Pin nu   | ımbeı   | r        |         |          |                                                      |          |                 |       |                                                                           |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                       | Additional<br>functions |

| 1       | 1       | B2       | A2       | 1       | D8       | 1       | А3       | PE2                                                  | I/O      | FT              | -     | TRACECLK, SPI4_SCK, SAI1_MCLK_A, ETH_MII_TXD3, FMC_A23, EVENTOUT          | -                       |

| 2       | 2       | C1       | A1       | 2       | C10      | 2       | A2       | PE3                                                  | I/O      | FT              | -     | TRACED0,<br>SAI1_SD_B,FMC_A19,<br>EVENTOUT                                | -                       |

| 3       | 3       | C2       | B1       | 3       | B11      | 3       | A1       | PE4                                                  | I/O      | FT              | -     | TRACED1, SPI4_NSS,<br>SAI1_FS_A, FMC_A20,<br>DCMI_D4, LCD_B0,<br>EVENTOUT | -                       |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

|         |         |          | Pin nı   | ımbeı   | r        |         |          |                                                      |          |                 |       |                                                                                                |                             |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|------------------------------------------------------------------------------------------------|-----------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                            | Additional functions        |

| -       | -       | M1       | L4       | 48      | N11      | ı       | L5       | BYPASS_<br>REG                                       | I        | FT              | -     | -                                                                                              | -                           |

| 28      | 39      | J11      | K4       | 49      | J8       | 52      | K5       | $V_{DD}$                                             | S        | -               | -     | -                                                                                              | -                           |

| 29      | 40      | N2       | N4       | 50      | M10      | 53      | N4       | PA4                                                  | I/O      | ТТа             | (5)   | SPI1_NSS, SPI3_NSS/I2S3_WS, USART2_CK, OTG_HS_SOF, DCMI_HSYNC, LCD_VSYNC, EVENTOUT             | ADC12_<br>IN4 /DAC_<br>OUT1 |

| 30      | 41      | M3       | P4       | 51      | M9       | 54      | P4       | PA5                                                  | I/O      | ТТа             | (5)   | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK,<br>OTG_HS_ULPI_CK,<br>EVENTOUT                   | ADC12_<br>IN5/DAC_<br>OUT2  |

| 31      | 42      | N3       | P3       | 52      | N10      | 55      | P3       | PA6                                                  | I/O      | FT              | (5)   | TIM1_BKIN, TIM3_CH1, TIM8_BKIN, SPI1_MISO, TIM13_CH1, DCMI_PIXCLK, LCD_G2, EVENTOUT            | ADC12_<br>IN6               |

| 32      | 43      | K4       | R3       | 53      | L8       | 56      | R3       | PA7                                                  | I/O      | FT              | (5)   | TIM1_CH1N, TIM3_CH2, TIM8_CH1N, SPI1_MOSI, TIM14_CH1, ETH_MII_RX_DV/ETH_ RMII_CRS_DV, EVENTOUT | ADC12_<br>IN7               |

| 33      | 44      | L4       | N5       | 54      | M8       | 57      | N5       | PC4                                                  | I/O      | FT              | (5)   | ETH_MII_RXD0/ETH_<br>RMII_RXD0,<br>EVENTOUT                                                    | ADC12_<br>IN14              |

| 34      | 45      | M4       | P5       | 55      | N9       | 58      | P5       | PC5                                                  | I/O      | FT              | (5)   | ETH_MII_RXD1/ETH_<br>RMII_RXD1,<br>EVENTOUT                                                    | ADC12_<br>IN15              |

| -       | -       | -        | -        | -       | J7       | 59      | L7       | $V_{DD}$                                             | S        | -               | -     | -                                                                                              | -                           |

| -       | -       | -        | -        | -       | -        | 60      | L6       | VSS                                                  | S        | -               | -     | -                                                                                              | -                           |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

|         |         |          | Pin nu   | ımber   | •        |         |          | -                                                    |          |                 |       |                                                                                         |                      |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------|----------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                     | Additional functions |

| -       | 91      | G11      | J15      | 110     | G4       | 133     | J15      | PG6                                                  | I/O      | FT              | -     | FMC_INT2, DCMI_D12,<br>LCD_R7, EVENTOUT                                                 | -                    |

| -       | 92      | G12      | J14      | 111     | H1       | 134     | J14      | PG7                                                  | I/O      | FT              | ı     | USART6_CK,<br>FMC_INT3, DCMI_D13,<br>LCD_CLK, EVENTOUT                                  | -                    |

| -       | 93      | F13      | H14      | 112     | G2       | 135     | H14      | PG8                                                  | I/O      | FT              | -     | SPI6_NSS, USART6_RTS, ETH_PPS_OUT, FMC_SDCLK, EVENTOUT                                  | -                    |

| -       | 94      | J7       | G12      | 113     | D2       | 136     | G10      | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                       | -                    |

| -       | 95      | E6       | H13      | 114     | G1       | 137     | G11      | $V_{DD}$                                             | S        |                 | -     | -                                                                                       | -                    |

| 63      | 96      | F9       | H15      | 115     | F2       | 138     | H15      | PC6                                                  | I/O      | FT              | -     | TIM3_CH1, TIM8_CH1,                                                                     | -                    |

| 64      | 97      | F10      | G15      | 116     | F3       | 139     | G15      | PC7                                                  | I/O      | FT              | -     | TIM3_CH2, TIM8_CH2,<br>I2S3_MCK,<br>USART6_RX,<br>SDIO_D7, DCMI_D1,<br>LCD_G6, EVENTOUT | -                    |

| 65      | 98      | F11      | G14      | 117     | E4       | 140     | G14      | PC8                                                  | I/O      | FT              | -     | TIM3_CH3, TIM8_CH3,<br>USART6_CK,<br>SDIO_D0, DCMI_D2,<br>EVENTOUT                      | -                    |

| 66      | 99      | F12      | F14      | 118     | E3       | 141     | F14      | PC9                                                  | I/O      | FT              | -     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, SDIO_D1,<br>DCMI_D3, EVENTOUT       | -                    |

| 67      | 100     | E13      | F15      | 119     | F1       | 142     | F15      | PA8                                                  | I/O      | FT              | -     | MCO1, TIM1_CH1,<br>I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF,<br>LCD_R6, EVENTOUT           | -                    |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

|         |         |           | Pin nu   |         |          |         |          | •                                                    |          |                 |       | deminitions (continued                                                                        | ,                       |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 82      | 115     | C9        | C12      | 143     | C4       | 165     | C12      | PD1                                                  | I/O      | FT              | -     | CAN1_TX, FMC_D3,<br>EVENTOUT                                                                  | -                       |

| 83      | 116     | В9        | D12      | 144     | A3       | 166     | D12      | PD2                                                  | I/O      | FT              | ı     | TIM3_ETR, UART5_RX, SDIO_CMD, DCMI_D11, EVENTOUT                                              | -                       |

| 84      | 117     | A9        | D11      | 145     | B4       | 167     | C11      | PD3                                                  | I/O      | FT              | -     | SPI2_SCK/I2S2_CK,<br>USART2_CTS,<br>FMC_CLK, DCMI_D5,<br>LCD_G7, EVENTOUT                     | -                       |

| 85      | 118     | D8        | D10      | 146     | B5       | 168     | D11      | PD4                                                  | I/O      | FT              | -     | USART2_RTS,<br>FMC_NOE,<br>EVENTOUT                                                           | -                       |

| 86      | 119     | C8        | C11      | 147     | A4       | 169     | C10      | PD5                                                  | I/O      | FT              | -     | USART2_TX,<br>FMC_NWE,<br>EVENTOUT                                                            | -                       |

| -       | 120     | ı         | D8       | 148     | -        | 170     | F8       | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 121     | D6        | C8       | 149     | C5       | 171     | E9       | $V_{DD}$                                             | S        |                 | -     | -                                                                                             | -                       |

| 87      | 122     | В8        | B11      | 150     | F4       | 172     | B11      | PD6                                                  | I/O      | FT              | -     | SPI3_MOSI/I2S3_SD,<br>SAI1_SD_A,<br>USART2_RX,<br>FMC_NWAIT,<br>DCMI_D10, LCD_B2,<br>EVENTOUT | -                       |

| 88      | 123     | A8        | A11      | 151     | A5       | 173     | A11      | PD7                                                  | I/O      | FT              | -     | USART2_CK,<br>FMC_NE1/FMC_NCE2,<br>EVENTOUT                                                   | -                       |

| -       | -       | -         | -        | -       | -        | 174     | B10      | PJ12                                                 | I/O      | FT              | -     | LCD_B0, EVENTOUT                                                                              | -                       |

| -       | -       | 1         | -        | -       | 1        | 175     | В9       | PJ13                                                 | I/O      | FT              | -     | LCD_B1, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 176     | C9       | PJ14                                                 | I/O      | FT              | -     | LCD_B2, EVENTOUT                                                                              | -                       |

| -       | -       | 1         | -        | -       | -        | 177     | D10      | PJ15                                                 | I/O      | FT              | -     | LCD_B3, EVENTOUT                                                                              | -                       |

| -       | 124     | NC<br>(2) | C10      | 152     | E5       | 178     | D9       | PG9                                                  | I/O      | FT              | -     | USART6_RX,<br>FMC_NE2/FMC_NCE3,<br>DCMI_VSYNC <sup>(8)</sup> ,<br>EVENTOUT                    | -                       |

Table 13. STM32F437xx and STM32F439xx register boundary addresses

| Bus       | Boundary address          | Peripheral                     |

|-----------|---------------------------|--------------------------------|

|           | 0xE00F FFFF - 0xFFFF FFFF | Reserved                       |

| Cortex-M4 | 0xE000 0000 - 0xE00F FFFF | Cortex-M4 internal peripherals |

|           | 0xD000 0000 - 0xDFFF FFFF | FMC bank 6                     |

|           | 0xC000 0000 - 0xCFFF FFFF | FMC bank 5                     |

|           | 0xA000 1000 - 0xBFFF FFFF | Reserved                       |

| AHB3      | 0xA000 0000- 0xA000 0FFF  | FMC control register           |

| ALIDO     | 0x9000 0000 - 0x9FFF FFFF | FMC bank 4                     |

|           | 0x8000 0000 - 0x8FFF FFFF | FMC bank 3                     |

|           | 0x7000 0000 - 0x7FFF FFFF | FMC bank 2                     |

|           | 0x6000 0000 - 0x6FFF FFFF | FMC bank 1                     |

|           | 0x5006 0C00- 0x5FFF FFFF  | Reserved                       |

|           | 0x5006 0800 - 0X5006 0BFF | RNG                            |

|           | 0x5006 0400 - 0X5006 07FF | HASH                           |

|           | 0x5006 0000 - 0X5006 03FF | CRYP                           |

| AHB2      | 0x5005 0400 - X5006 07FF  | Reserved                       |

|           | 0x5005 0000 - 0X5005 03FF | DCMI                           |

|           | 0x5004 0000- 0x5004 FFFF  | Reserved                       |

|           | 0x5000 0000 - 0X5003 FFFF | USB OTG FS                     |

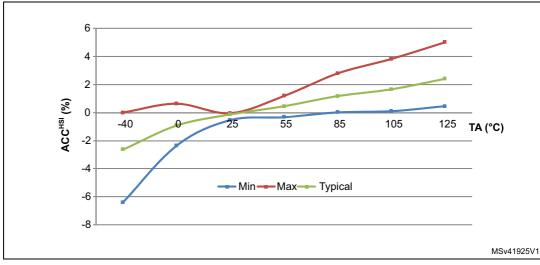

Figure 31. ACCHSI accuracy versus temperature

1. Guaranteed by characterization results.

### Low-speed internal (LSI) RC oscillator

Table 42. LSI oscillator characteristics (1)

| Symbol                              | Parameter                        | Min | Тур | Max | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> (3)            | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

- 1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by characterization results.

- 3. Guaranteed by design.

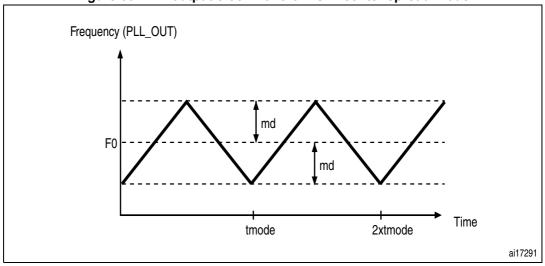

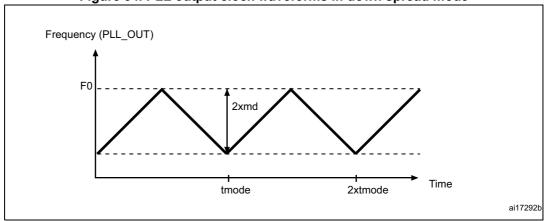

*Figure 33* and *Figure 34* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is  $f_{PLL\_OUT}$  nominal.

$T_{\text{mode}}$  is the modulation period.

md is the modulation depth.

Figure 33. PLL output clock waveforms in center spread mode

Figure 34. PLL output clock waveforms in down spread mode

Table 48. Flash memory programming (continued)

| Symbol          | Parameter           | Conditions                                 | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-----------------|---------------------|--------------------------------------------|--------------------|-----|--------------------|------|

|                 |                     | Program/erase parallelism<br>(PSIZE) = x 8 | -                  | 16  | 32                 |      |

| t <sub>BE</sub> | Bank erase time     | Program/erase parallelism (PSIZE) = x 16   | -                  | 11  | 22                 | s    |

|                 |                     | Program/erase parallelism (PSIZE) = x 32   | -                  | 8   | 16                 |      |

|                 |                     | 32-bit program operation                   | 2.7                | -   | 3.6                | V    |

| $V_{prog}$      | Programming voltage | 16-bit program operation                   | 2.1                | -   | 3.6                | V    |

|                 |                     | 8-bit program operation                    | 1.7                | -   | 3.6                | V    |

- 1. Guaranteed by characterization results.

- 2. The maximum programming time is measured after 100K erase operations.

Table 49. Flash memory programming with V<sub>PP</sub>

| Symbol                  | Parameter                                               | Conditions                                 | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------------|---------------------------------------------------------|--------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>       | Double word programming                                 |                                            | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time                               | $T_A = 0 \text{ to } +40 ^{\circ}\text{C}$ | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time                               | V <sub>DD</sub> = 3.3 V                    | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time                              | $V_{PP} = 8.5 \text{ V}$                   | -                  | 875 | -                  |      |

| t <sub>ME</sub>         | Mass erase time                                         |                                            | -                  | 6.9 | -                  | S    |

| t <sub>BE</sub>         | Bank erase time                                         |                                            | -                  | 6.9 | -                  | S    |

| V <sub>prog</sub>       | Programming voltage                                     |                                            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>         | V <sub>PP</sub> voltage range                           |                                            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>         | Minimum current sunk on the V <sub>PP</sub> pin         |                                            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> (3)    | Cumulative time during which V <sub>PP</sub> is applied |                                            | -                  | -   | 1                  | hour |

- 1. Guaranteed by design.

- 2. The maximum programming time is measured after 100K erase operations.

- 3.  $V_{PP}$  should only be connected during programming/erasing.

#### 6.3.16 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of - 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 55.

Table 55. I/O current injection susceptibility<sup>(1)</sup>

|                  | Description                                                                                                  | Functional s       |                    |      |

|------------------|--------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           |                                                                                                              | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                | - 0                | NA                 |      |

|                  | Injected current on NRST pin                                                                                 | - 0                | NA                 |      |

| I <sub>INJ</sub> | Injected current on PA0, PA1, PA2, PA3, PA6, PA7, PB0, PC0, PC1, PC2, PC3, PC4, PC5, PH1, PH2, PH3, PH4, PH5 | - 0                | NA                 | mA   |

|                  | Injected current on TTa pins: PA4 and PA5                                                                    | - 0                | +5                 |      |

|                  | Injected current on any other FT pin                                                                         | - 5                | NA                 |      |

<sup>1.</sup> NA = not applicable.

Note: It is recomme

It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

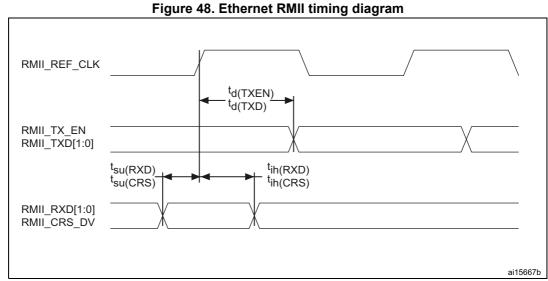

Table 72 gives the list of Ethernet MAC signals for the RMII and Figure 48 shows the corresponding timing diagram.

Table 72. Dynamics characteristics: Ethernet MAC signals for RMII<sup>(1)</sup>

| Symbol               | Parameter                        | Condition                        | Min | Тур  | Max  | Unit |

|----------------------|----------------------------------|----------------------------------|-----|------|------|------|

| t <sub>su(RXD)</sub> | Receive data setup time          |                                  | 1.5 | -    | -    |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1.71 V < V <sub>DD</sub> < 3.6 V | 0   | -    | -    |      |

| t <sub>su(CRS)</sub> | Carrier sense setup time         | 1.71 V \ V <sub>DD</sub> \ 3.0 V | 1   | -    | -    |      |

| t <sub>ih(CRS)</sub> | Carrier sense hold time          |                                  | 1   | -    | -    | ns   |

| +                    | Transmit enable valid delay time | 2.7 V < V <sub>DD</sub> < 3.6 V  | 8   | 10.5 | 12   | 115  |

| t <sub>d(TXEN)</sub> |                                  | 1.71 V < V <sub>DD</sub> < 3.6 V | 8   | 10.5 | 14   |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 2.7 V < V <sub>DD</sub> < 3.6 V  | 8   | 11   | 12.5 |      |

|                      |                                  | 1.71 V < V <sub>DD</sub> < 3.6 V | 8   | 11   | 14.5 |      |

<sup>1.</sup> Guaranteed by characterization results.

Table 73 gives the list of Ethernet MAC signals for MII and Figure 48 shows the corresponding timing diagram.

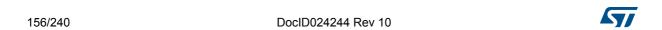

Figure 55. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

Table 86. Asynchronous non-multiplexed SRAM/PSRAM/NOR - read timings  $^{(1)(2)}$

| Symbol                    | Parameter                             | Min                      | Max                      | Unit |  |

|---------------------------|---------------------------------------|--------------------------|--------------------------|------|--|

| $t_{w(NE)}$               | FMC_NE low time                       | 2T <sub>HCLK</sub> - 0.5 | 2 T <sub>HCLK</sub> +0.5 | ns   |  |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low            | 0                        | 1                        | ns   |  |

| $t_{w(NOE)}$              | FMC_NOE low time                      | 2T <sub>HCLK</sub>       | 2T <sub>HCLK</sub> + 0.5 | ns   |  |

| $t_{h(NE\_NOE)}$          | FMC_NOE high to FMC_NE high hold time | 0                        | -                        | ns   |  |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid            | -                        | 2                        | ns   |  |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high  | 0                        | -                        | ns   |  |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid           | -                        | 2                        | ns   |  |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high   | 0                        | -                        | ns   |  |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        | ns   |  |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time      | T <sub>HCLK</sub> +2     | -                        | ns   |  |

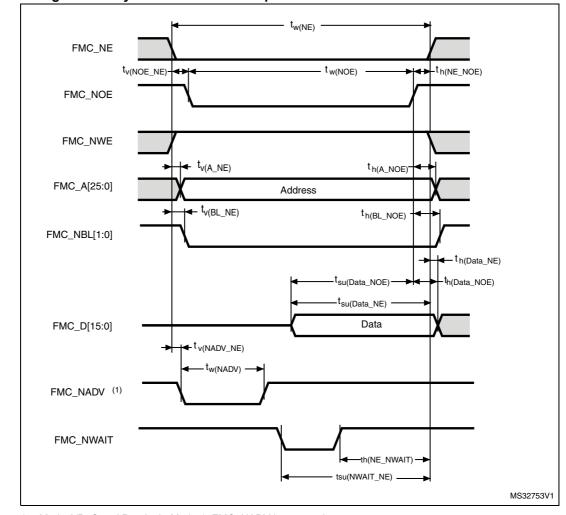

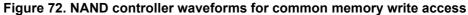

Figure 71. NAND controller waveforms for common memory read access

Table 100. Switching characteristics for NAND Flash read cycles<sup>(1)</sup>

| Symbol                  | Parameter                                  | Min                      | Max                      | Unit |

|-------------------------|--------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> - 0.5 | 4T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 9                        | -                        | ns   |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 0                        | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                        | 3T <sub>HCLK</sub> - 0.5 | ns   |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> - 2   | -                        | ns   |

<sup>1.</sup>  $C_L = 30 pF$ .

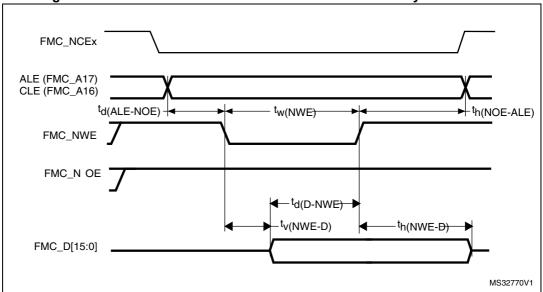

Figure 87. LQPF144- 144-pin,20 x 20 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

**47**/

Table 124. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 24-Apr-2014 | 5        | Changed SVGA (800x600) into XGA1024x768) on cover page and in Section 3.10: LCD-TFT controller (available only on STM32F439xx). Added DCMI_VSYNC alternate function on PG9 and updated note 6. in Table 10: STM32F437xx and STM32F439xx pin and ball definitions and Table 12: STM32F437xx and STM32F439xx alternate function mapping. Added note 2.belowFigure 16: STM32F43x UFBGA169 ballout.  Updated Section 3.18.2: Regulator OFF.  Updated signal corresponding to pin L5 in Figure 12: STM32F43x WLCSP143 ballout.  Updated Table 53: ESD absolute maximum ratings.  Updated V <sub>IH</sub> in Table 56: I/O static characteristics. Added condition V <sub>DD</sub> >1.7 V in Table 58: I/O AC characteristics.  Removed notes 3 and 4 in Table 62: SPI dynamic characteristics. Added ACC <sub>HSE</sub> in Table 39: HSE 4-26 MHz oscillator characteristics and ACC <sub>LSE</sub> in Table 40: LSE oscillator characteristics (fLSE = 32.768 kHz).  Removed note 3 in Table 80: Temperature sensor characteristics. Added Figure 82: LQFP100 marking example (package top view), Figure 85: WLCSP143 marking example (package top view), Figure 88: LQFP144 marking example (package top view), Figure 91: LQFP176 marking (package top view), Figure 94: LQFP208 marking example (package top view) and Figure 100: UFBGA176+25 marking example (package top view). Added Appendix A: Recommendations when using internal reset OFF and removed Internal reset OFF hardware connection appendix. |  |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved