# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437vgt7               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 180 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 180 MHz while the maximum frequency of the high-speed APB domains is 90 MHz. The maximum allowed frequency of the low-speed APB domain is 45 MHz.

The devices embed a dedicated PLL (PLLI2S) and PLLSAI which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

### 3.15 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface. Refer to application note AN2606 for details.

### 3.16 Power supply schemes

- $V_{DD}$  = 1.7 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Note: V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

## 3.17 **Power supply supervisor**

#### 3.17.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other package, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is

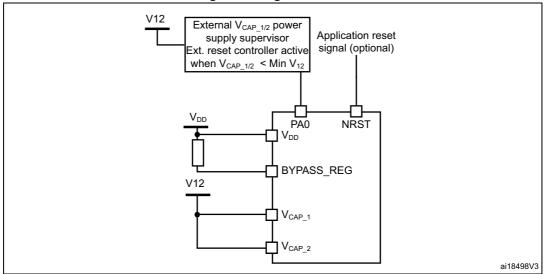

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below V<sub>12</sub> minimum value and V<sub>DD</sub> is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of  $V_{12}$  depends on the maximum frequency targeted in the application (see Table 17: General operating conditions).

#### 3.18.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table                                                       | 4. Regulator ON/                            |                                             | reset ON/OFF ava                        | anability                                                        |

|-------------------------------------------------------------|---------------------------------------------|---------------------------------------------|-----------------------------------------|------------------------------------------------------------------|

| Package                                                     | Regulator ON                                | Regulator OFF                               | Internal reset ON                       | Internal reset OFF                                               |

| LQFP100                                                     | Yes                                         | No                                          | Yes                                     | No                                                               |

| LQFP144,<br>LQFP208                                         | 165                                         | NO                                          |                                         | Yes                                                              |

| WLCSP143,<br>LQFP176,<br>UFBGA169,<br>UFBGA176,<br>TFBGA216 | Yes<br>BYPASS_REG set<br>to V <sub>SS</sub> | Yes<br>BYPASS_REG set<br>to V <sub>DD</sub> | Yes<br>PDR_ON set to<br>V <sub>DD</sub> | PDR_ON<br>connected to an<br>external power<br>supply supervisor |

#### Table 4. Regulator ON/OFF and internal reset ON/OFF availability

## 3.19 Real-time clock (RTC), backup SRAM and backup registers

The backup domain includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are performed automatically. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes. The sub-seconds value is also available in binary format.

It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

The 4-Kbyte backup SRAM is an EEPROM-like memory area. It can be used to store data which need to be retained in VBAT and standby mode. This memory area is disabled by default to minimize power consumption (see *Section 3.20: Low-power modes*). It can be enabled by software.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.20: Low-power modes).

## 3.30 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 3.31 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

The devices include the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F4xx reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

## 3.32 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive

|         |         |          | Pin nu   | ımbei   | r        |         |          |                                                      |          |    |   |                                                                                           |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|----|---|-------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type |    |   | Alternate functions                                                                       | Additional<br>functions |

| 49      | 71      | N9       | M10      | 81      | N2       | 92      | L11      | V <sub>CAP_1</sub>                                   | S        | -  | - | -                                                                                         | -                       |

| -       | I       | -        | -        | -       | H2       | 93      | K9       | V <sub>SS</sub>                                      | S        | -  | 1 | -                                                                                         | -                       |

| 50      | 72      | F8       | N10      | 82      | J6       | 94      | L10      | V <sub>DD</sub>                                      | S        | -  | I | -                                                                                         | -                       |

| -       | I       | -        | -        | -       | -        | 95      | M14      | PJ5                                                  | I/O      | -  | I | LCD_R6, EVENTOUT                                                                          | -                       |

| -       | -       | N10      | M11      | 83      | -        | 96      | P13      | PH6                                                  | I/O      | FT | - | I2C2_SMBA,<br>SPI5_SCK,<br>TIM12_CH1,<br>ETH_MII_RXD2,<br>FMC_SDNE1,<br>DCMI_D8, EVENTOUT | -                       |

| -       | -       | M10      | N12      | 84      | -        | 97      | N13      | PH7                                                  | I/O      | FT | - | I2C3_SCL, SPI5_MISO,<br>ETH_MII_RXD3,<br>FMC_SDCKE1,<br>DCMI_D9, EVENTOUT                 | -                       |

| -       | -       | L10      | M12      | 85      | -        | 98      | P14      | PH8                                                  | I/O      | FT | - | I2C3_SDA, FMC_D16,<br>DCMI_HSYNC,<br>LCD_R2, EVENTOUT                                     | -                       |

| -       | -       | K10      | M13      | 86      | -        | 99      | N14      | PH9                                                  | I/O      | FT | - | I2C3_SMBA,<br>TIM12_CH2,<br>FMC_D17, DCMI_D0,<br>LCD_R3, EVENTOUT                         | -                       |

| -       | -       | N11      | L13      | 87      | -        | 100     | P15      | PH10                                                 | I/O      | FT | - | TIM5_CH1, FMC_D18,<br>DCMI_D1, LCD_R4,<br>EVENTOUT                                        | -                       |

| -       | -       | M11      | L12      | 88      | -        | 101     | N15      | PH11                                                 | I/O      | FT | - | TIM5_CH2, FMC_D19,<br>DCMI_D2, LCD_R5,<br>EVENTOUT                                        | -                       |

| -       | -       | L11      | K12      | 89      | -        | 102     | M15      | PH12                                                 | I/O      | FT | - | TIM5_CH3, FMC_D20,<br>DCMI_D3, LCD_R6,<br>EVENTOUT                                        | -                       |

| -       | I       | E7       | H12      | 90      | -        | -       | K10      | V <sub>SS</sub>                                      | S        | -  | - | -                                                                                         | -                       |

| -       | -       | H8       | J12      | 91      | -        | 103     | K11      | V <sub>DD</sub>                                      | S        | -  | - | -                                                                                         | -                       |

| Table 10. | STM32F437xx and | STM32F439xx pin | and ball definitions | (continued) |

|-----------|-----------------|-----------------|----------------------|-------------|

|           |                 |                 |                      |             |

|         |         |          | Pin nu   | Imber   | -        |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| -       | 91      | G11      | J15      | 110     | G4       | 133     | J15      | PG6                                                  | I/O      | FT              | -     | FMC_INT2, DCMI_D12,<br>LCD_R7, EVENTOUT                                                       | -                       |

| -       | 92      | G12      | J14      | 111     | H1       | 134     | J14      | PG7                                                  | I/O      | FT              | -     | USART6_CK,<br>FMC_INT3, DCMI_D13,<br>LCD_CLK, EVENTOUT                                        | -                       |

| -       | 93      | F13      | H14      | 112     | G2       | 135     | H14      | PG8                                                  | I/O      | FT              | -     | SPI6_NSS,<br>USART6_RTS,<br>ETH_PPS_OUT,<br>FMC_SDCLK,<br>EVENTOUT                            | -                       |

| -       | 94      | J7       | G12      | 113     | D2       | 136     | G10      | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 95      | E6       | H13      | 114     | G1       | 137     | G11      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| 63      | 96      | F9       | H15      | 115     | F2       | 138     | H15      | PC6                                                  | I/O      | FT              | -     | TIM3_CH1, TIM8_CH1,<br>I2S2_MCK,<br>USART6_TX,<br>SDIO_D6, DCMI_D0,<br>LCD_HSYNC,<br>EVENTOUT | -                       |

| 64      | 97      | F10      | G15      | 116     | F3       | 139     | G15      | PC7                                                  | I/O      | FT              | -     | TIM3_CH2, TIM8_CH2,<br>I2S3_MCK,<br>USART6_RX,<br>SDIO_D7, DCMI_D1,<br>LCD_G6, EVENTOUT       | -                       |

| 65      | 98      | F11      | G14      | 117     | E4       | 140     | G14      | PC8                                                  | I/O      | FT              | -     | TIM3_CH3, TIM8_CH3,<br>USART6_CK,<br>SDIO_D0, DCMI_D2,<br>EVENTOUT                            | -                       |

| 66      | 99      | F12      | F14      | 118     | E3       | 141     | F14      | PC9                                                  | I/O      | FT              | -     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, SDIO_D1,<br>DCMI_D3, EVENTOUT             | -                       |

| 67      | 100     | E13      | F15      | 119     | F1       | 142     | F15      | PA8                                                  | I/O      | FT              | -     | MCO1, TIM1_CH1,<br>I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF,<br>LCD_R6, EVENTOUT                 | -                       |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

|         |         |          | Pin nu   | ımbeı   | •        |         |          |                                                      |                                      |    |       |                                                                                                                |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|--------------------------------------|----|-------|----------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type<br>I / O structure<br>Notes |    | Notes | Alternate functions                                                                                            | Additional<br>functions |

| 96      | 140     | C4       | B4       | 168     | В9       | 199     | B4       | PB9                                                  | I/O                                  | FT | -     | TIM4_CH4,<br>TIM11_CH1,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS,<br>CAN1_TX, SDIO_D5,<br>DCMI_D7, LCD_B7,<br>EVENTOUT | -                       |

| 97      | 141     | B4       | A4       | 169     | B10      | 200     | A6       | PE0                                                  | I/O                                  | FT | -     | TIM4_ETR,<br>UART8_RX,<br>FMC_NBL0, DCMI_D2,<br>EVENTOUT                                                       | -                       |

| 98      | 142     | A4       | A3       | 170     | A10      | 201     | A5       | PE1                                                  | I/O                                  | FT | -     | UART8_Tx,<br>FMC_NBL1, DCMI_D3,<br>EVENTOUT                                                                    | -                       |

| 99      | -       | F5       | D5       | -       | -        | 202     | F6       | $V_{SS}$                                             | S                                    |    | -     |                                                                                                                | -                       |

| -       | 143     | C3       | C6       | 171     | A11      | 203     | E5       | PDR_ON                                               | S                                    |    | -     |                                                                                                                | -                       |

| 100     | 144     | K6       | C5       | 172     | D7       | 204     | E7       | V <sub>DD</sub>                                      | S                                    |    | -     |                                                                                                                | -                       |

| -       | -       | В3       | D4       | 173     | -        | 205     | C3       | Pl4                                                  | I/O                                  | FT | -     | TIM8_BKIN,<br>FMC_NBL2, DCMI_D5,<br>LCD_B4, EVENTOUT                                                           | -                       |

| -       | -       | A3       | C4       | 174     | -        | 206     | D3       | PI5                                                  | I/O                                  | FT | -     | TIM8_CH1,<br>FMC_NBL3,<br>DCMI_VSYNC,<br>LCD_B5, EVENTOUT                                                      | -                       |

| -       | -       | A2       | C3       | 175     | -        | 207     | D6       | Pl6                                                  | I/O                                  | FT | -     | TIM8_CH2, FMC_D28,<br>DCMI_D6, LCD_B6,<br>EVENTOUT                                                             | -                       |

| -       | -       | B1       | C2       | 176     | -        | 208     | D4       | PI7                                                  | I/O                                  | FT | -     | TIM8_CH3, FMC_D29,<br>DCMI_D7, LCD_B7,<br>EVENTOUT                                                             | -                       |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

1. Function availability depends on the chosen device.

2. NC (not-connected) pins are not bonded. They must be configured by software to output push-pull and forced to 0 in the output data register to avoid extra current consumption in low power modes.

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

These I/Os must not be used as a current source (e.g. to drive an LED).

51

| ` |

|---|

|   |

|   |

|   |

DocID024244 Rev 10

83/240

|         |      | AF0 | AF1    | AF2      | AF3              | AF4          | AF5                | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11              | AF12                 | AF13        | AF14          | AF15         |

|---------|------|-----|--------|----------|------------------|--------------|--------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|-------------------|----------------------|-------------|---------------|--------------|

| P       | Port |     | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11 | l2C1/<br>2/3 | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ETH               | FMC/SDIO<br>/OTG2_FS | DCMI        | LCD           | SYS          |

|         | PI7  | -   | -      | -        | TIM8_<br>CH3     | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | FMC_D29              | DCMI_<br>D7 | LCD_B7        | EVEN<br>TOUT |

|         | PI8  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | -             | EVEN<br>TOUT |

|         | PI9  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | CAN1_RX                        | -                       | -                 | FMC_D30              | -           | LCD_<br>VSYNC | EVEN<br>TOUT |

|         | PI10 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>RX_ER | FMC_D31              | -           | LCD_<br>HSYNC | EVEN<br>TOUT |

| Port I  | PI11 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | OTG_HS_<br>ULPI_DIR     | -                 | -                    | -           | -             | EVEN<br>TOUT |

|         | PI12 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_<br>HSYNC | EVEN<br>TOUT |

|         | PI13 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_<br>VSYNC | EVEN<br>TOUT |

|         | PI14 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_<br>CLK   | EVEN<br>TOUT |

|         | PI15 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R0        | EVEN<br>TOUT |

|         | PJ0  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R1        | EVEN<br>TOUT |

|         | PJ1  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R2        | EVEN<br>TOUT |

|         | PJ2  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R3        | EVEN<br>TOUT |

| Port J  | PJ3  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R4        | EVEN<br>TOUT |

| 1 OIT 5 | PJ4  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R5        | EVEN<br>TOUT |

|         | PJ5  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R6        | EVEN<br>TOUT |

|         | PJ6  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_R7        | EVEN<br>TOUT |

|         | PJ7  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -                 | -                    | -           | LCD_G0        | EVEN<br>TOUT |

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

DocID024244 Rev 10

84/240

1. The DCMI\_VSYNC alternate function on PG9 is only available on silicon revision 3.

| τ        |

|----------|

| Ē        |

| -        |

| 0        |

| 2        |

| <b>T</b> |

| S        |

| a        |

|          |

| ā        |

| _        |

| σ        |

| 3        |

|          |

| Q        |

| Φ        |

| S        |

| C        |

| Ξ.       |

| -        |

| Ă        |

| <u> </u> |

| ¥        |

| <b>_</b> |

STM32F437xx and STM32F439xx

|        |      | AF0 | AF1    | AF2      | AF3              | AF4          | AF5                | AF6 | AF7 | AF8                        | AF9                            | AF10                    | AF11 | AF12                 | AF13 | AF14   | AF15         |

|--------|------|-----|--------|----------|------------------|--------------|--------------------|-----|-----|----------------------------|--------------------------------|-------------------------|------|----------------------|------|--------|--------------|

| Port   |      | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11 | l2C1/<br>2/3 | SPI1/2/<br>3/4/5/6 |     |     | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН  | FMC/SDIO<br>/OTG2_FS | DCMI | LCD    | SYS          |

|        | PJ8  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_G1 | EVEN<br>TOUT |

|        | PJ9  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_G2 | EVEN<br>TOUT |

|        | PJ10 | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_G3 | EVEN<br>TOUT |

|        | PJ11 | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_G4 | EVEN<br>TOUT |

| Port J | PJ12 | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B0 | EVEN<br>TOUT |

|        | PJ13 | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B1 | EVEN<br>TOUT |

|        | PJ14 | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B2 | EVEN<br>TOUT |

|        | PJ15 | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B3 | EVEN<br>TOUT |

|        | PK0  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_G5 | EVEN<br>TOUT |

|        | PK1  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_G6 | EVEN<br>TOUT |

|        | PK2  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_G7 | EVEN<br>TOUT |

| D. UK  | PK3  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B4 | EVEN<br>TOUT |

| Port K | PK4  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B5 | EVEN<br>TOUT |

|        | PK5  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B6 | EVEN<br>TOUT |

|        | PK6  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_B7 | EVEN<br>TOUT |

|        | PK7  | -   | -      | -        | -                | -            | -                  | -   | -   | -                          | -                              | -                       | -    | -                    | -    | LCD_DE | EVEN<br>TOUT |

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

|                 |                         |                                         |                                                  |     | Max <sup>(2)</sup>        |                           |                            |      |

|-----------------|-------------------------|-----------------------------------------|--------------------------------------------------|-----|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter               | arameter Conditions f <sub>HCLK</sub> ( | Parameter Conditions f <sub>HCLK</sub> (MHz) Typ | Тур | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                         |                                         | 180                                              | 98  | 104 <sup>(5)</sup>        | 123                       | 141 <sup>(5)</sup>         |      |

|                 |                         |                                         | 168                                              | 89  | 98 <sup>(5)</sup>         | 116                       | 133 <sup>(5)</sup>         |      |

|                 |                         |                                         | 150                                              | 75  | 84                        | 100                       | 115                        |      |

|                 |                         |                                         | 144                                              | 72  | 81                        | 96                        | 112                        |      |

|                 |                         |                                         | 120                                              | 54  | 58                        | 72                        | 85                         |      |

|                 |                         | All                                     | 90                                               | 43  | 45                        | 56                        | 66                         |      |

|                 |                         | Peripherals                             | 60                                               | 29  | 30                        | 38                        | 45                         |      |

|                 |                         | enabled <sup>(3)(4)</sup>               | 30                                               | 16  | 20                        | 34                        | 46                         |      |

|                 |                         |                                         | 25                                               | 13  | 16                        | 30                        | 43                         | -    |

|                 |                         |                                         | 16                                               | 11  | 13                        | 27                        | 39                         |      |

|                 |                         |                                         | 8                                                | 5   | 9                         | 23                        | 36                         |      |

|                 |                         | 4                                       | 4                                                | 8   | 21                        | 34                        | 1                          |      |

| 1               | Supply current in       |                                         | 2                                                | 2   | 7                         | 20                        | 33                         | mA   |

| I <sub>DD</sub> | RUN mode                |                                         | 180                                              | 44  | 47 <sup>(5)</sup>         | 69                        | 87 <sup>(5)</sup>          | ШA   |

|                 |                         |                                         | 168                                              | 41  | 45 <sup>(5)</sup>         | 66                        | 83 <sup>(5)</sup>          |      |

|                 |                         |                                         | 150                                              | 36  | 39                        | 57                        | 73                         |      |

|                 |                         |                                         | 144                                              | 33  | 37                        | 56                        | 72                         |      |

|                 |                         |                                         | 120                                              | 25  | 29                        | 43                        | 56                         |      |

|                 |                         | All                                     | 90                                               | 20  | 21                        | 32                        | 41                         | 1    |

|                 |                         | Peripherals                             | 60                                               | 14  | 15                        | 22                        | 28                         |      |

|                 | disabled <sup>(3)</sup> | 30                                      | 8                                                | 8   | 12                        | 26                        | 1                          |      |

|                 |                         |                                         | 25                                               | 7   | 7                         | 10                        | 24                         |      |

|                 |                         |                                         | 16                                               | 7   | 9                         | 22                        | 35                         |      |

|                 |                         |                                         | 8                                                | 3   | 7                         | 21                        | 34                         |      |

|                 |                         |                                         | 4                                                | 3   | 6                         | 20                        | 33                         |      |

|                 |                         |                                         | 2                                                | 2   | 6                         | 20                        | 33                         |      |

## Table 24. Typical and maximum current consumption in Run mode, code with data processing<br/>running from Flash memory (ART accelerator enabled except prefetch) or RAM<sup>(1)</sup>

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed by characterization.

3. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. Guaranteed by test in production.

#### 6.3.9 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 27*.

The characteristics given in *Table 37* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

| Symbol                                     | Parameter                                              | Conditions                       | Min         | Тур  | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|-------------|------|--------------------|------|

| Cymbol                                     | T drameter                                             | Conditions                       | WIIII       | - YP | max                | Onic |

| f <sub>HSE_ext</sub>                       | External user clock source<br>frequency <sup>(1)</sup> |                                  | 1           | -    | 50                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                    |                                  | $0.7V_{DD}$ | -    | $V_{DD}$           | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                     |                                  | $V_{SS}$    | -    | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>                 |                                  | 5           | -    | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>                |                                  | -           | -    | 10                 | 113  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>                |                                  | -           | 5    | -                  | pF   |

| $DuCy_{(HSE)}$                             | Duty cycle                                             |                                  | 45          | -    | 55                 | %    |

| ١ <sub>L</sub>                             | OSC_IN Input leakage current                           | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -           | -    | ±1                 | μA   |

Table 37. High-speed external user clock characteristics

1. Guaranteed by design.

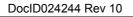

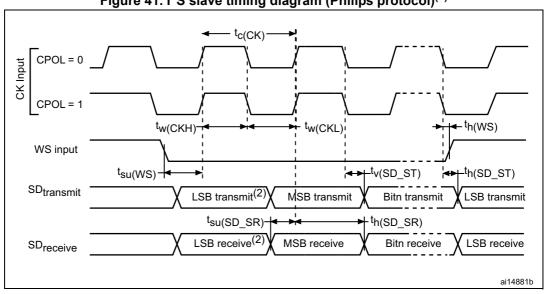

#### I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 63* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                             | Min    | Max                   | Unit |

|------------------------|--------------------------------|----------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256x8K | 256xFs <sup>(2)</sup> | MHz  |

| f                      | 129 clock froguency            | Master data: 32 bits                   | -      | 64xFs                 | MHz  |

| f <sub>CK</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -      | 64xFs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30     | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | 0      | 6                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 0      | -                     |      |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 1      | -                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 0      | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 7.5    | -                     |      |

| t <sub>su(SD_SR)</sub> |                                | Slave receiver                         | 2      | -                     |      |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 0      | -                     | ns   |

| t <sub>h(SD_SR)</sub>  |                                | Slave receiver                         | 0      | -                     |      |

| t <sub>v(SD_ST)</sub>  |                                | Slave transmitter (after enable edge)  | -      | 27                    |      |

| t <sub>h(SD_ST)</sub>  | Data output valid time         |                                        |        |                       |      |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -      | 20                    |      |

| t <sub>h(SD_MT)</sub>  | Data output hold time          | Master transmitter (after enable edge) | 2.5    | -                     |      |

| Table 63. I <sup>2</sup> S c | dynamic characteristics <sup>(1)</sup> |

|------------------------------|----------------------------------------|

|------------------------------|----------------------------------------|

1. Guaranteed by characterization results.

2. The maximum value of 256xFs is 45 MHz (APB1 maximum frequency).

Note: Refer to the I2S section of RM0090 reference manual for more details on the sampling frequency ( $F_S$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

Figure 41. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. .LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 42. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### STM32F437xx and STM32F439xx

| Symbol                          | Parameter                                                                                                                                                                | Table 85. DAC charact | Min |     | Max  | Unit     | Comments                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|------|----------|-----------------------------------------------------------------------------------------------------------------|

| Symbol                          | Parameter                                                                                                                                                                | Conditions            | win | Тур | wax  | Unit     |                                                                                                                 |

|                                 | DAC DC VDDA                                                                                                                                                              | -                     | -   | 280 | 380  | μA       | With no load, middle code<br>(0x800) on the inputs                                                              |

| I <sub>DDA</sub> <sup>(4)</sup> | current consumption in quiescent mode <sup>(3)</sup>                                                                                                                     | -                     | -   | 475 | 625  | μA       | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs |

| DNL <sup>(4)</sup>              | Differential non<br>linearity Difference<br>between two                                                                                                                  | -                     | -   | -   | ±0.5 | LSB      | Given for the DAC in 10-bit configuration.                                                                      |

|                                 | consecutive code-<br>1LSB)                                                                                                                                               | -                     | -   | -   | ±2   | LSB      | Given for the DAC in 12-bit configuration.                                                                      |

|                                 | Integral non linearity<br>(difference between                                                                                                                            | -                     | -   | -   | ±1   | LSB      | Given for the DAC in 10-bit configuration.                                                                      |

| INL <sup>(4)</sup>              | measured value at<br>Code i and the value<br>at Code i on a line<br>drawn between Code<br>0 and last Code 1023)                                                          | -                     | -   | -   | ±4   | LSB      | Given for the DAC in 12-bit configuration.                                                                      |

|                                 | Offset error                                                                                                                                                             | -                     | -   | -   | ±10  | mV       | Given for the DAC in 12-bit configuration                                                                       |

| Offset <sup>(4)</sup>           | (difference between<br>measured value at<br>Code (0x800) and the                                                                                                         | -                     | -   | -   | ±3   | LSB      | Given for the DAC in 10-bit at<br>V <sub>REF+</sub> = 3.6 V                                                     |

|                                 | ideal value = $V_{\text{REF+}}/2$ )                                                                                                                                      | -                     | -   | -   | ±12  | LSB      | Given for the DAC in 12-bit at<br>V <sub>REF+</sub> = 3.6 V                                                     |

| Gain<br>error <sup>(4)</sup>    | Gain error                                                                                                                                                               | -                     | -   | -   | ±0.5 | %        | Given for the DAC in 12-bit configuration                                                                       |

| <sup>t</sup> SETTLIN<br>G       | Settling time (full<br>scale: for a 10-bit input<br>code transition<br>between the lowest<br>and the highest input<br>codes when<br>DAC_OUT reaches<br>final value ±4LSB | -                     | -   | 3   | 6    | μs       | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                           |

| THD <sup>(4)</sup>              | Total Harmonic<br>Distortion<br>Buffer ON                                                                                                                                | -                     | -   | -   | -    | dB       | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                           |

| Update<br>rate <sup>(2)</sup>   | Max frequency for a correct DAC_OUT change when small variation in the input code (from code i to i+1LSB)                                                                | -                     | -   | -   | 1    | MS/<br>s | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                           |

#### Table 85. DAC characteristics (continued)

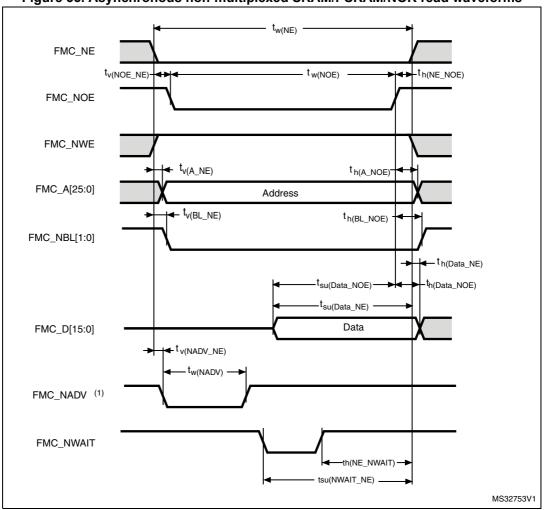

Figure 55. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

| Table 86. Asynchronous non-multiplexed SRAM/PSRAM/NOR - |

|---------------------------------------------------------|

| read timings <sup>(1)(2)</sup>                          |

| read unings (A)                                         |

| Symbol                    | Parameter                             | Min                      | Мах                      | Unit |

|---------------------------|---------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                       | 2T <sub>HCLK</sub> – 0.5 | 2 T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low            | 0                        | 1                        | ns   |

| t <sub>w(NOE)</sub>       | FMC_NOE low time                      | 2T <sub>HCLK</sub>       | 2T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time | 0                        | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid            | -                        | 2                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high  | 0                        | -                        | ns   |

| $t_{v(BL_NE)}$            | FMC_NEx low to FMC_BL valid           | -                        | 2                        | ns   |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time      | T <sub>HCLK</sub> +2     | -                        | ns   |

| Symbol                                    | Parameter              | Min                      | Мах                     | Unit |

|-------------------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>                     | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL_Data</sub> )              | Data output valid time | -                        | 3.5                     |      |

| t <sub>h(SDCLKL</sub> _Data)              | Data output hold time  | 0                        | -                       |      |

| $t_{d(SDCLKL_Add)}$                       | Address valid time     | -                        | 1.5                     |      |

| t <sub>d(SDCLKL_SDNWE)</sub>              | SDNWE valid time       | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNWE)</sub>              | SDNWE hold time        | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNE)</sub>               | Chip select valid time | -                        | 0.5                     | ns   |

| t <sub>h(SDCLKLSDNE)</sub>                | Chip select hold time  | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub>             | SDNRAS valid time      | -                        | 2                       |      |

| t <sub>h(SDCLKL_SDNRAS)</sub>             | SDNRAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub>             | SDNCAS valid time      | -                        | 0.5                     |      |

| t <sub>d(SDCLKL_SDNCAS)</sub>             | SDNCAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_NBL)</sub> NBL valid time |                        | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_NBL)</sub>                | NBLoutput time         | 0                        | -                       |      |

## Table 104. SDRAM write timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

## Table 105. LPSDR SDRAM write timings<sup>(1)(2)</sup>

| Symbol                         | Parameter              | Min                      | Max                     | Unit |

|--------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>          | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL _Data</sub> )  | Data output valid time | -                        | 5                       |      |

| t <sub>h(SDCLKL</sub> _Data)   | Data output hold time  | 2                        | -                       |      |

| $t_{d(SDCLKL_Add)}$            | Address valid time     | -                        | 2.8                     |      |

| t <sub>d(SDCLKL-SDNWE)</sub>   | SDNWE valid time       | -                        | 2                       |      |

| t <sub>h(SDCLKL-SDNWE)</sub>   | SDNWE hold time        | 1                        | -                       |      |

| t <sub>d(SDCLKL</sub> - SDNE)  | Chip select valid time | -                        | 1.5                     |      |

| t <sub>h(SDCLKL</sub> - SDNE)  | Chip select hold time  | 1                        | -                       | ns   |

| t <sub>d</sub> (SDCLKL-SDNRAS) | SDNRAS valid time      | -                        | 1.5                     |      |

| t <sub>h(SDCLKL-SDNRAS)</sub>  | SDNRAS hold time       | 1.5                      | -                       |      |

| t <sub>d</sub> (SDCLKL-SDNCAS) | SDNCAS valid time      | -                        | 1.5                     |      |

| t <sub>d</sub> (SDCLKL-SDNCAS) | SDNCAS hold time       | 1.5                      | -                       |      |

| $t_{d(SDCLKL_NBL)}$            | NBL valid time         | -                        | 1.5                     |      |

| t <sub>h(SDCLKL-NBL)</sub>     | NBL output time        | 1.5                      | -                       |      |

1. CL = 10 pF.

2. Guaranteed by characterization results.

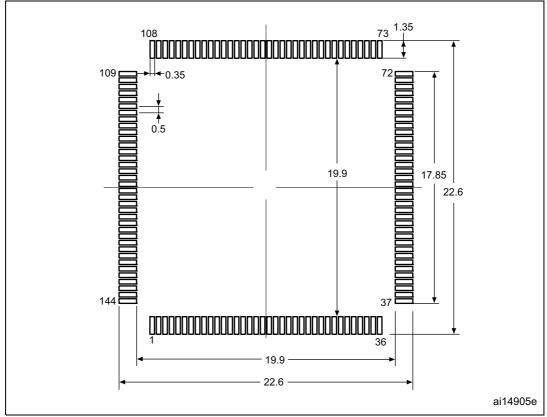

1. Dimensions are expressed in millimeters.

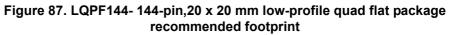

## Figure 93. LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

## 8 Part numbering

| Table 122. Ordering infor                                                                        | mation sc | heme |       |    |   |     |

|--------------------------------------------------------------------------------------------------|-----------|------|-------|----|---|-----|

| Example:                                                                                         | STM32     | F    | 439 V | ΙT | 6 | ххх |

| Device family                                                                                    |           |      |       |    |   |     |

| STM32 = ARM-based 32-bit microcontroller                                                         |           |      |       |    |   |     |

| Product type                                                                                     |           |      |       |    |   |     |

| F = general-purpose                                                                              |           |      |       |    |   |     |

| Device subfamily                                                                                 |           |      |       |    |   |     |

| 437= STM32F437xx, USB OTG FS/HS, camera interface,<br>Ethernet, cryptographic acceleration       |           |      |       |    |   |     |

| 439= STM32F439xx, USB OTG FS/HS, camera interface, Ethernet, LCD-TFT, cryptographic acceleration |           |      |       |    |   |     |

| Pin count                                                                                        |           |      |       |    |   |     |

| V = 100 pins                                                                                     |           |      |       |    |   |     |

| Z = 143 and 144 pins                                                                             |           |      |       |    |   |     |

| A = 169 pins                                                                                     |           |      |       |    |   |     |

| I = 176 pins                                                                                     |           |      |       |    |   |     |

| B = 208 pins                                                                                     |           |      |       |    |   |     |

| N = 216 pins                                                                                     |           |      |       |    |   |     |

| Flash memory size                                                                                |           |      |       |    |   |     |

| G = 1024 Kbytes of Flash memory                                                                  |           |      |       |    |   |     |

| I = 2048 Kbytes of Flash memory                                                                  |           |      |       |    |   |     |

| Package                                                                                          |           |      |       |    |   |     |

| T = LQFP                                                                                         |           |      |       |    |   |     |

| H = BGA                                                                                          |           |      |       |    |   |     |

| Y = WLCSP                                                                                        |           |      |       |    |   |     |

| Temperature range                                                                                |           |      |       |    |   |     |

| 6 = Industrial temperature range, $-40$ to 85 °C.                                                |           |      |       |    |   |     |

| 7 = Industrial temperature range, -40 to 105 °C.                                                 |           |      |       |    |   |     |

| Options                                                                                          |           |      |       |    |   |     |

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Date                | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>19-Feb-2015 | 6<br>Revision | Changes           Update SPI/IS2 in Table 2: STM32F437xx and STM32F439xx features<br>and peripheral counts.           Updated LQFP208 in Table 4: Regulator ON/OFF and internal reset<br>ON/OFF availability.           Updated Figure 19: Memory map.           Changed PLS[2:0]=101 (falling edge) maximum value in Table 22:<br>reset and power control block characteristics.           Updated current consumption with all peripherals disabled in Table 24:<br>Typical and maximum current consumption in Run mode, code with<br>data processing running from Flash memory (ART accelerator<br>enabled except prefetch) or RAM.           Updated note 1. in Table 28: Typical and maximum current<br>consumptions in Standby mode.           Updated Table 56: I/O static characteristics.           Section : I2C interface characteristics: updated section introduction,<br>removed Table 12C characteristics, Figure 12C bus AC waveforms and<br>measurement circuit and Table SCL frequency; added Table 61: I2C<br>analog filter characteristics.           Updated Figure 51: Typical connection diagram using the ADC.           Updated Figure 51: Typical connection diagram using the ADC.           Updated Figure 83: WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm<br>pitch wafer level chip scale package outline and Table 111: WLCSP143<br>- 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale<br>package mechanical data; added Figure 84: WLCSP143 - 143-ball,<br>4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale recommended<br>footprint and Table 112: WLCSP143 recommended PCB design rules<br>(0.4 mm pitch). Updated Figure 85: WLCSP143 - 143-ball,<br>4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale recommended<br>footprint and Table 112: WLCSP143 recommended PCB design rules<br>(0.4 m |

Table 124. Document revision history (continued)