# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| υ | e | C | а | IS |

|---|---|---|---|----|

|   |   |   |   |    |

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437vit6tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 6.1.1    | Minimum and maximum values                                      |

|-----|----------|-----------------------------------------------------------------|

|     | 6.1.2    | Typical values                                                  |

|     | 6.1.3    | Typical curves                                                  |

|     | 6.1.4    | Loading capacitor                                               |

|     | 6.1.5    | Pin input voltage                                               |

|     | 6.1.6    | Power supply scheme                                             |

|     | 6.1.7    | Current consumption measurement                                 |

| 6.2 | Absolute | e maximum ratings                                               |

| 6.3 | Operatir | ng conditions                                                   |

|     | 6.3.1    | General operating conditions                                    |

|     | 6.3.2    | VCAP1/VCAP2 external capacitor                                  |

|     | 6.3.3    | Operating conditions at power-up / power-down (regulator ON) 97 |

|     | 6.3.4    | Operating conditions at power-up / power-down (regulator OFF)97 |

|     | 6.3.5    | Reset and power control block characteristics                   |

|     | 6.3.6    | Over-drive switching characteristics                            |

|     | 6.3.7    | Supply current characteristics                                  |

|     | 6.3.8    | Wakeup time from low-power modes                                |

|     | 6.3.9    | External clock source characteristics                           |

|     | 6.3.10   | Internal clock source characteristics                           |

|     | 6.3.11   | PLL characteristics                                             |

|     | 6.3.12   | PLL spread spectrum clock generation (SSCG) characteristics 127 |

|     | 6.3.13   | Memory characteristics                                          |

|     | 6.3.14   | EMC characteristics                                             |

|     | 6.3.15   | Absolute maximum ratings (electrical sensitivity)               |

|     | 6.3.16   | I/O current injection characteristics                           |

|     | 6.3.17   | I/O port characteristics                                        |

|     | 6.3.18   | NRST pin characteristics                                        |

|     | 6.3.19   | TIM timer characteristics                                       |

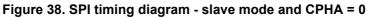

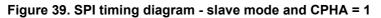

|     | 6.3.20   | Communications interfaces                                       |

|     | 6.3.21   | 12-bit ADC characteristics                                      |

|     | 6.3.22   | Temperature sensor characteristics                              |

|     | 6.3.23   | V <sub>BAT</sub> monitoring characteristics                     |

|     | 6.3.24   | Reference voltage                                               |

|     | 6.3.25   | DAC electrical characteristics                                  |

|     | 6.3.26   | FMC characteristics                                             |

|     | 6.3.27   | Camera interface (DCMI) timing specifications                   |

|     | 6.3.28   | LCD-TFT controller (LTDC) characteristics                       |

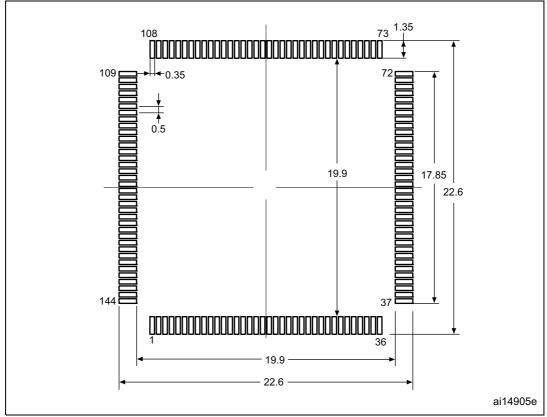

| Figure 90.  | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint    | 212 |

|-------------|------------------------------------------------------------------------------|-----|

| Figure 91.  | LQFP176 marking (package top view)                                           |     |

| Figure 92.  | LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package outline          |     |

| Figure 93.  | LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package                  |     |

| 0           | recommended footprint                                                        | 216 |

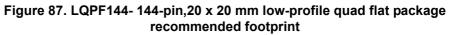

| Figure 94.  | LQFP208 marking example (package top view)                                   | 217 |

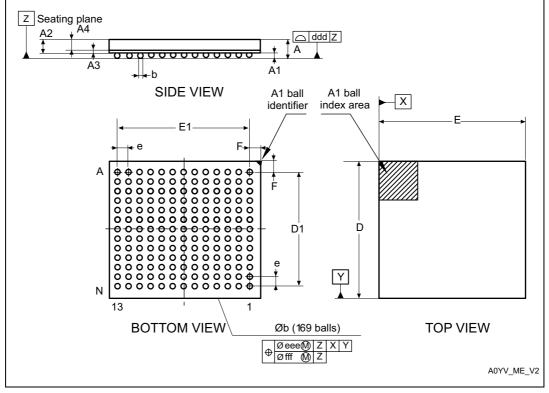

| Figure 95.  | UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid array |     |

| .guie eei   | package outline.                                                             |     |

| Figure 96.  | UFBGA169 - 169-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch               |     |

|             | ball grid array recommended footprint                                        | 219 |

| Figure 97.  | UFBGA169 marking example (package top view)                                  |     |

| Figure 98.  | UFBGA176+25 - ball 10 x 10 mm, 0.65 mm pitch ultra thin fine pitch           |     |

| 0           | ball grid array package outline                                              | 221 |

| Figure 99.  | UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch                |     |

| 0           | ball grid array package recommended footprint                                | 222 |

| Figure 100. | UFBGA176+25 marking example (package top view)                               |     |

|             | TFBGA216 - 216 ball 13 × 13 mm 0.8 mm pitch thin fine pitch                  |     |

| 5           | ball grid array package outline                                              | 224 |

| Figure 102. | TFBGA176 marking example (package top view)                                  |     |

|             | USB controller configured as peripheral-only and used                        |     |

| 0           | in Full speed mode                                                           | 229 |

| Figure 104. | USB controller configured as host-only and used in full speed mode.          |     |

|             | USB controller configured in dual mode and used in full speed mode           |     |

|             | USB controller configured as peripheral, host, or dual-mode                  |     |

| 0           | and used in high speed mode.                                                 | 231 |

| Figure 107. | MII mode using a 25 MHz crystal                                              |     |

|             | RMII with a 50 MHz oscillator                                                |     |

| -           | RMII with a 25 MHz crystal and PHY with PLL.                                 |     |

### 2.1 Full compatibility throughout the family

The STM32F437xx and STM32F439xx devices are part of the STM32F4 family. They are fully pin-to-pin, software and feature compatible with the STM32F2xx devices, allowing the user to try different memory densities, peripherals, and performances (FPU, higher frequency) for a greater degree of freedom during the development cycle.

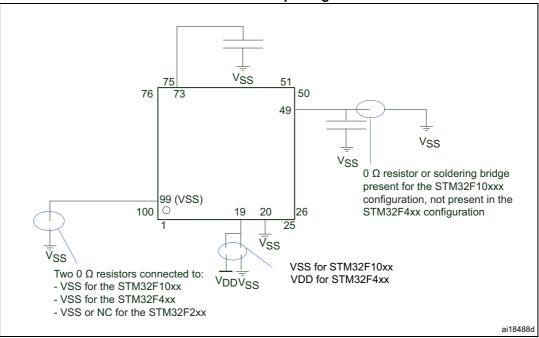

The STM32F437xx and STM32F439xx devices maintain a close compatibility with the whole STM32F10xx family. All functional pins are pin-to-pin compatible. The STM32F437xx and STM32F439xx, however, are not drop-in replacements for the STM32F10xx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xx to the STM32F43x family remains simple as only a few pins are impacted.

*Figure 1*, *Figure 2*, and *Figure 3*, give compatible board designs between the STM32F4xx, STM32F2xx, and STM32F10xx families.

Figure 1. Compatible board design STM32F10xx/STM32F2xx/STM32F4xx for LQFP100 package

detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 180 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 180 MHz while the maximum frequency of the high-speed APB domains is 90 MHz. The maximum allowed frequency of the low-speed APB domain is 45 MHz.

The devices embed a dedicated PLL (PLLI2S) and PLLSAI which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

### 3.15 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface. Refer to application note AN2606 for details.

### 3.16 Power supply schemes

- $V_{DD}$  = 1.7 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Note: V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

### 3.17 **Power supply supervisor**

### 3.17.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other package, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is

DocID024244 Rev 10

### 3.22.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

### 3.22.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F43x devices (see *Table 6* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F43x include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

### 3.22.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

DocID024244 Rev 10

### 3.26 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available. They can be operated in master or slave mode, in full duplex and simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

Note: For I2S2 full-duplex mode, I2S2\_CK and I2S2\_WS signals can be used only on GPIO Port B and GPIO Port D.

### 3.27 Serial Audio interface (SAI1)

The serial audio interface (SAI1) is based on two independent audio sub-blocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both sub-blocks can be configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

SAI1 can be served by the DMA controller.

### 3.28 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S/SAI flow with an external PLL (or Codec output).

### 3.29 Audio and LCD PLL(PLLSAI)

An additional PLL dedicated to audio and LCD-TFT is used for SAI1 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the LCD-TFT clock.

|         |         |          | Pin nu   | ımbei   | r        |         |          |                                                      |          |                 |       |                                                                                           |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                       | Additional<br>functions |

| 49      | 71      | N9       | M10      | 81      | N2       | 92      | L11      | V <sub>CAP_1</sub>                                   | S        | -               | -     | -                                                                                         | -                       |

| -       | I       | -        | -        | -       | H2       | 93      | K9       | V <sub>SS</sub>                                      | S        | -               | 1     | -                                                                                         | -                       |

| 50      | 72      | F8       | N10      | 82      | J6       | 94      | L10      | V <sub>DD</sub>                                      | S        | -               | I     | -                                                                                         | -                       |

| -       | I       | -        | -        | -       | -        | 95      | M14      | PJ5                                                  | I/O      | -               | I     | LCD_R6, EVENTOUT                                                                          | -                       |

| -       | -       | N10      | M11      | 83      | -        | 96      | P13      | PH6                                                  | I/O      | FT              | -     | I2C2_SMBA,<br>SPI5_SCK,<br>TIM12_CH1,<br>ETH_MII_RXD2,<br>FMC_SDNE1,<br>DCMI_D8, EVENTOUT | -                       |

| -       | -       | M10      | N12      | 84      | -        | 97      | N13      | PH7                                                  | I/O      | FT              | -     | I2C3_SCL, SPI5_MISO,<br>ETH_MII_RXD3,<br>FMC_SDCKE1,<br>DCMI_D9, EVENTOUT                 | -                       |

| -       | -       | L10      | M12      | 85      | -        | 98      | P14      | PH8                                                  | I/O      | FT              | -     | I2C3_SDA, FMC_D16,<br>DCMI_HSYNC,<br>LCD_R2, EVENTOUT                                     | -                       |

| -       | -       | K10      | M13      | 86      | -        | 99      | N14      | PH9                                                  | I/O      | FT              | -     | I2C3_SMBA,<br>TIM12_CH2,<br>FMC_D17, DCMI_D0,<br>LCD_R3, EVENTOUT                         | -                       |

| -       | -       | N11      | L13      | 87      | -        | 100     | P15      | PH10                                                 | I/O      | FT              | -     | TIM5_CH1, FMC_D18,<br>DCMI_D1, LCD_R4,<br>EVENTOUT                                        | -                       |

| -       | -       | M11      | L12      | 88      | -        | 101     | N15      | PH11                                                 | I/O      | FT              | -     | TIM5_CH2, FMC_D19,<br>DCMI_D2, LCD_R5,<br>EVENTOUT                                        | -                       |

| -       | -       | L11      | K12      | 89      | -        | 102     | M15      | PH12                                                 | I/O      | FT              | -     | TIM5_CH3, FMC_D20,<br>DCMI_D3, LCD_R6,<br>EVENTOUT                                        | -                       |

| -       | I       | E7       | H12      | 90      | -        | -       | K10      | V <sub>SS</sub>                                      | s        | -               | -     | -                                                                                         | -                       |

| -       | -       | H8       | J12      | 91      | -        | 103     | K11      | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                         | -                       |

| Table 10. | STM32F437xx and | STM32F439xx pin | and ball definitions | (continued) |

|-----------|-----------------|-----------------|----------------------|-------------|

|           |                 |                 |                      |             |

|         |         |          | Pin nu   | Imber   | -        |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| -       | 91      | G11      | J15      | 110     | G4       | 133     | J15      | PG6                                                  | I/O      | FT              | -     | FMC_INT2, DCMI_D12,<br>LCD_R7, EVENTOUT                                                       | -                       |

| -       | 92      | G12      | J14      | 111     | H1       | 134     | J14      | PG7                                                  | I/O      | FT              | -     | USART6_CK,<br>FMC_INT3, DCMI_D13,<br>LCD_CLK, EVENTOUT                                        | -                       |

| -       | 93      | F13      | H14      | 112     | G2       | 135     | H14      | PG8                                                  | I/O      | FT              | -     | SPI6_NSS,<br>USART6_RTS,<br>ETH_PPS_OUT,<br>FMC_SDCLK,<br>EVENTOUT                            | -                       |

| -       | 94      | J7       | G12      | 113     | D2       | 136     | G10      | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 95      | E6       | H13      | 114     | G1       | 137     | G11      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| 63      | 96      | F9       | H15      | 115     | F2       | 138     | H15      | PC6                                                  | I/O      | FT              | -     | TIM3_CH1, TIM8_CH1,<br>I2S2_MCK,<br>USART6_TX,<br>SDIO_D6, DCMI_D0,<br>LCD_HSYNC,<br>EVENTOUT | -                       |

| 64      | 97      | F10      | G15      | 116     | F3       | 139     | G15      | PC7                                                  | I/O      | FT              | -     | TIM3_CH2, TIM8_CH2,<br>I2S3_MCK,<br>USART6_RX,<br>SDIO_D7, DCMI_D1,<br>LCD_G6, EVENTOUT       | -                       |

| 65      | 98      | F11      | G14      | 117     | E4       | 140     | G14      | PC8                                                  | I/O      | FT              | -     | TIM3_CH3, TIM8_CH3,<br>USART6_CK,<br>SDIO_D0, DCMI_D2,<br>EVENTOUT                            | -                       |

| 66      | 99      | F12      | F14      | 118     | E3       | 141     | F14      | PC9                                                  | I/O      | FT              | -     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, SDIO_D1,<br>DCMI_D3, EVENTOUT             | -                       |

| 67      | 100     | E13      | F15      | 119     | F1       | 142     | F15      | PA8                                                  | I/O      | FT              | -     | MCO1, TIM1_CH1,<br>I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF,<br>LCD_R6, EVENTOUT                 | -                       |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

| Л | ۱ |

|---|---|

|   |   |

|   |   |

DocID024244 Rev 10

81/240

|          |        | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11                                     | AF12                       | AF13                  | AF14   | AF15         |

|----------|--------|-----|--------|----------|------------------|---------------|--------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|------------------------------------------|----------------------------|-----------------------|--------|--------------|

|          | Port   | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11 | l2C1/<br>2/3  | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН                                      | FMC/SDIO<br>/OTG2_FS       | DCMI                  | LCD    | SYS          |

|          | PG9    | -   | -      | -        | -                | -             | -                  | -               | -                       | USART6_<br>RX              | -                              | -                       | -                                        | FMC_NE2/<br>FMC_<br>NCE3   | DCMI_<br>VSYNC<br>(1) | -      | EVEN<br>TOUT |

|          | PG10   | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | LCD_G3                         | -                       | -                                        | FMC_<br>NCE4_1/<br>FMC_NE3 | DCMI_<br>D2           | LCD_B2 | EVEN<br>TOUT |

|          | PG11   | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>TX_EN/<br>ETH_RMII<br>_TX_EN | FMC_<br>NCE4_2             | DCMI_<br>D3           | LCD_B3 | EVEN<br>TOUT |

| Por<br>G | t PG12 | -   | -      | -        | -                | -             | SPI6_<br>MISO      | -               | -                       | USART6_<br>RTS             | LCD_B4                         | -                       | -                                        | FMC_NE4                    | -                     | LCD_B1 | EVEN<br>TOUT |

|          | PG13   | -   | -      | -        | -                | -             | SPI6_<br>SCK       | -               | -                       | USART6_<br>CTS             | -                              | -                       | ETH_MII_<br>TXD0/<br>ETH_RMII<br>_TXD0   | FMC_A24                    | -                     | -      | EVEN<br>TOUT |

|          | PG14   | -   | -      | -        | -                | -             | SPI6_<br>MOSI      | -               | -                       | USART6_<br>TX              | -                              | -                       | ETH_MII_<br>TXD1/<br>ETH_RMII<br>_TXD1   | FMC_A25                    | -                     | -      | EVEN<br>TOUT |

|          | PG15   | -   | -      | -        | -                | -             | -                  | -               | -                       | USART6_<br>CTS             | -                              | -                       | -                                        | FMC_<br>SDNCAS             | DCMI_<br>D13          | -      | EVEN<br>TOUT |

|          | PH0    | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | -                                        | -                          | -                     | -      | EVEN<br>TOUT |

|          | PH1    | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | -                                        | -                          | -                     | -      | EVEN<br>TOUT |

|          | PH2    | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>CRS                          | FMC_<br>SDCKE0             | -                     | LCD_R0 | EVEN<br>TOUT |

| Por<br>H | t PH3  | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>COL                          | FMC_SDN<br>E0              | -                     | LCD_R1 | EVEN<br>TOUT |

|          | PH4    | -   | -      | -        | -                | I2C2_<br>SCL  | -                  | -               | -                       | -                          | -                              | OTG_HS_<br>ULPI_NXT     | -                                        | -                          | -                     | -      | EVEN<br>TOUT |

|          | PH5    | -   | -      | -        | -                | I2C2_<br>SDA  | SPI5_N<br>SS       | -               | -                       | -                          | -                              | -                       | -                                        | FMC_SDN<br>WE              | -                     | -      | EVEN<br>TOUT |

|          | PH6    | -   | -      | -        | -                | I2C2_<br>SMBA | SPI5_<br>SCK       | -               | -                       | -                          | TIM12_CH1                      | -                       | -                                        | FMC_<br>SDNE1              | DCMI_<br>D8           | -      | -            |

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

Pinouts and pin description

STM32F437xx and STM32F439xx

| Symbol                               | Ratings                                                                         | Max.   | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|--------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>    | 270    |      |

| $\Sigma I_{VSS}$                     | Total current out of sum of all $V_{SS_x}$ ground lines $(sink)^{(1)}$          | - 270  |      |

| I <sub>VDD</sub>                     | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>  | 100    |      |

| I <sub>VSS</sub>                     | Maximum current out of each $V_{SS_x}$ ground line (sink) <sup>(1)</sup>        | - 100  |      |

| 1                                    | Output current sunk by any I/O and control pin                                  | 25     |      |

| I <sub>IO</sub>                      | Output current sourced by any I/Os and control pin                              | - 25   |      |

| 21                                   | Total output current sunk by sum of all I/O and control pins <sup>(2)</sup>     | 120    | mA   |

| Σl <sub>IO</sub>                     | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | - 120  |      |

|                                      | Injected current on FT pins <sup>(4)</sup>                                      | 5/10   |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on NRST and BOOT0 pins <sup>(4)</sup>                          | - 5/+0 |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ±5     | 1    |

| $\Sigma I_{\rm INJ(PIN)}^{(5)}$      | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ±25    | 1    |

#### Table 15. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.21: 12-bit ADC characteristics.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. A positive injection is induced by  $V_{IN} > V_{DDA}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 14* for the values of the maximum allowed input voltage.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 16. Thermal characteristics

| Symbol           | Ratings                      | Value        | Unit |

|------------------|------------------------------|--------------|------|

| T <sub>STG</sub> | Storage temperature range    | – 65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125          | °C   |

#### Additional current consumption

The MCU is placed under the following conditions:

- All I/O pins are configured in analog mode.

- The Flash memory access time is adjusted to fHCLK frequency.

- The voltage scaling is adjusted to fHCLK frequency as follows:

- Scale 3 for  $f_{HCLK} \le 120$  MHz,

- Scale 2 for 120 MHz <  $f_{HCLK} \le 144$  MHz

- Scale 1 for 144 MHz <  $f_{HCLK} \le$  180 MHz. The over-drive is only ON at 180 MHz.

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- HSE crystal clock frequency is 25 MHz.

- When the regulator is OFF, V12 is provided externally as described in *Table 17: General operating conditions*

- T<sub>A</sub>= 25 °C .

### Table 30. Typical current consumption in Run mode, code with data processing running from Flash memory or RAM, regulator ON (ART accelerator enabled except prefetch), $V_{DD}=1.7 V^{(1)}$

| Symbol          | Parameter                                                    | Conditions     | f <sub>HCLK</sub> (MHz) | Тур  | Unit |

|-----------------|--------------------------------------------------------------|----------------|-------------------------|------|------|

|                 |                                                              |                | 168                     | 88.2 |      |

|                 |                                                              |                | 150                     | 74.3 |      |

|                 |                                                              |                | 144                     | 71.3 |      |

|                 |                                                              | All Peripheral | 120                     | 52.9 |      |

|                 |                                                              | enabled        | 90                      | 42.6 |      |

|                 | Supply current in<br>RUN mode from<br>V <sub>DD</sub> supply |                | 60                      | 28.6 | - mA |

|                 |                                                              |                | 30                      | 15.7 |      |

|                 |                                                              |                | 25                      | 12.3 |      |

| I <sub>DD</sub> |                                                              |                | 168                     | 40.6 |      |

|                 |                                                              |                | 150                     | 30.6 |      |

|                 |                                                              |                | 144                     | 32.6 |      |

|                 |                                                              | All Peripheral | 120                     | 24.7 |      |

|                 |                                                              | disabled       | 90                      | 19.7 |      |

|                 |                                                              |                | 60                      | 13.6 |      |

|                 |                                                              |                | 30                      | 7.7  |      |

|                 |                                                              |                | 25                      | 6.7  |      |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherls (such as ADC, or DAC) is not included.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                                                              | Conditions                                      | Min | Тур | Мах                | Unit                         |  |

|-----------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|--------------------|------------------------------|--|

|                                               |                         |                                                                                                        | $C_L = 30 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$ | -   | -   | 100 <sup>(4)</sup> | ) <sup>(4)</sup>             |  |

|                                               |                         |                                                                                                        | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 50                 | .5<br><sub>0</sub> (4)<br>00 |  |

|                                               | f                       | Maximum frequency <sup>(3)</sup>                                                                       | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 42.5               |                              |  |

|                                               | † <sub>max(IO)out</sub> |                                                                                                        | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 180 <sup>(4)</sup> |                              |  |

|                                               |                         |                                                                                                        | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 100                |                              |  |

| 11                                            |                         |                                                                                                        | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 72.5               |                              |  |

| 11                                            |                         |                                                                                                        | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 4                  |                              |  |

|                                               |                         |                                                                                                        | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 6                  |                              |  |

|                                               | t <sub>f(IO)out</sub> / | Output high to low level fall                                                                          | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 7                  |                              |  |

|                                               | t <sub>r(IO)out</sub>   | time and output low to high level rise time                                                            | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 2.5                | ns                           |  |

|                                               |                         | $C_L = 10 \text{ pF}, V_{DD} \ge 1.8 \text{ V}$ -<br>$C_L = 10 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$ - | -                                               | 3.5 |     |                    |                              |  |

|                                               |                         |                                                                                                        | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 4                  |                              |  |

| -                                             | tEXTIpw                 | Pulse width of external signals detected by the EXTI controller                                        | -                                               | 10  | -   | -                  | ns                           |  |

| Table 58. I/O AC characteristics <sup>(1)(2)</sup> | (continued) |

|----------------------------------------------------|-------------|

|----------------------------------------------------|-------------|

1. Guaranteed by design.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

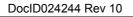

3. The maximum frequency is defined in *Figure 36*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

### Figure 36. I/O AC characteristics definition

#### **Electrical characteristics**

| Symbol                           | Parameter                                  | Conditions                                                                           | Min. | Тур. | Max. | Unit |

|----------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>SC</sub>                  | Control in (ULPI_DIR, ULPI_NXT) setup time |                                                                                      | 2    | -    | -    |      |

| t <sub>HC</sub>                  | Control in (ULPI_DIR, ULPI_NXT) hold time  |                                                                                      | 0.5  | -    | -    |      |

| t <sub>SD</sub>                  | Data in setup time                         |                                                                                      | 1.5  | -    | -    |      |

| t <sub>HD</sub>                  | Data in hold time                          |                                                                                      | 2    | -    | -    |      |

| t <sub>DC</sub> /t <sub>DD</sub> |                                            | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                | 9.5  | ns   |      |      |

|                                  | Data/control output delay                  | $C_L = 20 \text{ pF}$ and                                                            | -    | 10   | 15   |      |

|                                  |                                            | 1.7 V < V <sub>DD</sub> < 3.6 V,<br>C <sub>L</sub> = 15 pF and<br>OSPEEDRy[1:0] = 11 | -    | 1 12 |      |      |

Table 70. Dynamic characteristics: USB ULPI<sup>(1)</sup>

1. Guaranteed by characterization results.

### 6.3.25 DAC electrical characteristics

| Symbol                            | Parameter                                                                             | Table 85. DAC c       Parameter     Conditions |                                                       |                                  |     | Max                            | Unit | Comments                                                                                                                |  |

|-----------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|----------------------------------|-----|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------|--|

| •                                 |                                                                                       | Conditions                                     |                                                       | <b>Min</b><br>1.7 <sup>(1)</sup> | Тур |                                |      | Commenta                                                                                                                |  |

| V <sub>DDA</sub>                  | Analog supply voltage                                                                 | -                                              |                                                       | 1.7.9                            | -   | 3.6                            | V    | -                                                                                                                       |  |

| $V_{REF^+}$                       | Reference supply voltage                                                              | -                                              |                                                       | 1.7 <sup>(1)</sup>               | -   | 3.6                            | V    | V <sub>REF+</sub> ⊴V <sub>DDA</sub>                                                                                     |  |

| $V_{SSA}$                         | Ground                                                                                |                                                | -                                                     | 0                                | -   | 0                              | V    | -                                                                                                                       |  |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load                                                                        | DAC output<br>buffer ON                        | R <sub>LOAD</sub><br>connected<br>to V <sub>SSA</sub> | 5                                | -   | -                              | kΩ   | -                                                                                                                       |  |

|                                   |                                                                                       |                                                | R <sub>LOAD</sub><br>connected<br>to V <sub>DDA</sub> | 25                               |     |                                |      | -                                                                                                                       |  |

| R <sub>O</sub> <sup>(2)</sup>     | Impedance output with buffer OFF                                                      | -                                              |                                                       | -                                | -   | 15                             | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |  |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                                                       | -                                              |                                                       | -                                | -   | 50                             | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |  |

| DAC_O<br>UT<br>min <sup>(2)</sup> | Lower DAC_OUT voltage with buffer ON                                                  |                                                |                                                       | 0.2                              | -   | -                              | v    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input                                  |  |

| DAC_O<br>UT<br>max <sup>(2)</sup> | Higher DAC_OUT voltage with buffer ON                                                 |                                                |                                                       | -                                | -   | V <sub>DDA</sub><br>- 0.2      | v    | code (0x0E0) to (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V and (0x1C7) to<br>(0xE38) at V <sub>REF+</sub> = 1.7 V          |  |

| DAC_O<br>UT<br>min <sup>(2)</sup> | Lower DAC_OUT<br>voltage with buffer<br>OFF                                           | -                                              |                                                       | -                                | 0.5 | -                              | mV   | It gives the maximum output                                                                                             |  |

| DAC_O<br>UT<br>max <sup>(2)</sup> | Higher DAC_OUT<br>voltage with buffer<br>OFF                                          |                                                | -                                                     | -                                | -   | V <sub>REF+</sub><br>–<br>1LSB | v    | excursion of the DAC.                                                                                                   |  |

| I <sub>VREF+</sub> <sup>(4)</sup> | DAC DC V <sub>REF</sub> current<br>consumption in<br>quiescent mode<br>(Standby mode) | -                                              |                                                       | -                                | 170 | 240                            |      | With no load, worst code<br>(0x800) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs         |  |

|                                   |                                                                                       |                                                |                                                       | -                                | 50  | 75                             | μA   | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs         |  |

#### Table 85. DAC characteristics

### 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

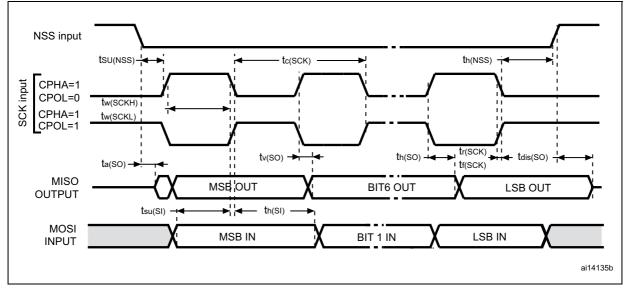

### 7.1 LQFP100 package information

Figure 80. LQFP100 -100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

1. Dimensions are expressed in millimeters.

#### **Device marking for LQFP208**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

### 7.6 UFBGA169 package information

Figure 95. UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 116. UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid arraypackage mechanical data

| Cumula a l |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol     | Min   | Тур         | Max   | Min                   | Тур    | Мах    |  |

| А          | 0.460 | 0.530       | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |

| A1         | 0.050 | 0.080       | 0.110 | 0.0020                | 0.0031 | 0.0043 |  |

| A2         | 0.400 | 0.450       | 0.500 | 0.0157                | 0.0177 | 0.0197 |  |

| A3         | -     | 0.130       | -     | -                     | 0.0051 | -      |  |

| A4         | 0.270 | 0.320       | 0.370 | 0.0106                | 0.0126 | 0.0146 |  |

| b          | 0.230 | 0.280       | 0.330 | 0.0091                | 0.0110 | 0.0130 |  |

| D          | 6.950 | 7.000       | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| D1         | 5.950 | 6.000       | 6.050 | 0.2343                | 0.2362 | 0.2382 |  |

| Е          | 6.950 | 7.000       | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| E1         | 5.950 | 6.000       | 6.050 | 0.2343                | 0.2362 | 0.2382 |  |

| е          | -     | 0.500       | -     | -                     | 0.0197 | -      |  |

## 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-Aug-2013 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10-Sep-2013 | 2        | Added STM32F439xx part numbers and related informations.<br><b>STM32F437xx part numbers:</b><br>Replaced FSMC by FMC added Chrom-ART Accelerator and SAI<br>interface.<br>Increased core, timer, GPIOs, SPI maximum frequencies<br>Updated Figure 4: STM32F437xx and STM32F439xx block diagram.<br>Updated Figure 5: STM32F437xx and STM32F439xx Multi-AHB<br>matrix.<br>Removed note in Section -: Standby mode.<br>Updated Figure 14: STM32F437xx and STM32F439xx pin and ball<br>definitions and Table 12: STM32F437xx and STM32F439xx alternate<br>function mapping<br>Modified Figure 19: Memory map.<br>Updated Table 17: General operating conditions, Table 18: Limitations<br>depending on the operating power supply range. Removed note 1 in<br>Table 22: reset and power control block characteristics. Added<br>Table 23: Over-drive switching characteristics.<br>Updated Section : Typical and maximum current consumption,<br>Table 34: Switching output I/O current consumption, Table 35:<br>Peripheral current consumption and Section : On-chip peripheral<br>current consumption.<br>Updated Table 36: Low-power mode wakeup timings.<br>Modified Section : High-speed external user clock generated<br>from an external source, and Section 6.3.10: Internal clock source<br>characteristics.<br>Updated Table 43: Main PLL characteristics and Table 45: PLLISAI<br>(audio and LCD-TFT PLL) characteristics.<br>Updated Table 57: Output voltage characteristics and Table 58: I/O AC<br>characteristics.<br>Updated Table 60: TIMx characteristics, Table 61: I2C characteristics,<br>Table 62: SPI dynamic characteristics, Section : SAI characteristics,<br>Table 62: SPI dynamic characteristics, Section : SAI characteristics,<br>Updated Table 60: TIMx characteristics, Table 61: I2C characteristics,<br>Updated Table 60: TIMx characteristics, Section : SAI characteristics,<br>Updated Table 60: SDRAM read timings and Table 104: SDRAM write<br>timings. |

| Table 124. | Document revision history |

|------------|---------------------------|

|            |                           |