#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Det | aı | IS |

|-----|----|----|

|     |    |    |

E·XF

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437vit6wtr            |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |        | 6.3.29    | SD/SDIO MMC card host interface (SDIO) characteristics | 197 |

|----------|--------|-----------|--------------------------------------------------------|-----|

|          |        | 6.3.30    | RTC characteristics                                    | 198 |

| 7        | Packa  | ige info  | rmation                                                | 99  |

|          | 7.1    | LQFP10    | 0 package information                                  | 199 |

|          | 7.2    | WLCSP     | 143 package information 2                              | 203 |

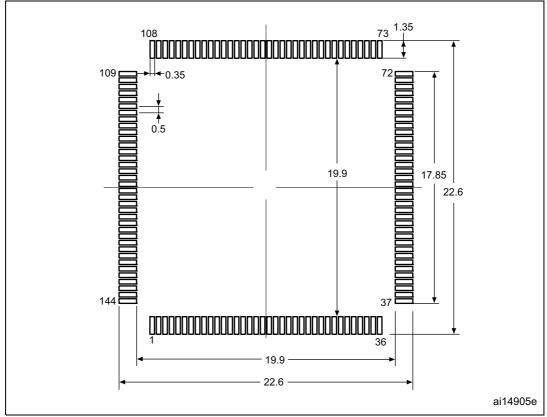

|          | 7.3    | LQFP14    | 4 package information                                  | 206 |

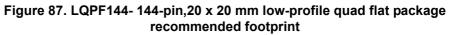

|          | 7.4    | LQFP17    | 6 package information                                  | 210 |

|          | 7.5    | LQFP20    | 8 package information                                  | 214 |

|          | 7.6    | UFBGA     | 169 package information                                | 218 |

|          | 7.7    | UFBGA     | 176+25 package information 2                           | 221 |

|          | 7.8    | TFBGA2    | 216 package information                                | 224 |

|          | 7.9    | Thermal   | characteristics                                        | 226 |

| 8        | Part n | umberi    | ng 2                                                   | 27  |

| Appendix | A Re   | ecomme    | endations when using internal reset OFF                | 228 |

|          | A.1    | Operatir  | ng conditions                                          | 228 |

| Appendix | B A    | oplicatio | on block diagrams 2                                    | 229 |

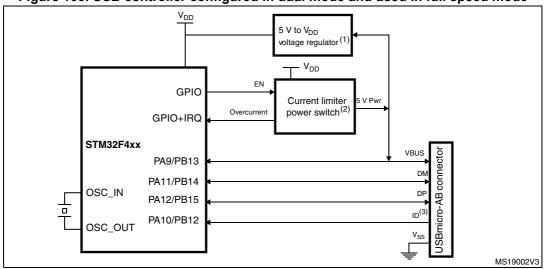

|          | B.1    | USB OT    | G full speed (FS) interface solutions                  | 229 |

|          | B.2    | USB OT    | G high speed (HS) interface solutions                  | 231 |

|          | B.3    | Etherne   | t interface solutions                                  | 232 |

| 9        | Revis  | ion hist  | ory                                                    | 234 |

FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). 256 bytes of SRAM are allocated for each CAN.

# 3.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 3.34 Universal serial bus on-the-go high-speed (OTG\_HS)

The devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1 Kbit × 35 with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

|         |         |          | Pin nu   | ımbei   | r        |         |          |                                                      |          |                 |       | · ·                                                                                                   |                            |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------------------------------|----------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                   | Additional<br>functions    |

| 22      | 33      | J4       | R1       | 39      | L10      | 42      | R1       | V <sub>DDA</sub>                                     | S        | -               | -     | -                                                                                                     | -                          |

| 23      | 34      | J5       | N3       | 40      | K9       | 43      | N3       | PA0-WKUP<br>(PA0)                                    | I/O      | FT              | (6)   | TIM2_CH1/TIM2_ETR,<br>TIM5_CH1, TIM8_ETR,<br>USART2_CTS,<br>UART4_TX,<br>ETH_MII_CRS,<br>EVENTOUT     | ADC123_<br>IN0/WKUP<br>(5) |

| 24      | 35      | K1       | N2       | 41      | K8       | 44      | N2       | PA1                                                  | I/O      | FT              | (5)   | TIM2_CH2, TIM5_CH2,<br>USART2_RTS,<br>UART4_RX,<br>ETH_MII_RX_CLK/ETH<br>_RMII_REF_CLK,<br>EVENTOUT   | ADC123_<br>IN1             |

| 25      | 36      | K2       | P2       | 42      | L9       | 45      | P2       | PA2                                                  | I/O      | FT              | (5)   | TIM2_CH3, TIM5_CH3,<br>TIM9_CH1,<br>USART2_TX,<br>ETH_MDIO,<br>EVENTOUT                               | ADC123_<br>IN2             |

| -       | -       | L2       | F4       | 43      | -        | 46      | K4       | PH2                                                  | I/O      | FT              | -     | ETH_MII_CRS,<br>FMC_SDCKE0,<br>LCD_R0, EVENTOUT                                                       | -                          |

| -       | -       | L1       | G4       | 44      | -        | 47      | J4       | PH3                                                  | I/O      | FT              | -     | ETH_MII_COL,<br>FMC_SDNE0, LCD_R1,<br>EVENTOUT                                                        | -                          |

| -       | -       | M2       | H4       | 45      | -        | 48      | H4       | PH4                                                  | I/O      | FT              | -     | I2C2_SCL,<br>OTG_HS_ULPI_NXT,<br>EVENTOUT                                                             | -                          |

| -       | -       | L3       | J4       | 46      | -        | 49      | J3       | PH5                                                  | I/O      | FT              | -     | I2C2_SDA, SPI5_NSS,<br>FMC_SDNWE,<br>EVENTOUT                                                         | -                          |

| 26      | 37      | K3       | R2       | 47      | M11      | 50      | R2       | PA3                                                  | I/O      | FT              | (5)   | TIM2_CH4, TIM5_CH4,<br>TIM9_CH2,<br>USART2_RX,<br>OTG_HS_ULPI_D0,<br>ETH_MII_COL,<br>LCD_B5, EVENTOUT | ADC123_<br>IN3             |

| 27      | 38      | -        | -        |         | -        | 51      | K6       | $V_{SS}$                                             | S        | -               | -     | -                                                                                                     | -                          |

## Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

| Pin name | CF  | NOR/PSRAM/<br>SRAM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |

|----------|-----|--------------------|------------------|--------|-------|

| PF0      | A0  | A0                 |                  |        | A0    |

| PF1      | A1  | A1                 |                  |        | A1    |

| PF2      | A2  | A2                 |                  |        | A2    |

| PF3      | A3  | A3                 |                  |        | A3    |

| PF4      | A4  | A4                 |                  |        | A4    |

| PF5      | A5  | A5                 |                  |        | A5    |

| PF12     | A6  | A6                 |                  |        | A6    |

| PF13     | A7  | A7                 |                  |        | A7    |

| PF14     | A8  | A8                 |                  |        | A8    |

| PF15     | A9  | A9                 |                  |        | A9    |

| PG0      | A10 | A10                |                  |        | A10   |

| PG1      |     | A11                |                  |        | A11   |

| PG2      |     | A12                |                  |        | A12   |

| PG3      |     | A13                |                  |        |       |

| PG4      |     | A14                |                  |        | BA0   |

| PG5      |     | A15                |                  |        | BA1   |

| PD11     |     | A16                | A16              | CLE    |       |

| PD12     |     | A17                | A17              | ALE    |       |

| PD13     |     | A18                | A18              |        |       |

| PE3      |     | A19                | A19              |        |       |

| PE4      |     | A20                | A20              |        |       |

| PE5      |     | A21                | A21              |        |       |

| PE6      |     | A22                | A22              |        |       |

| PE2      |     | A23                | A23              |        |       |

| PG13     |     | A24                | A24              |        |       |

| PG14     |     | A25                | A25              |        |       |

| PD14     | D0  | D0                 | DA0              | D0     | D0    |

| PD15     | D1  | D1                 | DA1              | D1     | D1    |

| PD0      | D2  | D2                 | DA2              | D2     | D2    |

| PD1      | D3  | D3                 | DA3              | D3     | D3    |

| PE7      | D4  | D4                 | DA4              | D4     | D4    |

| PE8      | D5  | D5                 | DA5              | D5     | D5    |

| PE9      | D6  | D6                 | DA6              | D6     | D6    |

| PE10     | D7  | D7                 | DA7              | D7     | D7    |

#### Table 11. FMC pin definition

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 8000- 0x4000 FFFF  | Reserved            |

|      | 0x4000 7C00 - 0x4000 7FFF | UART8               |

|      | 0x4000 7800 - 0x4000 7BFF | UART7               |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | Reserved            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | I2C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | Reserved            |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 13. STM32F437xx and STM32F439xx register boundary addresses (continued)

#### **Operating conditions** 6.3

#### 6.3.1 **General operating conditions**

| Table 17 | . General operating conditions |  |

|----------|--------------------------------|--|

|          |                                |  |

| Symbol                     | Parameter                                                                           | Conditions <sup>(1)</sup>                                                                                                    | Min                | Тур                | Max  | Unit  |     |

|----------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|-------|-----|

| f <sub>HCLK</sub> Ir       |                                                                                     | Power Scale 3 (VOS[1:0] bits<br>PWR_CR register = 0x01), Re<br>ON, over-drive OFF                                            |                    | 0                  | -    | - 120 |     |

|                            |                                                                                     | Power Scale 2 (VOS[1:0] bits                                                                                                 | Over-<br>drive OFF | 0                  | -    | 144   |     |

|                            | Internal AHB clock frequency                                                        | in PWR_CR register = 0x10),<br>Regulator ON                                                                                  | Over-<br>drive ON  | 0                  | -    | 168   |     |

|                            |                                                                                     | Power Scale 1 (VOS[1:0] bits<br>in PWR_CR register= 0x11),                                                                   | Over-<br>drive OFF | 0                  | -    | 168   | MHz |

|                            |                                                                                     | Regulator ON                                                                                                                 | Over-<br>drive ON  | 0                  | -    | 180   |     |

| f                          | Internal ADD1 clock froquency                                                       | Over-drive OFF                                                                                                               |                    | 0                  | -    | 42    |     |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                                                       | Over-drive ON                                                                                                                |                    | 0                  | -    | 45    |     |

| f                          | Internal ADP2 clock frequency                                                       | Over-drive OFF                                                                                                               | 0                  | -                  | 84   |       |     |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                                                       | Over-drive ON                                                                                                                |                    | 0                  | -    | 90    |     |

| $V_{DD}$                   | Standard operating voltage                                                          |                                                                                                                              | 1.7 <sup>(2)</sup> | -                  | 3.6  |       |     |

| V <sub>DDA</sub><br>(3)(4) | Analog operating voltage<br>(ADC limited to 1.2 M samples)                          |                                                                                                                              |                    | 1.7 <sup>(2)</sup> | -    | 2.4   | v   |

| (3)(4)                     | Analog operating voltage<br>(ADC limited to 2.4 M samples)                          | Must be the same potential as                                                                                                | VDD("/             | 2.4                | -    | 3.6   | v   |

| $V_{BAT}$                  | Backup operating voltage                                                            |                                                                                                                              |                    | 1.65               | -    | 3.6   |     |

|                            |                                                                                     | Power Scale 3 ((VOS[1:0] bits<br>PWR_CR register = 0x01), 12<br>HCLK max frequency                                           | 1.08               | 1.14               | 1.20 |       |     |

|                            | Regulator ON: 1.2 V internal voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins | Power Scale 2 ((VOS[1:0] bits<br>PWR_CR register = 0x10), 14<br>HCLK max frequency with ove<br>OFF or 168 MHz with over-driv | 1.20               | 1.26               | 1.32 |       |     |

| V <sub>12</sub>            |                                                                                     | Power Scale 1 ((VOS[1:0] bits<br>PWR_CR register = 0x11), 16<br>HCLK max frequency with ove<br>OFF or 180 MHz with over-driv | 1.26               | 1.32               | 1.40 | V     |     |

|                            | Regulator OFF: 1.2 V external                                                       | Max frequency 120 MHz                                                                                                        |                    | 1.10               | 1.14 | 1.20  | -   |

|                            | voltage must be supplied from external regulator on                                 | Max frequency 144 MHz                                                                                                        |                    | 1.20               | 1.26 | 1.32  |     |

|                            | $V_{CAP_1}/V_{CAP_2} pins^{(6)}$                                                    | Max frequency 168 MHz                                                                                                        | · ·                |                    |      |       |     |

| _                         |                     |         | 11      |         |        |

|---------------------------|---------------------|---------|---------|---------|--------|

| Peripheral                |                     | Scale 1 | Scale 2 | Scale 3 | Unit   |

|                           | SDIO                | 8.11    | 8.75    | 7.83    |        |

|                           | TIM1                | 17.11   | 15.97   | 14.17   |        |

|                           | TIM8                | 17.33   | 16.11   | 14.33   |        |

|                           | TIM9                | 7.22    | 6.67    | 6.00    |        |

| APB2<br>(up to<br>90 MHz) | TIM10               | 4.56    | 4.31    | 3.83    |        |

|                           | TIM11               | 4.78    | 4.44    | 4.00    |        |

|                           | ADC1 <sup>(5)</sup> | 4.67    | 4.31    | 3.83    |        |

|                           | ADC2 <sup>(5)</sup> | 4.78    | 4.44    | 4.00    |        |

|                           | ADC3 <sup>(5)</sup> | 4.56    | 4.17    | 3.67    |        |

|                           | SPI1                | 1.44    | 1.39    | 1.17    | µA/MHz |

|                           | USART1              | 4.00    | 3.75    | 3.33    |        |

|                           | USART6              | 4.00    | 3.75    | 3.33    |        |

|                           | SPI4                | 1.44    | 1.39    | 1.17    |        |

|                           | SPI5                | 1.44    | 1.39    | 1.17    |        |

|                           | SPI6                | 1.44    | 1.39    | 1.17    |        |

|                           | SYSCFG              | 0.78    | 0.69    | 0.67    |        |

|                           | LCD_TFT             | 39.89   | 37.22   | 33.17   |        |

|                           | SAI1                | 3.78    | 3.47    | 3.17    |        |

| Table 35. Peripheral current consumption (continued |

|-----------------------------------------------------|

|-----------------------------------------------------|

1. When the I/O compensation cell is ON,  $I_{\text{DD}}$  typical value increases by 0.22 mA.

2. The BusMatrix is automatically active when at least one master is ON.

3. To enable an I2S peripheral, first set the I2SMOD bit and then the I2SE bit in the SPI\_I2SCFGR register.

4. When the DAC is ON and EN1/2 bits are set in DAC\_CR register, add an additional power consumption of 0.8 mA per DAC channel for the analog part.

5. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

| Symbol                               | Parameter                                    | Condition                              | 5                  | Min          | Тур         | Мах                   | Unit |

|--------------------------------------|----------------------------------------------|----------------------------------------|--------------------|--------------|-------------|-----------------------|------|

|                                      |                                              |                                        | RMS                | -            | 25          | -                     |      |

| Jitter <sup>(3)</sup>                | Cycle-to-cycle jitter                        | System clock                           | peak<br>to<br>peak | -            | ±150        | -                     |      |

|                                      |                                              | 120 MHz                                | RMS                | -            | 15          | -                     |      |

|                                      | Period Jitter                                |                                        | peak<br>to<br>peak | -            | <u>+200</u> | -                     | ps   |

|                                      | Main clock output (MCO) for<br>RMII Ethernet | Cycle to cycle at 5<br>on 1000 samples | -                  | 32           | -           |                       |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet  | Cycle to cycle at 2 on 1000 samples    | -                  | 40           | -           |                       |      |

|                                      | Bit Time CAN jitter                          | Cycle to cycle at 2<br>on 1000 samples | -                  | 330          | -           |                       |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                 | VCO freq = 100 M                       | 1Hz                | 0.15         | _           | 0.40                  | mA   |

| יטט(PLL)                             |                                              | VCO freq = 432 M                       | 1Hz                | 0.45         | _           | -<br>-<br>-<br>-<br>- |      |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA                | VCO freq = 100 M<br>VCO freq = 432 M   |                    | 0.30<br>0.55 | -           |                       | mA   |

#### Table 43. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results.

| Symbol                  | Parameter                         | Conditions                                                              |                    | Min | Тур  | Мах  | Unit |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------|--------------------|-----|------|------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> |                                                                         |                    |     | 1    | 2.10 | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock    |                                                                         |                    | -   | -    | 216  | MHz  |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 |                                                                         |                    | 100 | -    | 432  | MHz  |

|                         |                                   | VCO freq = 100 MH:                                                      | Z                  | 75  | -    | 200  |      |

| t <sub>LOCK</sub>       | PLLI2S lock time                  | VCO freq = 432 MH:                                                      | 100                | -   | 300  | μs   |      |

| Jitter <sup>(3)</sup>   | Master 100 alash ütter            | Cycle to cycle at                                                       | RMS                | -   | 90   | -    |      |

|                         |                                   | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                            | peak<br>to<br>peak | -   | ±280 | -    | ps   |

|                         | Master I2S clock jitter           | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | -                  | 90  | -    | ps   |      |

|                         | WS I2S clock jitter               | Cycle to cycle at 48 on 1000 samples                                    | KHz                | -   | 400  | -    | ps   |

#### Table 44. PLLI2S (audio PLL) characteristics

## 6.3.15 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/ESDA/JEDEC JS-001 and ANSI/ESD S5.3.1 standards.

| Symbol                | Ratings                                            | Conditions                                                                                                        | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model) | T <sub>A</sub> = +25 °C conforming to<br>ANSI/ESDA/JEDEC JS-001                                                   | 2     | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device     | $T_A$ = +25 °C conforming to ANSI/ESD S5.3.1,<br>LQFP100/144/176, UFBGA169/176,<br>TFBGA176 and WLCSP143 packages | C3    | 250                             | V    |

|                       | model)                                             | $T_A = +25$ °C conforming to ANSI/ESD S5.3.1,<br>LQFP208 package                                                  | C3    | 250                             |      |

#### Table 53. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

#### Table 54. Electrical sensitivities

## 6.3.19 TIM timer characteristics

The parameters given in Table 60 are guaranteed by design.

Refer to Section 6.3.17: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                       | Conditions <sup>(3)</sup>                                            | Min | Max                     | Unit                 |  |  |  |

|------------------------|-------------------------------------------------|----------------------------------------------------------------------|-----|-------------------------|----------------------|--|--|--|

| t <sub>res(TIM)</sub>  | Timer resolution time                           | AHB/APBx prescaler=1<br>or 2 or 4, f <sub>TIMxCLK</sub> =<br>180 MHz | 1   | -                       | t <sub>TIMxCLK</sub> |  |  |  |

|                        |                                                 | AHB/APBx prescaler>4,<br>f <sub>TIMxCLK</sub> = 90 MHz               | 1   | -                       | t <sub>TIMxCLK</sub> |  |  |  |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 180 MHz                                       | 0   | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |  |

| Res <sub>TIM</sub>     | Timer resolution                                |                                                                      | -   | 16/32                   | bit                  |  |  |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count<br>with 32-bit counter   |                                                                      | -   | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |  |  |  |

| Table 60 | . TIMx | characteristics <sup>(1)(2)</sup> |

|----------|--------|-----------------------------------|

|----------|--------|-----------------------------------|

1. TIMx is used as a general term to refer to the TIM1 to TIM12 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 or APB2 is up to 180 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK = 4x PCLKx.

# 6.3.20 Communications interfaces

# I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0090 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 6.3.17: I/O port characteristics for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

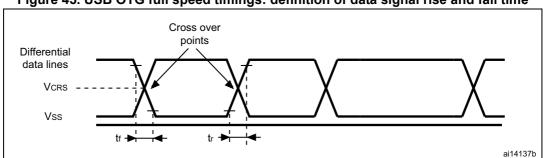

#### Figure 45. USB OTG full speed timings: definition of data signal rise and fall time

#### Table 67. USB OTG full speed electrical characteristics<sup>(1)</sup>

|                  | Driver characteristics                 |                                |     |     |      |  |  |  |  |

|------------------|----------------------------------------|--------------------------------|-----|-----|------|--|--|--|--|

| Symbol           | Parameter                              | Conditions Min                 |     | Max | Unit |  |  |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching               | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage        |                                | 1.3 | 2.0 | V    |  |  |  |  |

| Z <sub>DRV</sub> | Output driver impedance <sup>(3)</sup> | Driving high or<br>low         | 28  | 44  | Ω    |  |  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on DP (D+) and DM (D-) pins since the matching impedance is included in the embedded driver.

### USB high speed (HS) characteristics

Unless otherwise specified, the parameters given in *Table 70* for ULPI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 69* and  $V_{DD}$  supply voltage conditions summarized in *Table 68*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10, unless otherwise specified

- Capacitive load C = 30 pF, unless otherwise specified

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

| Symbol                      |  | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |  |  |  |  |

|-----------------------------|--|------------------------------|---------------------|---------------------|------|--|--|--|--|--|

| Input level V <sub>DD</sub> |  | USB OTG HS operating voltage | 1.7                 | 3.6                 | V    |  |  |  |  |  |

## Table 68. USB HS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

#### **Electrical characteristics**

| Symbol                           | Parameter                                  | Conditions                                                                           | Min. | Тур. | Max. | Unit |  |  |

|----------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|--|--|

| t <sub>SC</sub>                  | Control in (ULPI_DIR, ULPI_NXT) setup time |                                                                                      | 2    | -    | -    |      |  |  |

| t <sub>HC</sub>                  | Control in (ULPI_DIR, ULPI_NXT) hold time  |                                                                                      | 0.5  | -    | -    |      |  |  |

| t <sub>SD</sub>                  | Data in setup time                         |                                                                                      | 1.5  | -    | -    |      |  |  |

| t <sub>HD</sub>                  | Data in hold time                          |                                                                                      | 2    | -    | -    |      |  |  |

| t <sub>DC</sub> /t <sub>DD</sub> |                                            | 2.7 V < V <sub>DD</sub> < 3.6 V,<br>C <sub>L</sub> = 15 pF and<br>OSPEEDRy[1:0] = 11 | -    | 9    | 9.5  | ns   |  |  |

|                                  | Data/control output delay                  | 2.7 V < V <sub>DD</sub> < 3.6 V,<br>C <sub>L</sub> = 20 pF and<br>OSPEEDRy[1:0] = 10 | -    | - 12 | 15   |      |  |  |

|                                  |                                            | 1.7 V < V <sub>DD</sub> < 3.6 V,<br>C <sub>L</sub> = 15 pF and<br>OSPEEDRy[1:0] = 11 | -    | 1 12 |      |      |  |  |

Table 70. Dynamic characteristics: USB ULPI<sup>(1)</sup>

1. Guaranteed by characterization results.

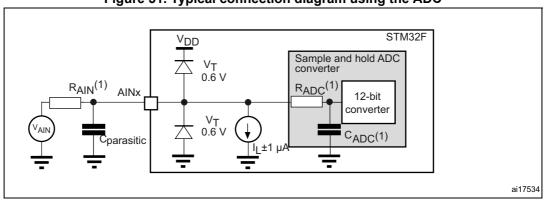

Figure 51. Typical connection diagram using the ADC

1. Refer to Table 74 for the values of  $\mathsf{R}_{\mathsf{AIN}},\,\mathsf{R}_{\mathsf{ADC}}\,\mathsf{and}\,\mathsf{C}_{\mathsf{ADC}}.$

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

# 6.3.23 V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            | Min | Тур | Мах | Unit |

|---------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 |     | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                |     | 4   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                                           | -1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy |     | -   | -   | μs   |

Table 82. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.24 Reference voltage

The parameters given in *Table 83* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                                | Parameter                                                        | Conditions                        | Min  | Тур  | Max  | Unit   |

|---------------------------------------|------------------------------------------------------------------|-----------------------------------|------|------|------|--------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                       | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the<br>internal reference voltage |                                   | 10   | -    | -    | μs     |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range     | $V_{DD}$ = 3V $\pm$ 10mV          | -    | 3    | 5    | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                          |                                   | -    | 30   | 50   | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                                     |                                   | -    | 6    | 10   | μs     |

Table 83. internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production

#### Table 84. Internal reference voltage calibration values

| Symbol          | Parameter                                                        | Memory address            |

|-----------------|------------------------------------------------------------------|---------------------------|

| $V_{REFIN}$ CAL | Raw data acquired at temperature of 30 $^\circ C_{VDDA}$ = 3.3 V | 0x1FFF 7A2A - 0x1FFF 7A2B |

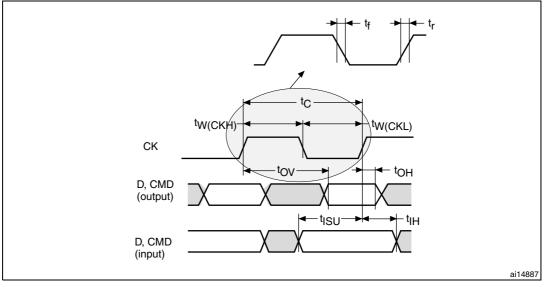

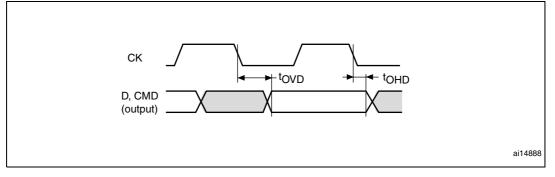

### 6.3.29 SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 108* for the SDIO/MMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

#### Figure 78. SDIO high-speed mode

Figure 79. SD default mode

1. Dimensions are expressed in millimeters.

| Sympol           | millimeters |       |        | inches <sup>(1)</sup> |        |        |  |

|------------------|-------------|-------|--------|-----------------------|--------|--------|--|

| Symbol           | Min         | Тур   | Мах    | Min                   | Тур    | Мах    |  |

| ZD               | -           | 1.250 | -      | -                     | 0.0492 | -      |  |

| Е                | 23.900      | -     | 24.100 | 0.9409                | -      | 0.9488 |  |

| HE               | 25.900      | -     | 26.100 | 1.0197                | -      | 1.0276 |  |

| ZE               | -           | 1.250 | -      | -                     | 0.0492 | -      |  |

| е                | -           | 0.500 | -      | -                     | 0.0197 | -      |  |

| L <sup>(2)</sup> | 0.450       | -     | 0.750  | 0.0177                | -      | 0.0295 |  |

| L1               | -           | 1.000 | -      | -                     | 0.0394 | -      |  |

| k                | 0°          | -     | 7°     | 0°                    | -      | 7°     |  |

| CCC              | -           | -     | 0.080  | -                     | -      | 0.0031 |  |

# Table 114. LQFP176 - 176-pin, 24 x 24 mm low-profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. L dimension is measured at gauge plane at 0.25 mm above the seating plane.

Figure 90. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

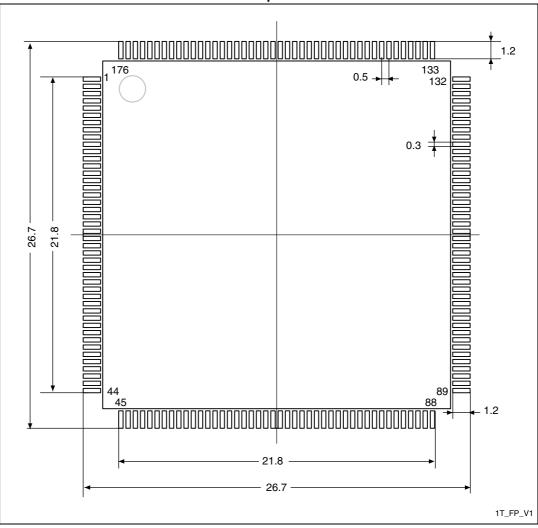

#### **Device marking for LQFP176**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Figure 91. LQFP176 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

Figure 105. USB controller configured in dual mode and used in full speed mode

- 1. External voltage regulator only needed when building a  $V_{\mbox{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

- 4. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.