# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| υ | е | ta | aı | IS |

|---|---|----|----|----|

|   |   |    |    |    |

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256К х 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437vit7tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 180 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 180 MHz while the maximum frequency of the high-speed APB domains is 90 MHz. The maximum allowed frequency of the low-speed APB domain is 45 MHz.

The devices embed a dedicated PLL (PLLI2S) and PLLSAI which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

### 3.15 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface. Refer to application note AN2606 for details.

### 3.16 Power supply schemes

- $V_{DD}$  = 1.7 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Note: V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

## 3.17 **Power supply supervisor**

### 3.17.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other package, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is

DocID024244 Rev 10

The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode: MR operates in normal mode (default mode of MR in stop mode) MR operates in under-drive mode (reduced leakage mode).

LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to Table 3 for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 22: Power supply scheme* and *Table 19: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. - means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

### 3.18.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 17: General operating conditions*. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 22: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

| Timer<br>type        | Timer               | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz)<br>(1) |

|----------------------|---------------------|-----------------------|-------------------------|---------------------------------------------|------------------------------|---------------------------------|-------------------------|------------------------------------|---------------------------------------|

| Advanced<br>-control | TIM1,<br>TIM8       | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | Yes                     | 90                                 | 180                                   |

|                      | TIM2,<br>TIM5       | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                      | 45                                 | 90/180                                |

| General              | TIM3,<br>TIM4       | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                      | 45                                 | 90/180                                |

|                      | TIM9                | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                      | 90                                 | 180                                   |

| purpose              | TIM10<br>,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                      | 90                                 | 180                                   |

|                      | TIM12               | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                      | 45                                 | 90/180                                |

|                      | TIM13<br>,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                      | 45                                 | 90/180                                |

| Basic                | TIM6,<br>TIM7       | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 0                               | No                      | 45                                 | 90/180                                |

Table 6. Timer feature comparison

1. The maximum timer clock is either 90 or 180 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

### 3.22.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

### 3.22.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.22.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 3.23 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the standard (up to 100 KHz), and fast (up to 400 KHz) modes. They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see *Table 7*).

|                                     | Analog filter | Digital filter                                            |

|-------------------------------------|---------------|-----------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns       | Programmable length from 1 to 15<br>I2C peripheral clocks |

### Table 7. Comparison of I2C analog and digital filters

# 3.24 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and four universal asynchronous receiver transmitters (UART4, UART5, UART7, and UART8).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to

# 3.26 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available. They can be operated in master or slave mode, in full duplex and simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

Note: For I2S2 full-duplex mode, I2S2\_CK and I2S2\_WS signals can be used only on GPIO Port B and GPIO Port D.

# 3.27 Serial Audio interface (SAI1)

The serial audio interface (SAI1) is based on two independent audio sub-blocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both sub-blocks can be configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

SAI1 can be served by the DMA controller.

## 3.28 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S/SAI flow with an external PLL (or Codec output).

# 3.29 Audio and LCD PLL(PLLSAI)

An additional PLL dedicated to audio and LCD-TFT is used for SAI1 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the LCD-TFT clock.

Fast I/O handling allowing maximum I/O toggling up to 90 MHz.

## 3.39 Analog-to-digital converters (ADCs)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4, TIM5, or TIM8 timer.

### 3.40 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

# 3.41 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 10-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

|         |         |           | Pin nı   | Imbe    | r        |         |          |                                                      |          |                 |       | •                                                                             |                         |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                           | Additional<br>functions |

| -       | 10      | F2        | E2       | 16      | F11      | 16      | D2       | PF0                                                  | I/O      | FT              | -     | I2C2_SDA, FMC_A0,<br>EVENTOUT                                                 | -                       |

| -       | 11      | F3        | H3       | 17      | E9       | 17      | E2       | PF1                                                  | I/O      | FT              | -     | I2C2_SCL, FMC_A1,<br>EVENTOUT                                                 | -                       |

| -       | 12      | G5        | H2       | 18      | F10      | 18      | G2       | PF2                                                  | I/O      | FT              | -     | I2C2_SMBA, FMC_A2,<br>EVENTOUT                                                | -                       |

| -       | -       | -         | -        | -       | -        | 19      | E3       | PI12                                                 | I/O      | FT              | -     | LCD_HSYNC,<br>EVENTOUT                                                        | -                       |

| -       | -       | -         | -        | -       | -        | 20      | G3       | PI13                                                 | I/O      | FT              | -     | LCD_VSYNC,<br>EVENTOUT                                                        | -                       |

| -       | -       | -         | -        | -       | -        | 21      | H3       | PI14                                                 | I/O      | FT              |       | LCD_CLK, EVENTOUT                                                             | -                       |

| -       | 13      | G4        | J2       | 19      | G11      | 22      | H2       | PF3                                                  | I/O      | FT              | (5)   | FMC_A3, EVENTOUT                                                              | ADC3_IN9                |

| -       | 14      | G3        | J3       | 20      | F9       | 23      | J2       | PF4                                                  | I/O      | FT              | (5)   | FMC_A4, EVENTOUT                                                              | ADC3_<br>IN14           |

| -       | 15      | H3        | K3       | 21      | F8       | 24      | K3       | PF5                                                  | I/O      | FT              | (5)   | FMC_A5, EVENTOUT                                                              | ADC3_<br>IN15           |

| 10      | 16      | G7        | G2       | 22      | H7       | 25      | H6       | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                             | -                       |

| 11      | 17      | G8        | G3       | 23      | -        | 26      | H5       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                             | -                       |

| -       | 18      | NC<br>(2) | K2       | 24      | G10      | 27      | K2       | PF6                                                  | I/O      | FT              | (5)   | TIM10_CH1,<br>SPI5_NSS,<br>SAI1_SD_B,<br>UART7_Rx,<br>FMC_NIORD,<br>EVENTOUT  | ADC3_IN4                |

| -       | 19      | NC<br>(2) | K1       | 25      | F7       | 28      | K1       | PF7                                                  | I/O      | FT              | (5)   | TIM11_CH1,<br>SPI5_SCK,<br>SAI1_MCLK_B,<br>UART7_Tx,<br>FMC_NREG,<br>EVENTOUT | ADC3_IN5                |

| -       | 20      | NC<br>(2) | L3       | 26      | H11      | 29      | L3       | PF8                                                  | I/O      | FT              | (5)   | SPI5_MISO,<br>SAI1_SCK_B,<br>TIM13_CH1,<br>FMC_NIOWR,<br>EVENTOUT             | ADC3_IN6                |

| Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued) | Table 10. | STM32F437xx and | STM32F439xx | pin and ball | definitions | (continued) |

|----------------------------------------------------------------------------|-----------|-----------------|-------------|--------------|-------------|-------------|

|----------------------------------------------------------------------------|-----------|-----------------|-------------|--------------|-------------|-------------|

|         |         |          | Pin nu   | ımbei   | r        |         |          |                                                      |          |                 |       | · ·                                                                                                   |                            |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------------------------------|----------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                   | Additional<br>functions    |

| 22      | 33      | J4       | R1       | 39      | L10      | 42      | R1       | V <sub>DDA</sub>                                     | S        | -               | -     | -                                                                                                     | -                          |

| 23      | 34      | J5       | N3       | 40      | K9       | 43      | N3       | PA0-WKUP<br>(PA0)                                    | I/O      | FT              | (6)   | TIM2_CH1/TIM2_ETR,<br>TIM5_CH1, TIM8_ETR,<br>USART2_CTS,<br>UART4_TX,<br>ETH_MII_CRS,<br>EVENTOUT     | ADC123_<br>IN0/WKUP<br>(5) |

| 24      | 35      | K1       | N2       | 41      | K8       | 44      | N2       | PA1                                                  | I/O      | FT              | (5)   | TIM2_CH2, TIM5_CH2,<br>USART2_RTS,<br>UART4_RX,<br>ETH_MII_RX_CLK/ETH<br>_RMII_REF_CLK,<br>EVENTOUT   | ADC123_<br>IN1             |

| 25      | 36      | K2       | P2       | 42      | L9       | 45      | P2       | PA2                                                  | I/O      | FT              | (5)   | TIM2_CH3, TIM5_CH3,<br>TIM9_CH1,<br>USART2_TX,<br>ETH_MDIO,<br>EVENTOUT                               | ADC123_<br>IN2             |

| -       | -       | L2       | F4       | 43      | -        | 46      | K4       | PH2                                                  | I/O      | FT              | -     | ETH_MII_CRS,<br>FMC_SDCKE0,<br>LCD_R0, EVENTOUT                                                       | -                          |

| -       | -       | L1       | G4       | 44      | -        | 47      | J4       | PH3                                                  | I/O      | FT              | -     | ETH_MII_COL,<br>FMC_SDNE0, LCD_R1,<br>EVENTOUT                                                        | -                          |

| -       | -       | M2       | H4       | 45      | -        | 48      | H4       | PH4                                                  | I/O      | FT              | -     | I2C2_SCL,<br>OTG_HS_ULPI_NXT,<br>EVENTOUT                                                             | -                          |

| -       | -       | L3       | J4       | 46      | -        | 49      | J3       | PH5                                                  | I/O      | FT              | -     | I2C2_SDA, SPI5_NSS,<br>FMC_SDNWE,<br>EVENTOUT                                                         | -                          |

| 26      | 37      | K3       | R2       | 47      | M11      | 50      | R2       | PA3                                                  | I/O      | FT              | (5)   | TIM2_CH4, TIM5_CH4,<br>TIM9_CH2,<br>USART2_RX,<br>OTG_HS_ULPI_D0,<br>ETH_MII_COL,<br>LCD_B5, EVENTOUT | ADC123_<br>IN3             |

| 27      | 38      | -        | -        |         | -        | 51      | K6       | $V_{SS}$                                             | S        | -               | -     | -                                                                                                     | -                          |

### Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

#### **Operating conditions** 6.3

#### 6.3.1 **General operating conditions**

| Table 17 | . General operating conditions |  |

|----------|--------------------------------|--|

|          |                                |  |

| Symbol                     | Parameter                                                                           | Conditions <sup>(1)</sup>                                                                                                    |                    | Min                | Тур  | Max  | Unit |

|----------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|------|------|

|                            |                                                                                     | Power Scale 3 (VOS[1:0] bits<br>PWR_CR register = 0x01), Re<br>ON, over-drive OFF                                            |                    | 0                  | -    | 120  |      |

| f <sub>HCLK</sub>          |                                                                                     | Power Scale 2 (VOS[1:0] bits                                                                                                 | Over-<br>drive OFF | 0                  | -    | 144  |      |

|                            | Internal AHB clock frequency                                                        | in PWR_CR register = 0x10),<br>Regulator ON                                                                                  | Over-<br>drive ON  | 0                  | -    | 168  |      |

|                            |                                                                                     | Power Scale 1 (VOS[1:0] bits<br>in PWR_CR register= 0x11),                                                                   | Over-<br>drive OFF | 0                  | -    | 168  | MHz  |

|                            |                                                                                     | Regulator ON                                                                                                                 | Over-<br>drive ON  | 0                  | -    | 180  |      |

| f                          | Internal ADD1 clock froquency                                                       | Over-drive OFF                                                                                                               | 0                  | -                  | 42   |      |      |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                                                       | Over-drive ON                                                                                                                | 0                  | -                  | 45   |      |      |

| f                          | Internal ADP2 clock frequency                                                       | Over-drive OFF                                                                                                               | 0                  | -                  | 84   |      |      |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                                                       | Over-drive ON                                                                                                                |                    | 0                  | -    | 90   |      |

| $V_{DD}$                   | Standard operating voltage                                                          |                                                                                                                              |                    | 1.7 <sup>(2)</sup> | -    | 3.6  |      |

| V <sub>DDA</sub><br>(3)(4) | Analog operating voltage<br>(ADC limited to 1.2 M samples)                          |                                                                                                                              | 1.7 <sup>(2)</sup> | -                  | 2.4  | - V  |      |

| (3)(4)                     | Analog operating voltage<br>(ADC limited to 2.4 M samples)                          | Must be the same potential as                                                                                                | 2.4                | -                  | 3.6  |      |      |

| $V_{BAT}$                  | Backup operating voltage                                                            |                                                                                                                              |                    | 1.65               | -    | 3.6  |      |

|                            |                                                                                     | Power Scale 3 ((VOS[1:0] bits<br>PWR_CR register = 0x01), 12<br>HCLK max frequency                                           |                    | 1.08               | 1.14 | 1.20 |      |

|                            | Regulator ON: 1.2 V internal voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins | Power Scale 2 ((VOS[1:0] bits<br>PWR_CR register = 0x10), 14<br>HCLK max frequency with ove<br>OFF or 168 MHz with over-driv | 1.20               | 1.26               | 1.32 | V    |      |

| V <sub>12</sub>            |                                                                                     | Power Scale 1 ((VOS[1:0] bits<br>PWR_CR register = 0x11), 16<br>HCLK max frequency with ove<br>OFF or 180 MHz with over-driv | 1.26               | 1.32               | 1.40 |      |      |

|                            | Regulator OFF: 1.2 V external                                                       | Max frequency 120 MHz                                                                                                        | 1.10               | 1.14               | 1.20 |      |      |

|                            | voltage must be supplied from external regulator on                                 | Max frequency 144 MHz                                                                                                        |                    | 1.20               | 1.26 | 1.32 |      |

|                            | $V_{CAP_1}/V_{CAP_2} pins^{(6)}$                                                    | Max frequency 168 MHz                                                                                                        | 1.26               | 1.32               | 1.38 | 1    |      |

### **On-chip peripheral current consumption**

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- I/O compensation cell enabled.

- The ART accelerator is ON.

- Scale 1 mode selected, internal digital voltage V12 = 1.32 V.

- HCLK is the system clock. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- $f_{HCLK}$  = 180 MHz (Scale1 + over-drive ON),  $f_{HCLK}$  = 144 MHz (Scale 2),  $f_{HCLK}$  = 120 MHz (Scale 3)"

- Ambient operating temperature is 25 °C and  $V_{DD}$ =3.3 V.

| Table 35. Peripheral current consumption |                                                    |                                     |                                       |         |        |  |  |  |  |  |  |

|------------------------------------------|----------------------------------------------------|-------------------------------------|---------------------------------------|---------|--------|--|--|--|--|--|--|

| E                                        | Peripheral                                         |                                     | I <sub>DD</sub> ( Typ) <sup>(1)</sup> |         | Unit   |  |  |  |  |  |  |

|                                          | rempheral                                          | Scale 1                             | Scale 2                               | Scale 3 |        |  |  |  |  |  |  |

|                                          | GPIOA                                              | 2.50                                | 2.36                                  | 2.08    |        |  |  |  |  |  |  |

|                                          | GPIOB                                              | 2.56                                | 2.36                                  | 2.08    |        |  |  |  |  |  |  |

|                                          | GPIOC                                              | 2.44                                | 2.29                                  | 2.00    |        |  |  |  |  |  |  |

|                                          | GPIOD                                              | 2.50                                | 2.36                                  | 2.08    | -      |  |  |  |  |  |  |

|                                          | GPIOE                                              | 2.44                                | 2.29                                  | 2.00    | -      |  |  |  |  |  |  |

|                                          | GPIOF                                              | 2.44                                | 2.29                                  | 2.00    | -      |  |  |  |  |  |  |

|                                          | GPIOG                                              | 2.39                                | 2.22                                  | 2.00    | -      |  |  |  |  |  |  |

|                                          | GPIOH                                              | 2.33                                | 2.15                                  | 1.92    | -      |  |  |  |  |  |  |

|                                          | GPIOI                                              | 2.39                                | 2.22                                  | 2.00    | -      |  |  |  |  |  |  |

| AHB1                                     | GPIOJ                                              | 2.33                                | 2.15                                  | 1.92    |        |  |  |  |  |  |  |

| (up to<br>180 MHz)                       | GPIOK                                              | 2.33                                | 2.15                                  | 1.92    | µA/MHz |  |  |  |  |  |  |

| 100 101 12)                              | OTG_HS+ULPI                                        | 27.00                               | 24.86                                 | 21.92   | -      |  |  |  |  |  |  |

|                                          | CRC                                                | 0.44                                | 0.42                                  | 0.33    | -      |  |  |  |  |  |  |

|                                          | BKPSRAM                                            | 0.78                                | 0.69                                  | 0.58    | -      |  |  |  |  |  |  |

|                                          | DMA1                                               | 25.33                               | 23.26                                 | 20.50   | -      |  |  |  |  |  |  |

|                                          | DMA2                                               | 24.72                               | 22.71                                 | 20.00   |        |  |  |  |  |  |  |

|                                          | DMA2D                                              | 28.50                               | 26.32                                 | 23.33   |        |  |  |  |  |  |  |

|                                          | ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX | 21.56                                 | 20.07   | 17.75  |  |  |  |  |  |  |

### Table 35. Peripheral current consumption

### 6.3.26 FMC characteristics

Unless otherwise specified, the parameters given in *Table 86* to *Table 101* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10 except at V<sub>DD</sub> range 1.7 to 2.1V where OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

### Asynchronous waveforms and timings

*Figure 55* through *Figure 58* represent asynchronous waveforms and *Table 86* through *Table 93* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode , DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

- For SDRAM memories,  $V_{DD}$  ranges from 2.7 to 3.6 V and maximum frequency FMC\_SDCLK = 90 MHz

- For Mobile LPSDR SDRAM memories, V<sub>DD</sub> ranges from 1.7 to 1.95 V and maximum frequency FMC\_SDCLK = 84 MHz

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL_Data</sub> )  | Data output valid time | -                        | 3.5                     |      |

| t <sub>h(SDCLKL</sub> _Data)  | Data output hold time  | 0                        | -                       |      |

| $t_{d(SDCLKL_Add)}$           | Address valid time     | -                        | 1.5                     |      |

| t <sub>d(SDCLKL_SDNWE)</sub>  | SDNWE valid time       | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNWE)</sub>  | SDNWE hold time        | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 0.5                     | ns   |

| t <sub>h(SDCLKLSDNE)</sub>    | Chip select hold time  | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 2                       |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 0.5                     |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_NBL)</sub>    | NBL valid time         | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_NBL)</sub>    | NBLoutput time         | 0                        | -                       |      |

# Table 104. SDRAM write timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

# Table 105. LPSDR SDRAM write timings<sup>(1)(2)</sup>

| Symbol                         | Parameter              | Min                      | Max                     | Unit |

|--------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>          | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL _Data</sub> )  | Data output valid time | -                        | 5                       |      |

| t <sub>h(SDCLKL</sub> _Data)   | Data output hold time  | 2                        | -                       |      |

| $t_{d(SDCLKL_Add)}$            | Address valid time     | -                        | 2.8                     |      |

| t <sub>d(SDCLKL-SDNWE)</sub>   | SDNWE valid time       | -                        | 2                       |      |

| t <sub>h(SDCLKL-SDNWE)</sub>   | SDNWE hold time        | 1                        | -                       |      |

| t <sub>d(SDCLKL</sub> - SDNE)  | Chip select valid time | -                        | 1.5                     |      |

| t <sub>h(SDCLKL</sub> - SDNE)  | Chip select hold time  | 1                        | -                       | ns   |

| t <sub>d</sub> (SDCLKL-SDNRAS) | SDNRAS valid time      | -                        | 1.5                     |      |

| t <sub>h(SDCLKL-SDNRAS)</sub>  | SDNRAS hold time       | 1.5                      | -                       |      |

| t <sub>d</sub> (SDCLKL-SDNCAS) | SDNCAS valid time      | -                        | 1.5                     |      |

| t <sub>d</sub> (SDCLKL-SDNCAS) | SDNCAS hold time       | 1.5                      | -                       |      |

| $t_{d(SDCLKL_NBL)}$            | NBL valid time         | -                        | 1.5                     |      |

| t <sub>h(SDCLKL-NBL)</sub>     | NBL output time        | putput time 1.5 -        |                         |      |

1. CL = 10 pF.

2. Guaranteed by characterization results.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

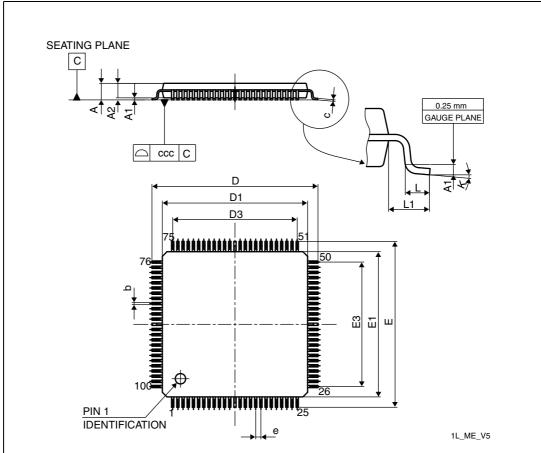

# 7.1 LQFP100 package information

Figure 80. LQFP100 -100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

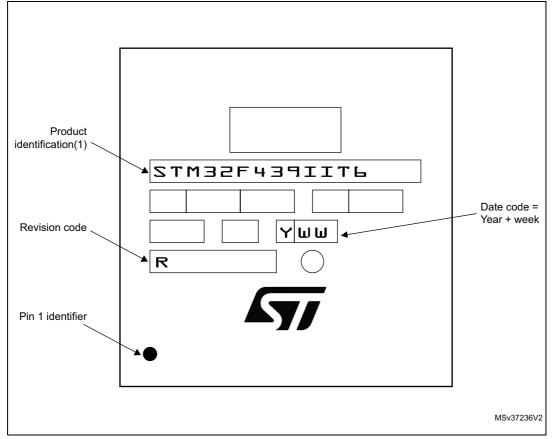

### **Device marking for LQFP176**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Figure 91. LQFP176 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

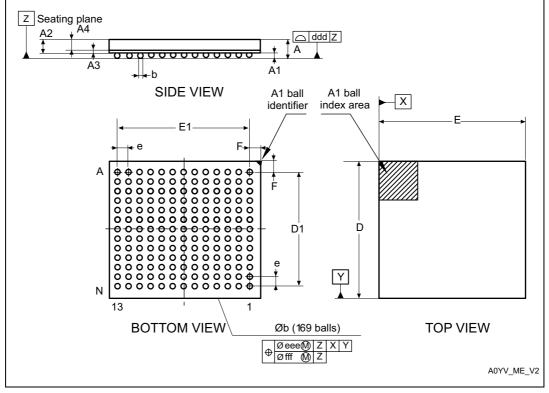

# 7.6 UFBGA169 package information

Figure 95. UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 116. UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid arraypackage mechanical data

| Cumula al | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|-----------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol    | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А         | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |

| A1        | 0.050       | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |  |

| A2        | 0.400       | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |  |

| A3        | -           | 0.130 | -     | -                     | 0.0051 | -      |  |

| A4        | 0.270       | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |  |

| b         | 0.230       | 0.280 | 0.330 | 0.0091                | 0.0110 | 0.0130 |  |

| D         | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| D1        | 5.950       | 6.000 | 6.050 | 0.2343                | 0.2362 | 0.2382 |  |

| Е         | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| E1        | 5.950       | 6.000 | 6.050 | 0.2343                | 0.2362 | 0.2382 |  |

| е         | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

# Table 118. UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch,ultra fine pitch ball grid array package mechanical data (continued)

| Symbol |      | millimeters |       |      |      |        |

|--------|------|-------------|-------|------|------|--------|

| Symbol | Min. | Тур.        | Max.  | Min. | Тур. | Max.   |

| eee    | -    | -           | 0.150 | -    | -    | 0.0059 |

| fff    | -    | -           | 0.050 | -    | -    | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

### Figure 99. UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package recommended footprint

| 000000000000000000000000000000000000    |            |

|-----------------------------------------|------------|

| 0000 0000                               |            |

| 000000000000000000000000000000000000000 |            |

| 000000000000000000000000000000000000000 | A0E7_FP_V1 |

### Table 119. UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA) Image: Commended PCB design rules (0.65 mm pitch BGA) Image: Commended PCB design rules (0.65 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.65 mm                                                          |

| Dpad              | 0.300 mm                                                         |

| Dsm               | 0.400 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.300 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

# 8 Part numbering

| Table 122. Ordering infor                                                                        | mation sc | heme |       |    |   |     |

|--------------------------------------------------------------------------------------------------|-----------|------|-------|----|---|-----|

| Example:                                                                                         | STM32     | F    | 439 V | ΙT | 6 | ххх |

| Device family                                                                                    |           |      |       |    |   |     |

| STM32 = ARM-based 32-bit microcontroller                                                         |           |      |       |    |   |     |

| Product type                                                                                     |           |      |       |    |   |     |

| F = general-purpose                                                                              |           |      |       |    |   |     |

| Device subfamily                                                                                 |           |      |       |    |   |     |

| 437= STM32F437xx, USB OTG FS/HS, camera interface,<br>Ethernet, cryptographic acceleration       |           |      |       |    |   |     |

| 439= STM32F439xx, USB OTG FS/HS, camera interface, Ethernet, LCD-TFT, cryptographic acceleration |           |      |       |    |   |     |

| Pin count                                                                                        |           |      |       |    |   |     |

| V = 100 pins                                                                                     |           |      |       |    |   |     |

| Z = 143 and 144 pins                                                                             |           |      |       |    |   |     |

| A = 169 pins                                                                                     |           |      |       |    |   |     |

| I = 176 pins                                                                                     |           |      |       |    |   |     |

| B = 208 pins                                                                                     |           |      |       |    |   |     |

| N = 216 pins                                                                                     |           |      |       |    |   |     |

| Flash memory size                                                                                |           |      |       |    |   |     |

| G = 1024 Kbytes of Flash memory                                                                  |           |      |       |    |   |     |

| I = 2048 Kbytes of Flash memory                                                                  |           |      |       |    |   |     |

| Package                                                                                          |           |      |       |    |   |     |

| T = LQFP                                                                                         |           |      |       |    |   |     |

| H = BGA                                                                                          |           |      |       |    |   |     |

| Y = WLCSP                                                                                        |           |      |       |    |   |     |

| Temperature range                                                                                |           |      |       |    |   |     |

| 6 = Industrial temperature range, $-40$ to 85 °C.                                                |           |      |       |    |   |     |

| 7 = Industrial temperature range, -40 to 105 °C.                                                 |           |      |       |    |   |     |

| Options                                                                                          |           |      |       |    |   |     |

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID024244 Rev 10

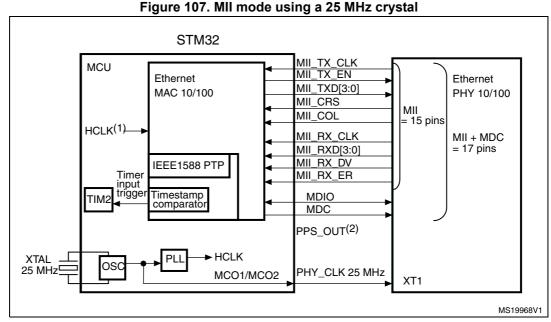

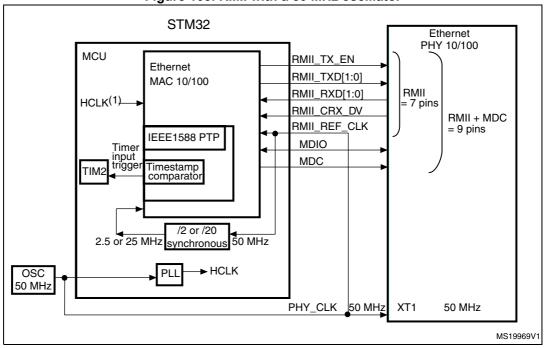

# **B.3** Ethernet interface solutions

1.  $f_{HCLK}$  must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

### Figure 108. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 12-Aug-2013 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 10-Sep-2013 | 2        | Added STM32F439xx part numbers and related informations.<br><b>STM32F437xx part numbers:</b><br>Replaced FSMC by FMC added Chrom-ART Accelerator and SAI<br>interface.<br>Increased core, timer, GPIOs, SPI maximum frequencies<br>Updated Figure 4: STM32F437xx and STM32F439xx block diagram.<br>Updated Figure 5: STM32F437xx and STM32F439xx Multi-AHB<br>matrix.<br>Removed note in Section -: Standby mode.<br>Updated Figure 14: STM32F437xx and STM32F439xx pin and ball<br>definitions and Table 12: STM32F437xx and STM32F439xx alternate<br>function mapping<br>Modified Figure 19: Memory map.<br>Updated Table 17: General operating conditions, Table 18: Limitations<br>depending on the operating power supply range. Removed note 1 in<br>Table 22: reset and power control block characteristics. Added<br>Table 23: Over-drive switching characteristics.<br>Updated Section : Typical and maximum current consumption,<br>Table 34: Switching output I/O current consumption, Table 35:<br>Peripheral current consumption and Section : On-chip peripheral<br>current consumption.<br>Updated Table 36: Low-power mode wakeup timings.<br>Modified Section : High-speed external user clock generated<br>from an external source, and Section 6.3.10: Internal clock source<br>characteristics.<br>Updated Table 43: Main PLL characteristics and Table 45: PLLISAI<br>(audio and LCD-TFT PLL) characteristics.<br>Updated Table 57: Output voltage characteristics and Table 58: I/O AC<br>characteristics.<br>Updated Table 60: TIMx characteristics, Table 61: I2C characteristics,<br>Table 62: SPI dynamic characteristics, Section : SAI characteristics,<br>Table 62: SPI dynamic characteristics, Section : SAI characteristics,<br>Updated Table 60: TIMx characteristics, Table 61: I2C characteristics,<br>Updated Table 60: TIMx characteristics, Section : SAI characteristics,<br>Updated Table 60: SDRAM read timings and Table 104: SDRAM write<br>timings. |  |

| Table 124. | Document revision history |

|------------|---------------------------|

|            |                           |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24-Apr-2014 | 5        | Changed SVGA (800x600) into XGA1024x768) on cover page and in<br>Section 3.10: LCD-TFT controller (available only on STM32F439xx).<br>Added DCMI_VSYNC alternate function on PG9 and updated note 6.<br>in Table 10: STM32F437xx and STM32F439xx pin and ball definitions<br>and Table 12: STM32F437xx and STM32F439xx alternate function<br>mapping. Added note 2.belowFigure 16: STM32F43x UFBGA169<br>ballout.<br>Updated Section 3.18.2: Regulator OFF.<br>Updated signal corresponding to pin L5 in Figure 12: STM32F43x<br>WLCSP143 ballout.<br>Updated Table 53: ESD absolute maximum ratings.<br>Updated V <sub>IH</sub> in Table 56: I/O static characteristics. Added condition<br>$V_{DD}$ >1.7 V in Table 56: I/O AC characteristics.<br>Added ACC <sub>HSE</sub> in Table 39: HSE 4-26 MHz oscillator characteristics<br>and ACC <sub>LSE</sub> in Table 40: LSE oscillator characteristics (fLSE = 32.768<br>kHz).<br>Removed note 3 in Table 80: Temperature sensor characteristics.<br>Added Figure 82: LQFP100 marking example (package top view),<br>Figure 85: WLCSP143 marking example (package top view),<br>Figure 85: LQFP144 marking example (package top view),<br>Figure 88: LQFP144 marking example (package top view),<br>Figure 87: WLCSP143 marking example (package top view),<br>Figure 88: LQFP144 marking example (package top view),<br>Figure 88: LQFP144 marking example (package top view),<br>Figure 87: UCSP143 marking example (package top view),<br>Figure 88: LQFP144 marking example (package top view),<br>Figure 88: LQFP144 marking example (package top view),<br>Figure 87: UCSP143 marking example (package top view),<br>Figure 88: LQFP144 marking example (package top vi |

| Table 124. | Document | revision | history | (continued) |

|------------|----------|----------|---------|-------------|

|            |          |          |         |             |