#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 1MB (1M × 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 144-LQFP                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437zgt6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 Functional overview

# 3.1 **ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU and embedded Flash and SRAM**

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core is a 32-bit RISC processor that features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F43x family is compatible with all ARM tools and software.

*Figure 4* shows the general block diagram of the STM32F43x family.

Note: Cortex-M4 with FPU core is binary compatible with the Cortex-M3 core.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 225 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART Accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 180 MHz.

# 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

### 3.4 Embedded Flash memory

The devices embed a Flash memory of up to 2 Mbytes available for storing programs and data.

# 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.6 Embedded SRAM

All devices embed:

- Up to 256Kbytes of system SRAM including 64 Kbytes of CCM (core coupled memory) data RAM

- RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

- 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM, FMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDIO

- Cryptographic acceleration

- Camera interface (DCMI)

- ADC

- SAI1.

## **3.9** Flexible memory controller (FMC)

All devices embed an FMC. It has four Chip Select outputs supporting the following modes: PCCard/Compact Flash, SDRAM/LPSDR SDRAM, SRAM, PSRAM, NOR Flash and NAND Flash.

Functionality overview:

- 8-,16-, 32-bit data bus width

- Read FIFO for SDRAM controller

- Write FIFO

- Maximum FMC\_CLK/FMC\_SDCLK frequency for synchronous accesses is 90 MHz.

#### LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

# 3.10 LCD-TFT controller (available only on STM32F439xx)

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 displays layers with dedicated FIFO (64x32-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 Input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events.

|         |         |           | Pin nu   | ımbei   | r        |         |          |                                                      |          |                 |            |                                                                                          |                              |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|------------|------------------------------------------------------------------------------------------|------------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes      | Alternate functions                                                                      | Additional<br>functions      |

| 4       | 4       | D1        | B2       | 4       | D9       | 4       | B1       | PE5                                                  | I/O      | FT              | -          | TRACED2, TIM9_CH1,<br>SPI4_MISO,<br>SAI1_SCK_A,<br>FMC_A21, DCMI_D6,<br>LCD_G0, EVENTOUT | -                            |

| 5       | 5       | D2        | B3       | 5       | E8       | 5       | B2       | PE6                                                  | I/O      | FT              | _          | TRACED3, TIM9_CH2,<br>SPI4_MOSI,<br>SAI1_SD_A, FMC_A22,<br>DCMI_D7, LCD_G1,<br>EVENTOUT  | -                            |

| -       | -       | -         | -        | -       | -        | I       | G6       | V <sub>SS</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | -         | -        | -       | -        | -       | F5       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| 6       | 6       | E5        | C1       | 6       | C11      | 6       | C1       | V <sub>BAT</sub>                                     | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | NC<br>(2) | D2       | 7       | -        | 7       | C2       | PI8                                                  | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | TAMP_2                       |

| 7       | 7       | E4        | D1       | 8       | D10      | 8       | D1       | PC13                                                 | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | TAMP_1                       |

| 8       | 8       | E1        | E1       | 9       | D11      | 9       | E1       | PC14-<br>OSC32_IN<br>(PC14)                          | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | OSC32_IN                     |

| 9       | 9       | F1        | F1       | 10      | E11      | 10      | F1       | PC15-<br>OSC32_OUT<br>(PC15)                         | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | OSC32_<br>OUT <sup>(5)</sup> |

| -       | -       | -         | -        | -       | -        | -       | G5       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | E2        | D3       | 11      | -        | 11      | E4       | PI9                                                  | I/O      | FT              | -          | CAN1_RX, FMC_D30,<br>LCD_VSYNC,<br>EVENTOUT                                              | -                            |

| -       | -       | E3        | E3       | 12      | -        | 12      | D5       | PI10                                                 | I/O      | FT              | -          | ETH_MII_RX_ER,<br>FMC_D31,<br>LCD_HSYNC,<br>EVENTOUT                                     | -                            |

| -       | -       | NC<br>(2) | E4       | 13      | -        | 13      | F3       | PI11                                                 | I/O      | FT              | -          | OTG_HS_ULPI_DIR,<br>EVENTOUT                                                             | -                            |

| -       | -       | F6        | F2       | 14      | E7       | 14      | F2       | V <sub>SS</sub>                                      | s        | -               | -          | -                                                                                        | -                            |

| -       | -       | F4        | F3       | 15      | E10      | 15      | F4       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

|         |         |          | Pin nu   | ımbeı   | •        |         |          |                                                      |          | Pin type<br>I / O structure |   |                                                                                                                |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------------------|---|----------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type |                             |   | Alternate functions                                                                                            | Additional<br>functions |

| 96      | 140     | C4       | B4       | 168     | В9       | 199     | B4       | PB9                                                  | I/O      | FT                          | - | TIM4_CH4,<br>TIM11_CH1,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS,<br>CAN1_TX, SDIO_D5,<br>DCMI_D7, LCD_B7,<br>EVENTOUT | -                       |

| 97      | 141     | B4       | A4       | 169     | B10      | 200     | A6       | PE0                                                  | I/O      | FT                          | - | TIM4_ETR,<br>UART8_RX,<br>FMC_NBL0, DCMI_D2,<br>EVENTOUT                                                       | -                       |

| 98      | 142     | A4       | A3       | 170     | A10      | 201     | A5       | PE1                                                  | I/O      | FT                          | - | UART8_Tx,<br>FMC_NBL1, DCMI_D3,<br>EVENTOUT                                                                    | -                       |

| 99      | -       | F5       | D5       | -       | -        | 202     | F6       | $V_{SS}$                                             | S        |                             | - |                                                                                                                | -                       |

| -       | 143     | C3       | C6       | 171     | A11      | 203     | E5       | PDR_ON                                               | S        |                             | - |                                                                                                                | -                       |

| 100     | 144     | K6       | C5       | 172     | D7       | 204     | E7       | V <sub>DD</sub>                                      | S        |                             | - |                                                                                                                | -                       |

| -       | -       | В3       | D4       | 173     | -        | 205     | C3       | Pl4                                                  | I/O      | FT                          | - | TIM8_BKIN,<br>FMC_NBL2, DCMI_D5,<br>LCD_B4, EVENTOUT                                                           | -                       |

| -       | -       | A3       | C4       | 174     | -        | 206     | D3       | PI5                                                  | I/O      | FT                          | - | TIM8_CH1,<br>FMC_NBL3,<br>DCMI_VSYNC,<br>LCD_B5, EVENTOUT                                                      | -                       |

| -       | -       | A2       | C3       | 175     | -        | 207     | D6       | Pl6                                                  | I/O      | FT                          | - | TIM8_CH2, FMC_D28,<br>DCMI_D6, LCD_B6,<br>EVENTOUT                                                             | -                       |

| -       | -       | B1       | C2       | 176     | -        | 208     | D4       | PI7                                                  | I/O      | FT                          | - | TIM8_CH3, FMC_D29,<br>DCMI_D7, LCD_B7,<br>EVENTOUT                                                             | -                       |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

1. Function availability depends on the chosen device.

2. NC (not-connected) pins are not bonded. They must be configured by software to output push-pull and forced to 0 in the output data register to avoid extra current consumption in low power modes.

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

These I/Os must not be used as a current source (e.g. to drive an LED).

51

DocID024244 Rev 10

### Pinouts and pin description

| Table 11. FMC pin definition (continued) |        |                    |                  |        |       |  |  |  |  |  |

|------------------------------------------|--------|--------------------|------------------|--------|-------|--|--|--|--|--|

| Pin name                                 | CF     | NOR/PSRAM/<br>SRAM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |  |  |  |  |  |

| PE11                                     | D8     | D8                 | DA8              | D8     | D8    |  |  |  |  |  |

| PE12                                     | D9     | D9                 | DA9              | D9     | D9    |  |  |  |  |  |

| PE13                                     | D10    | D10                | DA10             | D10    | D10   |  |  |  |  |  |

| PE14                                     | D11    | D11                | DA11             | D11    | D11   |  |  |  |  |  |

| PE15                                     | D12    | D12                | DA12             | D12    | D12   |  |  |  |  |  |

| PD8                                      | D13    | D13                | DA13             | D13    | D13   |  |  |  |  |  |

| PD9                                      | D14    | D14                | DA14             | D14    | D14   |  |  |  |  |  |

| PD10                                     | D15    | D15                | DA15             | D15    | D15   |  |  |  |  |  |

| PH8                                      |        | D16                |                  |        | D16   |  |  |  |  |  |

| PH9                                      |        | D17                |                  |        | D17   |  |  |  |  |  |

| PH10                                     |        | D18                |                  |        | D18   |  |  |  |  |  |

| PH11                                     |        | D19                |                  |        | D19   |  |  |  |  |  |

| PH12                                     |        | D20                |                  |        | D20   |  |  |  |  |  |

| PH13                                     |        | D21                |                  |        | D21   |  |  |  |  |  |

| PH14                                     |        | D22                |                  |        | D22   |  |  |  |  |  |

| PH15                                     |        | D23                |                  |        | D23   |  |  |  |  |  |

| PI0                                      |        | D24                |                  |        | D24   |  |  |  |  |  |

| PI1                                      |        | D25                |                  |        | D25   |  |  |  |  |  |

| Pl2                                      |        | D26                |                  |        | D26   |  |  |  |  |  |

| PI3                                      |        | D27                |                  |        | D27   |  |  |  |  |  |

| PI6                                      |        | D28                |                  |        | D28   |  |  |  |  |  |

| PI7                                      |        | D29                |                  |        | D29   |  |  |  |  |  |

| PI9                                      |        | D30                |                  |        | D30   |  |  |  |  |  |

| PI10                                     |        | D31                |                  |        | D31   |  |  |  |  |  |

| PD7                                      |        | NE1                | NE1              | NCE2   |       |  |  |  |  |  |

| PG9                                      |        | NE2                | NE2              | NCE3   |       |  |  |  |  |  |

| PG10                                     | NCE4_1 | NE3                | NE3              |        |       |  |  |  |  |  |

| PG11                                     | NCE4_2 |                    |                  |        |       |  |  |  |  |  |

| PG12                                     |        | NE4                | NE4              |        |       |  |  |  |  |  |

| PD3                                      |        | CLK                | CLK              |        |       |  |  |  |  |  |

| PD4                                      | NOE    | NOE                | NOE              | NOE    |       |  |  |  |  |  |

| PD5                                      | NWE    | NWE                | NWE              | NWE    |       |  |  |  |  |  |

| PD6                                      | NWAIT  | NWAIT              | NWAIT            | NWAIT  |       |  |  |  |  |  |

| PB7                                      |        | NL(NADV)           | NL(NADV)         |        |       |  |  |  |  |  |

### Table 11. FMC pin definition (continued)

77/240

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

| 77/240             |           |      | AF0  | AF1    | AF2          | AF3              | AF4          | AF5                       | AF6                       | AF7                     | AF8                        | AF9                            | AF10                    | AF11 | AF12                 | AF13         | AF14   | AF15         |

|--------------------|-----------|------|------|--------|--------------|------------------|--------------|---------------------------|---------------------------|-------------------------|----------------------------|--------------------------------|-------------------------|------|----------------------|--------------|--------|--------------|

| 0                  | Port      |      | SYS  | TIM1/2 | TIM3/4/5     | TIM8/9/<br>10/11 | I2C1/<br>2/3 | SPI1/2/<br>3/4/5/6        | SPI2/3/<br>SAI1           | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН  | FMC/SDIO<br>/OTG2_FS | DCMI         | LCD    | SYS          |

|                    |           | PC8  | -    | -      | TIM3_<br>CH3 | TIM8_<br>CH3     | -            | -                         | -                         | -                       | USART6_<br>CK              | -                              | -                       | -    | SDIO_D0              | DCMI_<br>D2  | -      | EVEN<br>TOUT |

|                    |           | PC9  | MCO2 | -      | TIM3_<br>CH4 | TIM8_<br>CH4     | I2C3_<br>SDA | I2S_<br>CKIN              | -                         | -                       | -                          | -                              | -                       | -    | SDIO_D1              | DCMI_<br>D3  | -      | EVEN<br>TOUT |

|                    |           | PC10 | -    | -      | -            | -                | -            | -                         | SPI3_<br>SCK/I2S<br>3_CK  | USART3_<br>TX           | UART4_TX                   | -                              | -                       | -    | SDIO_D2              | DCMI_<br>D8  | LCD_R2 | EVEN<br>TOUT |

|                    | Port      | PC11 | -    | -      | -            | -                | -            | I2S3ext<br>_SD            | SPI3_<br>MISO             | USART3_<br>RX           | UART4_RX                   | -                              | -                       | -    | SDIO_D3              | DCMI_<br>D4  | -      | EVEN<br>TOUT |

| D                  | Port<br>C | PC12 | -    | -      | -            | -                | -            | -                         | SPI3_<br>MOSI/I2<br>S3_SD | USART3_<br>CK           | UART5_TX                   | -                              | -                       | -    | SDIO_CK              | DCMI_<br>D9  | -      | EVEN<br>TOUT |

| ocID0              |           | PC13 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

| 2424               |           | PC14 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

| DocID024244 Rev 10 |           | PC15 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

| 10                 |           | PD0  | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | CAN1_RX                        | -                       | -    | FMC_D2               | -            | -      | EVEN<br>TOUT |

|                    |           | PD1  | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | CAN1_TX                        | -                       | -    | FMC_D3               | -            | -      | EVEN<br>TOUT |

|                    |           | PD2  | -    | -      | TIM3_<br>ETR | -                | -            | -                         | -                         | -                       | UART5_RX                   | -                              | -                       | -    | SDIO_<br>CMD         | DCMI_<br>D11 | -      | EVEN<br>TOUT |

|                    | Port<br>D | PD3  | -    | -      | -            | -                | -            | SPI2_S<br>CK/I<br>2S2_CK  | -                         | USART2_<br>CTS          | -                          | -                              | -                       | -    | FMC_CLK              | DCMI_<br>D5  | LCD_G7 | EVEN<br>TOUT |

|                    |           | PD4  | -    | -      | -            | -                | -            | -                         | -                         | USART2_<br>RTS          | -                          | -                              | -                       | -    | FMC_NOE              | -            | -      | EVEN<br>TOUT |

|                    |           | PD5  | -    | -      | -            | -                | -            | -                         | -                         | USART2_<br>TX           | -                          | -                              | -                       | -    | FMC_NWE              | -            | -      | EVEN<br>TOUT |

| 6                  |           | PD6  | -    | -      | -            | -                | -            | SPI3_<br>MOSI/I2<br>S3_SD | SAI1_<br>SD_A             | USART2_<br>RX           | -                          | -                              | -                       | -    | FMC_<br>NWAIT        | DCMI_<br>D10 | LCD_B2 | EVEN<br>TOUT |

Pinouts and pin description

STM32F437xx and STM32F439xx

| Л | ۱ |

|---|---|

|   |   |

|   |   |

DocID024244 Rev 10

81/240

|          |        | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11                                     | AF12                       | AF13                  | AF14   | AF15         |

|----------|--------|-----|--------|----------|------------------|---------------|--------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|------------------------------------------|----------------------------|-----------------------|--------|--------------|

|          | Port   | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11 | l2C1/<br>2/3  | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН                                      | FMC/SDIO<br>/OTG2_FS       | DCMI                  | LCD    | SYS          |

|          | PG9    | -   | -      | -        | -                | -             | -                  | -               | -                       | USART6_<br>RX              | -                              | -                       | -                                        | FMC_NE2/<br>FMC_<br>NCE3   | DCMI_<br>VSYNC<br>(1) | -      | EVEN<br>TOUT |

|          | PG10   | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | LCD_G3                         | -                       | -                                        | FMC_<br>NCE4_1/<br>FMC_NE3 | DCMI_<br>D2           | LCD_B2 | EVEN<br>TOUT |

|          | PG11   | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>TX_EN/<br>ETH_RMII<br>_TX_EN | FMC_<br>NCE4_2             | DCMI_<br>D3           | LCD_B3 | EVEN<br>TOUT |

| Por<br>G | t PG12 | -   | -      | -        | -                | -             | SPI6_<br>MISO      | -               | -                       | USART6_<br>RTS             | LCD_B4                         | -                       | -                                        | FMC_NE4                    | -                     | LCD_B1 | EVEN<br>TOUT |

|          | PG13   | -   | -      | -        | -                | -             | SPI6_<br>SCK       | -               | -                       | USART6_<br>CTS             | -                              | -                       | ETH_MII_<br>TXD0/<br>ETH_RMII<br>_TXD0   | FMC_A24                    | -                     | -      | EVEN<br>TOUT |

|          | PG14   | -   | -      | -        | -                | -             | SPI6_<br>MOSI      | -               | -                       | USART6_<br>TX              | -                              | -                       | ETH_MII_<br>TXD1/<br>ETH_RMII<br>_TXD1   | FMC_A25                    | -                     | -      | EVEN<br>TOUT |

|          | PG15   | -   | -      | -        | -                | -             | -                  | -               | -                       | USART6_<br>CTS             | -                              | -                       | -                                        | FMC_<br>SDNCAS             | DCMI_<br>D13          | -      | EVEN<br>TOUT |

|          | PH0    | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | -                                        | -                          | -                     | -      | EVEN<br>TOUT |

|          | PH1    | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | -                                        | -                          | -                     | -      | EVEN<br>TOUT |

|          | PH2    | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>CRS                          | FMC_<br>SDCKE0             | -                     | LCD_R0 | EVEN<br>TOUT |

| Por<br>H | t PH3  | -   | -      | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>COL                          | FMC_SDN<br>E0              | -                     | LCD_R1 | EVEN<br>TOUT |

|          | PH4    | -   | -      | -        | -                | I2C2_<br>SCL  | -                  | -               | -                       | -                          | -                              | OTG_HS_<br>ULPI_NXT     | -                                        | -                          | -                     | -      | EVEN<br>TOUT |

|          | PH5    | -   | -      | -        | -                | I2C2_<br>SDA  | SPI5_N<br>SS       | -               | -                       | -                          | -                              | -                       | -                                        | FMC_SDN<br>WE              | -                     | -      | EVEN<br>TOUT |

|          | PH6    | -   | -      | -        | -                | I2C2_<br>SMBA | SPI5_<br>SCK       | -               | -                       | -                          | TIM12_CH1                      | -                       | -                                        | FMC_<br>SDNE1              | DCMI_<br>D8           | -      | -            |

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

Pinouts and pin description

STM32F437xx and STM32F439xx

DocID024244 Rev 10

84/240

1. The DCMI\_VSYNC alternate function on PG9 is only available on silicon revision 3.

| τ        |

|----------|

| Ē        |

| -        |

| 0        |

| 2        |

| <b>T</b> |

| S        |

| a        |

|          |

| ā        |

| _        |

| σ        |

| 3        |

|          |

| Q        |

| Φ        |

| S        |

| C        |

| Ξ.       |

| -        |

| Ă        |

| <u> </u> |

| ¥        |

| <b>_</b> |

STM32F437xx and STM32F439xx

|        |      | AF0 | AF1    | AF2      | AF3              | AF4          | AF5                | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11 | AF12                 | AF13 | AF14   | AF15         |

|--------|------|-----|--------|----------|------------------|--------------|--------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|------|----------------------|------|--------|--------------|

| P      | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11 | l2C1/<br>2/3 | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН  | FMC/SDIO<br>/OTG2_FS | DCMI | LCD    | SYS          |

|        | PJ8  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_G1 | EVEN<br>TOUT |

|        | PJ9  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_G2 | EVEN<br>TOUT |

|        | PJ10 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_G3 | EVEN<br>TOUT |

|        | PJ11 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_G4 | EVEN<br>TOUT |

| Port J | PJ12 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B0 | EVEN<br>TOUT |

|        | PJ13 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B1 | EVEN<br>TOUT |

|        | PJ14 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B2 | EVEN<br>TOUT |

|        | PJ15 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B3 | EVEN<br>TOUT |

|        | PK0  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_G5 | EVEN<br>TOUT |

|        | PK1  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_G6 | EVEN<br>TOUT |

|        | PK2  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_G7 | EVEN<br>TOUT |

| D. UK  | PK3  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B4 | EVEN<br>TOUT |

| Port K | PK4  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B5 | EVEN<br>TOUT |

|        | PK5  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B6 | EVEN<br>TOUT |

|        | PK6  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_B7 | EVEN<br>TOUT |

|        | PK7  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -    | -                    | -    | LCD_DE | EVEN<br>TOUT |

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

| Bus  | Boundary address          | Peripheral         |

|------|---------------------------|--------------------|

|      | 0x4001 6C00- 0x4001 FFFF  | Reserved           |

|      | 0x4001 6800 - 0x4001 6BFF | LCD-TFT            |

|      | 0x4001 5C00 - 0x4001 67FF | Reserved           |

|      | 0x4001 5800 - 0x4001 5BFF | SAI1               |

|      | 0x4001 5400 - 0x4001 57FF | SPI6               |

|      | 0x4001 5000 - 0x4001 53FF | SPI5               |

|      | 0x4001 4C00 - 0x4001 4FFF | Reserved           |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11              |

|      | 0x4001 4400 - 0x4001 47FF | TIM10              |

|      | 0x4001 4000 - 0x4001 43FF | TIM9               |

|      | 0x4001 3C00 - 0x4001 3FFF | EXTI               |

| APB2 | 0x4001 3800 - 0x4001 3BFF | SYSCFG             |

| AFDZ | 0x4001 3400 - 0x4001 37FF | SPI4               |

|      | 0x4001 3000 - 0x4001 33FF | SPI1               |

|      | 0x4001 2C00 - 0x4001 2FFF | SDIO               |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved           |

|      | 0x4001 2000 - 0x4001 23FF | ADC1 - ADC2 - ADC3 |

|      | 0x4001 1800 - 0x4001 1FFF | Reserved           |

|      | 0x4001 1400 - 0x4001 17FF | USART6             |

|      | 0x4001 1000 - 0x4001 13FF | USART1             |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved           |

|      | 0x4001 0400 - 0x4001 07FF | TIM8               |

|      | 0x4001 0000 - 0x4001 03FF | TIM1               |

### Table 13. STM32F437xx and STM32F439xx register boundary addresses (continued)

### 6.3.7 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 23: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- Regulator ON

- The voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \leq 120 \text{ MHz}$

- Scale 2 for 120 MHz < f<sub>HCLK</sub> ≤144 MHz

- Scale 1 for 144 MHz < f<sub>HCLK</sub> ≤180 MHz. The over-drive is only ON at 180 MHz.

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- External clock frequency is 4 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and a maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

| Symbol           | Parameter Conditions | Conditions                                                                              | Value | Unit    |

|------------------|----------------------|-----------------------------------------------------------------------------------------|-------|---------|

|                  |                      | Min <sup>(1)</sup>                                                                      | Unit  |         |

| N <sub>END</sub> | Endurance            | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10    | kcycles |

|                  |                      | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30    |         |

| t <sub>RET</sub> | Data retention       | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10    | Years   |

|                  |                      | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20    |         |

Table 50. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

### 6.3.14 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                         | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2                                            | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP176}, \text{T}_{\text{A}} = +25 \text{ °C}, \text{f}_{\text{HCLK}} = 168 \text{ MHz}, \text{ conforms to} \text{IEC 61000-4-2}$ | 4A              |

Table 51. EMS characteristics

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, PH2, PH3, PH4, PH5, PA3, PA4, PA5, PA6, PA7, PC4, and PC5.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

DocID024244 Rev 10

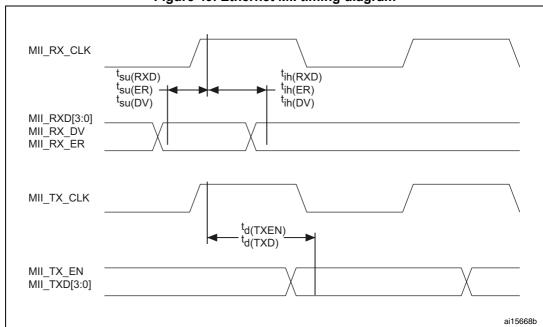

Figure 49. Ethernet MII timing diagram

| Table 73. Dynamics characteristics: Ethernet MAC signals for MII <sup>(1)</sup> |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Symbol               | Parameter                        | Condition                        | Min | Тур | Max | Unit |

|----------------------|----------------------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          |                                  | 9   | -   | -   |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           |                                  | 10  | -   | -   |      |

| t <sub>su(DV)</sub>  | Data valid setup time            | 1.71 V < V <sub>DD</sub> < 3.6 V | 9   | -   | -   |      |

| t <sub>ih(DV)</sub>  | Data valid hold time             | $1.71 v < v_{DD} < 3.0 v$        | 8   | -   | -   |      |

| t <sub>su(ER)</sub>  | Error setup time                 |                                  | 6   | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  |                                  | 8   | -   | -   | 115  |

| +                    | Transmit anable valid delay time | 2.7 V < V <sub>DD</sub> < 3.6 V  | 8   | 10  | 14  |      |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 1.71 V < V <sub>DD</sub> < 3.6 V | 8   | 10  | 16  |      |

| +                    | Transmit data valid delay time   | 2.7 V < V <sub>DD</sub> < 3.6 V  | 7.5 | 10  | 15  |      |

| t <sub>d(TXD)</sub>  |                                  | 1.71 V < V <sub>DD</sub> < 3.6 V | 7.5 | 10  | 17  |      |

1. Guaranteed by characterization results.

#### CAN (controller area network) interface

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (CANx\_TX and CANx\_RX).

### 6.3.21 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 74* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 17*.

| Symbol                           | Parameter                                       | Conditions                                           | Min                                                            | Тур      | Мах               | Unit               |

|----------------------------------|-------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|----------|-------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                                    |                                                      | 1.7 <sup>(1)</sup>                                             | -        | 3.6               |                    |

| V <sub>REF+</sub>                | Positive reference voltage                      | $V_{DDA} - V_{REF+} < 1.2 V$                         | 1.7 <sup>(1)</sup>                                             | -        | V <sub>DDA</sub>  | V                  |

| V <sub>REF-</sub>                | Negative reference voltage                      |                                                      |                                                                | 0        | -                 |                    |

| £                                | ADC alook fraguanay                             | V <sub>DDA</sub> = 1.7 <sup>(1)</sup> to 2.4 V       | 0.6                                                            | 15       | 18                | MHz                |

| f <sub>ADC</sub>                 | ADC clock frequency                             | V <sub>DDA</sub> = 2.4 to 3.6 V                      | 0.6                                                            | 30       | 36                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                      | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution      | -                                                              | -        | 1764              | kHz                |

|                                  |                                                 |                                                      | -                                                              | I        | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>         |                                                      | 0<br>(V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -        | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                        | See <i>Equation 1</i> for details                    | -                                                              | -        | 50                | kΩ                 |

| $R_{ADC}^{(2)(4)}$               | Sampling switch resistance                      |                                                      | -                                                              | -        | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor              |                                                      | -                                                              | 4        | 7                 | pF                 |

| t <sub>lat</sub> (2)             | Injection trigger conversion latency            | f <sub>ADC</sub> = 30 MHz                            | -                                                              | -        | 0.100             | μs                 |

| Hat                              |                                                 |                                                      | -                                                              | -        | 3 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                      | f <sub>ADC</sub> = 30 MHz                            | -                                                              | I        | 0.067             | μs                 |

| Yatr                             | latency                                         |                                                      | -                                                              | I        | 2 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                                   | f <sub>ADC</sub> = 30 MHz                            | 0.100                                                          | -        | 16                | μs                 |

| -                                |                                                 |                                                      | 3                                                              | -        | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                   |                                                      | -                                                              | 2        | 3                 | μs                 |

|                                  |                                                 | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution       | 0.50                                                           | -        | 16.40             | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time (including sampling time) | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution       | 0.43                                                           | -        | 16.34             | μs                 |

|                                  |                                                 | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution        | 0.37                                                           | -        | 16.27             | μs                 |

|                                  |                                                 | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution        | 0.30                                                           | -        | 16.20             | μs                 |

|                                  |                                                 | 9 to 492 (t <sub>S</sub> for sampling approximation) | +n-bit resolution f                                            | or succe | ssive             | 1/f <sub>ADC</sub> |

| Table | 74. ADC | characteristics |

|-------|---------|-----------------|

| TUDIC | 1 T. AD |                 |

| Symbol                            | Parameter                                                                          | Conditions                                         | Min | Тур | Max  | Unit |

|-----------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|------|

|                                   | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Single ADC                    | -   | -   | 2    | Msps |

| f <sub>S</sub> <sup>(2)</sup>     |                                                                                    | 12-bit resolution<br>Interleave Dual ADC<br>mode   | -   | -   | 3.75 | Msps |

|                                   |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode | -   | -   | 6    | Msps |

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               |                                                    | -   | 300 | 500  | μA   |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               |                                                    | -   | 1.6 | 1.8  | mA   |

Table 74. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

2. Guaranteed by characterization results.

3.  $V_{\mathsf{REF}}$  is internally connected to  $V_{\mathsf{DDA}}$  and  $V_{\mathsf{REF}}$  is internally connected to  $V_{\mathsf{SSA}}.$

4.  $R_{ADC}$  maximum value is given for  $V_{DD}$ =1.7 V, and minimum value for  $V_{DD}$ =3.3 V.

5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 74.

#### Equation 1: RAIN max formula

$$R_{AIN} = \frac{(k-0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

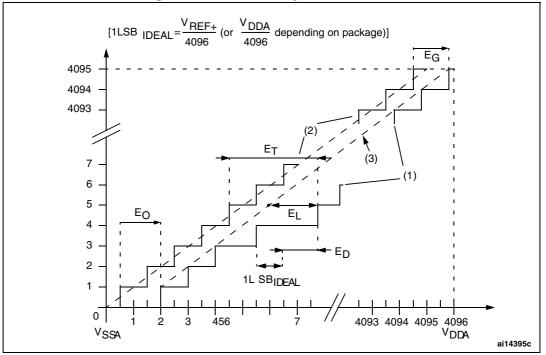

|        |                              | · · ·                                                       |     |                    |      |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(1)</sup> | Unit |

| ET     | Total unadjusted error       | ( (0))                                                      | ±3  | ±4                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 |      |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V                  | ±1  | ±2                 |      |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |

Table 75. ADC static accuracy at f<sub>ADC</sub> = 18 MHz

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.17 does not affect the ADC accuracy.

- 1. See also Table 76.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4. End point correlation line.

- E<sub>T</sub> = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

#### **Electrical characteristics**

| Symbol                | Parameter Conditions Min Typ Max Unit                                                 |   |   |     | Parameter Conditions Min Typ Max | Parameter | Comments                                                                                                                |

|-----------------------|---------------------------------------------------------------------------------------|---|---|-----|----------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| eysei                 |                                                                                       |   |   | .76 | max                              | •         |                                                                                                                         |

| t <sub>WAKEUP</sub> ( | Wakeup time from off<br>state (Setting the ENx<br>bit in the DAC Control<br>register) | - | - | 6.5 | 10                               | μs        | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |

| PSRR+<br>(2)          | Power supply rejection<br>ratio (to V <sub>DDA</sub> ) (static<br>DC measurement)     | - | - | -67 | -40                              | dB        | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |

### Table 85. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

2. Guaranteed by design.

The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization.

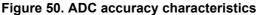

#### Figure 54. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

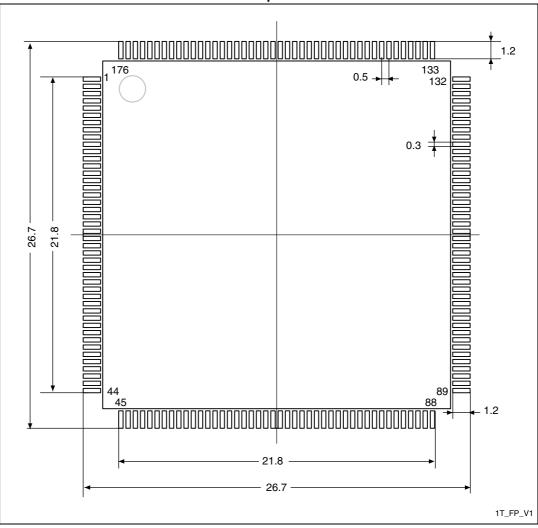

Figure 90. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

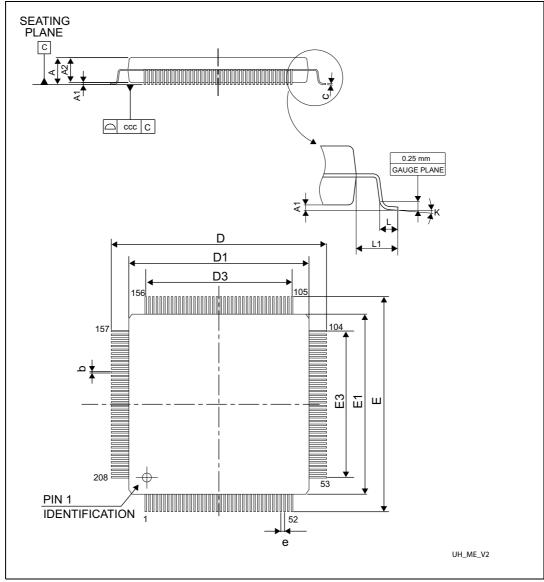

# 7.5 LQFP208 package information

Figure 92. LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package outline

1. Drawing is not to scale.

# Appendix B Application block diagrams

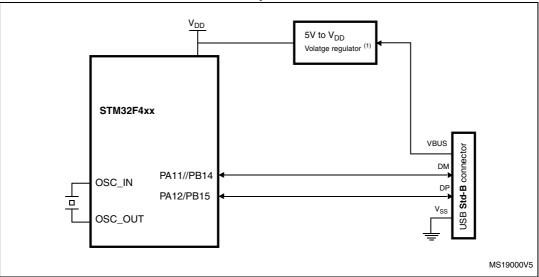

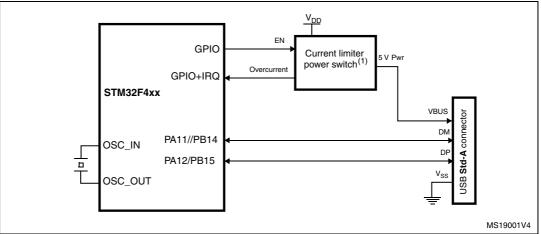

# B.1 USB OTG full speed (FS) interface solutions

Figure 103. USB controller configured as peripheral-only and used in Full speed mode

1. External voltage regulator only needed when building a  $V_{\text{BUS}}$  powered device.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.