## STMicroelectronics - STM32F437ZIT7TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 144-LQFP                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f437zit7tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Reference   | Part number                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| STM32F437xx | STM32F437VG, STM32F437ZG, STM32F437IG, STM32F437VI, STM32F437ZI, STM32F437II, STM32F437AI                                                     |  |  |  |  |  |  |  |  |  |

| STM32F439xx | STM32F439VI, STM32F439VG, STM32F439ZG, STM32F439ZI, STM32F439IG, STM32F439II, STM32F439BG, STM32F439BI, STM32F439NI, STM32F439AI, STM32F439NG |  |  |  |  |  |  |  |  |  |

## Table 1. Device summary

# 2.1 Full compatibility throughout the family

The STM32F437xx and STM32F439xx devices are part of the STM32F4 family. They are fully pin-to-pin, software and feature compatible with the STM32F2xx devices, allowing the user to try different memory densities, peripherals, and performances (FPU, higher frequency) for a greater degree of freedom during the development cycle.

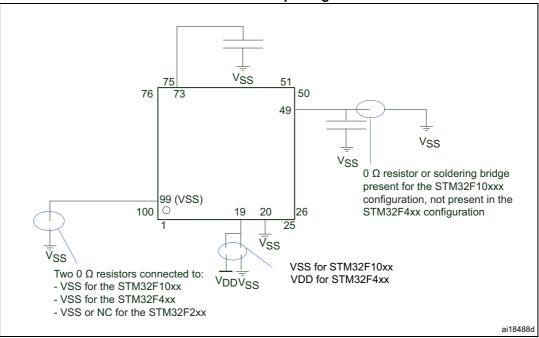

The STM32F437xx and STM32F439xx devices maintain a close compatibility with the whole STM32F10xx family. All functional pins are pin-to-pin compatible. The STM32F437xx and STM32F439xx, however, are not drop-in replacements for the STM32F10xx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xx to the STM32F43x family remains simple as only a few pins are impacted.

*Figure 1*, *Figure 2*, and *Figure 3*, give compatible board designs between the STM32F4xx, STM32F2xx, and STM32F10xx families.

Figure 1. Compatible board design STM32F10xx/STM32F2xx/STM32F4xx for LQFP100 package

# 3.26 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available. They can be operated in master or slave mode, in full duplex and simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

Note: For I2S2 full-duplex mode, I2S2\_CK and I2S2\_WS signals can be used only on GPIO Port B and GPIO Port D.

# 3.27 Serial Audio interface (SAI1)

The serial audio interface (SAI1) is based on two independent audio sub-blocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both sub-blocks can be configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

SAI1 can be served by the DMA controller.

# 3.28 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S/SAI flow with an external PLL (or Codec output).

# 3.29 Audio and LCD PLL(PLLSAI)

An additional PLL dedicated to audio and LCD-TFT is used for SAI1 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the LCD-TFT clock.

FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). 256 bytes of SRAM are allocated for each CAN.

# 3.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 3.34 Universal serial bus on-the-go high-speed (OTG\_HS)

The devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1 Kbit × 35 with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

|         |         |          | Pin nu   | ımbeı   | r        |         |          |                                                                        |     |                     |                         |                                                                                                                 |   |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------------------------|-----|---------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------|---|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup><br>Notes<br>Notes |     | Alternate functions | Additional<br>functions |                                                                                                                 |   |

| 38      | 58      | N7       | R8       | 68      | L5       | 79      | R8       | PE7                                                                    | I/O | FT                  | -                       | TIM1_ETR, UART7_Rx,<br>FMC_D4, EVENTOUT                                                                         | - |

| 39      | 59      | J8       | P8       | 69      | M5       | 80      | N9       | PE8                                                                    | I/O | FT                  | -                       | TIM1_CH1N,<br>UART7_Tx, FMC_D5,<br>EVENTOUT                                                                     | - |

| 40      | 60      | K8       | P9       | 70      | N5       | 81      | P9       | PE9                                                                    | I/O | FT                  | -                       | TIM1_CH1, FMC_D6,<br>EVENTOUT                                                                                   | - |

| -       | 61      | J6       | M9       | 71      | H3       | 82      | K8       | V <sub>SS</sub>                                                        | S   |                     | -                       |                                                                                                                 | - |

| -       | 62      | G10      | N9       | 72      | J5       | 83      | L9       | V <sub>DD</sub>                                                        | S   |                     | -                       |                                                                                                                 | - |

| 41      | 63      | L8       | R9       | 73      | J4       | 84      | R9       | PE10                                                                   | I/O | FT                  | -                       | TIM1_CH2N, FMC_D7,<br>EVENTOUT                                                                                  | - |

| 42      | 64      | M8       | P10      | 74      | K4       | 85      | P10      | PE11                                                                   | I/O | FT                  | -                       | TIM1_CH2, SPI4_NSS,<br>FMC_D8, LCD_G3,<br>EVENTOUT                                                              | - |

| 43      | 65      | N8       | R10      | 75      | L4       | 86      | R10      | PE12                                                                   | I/O | FT                  | -                       | TIM1_CH3N,<br>SPI4_SCK, FMC_D9,<br>LCD_B4, EVENTOUT                                                             | - |

| 44      | 66      | H9       | N11      | 76      | N4       | 87      | R12      | PE13                                                                   | I/O | FT                  | -                       | TIM1_CH3,<br>SPI4_MISO, FMC_D10,<br>LCD_DE, EVENTOUT                                                            | - |

| 45      | 67      | J9       | P11      | 77      | M4       | 88      | P11      | PE14                                                                   | I/O | FT                  | -                       | TIM1_CH4,<br>SPI4_MOSI, FMC_D11,<br>LCD_CLK, EVENTOUT                                                           | - |

| 46      | 68      | K9       | R11      | 78      | L3       | 89      | R11      | PE15                                                                   | I/O | FT                  | -                       | TIM1_BKIN, FMC_D12,<br>LCD_R7, EVENTOUT                                                                         | - |

| 47      | 69      | L9       | R12      | 79      | M3       | 90      | P12      | PB10                                                                   | I/O | FT                  | _                       | TIM2_CH3, I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>USART3_TX,<br>OTG_HS_ULPI_D3,<br>ETH_MII_RX_ER,<br>LCD_G4, EVENTOUT | - |

| 48      | 70      | M9       | R13      | 80      | N3       | 91      | R13      | PB11                                                                   | I/O | FT                  | -                       | TIM2_CH4, I2C2_SDA,<br>USART3_RX,<br>OTG_HS_ULPI_D4,<br>ETH_MII_TX_EN/ETH_<br>RMII_TX_EN, LCD_G5,<br>EVENTOUT   | - |

| Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued) |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

|         |         |          | Pin nu   | Imber   | •        |         |          |                                                      |          |                 |       |                                                                                          |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                      | Additional<br>functions |

| 68      | 101     | E8       | E15      | 120     | E2       | 143     | E15      | PA9                                                  | I/O      | FT              | -     | TIM1_CH2,<br>I2C3_SMBA,<br>USART1_TX,<br>DCMI_D0, EVENTOUT                               | OTG_FS_<br>VBUS         |

| 69      | 102     | E9       | D15      | 121     | D5       | 144     | D15      | PA10                                                 | I/O      | FT              | -     | TIM1_CH3,<br>USART1_RX,<br>OTG_FS_ID,<br>DCMI_D1, EVENTOUT                               | -                       |

| 70      | 103     | E10      | C15      | 122     | D4       | 145     | C15      | PA11                                                 | I/O      | FT              | -     | TIM1_CH4,<br>USART1_CTS,<br>CAN1_RX, LCD_R4,<br>OTG_FS_DM,<br>EVENTOUT                   | -                       |

| 71      | 104     | E11      | B15      | 123     | E1       | 146     | B15      | PA12                                                 | I/O      | FT              | -     | TIM1_ETR,<br>USART1_RTS,<br>CAN1_TX, LCD_R5,<br>OTG_FS_DP,<br>EVENTOUT                   | -                       |

| 72      | 105     | E12      | A15      | 124     | D3       | 147     | A15      | PA13<br>(JTMS-<br>SWDIO)                             | I/O      | FT              | -     | JTMS-SWDIO,<br>EVENTOUT                                                                  | -                       |

| 73      | 106     | D12      | F13      | 125     | D1       | 148     | E11      | V <sub>CAP_2</sub>                                   | S        |                 | -     | -                                                                                        | -                       |

| 74      | 107     | J10      | F12      | 126     | D2       | 149     | F10      | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                        | -                       |

| 75      | 108     | H4       | G13      | 127     | C1       | 150     | F11      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                        | -                       |

| -       | -       | D13      | E12      | 128     | -        | 151     | E12      | PH13                                                 | I/O      | FT              | -     | TIM8_CH1N,<br>CAN1_TX, FMC_D21,<br>LCD_G2, EVENTOUT                                      | -                       |

| -       | -       | C13      | E13      | 129     | -        | 152     | E13      | PH14                                                 | I/O      | FT              | -     | TIM8_CH2N,<br>FMC_D22, DCMI_D4,<br>LCD_G3, EVENTOUT                                      | -                       |

| -       | -       | C12      | D13      | 130     | -        | 153     | D13      | PH15                                                 | I/O      | FT              | -     | TIM8_CH3N,<br>FMC_D23, DCMI_D11,<br>LCD_G4, EVENTOUT                                     | -                       |

| -       | -       | B13      | E14      | 131     | -        | 154     | E14      | PIO                                                  | I/O      | FT              | -     | TIM5_CH4,<br>SPI2_NSS/I2S2_WS <sup>(7)</sup> ,<br>FMC_D24, DCMI_D13,<br>LCD_G5, EVENTOUT | -                       |

| Table 10. STM32F437xx and STM32F439xx | nin and hall definitions (continued) |

|---------------------------------------|--------------------------------------|

|                                       | pin and ball deminions (continued)   |

64/240

DocID024244 Rev 10

| Bus  | Boundary address          | Peripheral         |

|------|---------------------------|--------------------|

|      | 0x4001 6C00- 0x4001 FFFF  | Reserved           |

|      | 0x4001 6800 - 0x4001 6BFF | LCD-TFT            |

|      | 0x4001 5C00 - 0x4001 67FF | Reserved           |

|      | 0x4001 5800 - 0x4001 5BFF | SAI1               |

|      | 0x4001 5400 - 0x4001 57FF | SPI6               |

|      | 0x4001 5000 - 0x4001 53FF | SPI5               |

|      | 0x4001 4C00 - 0x4001 4FFF | Reserved           |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11              |

|      | 0x4001 4400 - 0x4001 47FF | TIM10              |

|      | 0x4001 4000 - 0x4001 43FF | TIM9               |

|      | 0x4001 3C00 - 0x4001 3FFF | EXTI               |

| APB2 | 0x4001 3800 - 0x4001 3BFF | SYSCFG             |

| AFDZ | 0x4001 3400 - 0x4001 37FF | SPI4               |

|      | 0x4001 3000 - 0x4001 33FF | SPI1               |

|      | 0x4001 2C00 - 0x4001 2FFF | SDIO               |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved           |

|      | 0x4001 2000 - 0x4001 23FF | ADC1 - ADC2 - ADC3 |

|      | 0x4001 1800 - 0x4001 1FFF | Reserved           |

|      | 0x4001 1400 - 0x4001 17FF | USART6             |

|      | 0x4001 1000 - 0x4001 13FF | USART1             |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved           |

|      | 0x4001 0400 - 0x4001 07FF | TIM8               |

|      | 0x4001 0000 - 0x4001 03FF | TIM1               |

## Table 13. STM32F437xx and STM32F439xx register boundary addresses (continued)

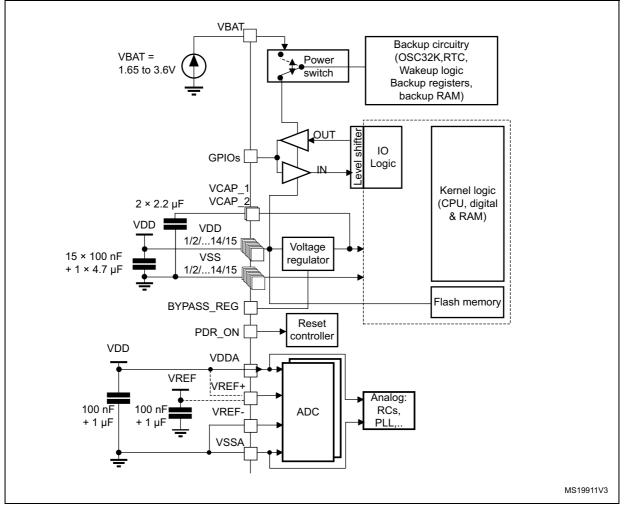

## 6.1.6 Power supply scheme

### Figure 22. Power supply scheme

1. To connect BYPASS\_REG and PDR\_ON pins, refer to Section 3.17: Power supply supervisor and Section 3.18: Voltage regulator

- 2. The two 2.2 µF ceramic capacitors should be replaced by two 100 nF decoupling capacitors when the voltage regulator is OFF.

- 3. The 4.7  $\mu F$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

- 4.  $V_{DDA}=V_{DD}$  and  $V_{SSA}=V_{SS}$ .

- **Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> ...) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure good operation of the device. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect operation of the device.

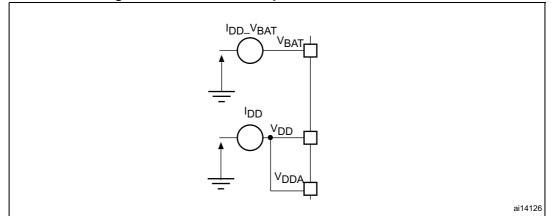

## 6.1.7 Current consumption measurement

### Figure 23. Current consumption measurement scheme

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 14: Voltage characteristics*, *Table 15: Current characteristics*, and *Table 16: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard, extended mission profiles are available on demand.

| Symbol                            | Ratings                                                                                                                           | Min                       | Max                  | Unit |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|------|

| $V_{DD}-V_{SS}$                   | External main supply voltage (including $V_{DDA}, V_{DD}$ and VBAT) $^{(1)}$                                                      | - 0.3                     | 4.0                  |      |

|                                   | Input voltage on FT pins <sup>(2)</sup>                                                                                           | V <sub>SS</sub> - 0.3     | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub>                   | Input voltage on TTa pins                                                                                                         | V <sub>SS</sub> - 0.3 4.0 |                      | V    |

|                                   | Input voltage on any other pin                                                                                                    | V <sub>SS</sub> – 0.3     | 4.0                  |      |

|                                   | Input voltage on BOOT0 pin                                                                                                        | V <sub>SS</sub>           | 9.0                  |      |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins                                                                                  | -                         | 50                   |      |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins including $V_{REF^-}$                                                            | -                         | 50                   | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model) see Section 6.3.15:<br>Absolute maximum<br>ratings (electrical<br>sensitivity) |                           |                      |      |

### Table 14. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2.  $V_{IN}$  maximum value must always be respected. Refer to *Table 15* for the values of the maximum allowed injected current.

DocID024244 Rev 10

|                 |                                    |                        |                         |     | · · · · · ·               | Max <sup>(1)</sup>        |                            |      |  |  |  |  |

|-----------------|------------------------------------|------------------------|-------------------------|-----|---------------------------|---------------------------|----------------------------|------|--|--|--|--|

| Symbol          | Parameter                          | Conditions             | f <sub>HCLK</sub> (MHz) | Тур | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |  |  |  |

|                 |                                    |                        | 180                     | 78  | 89 <sup>(3)</sup>         | 110                       | 130 <sup>(3)</sup>         |      |  |  |  |  |

|                 |                                    |                        | 168                     | 66  | 75 <sup>(3)</sup>         | 93                        | 110 <sup>(3)</sup>         |      |  |  |  |  |

|                 |                                    |                        | 150                     | 56  | 61                        | 80                        | 96                         |      |  |  |  |  |

|                 |                                    |                        | 144                     | 54  | 58                        | 78                        | 94                         |      |  |  |  |  |

|                 |                                    |                        | 120                     | 40  | 44                        | 59                        | 72                         |      |  |  |  |  |

|                 |                                    | All                    | 90                      | 32  | 34                        | 46                        | 56                         |      |  |  |  |  |

|                 |                                    | Peripherals            | 60                      | 22  | 23                        | 31                        | 38                         |      |  |  |  |  |

|                 |                                    | enabled <sup>(2)</sup> | 30                      | 10  | 16                        | 30                        | 43                         |      |  |  |  |  |

|                 | Supply<br>current in<br>Sleep mode |                        | 25                      | 9   | 14                        | 28                        | 40                         | -    |  |  |  |  |

|                 |                                    |                        | 16                      | 5   | 12                        | 25                        | 40                         |      |  |  |  |  |

|                 |                                    |                        | 8                       | 3   | 8                         | 22                        | 35                         |      |  |  |  |  |

|                 |                                    |                        | 4                       | 3   | 7                         | 21                        | 34                         |      |  |  |  |  |

| 1               |                                    |                        | 2                       | 2   | 6.5                       | 20                        | 33                         | mA   |  |  |  |  |

| I <sub>DD</sub> |                                    | All                    | 180                     | 21  | 26 <sup>(3)</sup>         | 54                        | 76 <sup>(3)</sup>          | ШA   |  |  |  |  |

|                 |                                    |                        | 168                     | 16  | 20 <sup>(3)</sup>         | 41                        | 58 <sup>(3)</sup>          |      |  |  |  |  |

|                 |                                    |                        | 150                     | 14  | 17                        | 36                        | 52                         |      |  |  |  |  |

|                 |                                    |                        | 144                     | 13  | 16.5                      | 35                        | 51                         |      |  |  |  |  |

|                 |                                    |                        | 120                     | 10  | 14                        | 28                        | 41                         |      |  |  |  |  |

|                 |                                    |                        | 90                      | 8   | 13                        | 26                        | 37                         |      |  |  |  |  |

|                 |                                    | Peripherals            | 60                      | 6   | 9                         | 17                        | 25                         |      |  |  |  |  |

|                 |                                    | disabled               | 30                      | 5   | 8                         | 22                        | 35                         |      |  |  |  |  |

|                 |                                    |                        | 25                      | 3   | 7                         | 21                        | 34                         |      |  |  |  |  |

|                 |                                    |                        | 16                      | 3   | 7                         | 21                        | 34                         |      |  |  |  |  |

|                 |                                    |                        | 8                       | 2   | 6                         | 20                        | 33                         |      |  |  |  |  |

|                 |                                    |                        | 4                       | 2   | 6                         | 20                        | 33                         |      |  |  |  |  |

|                 |                                    |                        | 2                       | 2   | 6                         | 20                        | 33                         |      |  |  |  |  |

| Table 26 | . Typical and | l maximum | current | consump | otion in | Sleep | mode |

|----------|---------------|-----------|---------|---------|----------|-------|------|

|----------|---------------|-----------|---------|---------|----------|-------|------|

1. Guaranteed by characterization unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. Based on characterization, tested in production.

| Symbol            | Parameter           | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|---------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>BE</sub>   |                     | Program/erase parallelism<br>(PSIZE) = x 8  |                    | 16  | 32                 |      |

|                   | Bank erase time     | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 11  | 22                 | s    |

|                   |                     | Program/erase parallelism<br>(PSIZE) = x 32 |                    |     | 16                 |      |

|                   |                     | 32-bit program operation                    | 2.7                | -   | 3.6                | V    |

| V <sub>prog</sub> | Programming voltage | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |

|                   |                     | 8-bit program operation                     | 1.7                | -   | 3.6                | V    |

2. The maximum programming time is measured after 100K erase operations.

| Table 49. Flash memory programming with V <sub>PP</sub> |                                                  |                              |                    |     |                    |      |

|---------------------------------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| Symbol                                                  | Parameter                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

| t <sub>prog</sub>                                       | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>                                  | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>                                  | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>                                 | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>                                         | Mass erase time                                  |                              | -                  | 6.9 | -                  | s    |

| t <sub>BE</sub>                                         | Bank erase time                                  |                              | -                  | 6.9 | -                  | s    |

| V <sub>prog</sub>                                       | Programming voltage                              |                              | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                                         | V <sub>PP</sub> voltage range                    |                              | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                                         | Minimum current sunk on the $V_{\rm PP}$ pin     |                              | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup>                         | Cumulative time during which $V_{PP}$ is applied |                              | -                  | -   | 1                  | hour |

| Table 49. Flash memory | v programming | with $V_{PP}$ |

|------------------------|---------------|---------------|

|------------------------|---------------|---------------|

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value              | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Farameter      | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

Table 50. Flash memory endurance and data retention

2. Cycling performed over the whole temperature range.

## 6.3.14 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                   | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2                      | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP176}, \text{T}_{\text{A}} = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 168 MHz, conforms to<br>IEC 61000-4-2 | 4A              |

Table 51. EMS characteristics

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, PH2, PH3, PH4, PH5, PA3, PA4, PA5, PA6, PA7, PC4, and PC5.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

DocID024244 Rev 10

## 6.3.16 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of – 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 55.

|                  |                                                                                                              | Functional s       |                    |      |

|------------------|--------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                  | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                | - 0                | NA                 |      |

|                  | Injected current on NRST pin                                                                                 | - 0                | NA                 |      |

| I <sub>INJ</sub> | Injected current on PA0, PA1, PA2, PA3, PA6, PA7, PB0, PC0, PC1, PC2, PC3, PC4, PC5, PH1, PH2, PH3, PH4, PH5 | - 0                | NA                 | mA   |

|                  | Injected current on TTa pins: PA4 and PA5                                                                    | - 0                | +5                 |      |

|                  | Injected current on any other FT pin                                                                         | - 5                | NA                 |      |

### Table 55. I/O current injection susceptibility<sup>(1)</sup>

1. NA = not applicable.

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                | Conditions                                               | Min                                 | Max                | Unit |

|--------------------------------|------------------------------------------|----------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup>                                 | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = +8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V | V <sub>DD</sub> - 0.4               | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup>                                  | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> =+ 8mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V  | 2.4                                 | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +20 mA                                 | -                                   | 1.3 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 2.7 V ≤V <sub>DD</sub> ≤3.6 V                            | $V_{DD}$ - 1.3 <sup>(4)</sup>       | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +6 mA                                  | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.8 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA                                  | -                                   | 0.4 <sup>(5)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.7 V ≤V <sub>DD</sub> ≤3.6V                             | $V_{DD}$ -0.4 <sup>(5)</sup>        | -                  | v    |

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 15*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 15 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data.

5. Guaranteed by design.

| Symbol               | Parameter                       | Conditions                                                                       | Min                    | Тур               | Max                    | Unit |

|----------------------|---------------------------------|----------------------------------------------------------------------------------|------------------------|-------------------|------------------------|------|

| t <sub>w(SCKH)</sub> | SCK high and low time           | Master mode, SPI presc = 2,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V                      | T <sub>PCLK</sub> -0.5 | T <sub>PCLK</sub> | T <sub>PCLK</sub> +0.5 |      |

| t <sub>w(SCKL)</sub> |                                 | Master mode, SPI presc = 2,<br>1.7 V≤V <sub>DD</sub> ≤3.6 V                      | T <sub>PCLK</sub> – 2  | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2   |      |

| t <sub>su(NSS)</sub> | NSS setup time                  | Slave mode, SPI presc = 2                                                        | 4T <sub>PCLK</sub>     |                   |                        |      |

| t <sub>h(NSS)</sub>  | NSS hold time                   | Slave mode, SPI presc = 2                                                        | 2T <sub>PCLK</sub>     | -                 | -                      |      |

| t <sub>su(MI)</sub>  | Data input actus timo           | Master mode                                                                      | 3                      | -                 | -                      |      |

| t <sub>su(SI)</sub>  | Data input setup time           | Slave mode                                                                       | 0                      | -                 | -                      | ns   |

| t <sub>h(MI)</sub>   | Data input hold time            | Master mode                                                                      | 0.5                    | -                 | -                      |      |

| t <sub>h(SI)</sub>   | Data input hold time            | Slave mode                                                                       | 2                      | -                 | -                      |      |

| t <sub>a(SO</sub> )  | Data output access time         | Slave mode, SPI presc = 2                                                        | 0                      | -                 | 4T <sub>PCLK</sub>     |      |

| +                    | is(SO) Data output disable time | Slave mode, SPI1/4/5/6,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V                          | 0                      | -                 | 8.5                    |      |

| <sup>ı</sup> dis(SO) |                                 | Slave mode, SPI1/2/3/4/5/6 and<br>1.7 V≤V <sub>DD</sub> ≤3.6 V                   | 0                      | -                 | 16.5                   |      |

|                      |                                 | Slave mode (after enable edge),<br>SPI1/4/5/6 and 2.7V $\leq V_{DD} \leq 3.6V$   | -                      | 11                | 13                     |      |

| t <sub>v(SO)</sub>   | Data output valid/hold          | Slave mode (after enable edge),<br>SPI2/3, 2.7 V≤V <sub>DD</sub> ≤3.6 V          | -                      | 14                | 15                     |      |

| t <sub>h(SO)</sub>   | time                            | Slave mode (after enable edge),<br>SPI1/4/5/6, 1.7 V≤V <sub>DD</sub> ≤3.6 V      | -                      | 15.5              | 19                     |      |

|                      |                                 | Slave mode (after enable edge),<br>SPI2/3, 1.7 V≤V <sub>DD</sub> ≤3.6 V          | -                      | 15.5              | 17.5                   | ns   |

| +                    | Data output valid time          | Master mode (after enable edge),<br>SPI1/4/5/6, 2.7 V≤V <sub>DD</sub> ≤3.6 V     | -                      | -                 | 2.5                    |      |

| t <sub>v(MO)</sub>   | Data output valid time          | Master mode (after enable edge),<br>SPI1/2/3/4/5/6, 1.7 V≤V <sub>DD</sub> ≤3.6 V | -                      | -                 | 4.5                    |      |

| t <sub>h(MO)</sub>   | Data output hold time           | Master mode (after enable edge)                                                  | 0                      | -                 | -                      |      |

| Table 62. SPI o | ynamic characteristics <sup>(1)</sup> | (continued) |

|-----------------|---------------------------------------|-------------|

|-----------------|---------------------------------------|-------------|

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50%

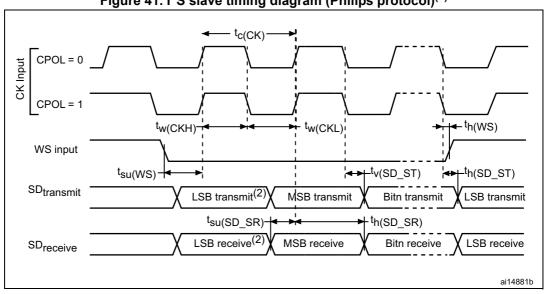

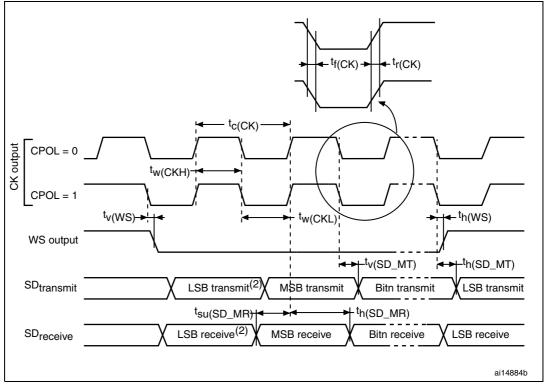

Figure 41. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. .LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

### Figure 42. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

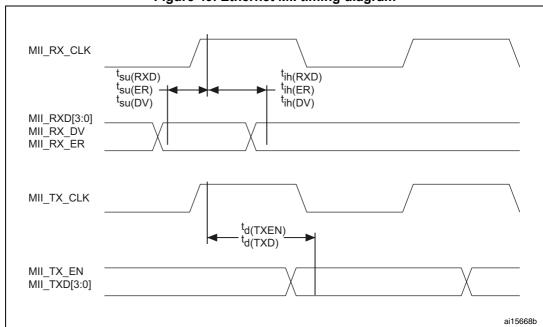

Figure 49. Ethernet MII timing diagram

| Table 73. Dynamics characteristics: Ethernet MAC signals for MII <sup>(1)</sup> |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Symbol               | Parameter                        | Condition                        | Min | Тур | Max | Unit |

|----------------------|----------------------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          |                                  | 9   | -   | -   |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           |                                  | 10  | -   | -   |      |

| t <sub>su(DV)</sub>  | Data valid setup time            | 1.71 V < V <sub>DD</sub> < 3.6 V | 9   | -   | -   |      |

| t <sub>ih(DV)</sub>  | Data valid hold time             | $1.71 v < v_{DD} < 3.0 v$        | 8   | -   | -   |      |

| t <sub>su(ER)</sub>  | Error setup time                 |                                  | 6   | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  |                                  | 8   | -   | -   | 115  |

| +                    | Transmit anable valid dolov time | 2.7 V < V <sub>DD</sub> < 3.6 V  | 8   | 10  | 14  |      |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 1.71 V < V <sub>DD</sub> < 3.6 V | 8   | 10  | 16  |      |

| +                    | Transmit data valid delay time   | 2.7 V < V <sub>DD</sub> < 3.6 V  | 7.5 | 10  | 15  |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 1.71 V < V <sub>DD</sub> < 3.6 V | 7.5 | 10  | 17  |      |

### CAN (controller area network) interface

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (CANx\_TX and CANx\_RX).

| Symbol                      | Parameter                                  | Min                    | Max | Unit |

|-----------------------------|--------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period, VDD range= 2.7 to 3.6 V    | 2T <sub>HCLK</sub> – 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                      | 1.5 | ns   |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub>      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -                      | 0   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 0                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -                      | 0   | ns   |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>      | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -                      | 0   | ns   |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high               | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -                      | 3   | ns   |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0                      | -   | ns   |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -                      | 3   | ns   |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | 0                      | -   | ns   |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 4                      | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 0                      | -   | ns   |

Table 95. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

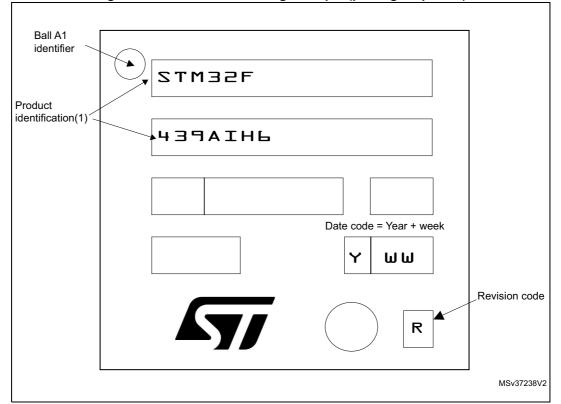

### **Device marking for UFBGA169**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

### Figure 97. UFBGA169 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

|             | Table 124. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Date        | Revision                                         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 28-Sep-2015 | 7                                                | Updated notes related to the minimum and maximum values<br>guaranteed by design, characterization or test in production.<br>Updated I <sub>DD_STOP_UDM</sub> in <i>Table 27: Typical and maximum current</i><br><i>consumptions in Stop mode</i> .<br>Removed note related to tests in production in <i>Table 24: Typical and</i><br><i>maximum current consumption in Run mode, code with data</i><br><i>processing running from Flash memory</i> ( <i>ART accelerator enabled</i><br><i>except prefetch) or RAM</i> and <i>Table 26: Typical and maximum current</i><br><i>consumption in Sleep mode</i> .<br>Updated <i>Table 41: HSI oscillator characteristics. Figure 31</i> renamed<br><i>ACCHSI accuracy versus temperature</i> and updated.<br>Updated <i>Figure 38: SPI timing diagram - slave mode and CPHA = 0.</i><br>Updated <i>Section : Ethernet characteristics, Table 44: PLLI2S</i> ( <i>audio</i><br><i>PLL) characteristics</i> and <i>Table 45: PLLISAI</i> ( <i>audio and LCD-TFT PLL</i> )<br><i>characteristics.</i><br>Removed note 1 in <i>Table 75: ADC static accuracy at fADC = 18 MHz,</i><br><i>Table 76: ADC static accuracy at fADC = 30 MHz</i> and <i>Table 77: ADC</i><br><i>static accuracy at fADC = 36 MHz.</i><br>Updated t <sub>d</sub> (SDCLKL_Data) and t <sub>h</sub> (SDCLKL_Data) in <i>Table 104: SDRAM</i><br><i>write timings.</i><br>Updated note below marking schematics.<br>Added Figure 96: UFBGA169 - 169-ball, 7 x 7 mm, 0.50 mm pitch, ultra<br><i>fine pitch ball grid array recommended footprint</i> and <i>Table 117:</i><br>UFBGA169 recommended PCB design rules (0.5 mm pitch, gent).<br>Added Figure 99: UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch,<br>ultra fine pitch ball grid array package recommended footprint and<br>Table 119: UFBGA176+25 recommended PCB design rules (0.65 mm<br>pitch, BGA). |  |  |  |  |  |

| 30-Nov-2015 | 8                                                | Updated $ V_{SSX} - V_{SS} $ in Table 14: Voltage characteristics to add $V_{REF}$ .<br>Updated $t_{d(TXEN)}$ and $t_{d(TXD)}$ minimum value in Table 72: Dynamics<br>characteristics: Ethernet MAC signals for RMII and Table 73: Dynamics<br>characteristics: Ethernet MAC signals for MII.<br>Added $V_{REF}$ in Table 74: ADC characteristics.<br>Added A1 minimum and maximum values in Table 111: WLCSP143 -<br>143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale<br>package mechanical data.<br>Updated Figure 86: LQFP144-144-pin, 20 x 20 mm low-profile quad<br>flat package outline.Updated Figure 98: UFBGA176+25 - ball 10 x<br>10 mm, 0.65 mm pitch ultra thin fine pitch ball grid array package<br>outline and Table 118: UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm<br>pitch, ultra fine pitch ball grid array package mechanical data.<br>Updated Figure 101: TFBGA216 - 216 ball 13 × 13 mm 0.8 mm pitch<br>thin fine pitch ball grid array package outline and Table 120:<br>TFBGA216 - 216 ball 13 × 13 mm 0.8 mm pitch thin fine pitch ball grid<br>array package mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Table 124 | . Document | revision | history | (continued) |

|-----------|------------|----------|---------|-------------|

|-----------|------------|----------|---------|-------------|