Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 169-UFBGA                                                                           |

| Supplier Device Package    | 169-UFBGA (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f439aih6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 44.<br>Figure 45.<br>Figure 46. | SAI slave timing waveforms                                                      | 152 |

|----------------------------------------|---------------------------------------------------------------------------------|-----|

| Figure 47.                             | Ethernet SMI timing diagram                                                     |     |

| Figure 48.                             | Ethernet RMII timing diagram                                                    |     |

| Figure 49.                             | Ethernet MII timing diagram                                                     |     |

| Figure 50.                             | ADC accuracy characteristics                                                    |     |

| Figure 51.                             | Typical connection diagram using the ADC                                        |     |

| Figure 52.                             | Power supply and reference decoupling ( $V_{RFF+}$ not connected to $V_{DDA}$ ) |     |

| Figure 53.                             | Power supply and reference decoupling ( $V_{REF+}$ not connected to $V_{DDA}$ ) |     |

| Figure 54.                             | 12-bit buffered /non-buffered DAC                                               |     |

| Figure 55.                             | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                      |     |

| Figure 56.                             | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                     |     |

| -                                      | Asynchronous multiplexed PSRAM/NOR read waveforms.                              |     |

| Figure 57.                             | Asynchronous multiplexed PSRAM/NOR vite waveforms                               |     |

| Figure 58.                             |                                                                                 |     |

| Figure 59.                             | Synchronous multiplexed NOR/PSRAM read timings                                  |     |

| Figure 60.                             | Synchronous multiplexed PSRAM write timings.                                    |     |

| Figure 61.                             | Synchronous non-multiplexed NOR/PSRAM read timings                              |     |

| Figure 62.                             | Synchronous non-multiplexed PSRAM write timings                                 |     |

| Figure 63.                             | PC Card/CompactFlash controller waveforms for common memory read access         |     |

| Figure 64.                             | PC Card/CompactFlash controller waveforms for common memory write access        | 183 |

| Figure 65.                             | PC Card/CompactFlash controller waveforms for attribute memory                  |     |

|                                        | read access                                                                     | 184 |

| Figure 66.                             | PC Card/CompactFlash controller waveforms for attribute memory                  |     |

|                                        | write access                                                                    |     |

| Figure 67.                             | PC Card/CompactFlash controller waveforms for I/O space read access             |     |

| Figure 68.                             | PC Card/CompactFlash controller waveforms for I/O space write access            |     |

| Figure 69.                             | NAND controller waveforms for read access                                       | 188 |

| Figure 70.                             | NAND controller waveforms for write access                                      | 188 |

| Figure 71.                             | NAND controller waveforms for common memory read access                         | 189 |

| Figure 72.                             | NAND controller waveforms for common memory write access                        | 189 |

| Figure 73.                             | SDRAM read access waveforms (CL = 1)                                            | 190 |

| Figure 74.                             | SDRAM write access waveforms                                                    | 192 |

| Figure 75.                             | DCMI timing diagram                                                             | 194 |

| Figure 76.                             | LCD-TFT horizontal timing diagram                                               | 196 |

| Figure 77.                             | LCD-TFT vertical timing diagram                                                 |     |

| Figure 78.                             | SDIO high-speed mode                                                            |     |

| Figure 79.                             | SD default mode                                                                 |     |

| Figure 80.                             | LQFP100 -100-pin, 14 x 14 mm low-profile quad flat package outline              | 199 |

| Figure 81.                             | LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat                             |     |

|                                        | recommended footprint.                                                          | 201 |

| Figure 82.                             | LQFP100 marking example (package top view).                                     |     |

| Figure 83.                             | WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale       |     |

| i igui e ee.                           | package outline                                                                 | 203 |

| Figure 84.                             | WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale       | 200 |

| i iguio o i.                           | recommended footprint                                                           | 204 |

| Figure 85.                             | WLCSP143 marking example (package top view)                                     |     |

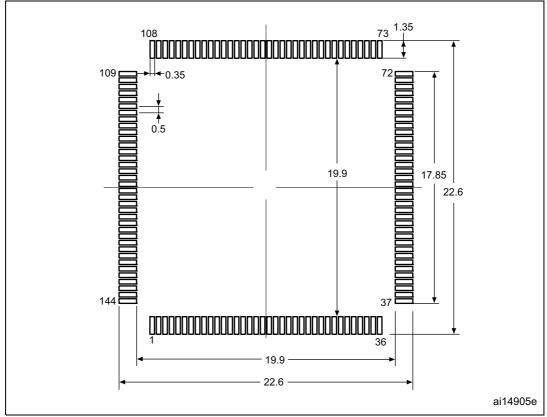

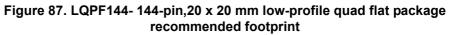

| Figure 86.                             | LQFP144-144-pin, 20 x 20 mm low-profile quad flat package outline               |     |

| Figure 87.                             | LQPF144- 144-pin, 20 x 20 mm low-profile quad flat package                      | 200 |

| i igule or.                            | recommended footprint.                                                          | 208 |

| Figure 88.                             | LQFP144 marking example (package top view).                                     |     |

| Figure 89.                             | LQFP176 - 176-pin, 24 x 24 mm low-profile quad flat package outline             |     |

| . iguie 00.                            |                                                                                 |     |

DocID024244 Rev 10

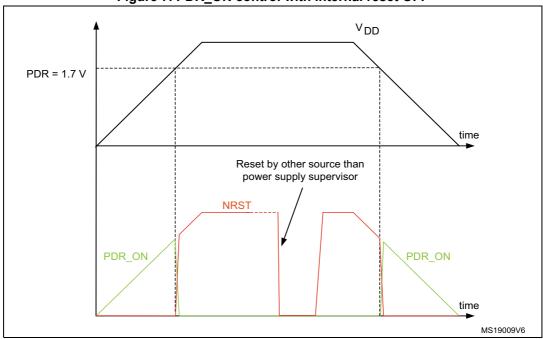

Figure 7. PDR\_ON control with internal reset OFF

### 3.18 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

#### 3.18.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR mode used in Run/sleep modes or in Stop modes

- In Run/Sleep mode

The MR mode is used either in the normal mode (default mode) or the over-drive mode (enabled by software). Different voltages scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). 256 bytes of SRAM are allocated for each CAN.

## 3.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

### 3.34 Universal serial bus on-the-go high-speed (OTG\_HS)

The devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1 Kbit × 35 with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

Fast I/O handling allowing maximum I/O toggling up to 90 MHz.

### 3.39 Analog-to-digital converters (ADCs)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4, TIM5, or TIM8 timer.

### 3.40 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

## 3.41 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 10-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

### 3.42 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 3.43 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F43x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|   |                |       | Figur  | e 12. J | TIVIJZE | 438 88 | LUGFI  | 45 Dai | iout   |            |            |

|---|----------------|-------|--------|---------|---------|--------|--------|--------|--------|------------|------------|

| ī | 11             | 10    | 9      | 8       | 7       | 6      | 5      | 4      | 3      | 2          | 1          |

| А |                | (PE1) | (PB8)  | (PB6)   | PG15    | PG12   | PD7    | PD5    | PD2    | PC10       | VDD        |

| в | PE4            | PE0   | (PB9)  | (PB7)   | (PB3)   | PG11   | (PD4)  | (PD3)  | PD0    | PC11       | PA14       |

| с | VBAT           | (PE3) |        | (PB5)   | (PB4)   | PG10   | VDD    | (PD1)  | PC12   | PA15       | VDD        |

| D | PC14           | PC13  | PE5    | PE2     | VDD     | PG13   | (PA10) | (PA11) | (PA13) | vss        | VCAP<br>_2 |

| E | PC15           | VDD   | (PF1)  | PE6     | vss     | VDD    | PG9    | PC8    | PC9    | PA9        | (PA12)     |

| F | PF0            | PF2   | (PF4)  | PF5     | (PF7)   | PG14   | vss    | PD6    | PC7    | PC6        | PA8        |

| G | (PF3)          | PF6   | (PF10) | (PF9)   | VDD     | PG5    | PG4    | PG6    | (PG3)  | PG8        | VDD        |

| н | PF8            | (PH1) | NRST   | PC0     | vss     | (PD12) | (PD13) | PD10   | vss    | vss        | PG7        |

| J | (PH0)          | PC2   | PC3    | VDD     | VDD     | VDD    | VDD    | (PE10) | PB15   | (PD14)     | (PG2)      |

| к | PC1            | VSSA  | PAO    | (PA1)   | (PB1)   | (PF13) | (PG1)  | (PE11) | (PB14) | (PD11)     | PD15       |

| L | VREF<br>+      | VDDA  | (PA2)  | (PA7)   | (PB2)   | (PF14) | (PE7)  | PE12   | PE15   | PD8        | VDD        |

| м | (PA3)          | (PA4) | PA5    | PC4     | (PF11)  | (PF15) | PE8    | PE14   | (PB10) | (PB12)     | PD9        |

| N | BYPASS_<br>REG | (PA6) | PC5    | PB0     | (PF12)  | PG0    | PE9    | PE13   | (PB11) | VCAP<br>_1 | PB13       |

| l |                |       |        |         |         |        |        |        |        |            | M          |

Figure 12. STM32F43x WLCSP143 ballout

1. The above figure shows the package bump view.

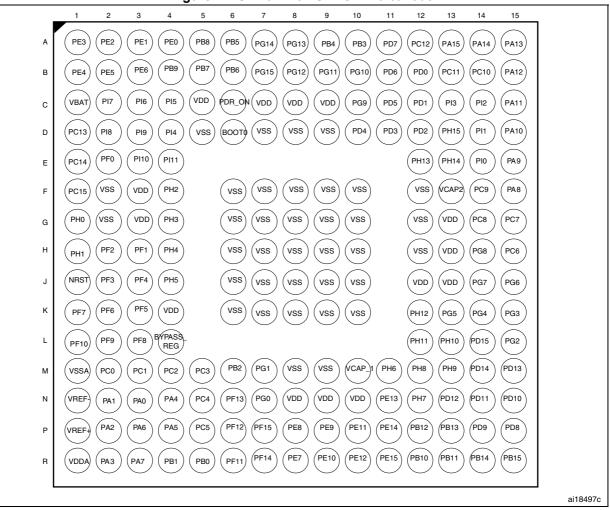

Figure 17. STM32F43x UFBGA176 ballout

1. The above figure shows the package top view.

|         |         |          | Pin nı   | Imbe    | r        |         |          |                                                      |          |                 |       |                                                                                                                     |                             |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                                 | Additional<br>functions     |

| -       | _       | M1       | L4       | 48      | N11      | -       | L5       | BYPASS_<br>REG                                       | I        | FT              | -     | -                                                                                                                   | -                           |

| 28      | 39      | J11      | K4       | 49      | J8       | 52      | K5       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| 29      | 40      | N2       | N4       | 50      | M10      | 53      | N4       | PA4                                                  | I/O      | ТТа             | (5)   | SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK,<br>OTG_HS_SOF,<br>DCMI_HSYNC,<br>LCD_VSYNC,<br>EVENTOUT                | ADC12_<br>IN4 /DAC_<br>OUT1 |

| 30      | 41      | М3       | P4       | 51      | M9       | 54      | P4       | PA5                                                  | I/O      | ТТа             | (5)   | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK,<br>OTG_HS_ULPI_CK,<br>EVENTOUT                                        | ADC12_<br>IN5/DAC_<br>OUT2  |

| 31      | 42      | N3       | P3       | 52      | N10      | 55      | P3       | PA6                                                  | I/O      | FT              | (5)   | TIM1_BKIN,<br>TIM3_CH1,<br>TIM8_BKIN,<br>SPI1_MISO,<br>TIM13_CH1,<br>DCMI_PIXCLK,<br>LCD_G2, EVENTOUT               | ADC12_<br>IN6               |

| 32      | 43      | K4       | R3       | 53      | L8       | 56      | R3       | PA7                                                  | I/O      | FT              | (5)   | TIM1_CH1N,<br>TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI,<br>TIM14_CH1,<br>ETH_MII_RX_DV/ETH_<br>RMII_CRS_DV,<br>EVENTOUT | ADC12_<br>IN7               |

| 33      | 44      | L4       | N5       | 54      | M8       | 57      | N5       | PC4                                                  | I/O      | FT              | (5)   | ETH_MII_RXD0/ETH_<br>RMII_RXD0,<br>EVENTOUT                                                                         | ADC12_<br>IN14              |

| 34      | 45      | M4       | P5       | 55      | N9       | 58      | P5       | PC5                                                  | I/O      | FT              | (5)   | ETH_MII_RXD1/ETH_<br>RMII_RXD1,<br>EVENTOUT                                                                         | ADC12_<br>IN15              |

| -       | -       | -        | -        | -       | J7       | 59      | L7       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| -       | -       | -        | -        | -       | -        | 60      | L6       | VSS                                                  | S        | -               | -     | -                                                                                                                   | -                           |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

| Symbol          | Parameter                                                                    | Conditions <sup>(1)</sup>            | Min   | Тур | Мах                       | Unit |  |

|-----------------|------------------------------------------------------------------------------|--------------------------------------|-------|-----|---------------------------|------|--|

|                 | Input voltage on RST and FT                                                  | 2 V ≤V <sub>DD</sub> ≤3.6 V          | - 0.3 | -   | 5.5                       |      |  |

|                 | pins <sup>(7)</sup>                                                          | V <sub>DD</sub> ≤2 V                 | - 0.3 | -   | 5.2                       |      |  |

| V <sub>IN</sub> | Input voltage on TTa pins                                                    |                                      | - 0.3 | -   | V <sub>DDA</sub> +<br>0.3 | V    |  |

|                 | Input voltage on BOOT0 pin                                                   |                                      | 0     | -   | 9                         |      |  |

|                 |                                                                              | LQFP100                              | -     | -   | 465                       |      |  |

|                 |                                                                              | WLCSP143                             | -     | -   | 641                       |      |  |

|                 |                                                                              | LQFP144                              | -     | -   | 500                       |      |  |

|                 | Power dissipation at $T_A = 85 \degree C$                                    | UFBGA169                             | -     | -   | 385                       |      |  |

| $P_D$           | $P_D$ for suffix 6 or T <sub>A</sub> = 105 °C for<br>suffix 7 <sup>(8)</sup> | LQFP176                              | -     | -   | 526                       | mW   |  |

|                 |                                                                              | UFBGA176                             | -     | -   | 513                       |      |  |

|                 |                                                                              | LQFP208                              | -     | -   | 1053                      |      |  |

|                 |                                                                              | TFBGA216                             | -     | -   | 690                       |      |  |

|                 | Ambient temperature for 6 suffix                                             | Maximum power dissipation            | - 40  |     | 85                        | °C   |  |

| т.              | version                                                                      | Low power dissipation <sup>(9)</sup> | - 40  |     | 105                       |      |  |

| ΤΑ              | Ambient temperature for 7 suffix                                             | Maximum power dissipation            | - 40  |     | 105                       | ;    |  |

|                 | version                                                                      | Low power dissipation <sup>(9)</sup> | - 40  |     | 125                       | °C   |  |

| ТJ              | lunction tomporature range                                                   | 6 suffix version                     | - 40  |     | 105                       | °C   |  |

| IJ              | Junction temperature range                                                   | 7 suffix version                     | - 40  |     | 125                       |      |  |

Table 17. General operating conditions (continued)

1. The over-drive mode is not supported at the voltage ranges from 1.7 to 2.1 V.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

3. When the ADC is used, refer to *Table 74: ADC characteristics*.

4. If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF+} < 1.2$  V.

5. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

- 6. The over-drive mode is not supported when the internal regulator is OFF.

- 7. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

8. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

9. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

|                                  | sie III i eeet alla pell                                                            |                                                                                           |     |     |     |      |

|----------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Symbol                           | Parameter                                                                           | Conditions                                                                                | Min | Тур | Max | Unit |

| I <sub>RUSH</sub> <sup>(1)</sup> | InRush current on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby) |                                                                                           | -   | 160 | 200 | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup> | InRush energy on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -   | -   | 5.4 | μC   |

Table 22. reset and power control block characteristics (continued)

1. Guaranteed by design.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

### 6.3.6 Over-drive switching characteristics

When the over-drive mode switches from enabled to disabled or disabled to enabled, the system clock is stalled during the internal voltage set-up.

The over-drive switching characteristics are given in *Table 23*. They are sbject to general operating conditions for  $T_A$ .

| Symbol    | Parameter                        | Conditions                              | Min | Тур | Max | Unit |

|-----------|----------------------------------|-----------------------------------------|-----|-----|-----|------|

|           |                                  | HSI                                     | -   | 45  | -   |      |

| Tod_swen  | Over_drive switch<br>enable time | HSE max for 4 MHz<br>and min for 26 MHz | 45  | -   | 100 |      |

|           |                                  | External HSE<br>50 MHz                  | -   | 40  | -   | 116  |

|           |                                  | HSI                                     | -   | 20  | -   | μs   |

| Tod_swdis | Over_drive switch disable time   | HSE max for 4 MHz and min for 26 MHz.   | 20  | -   | 80  |      |

|           |                                  | External HSE<br>50 MHz                  | -   | 15  | -   |      |

Table 23. Over-drive switching characteristics<sup>(1)</sup>

1. Guaranteed by design.

| Symbol                             | Deremeter                       | Conditions                  | £ (MU-)                 | VDD:              | =3.3 V          | VDD               | =1.7 V          | Unit |

|------------------------------------|---------------------------------|-----------------------------|-------------------------|-------------------|-----------------|-------------------|-----------------|------|

| Symbol                             | Symbol Parameter                |                             | f <sub>HCLK</sub> (MHz) | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub> | I <sub>DD</sub> |      |

|                                    |                                 |                             | 180                     | 61.5              | 1.4             | -                 | -               |      |

|                                    |                                 |                             | 168                     | 59.4              | 1.3             | 59.4              | 1.0             |      |

|                                    |                                 |                             | 150                     | 53.9              | 1.3             | 53.9              | 1.0             |      |

|                                    |                                 |                             | 144                     | 49.0              | 1.3             | 49.0              | 1.0             |      |

|                                    |                                 | All Peripherals<br>enabled  | 120                     | 38.0              | 1.2             | 38.0              | 0.9             |      |

|                                    |                                 | 0.102.00                    | 90                      | 29.3              | 1.4             | 29.3              | 1.1             |      |

|                                    |                                 |                             | 60                      | 20.2              | 1.2             | 20.2              | 0.9             |      |

|                                    | Our also summer t               |                             | 30                      | 11.9              | 1.2             | 11.9              | 0.9             |      |

| 1 /1                               | Supply current<br>in Sleep mode |                             | 25                      | 10.4              | 1.2             | 10.4              | 0.9             |      |

| I <sub>DD12</sub> /I <sub>DD</sub> | from V <sub>12</sub> and        |                             | 180                     | 14.9              | 1.4             | -                 | -               | mA   |

|                                    | $V_{DD}$ supply                 |                             | 168                     | 14.0              | 1.3             | 14.0              | 1.0             |      |

|                                    |                                 |                             | 150                     | 12.6              | 1.3             | 12.6              | 1.0             |      |

|                                    |                                 |                             | 144                     | 11.5              | 1.3             | 11.5              | 1.0             |      |

|                                    |                                 | All Peripherals<br>disabled | 120                     | 8.7               | 1.2             | 8.7               | 0.9             |      |

|                                    |                                 | aloubiou                    | 90                      | 7.1               | 1.4             | 7.1               | 1.1             |      |

|                                    |                                 |                             | 60                      | 5.0               | 1.2             | 5.0               | 0.9             |      |

|                                    |                                 |                             | 30                      | 3.1               | 1.2             | 3.1               | 0.9             |      |

|                                    |                                 |                             | 25                      | 2.8               | 1.2             | 2.8               | 0.9             |      |

| Table 33. Tyical current consumption in Sleep mode, regulator OFF <sup>(1)</sup> |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

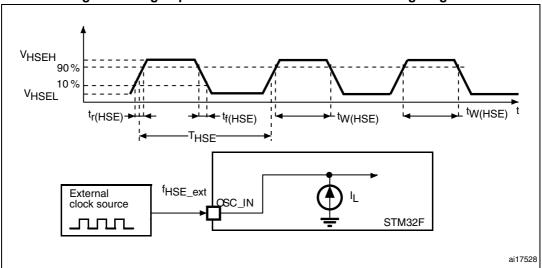

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 28*.

The characteristics given in *Table 38* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                |                                  | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>            |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>           |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>           |                                  | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                          |                                  | 30                 | -      | 70                 | %    |

| ΙL                                         | OSC32_IN Input leakage current                      | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 38. Low-speed externa | al user clock characteristics |

|-----------------------------|-------------------------------|

|-----------------------------|-------------------------------|

1. Guaranteed by design.

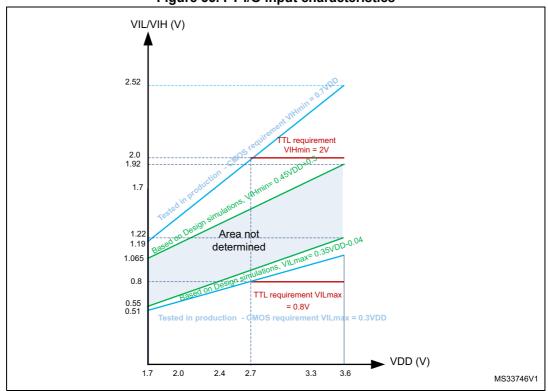

Figure 35. FT I/O input characteristics

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14, PC15 and PI8 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 and PI8 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15*).

### USB OTG full speed (FS) characteristics

This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                                   | Мах | Unit |

|-------------------------------------|---------------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG full speed transceiver startup time | 1   | μs   |

### Table 65. USB OTG full speed startup time

1. Guaranteed by design.

| Symbol          |                                | Parameter                                                 | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |  |

|-----------------|--------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|--|

|                 | V <sub>DD</sub>                | USB OTG full speed<br>transceiver operating<br>voltage    |                                                                  | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |  |

| Input<br>levels | V <sub>DI</sub> <sup>(3)</sup> | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                 | -    | -                   |      |  |

| levels          | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |  |

|                 | $V_{SE}^{(3)}$                 | Single ended receiver threshold                           |                                                                  | 1.3                 | -    | 2.0                 |      |  |

| Output          | V <sub>OL</sub>                | Static output level low                                   | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(4)}$                    | -                   | -    | 0.3                 | v    |  |

| levels          | V <sub>OH</sub>                | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |  |

| R <sub>PD</sub> |                                | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                  | 21   | 24                  |      |  |

|                 |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                        | 0.65                | 1.1  | 2.0                 | kΩ   |  |

| R <sub>PU</sub> |                                | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 |      |  |

|                 |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25                | 0.37 | 0.55                |      |  |

#### Table 66. USB OTG full speed DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The USB OTG full speed transceiver functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V V<sub>DD</sub> voltage range.

3. Guaranteed by design.

4. R<sub>L</sub> is the load connected on the USB OTG full speed drivers.

Note:

When VBUS sensing feature is enabled, PA9 and PB13 should be left at their default state (floating input), not as alternate function. A typical 200  $\mu$ A current consumption of the sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 and PB13 when the feature is enabled.

## 6.3.25 DAC electrical characteristics

| Symbol                            | Parameter                                                                             |            | itions                                                | haracteristics<br>Min Typ Max Unit Co |     | Comments                       |     |                                                                                                                         |  |

|-----------------------------------|---------------------------------------------------------------------------------------|------------|-------------------------------------------------------|---------------------------------------|-----|--------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------|--|

| •                                 |                                                                                       | 00110      |                                                       | 1.7 <sup>(1)</sup>                    |     |                                |     | Commenta                                                                                                                |  |

| V <sub>DDA</sub>                  | Analog supply voltage                                                                 | -          |                                                       | 1.7.9                                 | -   | 3.6                            | V   | -                                                                                                                       |  |

| $V_{REF^+}$                       | Reference supply voltage                                                              | -          |                                                       | 1.7 <sup>(1)</sup>                    | -   | 3.6                            | V   | V <sub>REF+</sub> ⊴V <sub>DDA</sub>                                                                                     |  |

| $V_{SSA}$                         | Ground                                                                                | -          |                                                       | 0                                     | -   | 0                              | V   | -                                                                                                                       |  |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load                                                                        | DAC output | R <sub>LOAD</sub><br>connected<br>to V <sub>SSA</sub> | 5                                     | -   | -                              | kΩ  | -                                                                                                                       |  |

|                                   |                                                                                       | buffer ON  | R <sub>LOAD</sub><br>connected<br>to V <sub>DDA</sub> | 25                                    |     |                                | 112 | -                                                                                                                       |  |

| R <sub>O</sub> <sup>(2)</sup>     | Impedance output with buffer OFF                                                      |            | -                                                     | -                                     | -   | 15                             | kΩ  | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |  |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                                                       |            | -                                                     | -                                     | -   | 50                             | pF  | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |  |

| DAC_O<br>UT<br>min <sup>(2)</sup> | Lower DAC_OUT voltage with buffer ON                                                  |            | -                                                     | 0.2                                   | -   | -                              | v   | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input                                  |  |

| DAC_O<br>UT<br>max <sup>(2)</sup> | Higher DAC_OUT voltage with buffer ON                                                 |            | -                                                     | -                                     | -   | V <sub>DDA</sub><br>- 0.2      | v   | code (0x0E0) to (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V and (0x1C7) to<br>(0xE38) at V <sub>REF+</sub> = 1.7 V          |  |

| DAC_O<br>UT<br>min <sup>(2)</sup> | Lower DAC_OUT<br>voltage with buffer<br>OFF                                           |            | -                                                     | -                                     | 0.5 | -                              | mV  | It gives the maximum output                                                                                             |  |

| DAC_O<br>UT<br>max <sup>(2)</sup> | Higher DAC_OUT<br>voltage with buffer<br>OFF                                          |            | -                                                     | -                                     | -   | V <sub>REF+</sub><br>–<br>1LSB | v   | excursion of the DAC.                                                                                                   |  |

| I <sub>VREF+</sub> <sup>(4)</sup> | DAC DC V <sub>REF</sub> current<br>consumption in<br>quiescent mode<br>(Standby mode) |            |                                                       | -                                     | 170 | 240                            |     | With no load, worst code<br>(0x800) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs         |  |

|                                   |                                                                                       |            | -                                                     | -                                     | 50  | 75                             | μA  | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs         |  |

#### Table 85. DAC characteristics

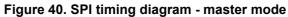

Figure 55. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

| Table 86. Asynchronous non-multiplexed SRAM/PSRAM/NOR - |

|---------------------------------------------------------|

| read timings <sup>(1)(2)</sup>                          |

| read unings (A)                                         |

| Symbol                    | Parameter                             | Min                      | Мах                      | Unit |

|---------------------------|---------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                       | 2T <sub>HCLK</sub> – 0.5 | 2 T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low            | 0                        | 1                        | ns   |

| t <sub>w(NOE)</sub>       | FMC_NOE low time                      | 2T <sub>HCLK</sub>       | 2T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time | 0                        | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid            | -                        | 2                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high  | 0                        | -                        | ns   |

| $t_{v(BL_NE)}$            | FMC_NEx low to FMC_BL valid           | -                        | 2                        | ns   |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time      | T <sub>HCLK</sub> +2     | -                        | ns   |

DocID024244 Rev 10

|                           | -                                         | 0                       |                         |      |  |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|--|

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |  |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 9T <sub>HCLK</sub>      | 9T <sub>HCLK</sub> +0.5 | ns   |  |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 7T <sub>HCLK</sub>      | 7T <sub>HCLK</sub> +2   | ns   |  |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                       | ns   |  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> –1   | -                       | ns   |  |

Table 93. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

#### Synchronous waveforms and timings

*Figure 59* through *Figure 62* represent synchronous waveforms and *Table 94* through *Table 97* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F4xx reference manual : RM0090)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period (with maximum FMC\_CLK = 90 MHz).

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL_Data</sub> )  | Data output valid time | -                        | 3.5                     |      |

| t <sub>h(SDCLKL</sub> _Data)  | Data output hold time  | 0                        | -                       |      |

| $t_{d(SDCLKL_Add)}$           | Address valid time     | -                        | 1.5                     |      |

| t <sub>d(SDCLKL_SDNWE)</sub>  | SDNWE valid time       | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNWE)</sub>  | SDNWE hold time        | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 0.5                     | ns   |

| t <sub>h(SDCLKLSDNE)</sub>    | Chip select hold time  | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 2                       |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 0.5                     |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_NBL)</sub>    | NBL valid time         | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_NBL)</sub>    | NBLoutput time         | 0                        | -                       |      |

# Table 104. SDRAM write timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

## Table 105. LPSDR SDRAM write timings<sup>(1)(2)</sup>

| Symbol                         | Parameter              | Min                      | Max                     | Unit |

|--------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>          | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL _Data</sub> )  | Data output valid time | -                        | 5                       |      |

| t <sub>h(SDCLKL</sub> _Data)   | Data output hold time  | 2                        | -                       |      |

| $t_{d(SDCLKL_Add)}$            | Address valid time     | -                        | 2.8                     |      |

| t <sub>d(SDCLKL-SDNWE)</sub>   | SDNWE valid time       | -                        | 2                       |      |

| t <sub>h(SDCLKL-SDNWE)</sub>   | SDNWE hold time        | 1                        | -                       |      |

| t <sub>d(SDCLKL</sub> - SDNE)  | Chip select valid time | -                        | 1.5                     |      |

| t <sub>h(SDCLKL</sub> - SDNE)  | Chip select hold time  | 1                        | -                       | ns   |

| t <sub>d</sub> (SDCLKL-SDNRAS) | SDNRAS valid time      | -                        | 1.5                     |      |

| t <sub>h(SDCLKL-SDNRAS)</sub>  | SDNRAS hold time       | 1.5                      | -                       |      |

| t <sub>d</sub> (SDCLKL-SDNCAS) | SDNCAS valid time      | -                        | 1.5                     |      |

| t <sub>d</sub> (SDCLKL-SDNCAS) | SDNCAS hold time       | 1.5                      | -                       |      |

| $t_{d(SDCLKL_NBL)}$            | NBL valid time         | -                        | 1.5                     |      |

| t <sub>h(SDCLKL-NBL)</sub>     | NBL output time        | 1.5                      | -                       |      |

1. CL = 10 pF.

2. Guaranteed by characterization results.

1. Dimensions are expressed in millimeters.