Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 168                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

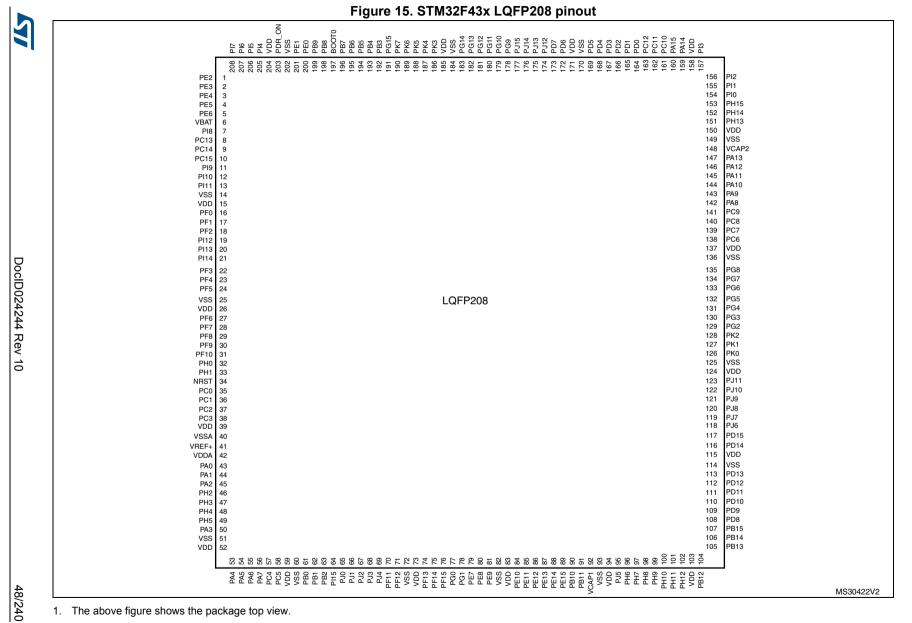

| Package / Case             | 208-LQFP                                                                            |

| Supplier Device Package    | 208-LQFP (28x28)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f439bit6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

communicate at speeds of up to 11.25 Mbit/s. The other available interfaces communicate at up to 5.62 bit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

| USART<br>name | Standard<br>features | Modem<br>(RTS/CTS) | LIN | SPI<br>master | irDA | Smartcard<br>(ISO 7816) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 16) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 8) | APB<br>mapping           |  |  |  |

|---------------|----------------------|--------------------|-----|---------------|------|-------------------------|--------------------------------------------------------|-------------------------------------------------------|--------------------------|--|--|--|

| USART1        | х                    | х                  | х   | х             | х    | х                       | 5.62                                                   | 11.25                                                 | APB2<br>(max.<br>90 MHz) |  |  |  |

| USART2        | х                    | х                  | x   | х             | х    | х                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |  |  |  |

| USART3        | х                    | х                  | x   | х             | x    | х                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |  |  |  |

| UART4         | х                    | -                  | x   | -             | х    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |  |  |  |

| UART5         | х                    | -                  | x   | -             | x    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |  |  |  |

| USART6        | х                    | Х                  | x   | х             | х    | х                       | 5.62                                                   | 11.25                                                 | APB2<br>(max.<br>90 MHz) |  |  |  |

| UART7         | х                    | -                  | х   | -             | х    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |  |  |  |

| UART8         | х                    | -                  | х   | -             | х    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |  |  |  |

| Table 8. | USART | feature | com | parison <sup>(1</sup> | 1) |

|----------|-------|---------|-----|-----------------------|----|

|----------|-------|---------|-----|-----------------------|----|

1. X = feature supported.

# 3.25 Serial peripheral interface (SPI)

The devices feature up to six SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, SPI4, SPI5, and SPI6 can communicate at up to 45 Mbits/s, SPI2 and SPI3 can communicate at up to 22.5 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

DocID024244 Rev 10

# 3.35 Digital camera interface (DCMI)

The devices embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbyte/s at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

# 3.36 Cryptographic acceleration

The devices embed a cryptographic accelerator. This cryptographic accelerator provides a set of hardware acceleration for the advanced cryptographic algorithms usually needed to provide confidentiality, authentication, data integrity and non repudiation when exchanging messages with a peer.

• These algorithms consists of:

Encryption/Decryption

- DES/TDES (data encryption standard/triple data encryption standard): ECB (electronic codebook) and CBC (cipher block chaining) chaining algorithms, 64-, 128- or 192-bit key

- AES (advanced encryption standard): ECB, CBC, GCM, CCM, and CTR (counter mode) chaining algorithms, 128, 192 or 256-bit key

Universal hash

- SHA-1 and SHA-2 (secure hash algorithms)

- MD5

- HMAC

The cryptographic accelerator supports DMA request generation.

## 3.37 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

# 3.38 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

DocID024244 Rev 10

Pinouts and pin description

STM32F437xx and STM32F439xx

1. The above figure shows the package top view.

|        |      |                       |                           |              | 2. 31103         | 2643          |                          |                           | . 43988                 | allemale                   | function                       | mapping                 |                   | ieu)                 |                |        |   |

|--------|------|-----------------------|---------------------------|--------------|------------------|---------------|--------------------------|---------------------------|-------------------------|----------------------------|--------------------------------|-------------------------|-------------------|----------------------|----------------|--------|---|

|        |      | AF0                   | AF1                       | AF2          | AF3              | AF4           | AF5                      | AF6                       | AF7                     | AF8                        | AF9                            | AF10                    | AF11              | AF12                 | AF13           | AF14   |   |

| Po     | ort  | SYS                   | TIM1/2                    | TIM3/4/5     | TIM8/9/<br>10/11 | l2C1/<br>2/3  | SPI1/2/<br>3/4/5/6       | SPI2/3/<br>SAI1           | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН               | FMC/SDIO<br>/OTG2_FS | DCMI           | LCD    |   |

|        | PA13 | JTMS-<br>SWDI<br>O    | -                         | -            | -                | -             | -                        | -                         | -                       | -                          | -                              | -                       | -                 | -                    | -              | -      |   |

| Port A | PA14 | JTCK-<br>SWCL<br>K    | -                         | -            | -                | -             | -                        | -                         | -                       | -                          | -                              | -                       | -                 | -                    | -              | -      |   |

|        | PA15 | JTDI                  | TIM2_<br>CH1/TIM2<br>_ETR | -            | -                | -             | SPI1_<br>NSS             | SPI3_<br>NSS/<br>I2S3_WS  | -                       | -                          | -                              | -                       | -                 | -                    | -              | -      |   |

|        | PB0  | -                     | TIM1_<br>CH2N             | TIM3_<br>CH3 | TIM8_<br>CH2N    | -             | -                        | -                         | -                       | -                          | LCD_R3                         | OTG_HS_<br>ULPI_D1      | ETH_MII_<br>RXD2  | -                    | -              | -      | Ī |

|        | PB1  | -                     | TIM1_<br>CH3N             | TIM3_<br>CH4 | TIM8_<br>CH3N    | -             | -                        | -                         | -                       | -                          | LCD_R6                         | OTG_HS_<br>ULPI_D2      | ETH_MII_<br>RXD3  | -                    | -              | -      |   |

|        | PB2  | -                     | -                         | -            | -                | -             | -                        | -                         | -                       | -                          | -                              | -                       | -                 | -                    | -              | -      |   |

|        | PB3  | JTDO/<br>TRAC<br>ESWO | TIM2_<br>CH2              | -            | -                | -             | SPI1_<br>SCK             | SPI3_<br>SCK/<br>I2S3_CK  | -                       | -                          | -                              | -                       | -                 | -                    | -              | -      |   |

|        | PB4  | NJTR<br>ST            | -                         | TIM3_<br>CH1 | -                | -             | SPI1_<br>MISO            | SPI3_<br>MISO             | I2S3ext_<br>SD          | -                          | -                              | -                       | -                 | -                    | -              | -      |   |

| Port B | PB5  | -                     | -                         | TIM3_<br>CH2 | -                | I2C1_<br>SMBA | SPI1_<br>MOSI            | SPI3_<br>MOSI/<br>I2S3_SD | -                       | -                          | CAN2_RX                        | OTG_HS_<br>ULPI_D7      | ETH_PPS<br>_OUT   | FMC_<br>SDCKE1       | DCMI_<br>D10   | -      |   |

|        | PB6  | -                     | -                         | TIM4_<br>CH1 | -                | I2C1_<br>SCL  | -                        | -                         | USART1_<br>TX           | -                          | CAN2_TX                        | -                       | -                 | FMC_<br>SDNE1        | DCMI_<br>D5    | -      |   |

|        | PB7  | -                     | -                         | TIM4_<br>CH2 | -                | I2C1_<br>SDA  | -                        | -                         | USART1_<br>RX           | -                          | -                              | -                       | -                 | FMC_NL               | DCMI_<br>VSYNC | -      |   |

|        | PB8  | -                     | -                         | TIM4_<br>CH3 | TIM10_<br>CH1    | I2C1_<br>SCL  | -                        | -                         | -                       | -                          | CAN1_RX                        | -                       | ETH_MII_<br>TXD3  | SDIO_D4              | DCMI_<br>D6    | LCD_B6 |   |

|        | PB9  | -                     | -                         | TIM4_<br>CH4 | TIM11_<br>CH1    | I2C1_<br>SDA  | SPI2_<br>NSS/I2<br>S2_WS | -                         | -                       | -                          | CAN1_TX                        | -                       | -                 | SDIO_D5              | DCMI_<br>D7    | LCD_B7 |   |

|        | PB10 | -                     | TIM2_<br>CH3              | -            | -                | I2C2_<br>SCL  | SPI2_<br>SCK/I2<br>S2_CK | -                         | USART3_<br>TX           | -                          | -                              | OTG_HS_<br>ULPI_D3      | ETH_MII_<br>RX_ER | -                    | -              | LCD_G4 |   |

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

DocID024244 Rev 10

STM32F437xx and STM32F439xx

# Pinouts and pin description

AF15

SYS

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN

TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN

TOUT

TOUT EVEN TOUT

EVEN TOUT

EVEN TOUT

DocID024244 Rev 10

79/240

|        |      | AF0 | AF1           | AF2      | AF3              | AF4           | AF5                | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11 | AF12                 | AF13 | AF14        | AF15         |

|--------|------|-----|---------------|----------|------------------|---------------|--------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|------|----------------------|------|-------------|--------------|

| P      | ort  | SYS | TIM1/2        | TIM3/4/5 | TIM8/9/<br>10/11 | I2C1/<br>2/3  | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ETH  | FMC/SDIO<br>/OTG2_FS | DCMI | LCD         | SYS          |

|        | PE7  | -   | TIM1_<br>ETR  | -        | -                | -             | -                  | -               | -                       | UART7_Rx                   | -                              | -                       | -    | FMC_D4               | -    | -           | EVEN<br>TOUT |

|        | PE8  | -   | TIM1_<br>CH1N | -        | -                | -             | -                  | -               | -                       | UART7_Tx                   | -                              | -                       | -    | FMC_D5               | -    | -           | EVEN<br>TOUT |

|        | PE9  | -   | TIM1_<br>CH1  | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_D6               | -    | -           | EVEN<br>TOUT |

|        | PE10 | -   | TIM1_<br>CH2N | -        | -                | -             | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_D7               | -    | -           | EVEN<br>TOUT |

| Port E | PE11 | -   | TIM1_<br>CH2  | -        | -                | -             | SPI4_<br>NSS       | -               | -                       | -                          | -                              | -                       | -    | FMC_D8               | -    | LCD_G3      | EVEN<br>TOUT |

|        | PE12 | -   | TIM1_<br>CH3N | -        | -                | -             | SPI4_<br>SCK       | -               | -                       | -                          | -                              | -                       | -    | FMC_D9               | -    | LCD_B4      | EVEN<br>TOUT |

|        | PE13 | -   | TIM1_<br>CH3  | -        | -                | -             | SPI4_<br>MISO      | -               | -                       | -                          | -                              | -                       | -    | FMC_D10              | -    | LCD_DE      | EVEN<br>TOUT |

|        | PE14 | -   | TIM1_<br>CH4  | -        | -                | -             | SPI4_<br>MOSI      | -               | -                       | -                          | -                              | -                       | -    | FMC_D11              | -    | LCD_<br>CLK | EVEN<br>TOUT |

|        | PE15 | -   | TIM1_<br>BKIN | -        | -                | -             |                    | -               | -                       | -                          | -                              | -                       | -    | FMC_D12              | -    | LCD_R7      | EVEN<br>TOUT |

|        | PF0  | -   | -             | -        | -                | I2C2_<br>SDA  | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_A0               | -    | -           | EVEN<br>TOUT |

|        | PF1  | -   |               |          |                  | I2C2_<br>SCL  | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_A1               | -    | -           | EVEN<br>TOUT |

|        | PF2  | -   | -             | -        | -                | I2C2_<br>SMBA | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_A2               | -    | -           | EVEN<br>TOUT |

| Port F | PF3  | -   | -             | -        | -                |               | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_A3               | -    | -           | EVEN<br>TOUT |

| Port F | PF4  | -   | -             | -        | -                |               | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_A4               | -    | -           | EVEN<br>TOUT |

|        | PF5  | -   | -             | -        | -                |               | -                  | -               | -                       | -                          | -                              | -                       | -    | FMC_A5               | -    | -           | EVEN<br>TOUT |

|        | PF6  | -   | -             | -        | TIM10_<br>CH1    | -             | SPI5_<br>NSS       | SAI1_<br>SD_B   | -                       | UART7_Rx                   | -                              | -                       | -    | FMC_<br>NIORD        | -    | -           | EVEN<br>TOUT |

|        | PF7  | -   | -             | -        | TIM11_<br>CH1    | -             | SPI5_<br>SCK       | SAI1_<br>MCLK_B | -                       | UART7_Tx                   | -                              | -                       | -    | FMC_<br>NREG         | -    | -           | EVEN<br>TOUT |

## Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

|      | 0x4008 0000- 0x4FFF FFFF  | Reserved                 |

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 BC00- 0x4003 FFFF  | Reserved                 |

|      | 0x4002 B000 - 0x4002 BBFF | DMA2D                    |

|      | 0x4002 9400 - 0x4002 AFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0X4002 5000 - 0X4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| АПВТ | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0X4002 3400 - 0X4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2C00 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2800 - 0x4002 2BFF | GPIOK                    |

|      | 0x4002 2400 - 0x4002 27FF | GPIOJ                    |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0X4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

# Table 13. STM32F437xx and STM32F439xx register boundary addresses (continued)

| Symbol                           | Parameter                                                                           | Conditions                                                                                | Min | Тур | Max | Unit |  |  |  |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|--|--|

| I <sub>RUSH</sub> <sup>(1)</sup> | InRush current on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby) |                                                                                           | -   | 160 | 200 | mA   |  |  |  |  |  |  |

| E <sub>RUSH</sub> <sup>(1)</sup> | InRush energy on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -   | -   | 5.4 | μC   |  |  |  |  |  |  |

Table 22. reset and power control block characteristics (continued)

1. Guaranteed by design.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

## 6.3.6 Over-drive switching characteristics

When the over-drive mode switches from enabled to disabled or disabled to enabled, the system clock is stalled during the internal voltage set-up.

The over-drive switching characteristics are given in *Table 23*. They are sbject to general operating conditions for  $T_A$ .

| Symbol    | Parameter                         | Conditions                              | Min | Тур | Max | Unit |

|-----------|-----------------------------------|-----------------------------------------|-----|-----|-----|------|

|           |                                   | HSI                                     | -   | 45  | -   |      |

| Tod_swen  | Over_drive switch<br>enable time  | HSE max for 4 MHz<br>and min for 26 MHz | 45  | -   | 100 |      |

|           |                                   | External HSE<br>50 MHz                  | -   | 40  | -   | 110  |

|           |                                   | HSI                                     | -   | 20  | -   | μs   |

| Tod_swdis | Over_drive switch<br>disable time | HSE max for 4 MHz and min for 26 MHz.   | 20  | -   | 80  |      |

|           |                                   | External HSE<br>50 MHz                  | -   | 15  | -   |      |

Table 23. Over-drive switching characteristics<sup>(1)</sup>

1. Guaranteed by design.

| Symbol          | Parameter                                                   | Conditions               | f <sub>HCLK</sub> (MHz) | Тур  | Unit |

|-----------------|-------------------------------------------------------------|--------------------------|-------------------------|------|------|

|                 |                                                             |                          | 168                     | 65.5 |      |

|                 |                                                             |                          | 150                     | 55.5 |      |

|                 |                                                             |                          | 144                     | 53.5 |      |

|                 |                                                             | All Deripherale enabled  | 120                     | 39.0 |      |

|                 |                                                             | All Peripherals enabled  | 90                      | 31.6 |      |

|                 |                                                             |                          | 60                      | 21.7 | - mA |

|                 | Supply current in Sleep<br>mode from V <sub>DD</sub> supply |                          | 30                      | 9.8  |      |

|                 |                                                             |                          | 25                      | 8.8  |      |

| I <sub>DD</sub> |                                                             |                          | 168                     | 15.7 |      |

|                 |                                                             |                          | 150                     | 13.7 |      |

|                 |                                                             |                          | 144                     | 12.7 |      |

|                 |                                                             | All Deripherale dischlod | 120                     | 9.7  |      |

|                 |                                                             | All Peripherals disabled | 90                      | 7.7  |      |

|                 |                                                             |                          | 60                      | 5.7  |      |

|                 |                                                             |                          | 30                      | 4.7  |      |

|                 |                                                             |                          | 25                      | 2.8  |      |

| Table 32. Typical curre | nt consumption in Slee | ep mode, regulator Ol  | λ. V <sub>DD</sub> =1.7 V <sup>(1)</sup> |

|-------------------------|------------------------|------------------------|------------------------------------------|

| Table of Typical curre  | ni consumption in oice | spiniouc, regulator of | •, •DD=1./ •                             |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 56: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 35: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DD</sub> is the MCU supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

## 6.3.8 Wakeup time from low-power modes

The wakeup times given in *Table 36* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

| Symbol                              | Parameter                                   | Conditions                                                                              | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                  |

|-------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup> | Wakeup from Sleep                           | -                                                                                       | 6                  | -                  | CPU<br>clock<br>cycle |

|                                     |                                             | Main regulator is ON                                                                    | 13.6               | -                  | _                     |

| twustop <sup>(2)</sup>              | Wakeup from Stop mode                       | Main regulator is ON and Flash memory in Deep power down mode                           | 93                 | 111                |                       |

|                                     | with MR/LP regulator in<br>normal mode      | Low power regulator is ON                                                               | 22                 | 32                 |                       |

|                                     |                                             | Low power regulator is ON and Flash memory in Deep power down mode                      | 103                | 126                | μs                    |

|                                     | Wakeup from Stop mode                       | Main regulator in under-drive mode<br>(Flash memory in Deep power-down<br>mode)         | 105                | 128                |                       |

| t <sub>WUSTOP</sub> <sup>(2)</sup>  | with MR/LP regulator in<br>Under-drive mode | Low power regulator in under-drive<br>mode<br>(Flash memory in Deep power-down<br>mode) | 125                | 155                |                       |

| tWUSTDBY<br>(2)(3)                  | Wakeup from Standby mode                    |                                                                                         | 318                | 412                |                       |

#### Table 36. Low-power mode wakeup timings

1. Guaranteed by characterization results.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first

3.  $t_{WUSTDBY}$  maximum value is given at -40 °C.

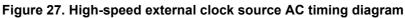

## Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 28*.

The characteristics given in *Table 38* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

| Symbol                                     | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   |                                  | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              |                                  | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             |                                  | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 38. | Low-speed | external us | ser clock chara | acteristics |

|-----------|-----------|-------------|-----------------|-------------|

|-----------|-----------|-------------|-----------------|-------------|

1. Guaranteed by design.

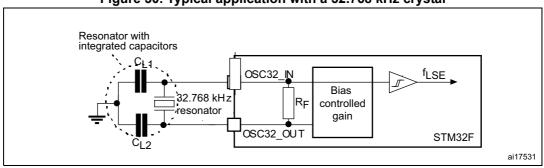

## Figure 30. Typical application with a 32.768 kHz crystal

## 6.3.10 Internal clock source characteristics

The parameters given in *Table 41* and *Table 42* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

### High-speed internal (HSI) RC oscillator

|                                     |                                |                                      | -   |     |     |      |

|-------------------------------------|--------------------------------|--------------------------------------|-----|-----|-----|------|

| Symbol                              | Parameter                      | Conditions                           | Min | Тур | Max | Unit |

| f <sub>HSI</sub>                    | Frequency                      | -                                    | -   | 16  | -   | MHz  |

|                                     | HSI user-trimming step (2)     | -                                    | -   | -   | 1   | %    |

|                                     | Accuracy of the HSI oscillator | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

| ACC <sub>HSI</sub>                  |                                | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

|                                     |                                | $T_A = 25 \ ^{\circ}C^{(4)}$         | - 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time    | -                                    | -   | 2.2 | 4   | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> |                                | -                                    | -   | 60  | 80  | μA   |

Table 41. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

| Symbol                               | Parameter                                    | Condition                                   | 5                  | Min          | Тур         | Мах          | Unit |

|--------------------------------------|----------------------------------------------|---------------------------------------------|--------------------|--------------|-------------|--------------|------|

|                                      |                                              |                                             | RMS                | -            | 25          | -            |      |

|                                      | Cycle-to-cycle jitter                        | System clock                                | peak<br>to<br>peak | -            | ±150        | -            |      |

|                                      |                                              | 120 MHz                                     | RMS                | -            | 15          | -            |      |

| Jitter <sup>(3)</sup>                | Period Jitter                                | i                                           | peak<br>to<br>peak | -            | <u>+200</u> | -            | ps   |

|                                      | Main clock output (MCO) for<br>RMII Ethernet | Cycle to cycle at 50 MHz<br>on 1000 samples |                    | -            | 32          | -            |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet  | Cycle to cycle at 2 on 1000 samples         | -                  | 40           | -           |              |      |

|                                      | Bit Time CAN jitter                          | Cycle to cycle at 1 MHz on 1000 samples     |                    | -            | 330         | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                 | VCO freq = 100 MHz<br>VCO freq = 432 MHz    |                    | 0.15         | _           | 0.40         | mA   |

| UD(PLL)                              |                                              |                                             |                    | 0.45         |             | 0.75         |      |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA                | VCO freq = 100 M<br>VCO freq = 432 M        |                    | 0.30<br>0.55 | -           | 0.40<br>0.85 | mA   |

Table 43. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results.

| Symbol                  | Parameter                         | Conditions                                                              |                    | Min                 | Тур  | Max  | Unit |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> |                                                                         |                    | 0.95 <sup>(2)</sup> | 1    | 2.10 | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock    |                                                                         |                    | -                   | -    | 216  | MHz  |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 |                                                                         |                    | 100                 | -    | 432  | MHz  |

| 1                       |                                   | VCO freq = 100 MHz                                                      | <u>z</u>           | 75                  | -    | 200  |      |

| t <sub>LOCK</sub>       | PLLI2S lock time                  | VCO freq = 432 MHz                                                      | <u>z</u>           | 100                 | -    | 300  | μs   |

|                         | Ma (1.100 do 1. 1. ""             | Cycle to cycle at                                                       | RMS                | -                   | 90   | -    |      |

|                         |                                   | 48KHz period, to<br>N=432, R=5 pea                                      | peak<br>to<br>peak | -                   | ±280 | -    | ps   |

| Jitter <sup>(3)</sup>   | Master I2S clock jitter           | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | of                 | -                   | 90   | -    | ps   |

|                         | WS I2S clock jitter               | Cycle to cycle at 48 KHz<br>on 1000 samples                             |                    | -                   | 400  | -    | ps   |

## Table 44. PLLI2S (audio PLL) characteristics

## 6.3.13 Memory characteristics

## Flash memory

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter      | Conditions                                  | Min | Тур | Max | Unit |

|-----------------|----------------|---------------------------------------------|-----|-----|-----|------|

|                 |                | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 5   | -   |      |

| I <sub>DD</sub> | Supply current | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

|                         | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |

| t <sub>erase128kb</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 16   | 32                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 11   | 22                 | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |

## Table 48. Flash memory programming

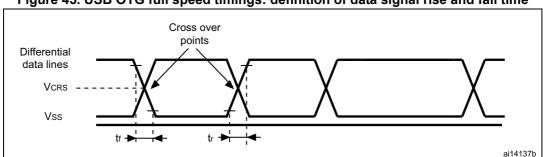

#### Figure 45. USB OTG full speed timings: definition of data signal rise and fall time

#### Table 67. USB OTG full speed electrical characteristics<sup>(1)</sup>

|                  | Driver characteristics                 |                                |     |     |      |  |  |  |  |  |  |

|------------------|----------------------------------------|--------------------------------|-----|-----|------|--|--|--|--|--|--|

| Symbol           | Parameter                              | Conditions                     | Min | Max | Unit |  |  |  |  |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |  |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching               | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |  |  |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage        |                                | 1.3 | 2.0 | V    |  |  |  |  |  |  |

| Z <sub>DRV</sub> | Output driver impedance <sup>(3)</sup> | Driving high or<br>low         | 28  | 44  | Ω    |  |  |  |  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on DP (D+) and DM (D-) pins since the matching impedance is included in the embedded driver.

## USB high speed (HS) characteristics

Unless otherwise specified, the parameters given in *Table 70* for ULPI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 69* and  $V_{DD}$  supply voltage conditions summarized in *Table 68*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10, unless otherwise specified

- Capacitive load C = 30 pF, unless otherwise specified

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

| Symb        | ol              |                              |     | Unit |   |  |  |  |  |  |

|-------------|-----------------|------------------------------|-----|------|---|--|--|--|--|--|

| Input level | V <sub>DD</sub> | USB OTG HS operating voltage | 1.7 | 3.6  | V |  |  |  |  |  |

Table 68. USB HS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

## Table 76. ADC static accuracy at f<sub>ADC</sub> = 30 MHz

1. Guaranteed by characterization results.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |  |  |  |  |  |  |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|--|--|--|--|--|--|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |  |  |  |  |  |  |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |  |  |  |  |  |  |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |  |  |  |  |  |  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |  |  |  |  |  |  |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |  |  |  |  |  |  |

## Table 77. ADC static accuracy at $f_{ADC}$ = 36 MHz

1. Guaranteed by characterization results.

# Table 78. ADC dynamic accuracy at $f_{ADC}$ = 18 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions                                                                                                             | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = V <sub>REF+</sub> = 1.7 V<br>Input Frequency = 20 KHz<br>Temperature = 25 °C | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio |                                                                                                                             | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                |                                                                                                                             | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            |                                                                                                                             | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

# Table 79. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions                                 | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|-------------------------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz                        | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$                    | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz<br>Temperature = 25 °C | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            |                                                 | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

| Symbol                         | Parameter                                 | Min | Мах | Unit |

|--------------------------------|-------------------------------------------|-----|-----|------|

| t <sub>h(CLKH-DV)</sub>        | FMC_D[15:0] valid data after FMC_CLK high | 0   | -   | ns   |

| t <sub>(NWAIT-CLKH)</sub>      | FMC_NWAIT valid before FMC_CLK high       | 4   |     |      |

| t <sub>h(CLKH-</sub><br>NWAIT) | FMC_NWAIT valid after FMC_CLK high        | 0   |     |      |

|  | Table 96. Synchronous non-multip | lexed NOR/PSRAM read timings <sup>(1)(2)</sup> (continued) |

|--|----------------------------------|------------------------------------------------------------|

|--|----------------------------------|------------------------------------------------------------|

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

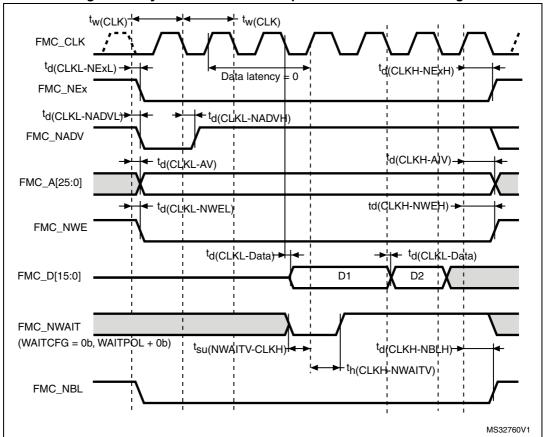

#### Figure 62. Synchronous non-multiplexed PSRAM write timings

|                            |                                      | 0                      |     |      |  |

|----------------------------|--------------------------------------|------------------------|-----|------|--|

| Symbol                     | Parameter                            | Min                    | Мах | Unit |  |

| t <sub>(CLK)</sub>         | FMC_CLK period                       | 2T <sub>HCLK</sub> – 1 | -   | ns   |  |

| t <sub>d(CLKL-NExL)</sub>  | FMC_CLK low to FMC_NEx low (x=02)    | -                      | 0.5 | ns   |  |

| t <sub>(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02) | T <sub>HCLK</sub>      | -   | ns   |  |

| t <sub>d(CLKL-NADVL)</sub> | FMC_CLK low to FMC_NADV low          | -                      | 0   | ns   |  |

| t <sub>d(CLKL-NADVH)</sub> | FMC_CLK low to FMC_NADV high         | 0                      | -   | ns   |  |

| t <sub>d(CLKL-AV)</sub>    | FMC_CLK low to FMC_Ax valid (x=1625) | -                      | 0   | ns   |  |

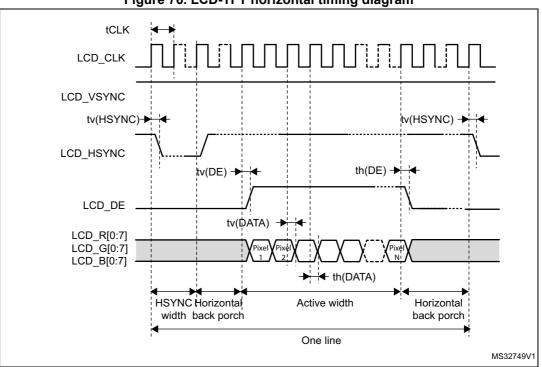

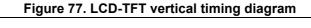

Figure 76. LCD-TFT horizontal timing diagram

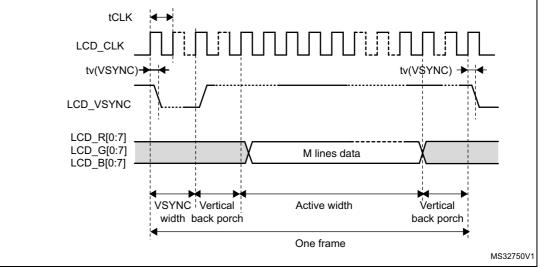

#### **Device marking for UFBGA176+25**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

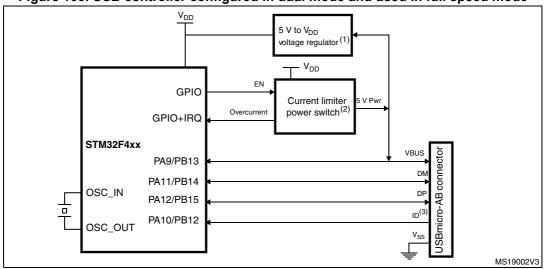

Figure 105. USB controller configured in dual mode and used in full speed mode

- 1. External voltage regulator only needed when building a  $V_{\mbox{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

- 4. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.