Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 140                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | ·                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 201-UFBGA                                                                           |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f439iih6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode: MR operates in normal mode (default mode of MR in stop mode) MR operates in under-drive mode (reduced leakage mode).

LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to Table 3 for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 22: Power supply scheme* and *Table 19: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. - means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

## 3.18.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 17: General operating conditions*. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 22: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

# 3.30 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 3.31 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

The devices include the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F4xx reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

# 3.32 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive

DocID024244 Rev 10

|         |         |           | Pin nu   | ımbei   | r        |         |          |                                                      |          |                 |            |                                                                                          |                              |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|------------|------------------------------------------------------------------------------------------|------------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes      | Alternate functions                                                                      | Additional<br>functions      |

| 4       | 4       | D1        | B2       | 4       | D9       | 4       | B1       | PE5                                                  | I/O      | FT              | -          | TRACED2, TIM9_CH1,<br>SPI4_MISO,<br>SAI1_SCK_A,<br>FMC_A21, DCMI_D6,<br>LCD_G0, EVENTOUT | -                            |

| 5       | 5       | D2        | B3       | 5       | E8       | 5       | B2       | PE6                                                  | I/O      | FT              | _          | TRACED3, TIM9_CH2,<br>SPI4_MOSI,<br>SAI1_SD_A, FMC_A22,<br>DCMI_D7, LCD_G1,<br>EVENTOUT  | -                            |

| -       | -       | -         | -        | -       | -        | I       | G6       | V <sub>SS</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | -         | -        | -       | -        | -       | F5       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| 6       | 6       | E5        | C1       | 6       | C11      | 6       | C1       | V <sub>BAT</sub>                                     | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | NC<br>(2) | D2       | 7       | -        | 7       | C2       | PI8                                                  | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | TAMP_2                       |

| 7       | 7       | E4        | D1       | 8       | D10      | 8       | D1       | PC13                                                 | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | TAMP_1                       |

| 8       | 8       | E1        | E1       | 9       | D11      | 9       | E1       | PC14-<br>OSC32_IN<br>(PC14)                          | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | OSC32_IN                     |

| 9       | 9       | F1        | F1       | 10      | E11      | 10      | F1       | PC15-<br>OSC32_OUT<br>(PC15)                         | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | OSC32_<br>OUT <sup>(5)</sup> |

| -       | -       | -         | -        | -       | -        | -       | G5       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | E2        | D3       | 11      | -        | 11      | E4       | PI9                                                  | I/O      | FT              | -          | CAN1_RX, FMC_D30,<br>LCD_VSYNC,<br>EVENTOUT                                              | -                            |

| -       | -       | E3        | E3       | 12      | -        | 12      | D5       | PI10                                                 | I/O      | FT              | -          | ETH_MII_RX_ER,<br>FMC_D31,<br>LCD_HSYNC,<br>EVENTOUT                                     | -                            |

| -       | -       | NC<br>(2) | E4       | 13      | -        | 13      | F3       | PI11                                                 | I/O      | FT              | -          | OTG_HS_ULPI_DIR,<br>EVENTOUT                                                             | -                            |

| -       | -       | F6        | F2       | 14      | E7       | 14      | F2       | V <sub>SS</sub>                                      | s        | -               | -          | -                                                                                        | -                            |

| -       | -       | F4        | F3       | 15      | E10      | 15      | F4       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

## Pinouts and pin description

| Table 11. FMC pin definition (continued) |        |                    |                  |        |       |  |  |  |  |  |  |  |  |

|------------------------------------------|--------|--------------------|------------------|--------|-------|--|--|--|--|--|--|--|--|

| Pin name                                 | CF     | NOR/PSRAM/<br>SRAM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |  |  |  |  |  |  |  |  |

| PE11                                     | D8     | D8                 | DA8              | D8     | D8    |  |  |  |  |  |  |  |  |

| PE12                                     | D9     | D9                 | DA9              | D9     | D9    |  |  |  |  |  |  |  |  |

| PE13                                     | D10    | D10                | DA10             | D10    | D10   |  |  |  |  |  |  |  |  |

| PE14                                     | D11    | D11                | DA11             | D11    | D11   |  |  |  |  |  |  |  |  |

| PE15                                     | D12    | D12                | DA12             | D12    | D12   |  |  |  |  |  |  |  |  |

| PD8                                      | D13    | D13                | DA13             | D13    | D13   |  |  |  |  |  |  |  |  |

| PD9                                      | D14    | D14                | DA14             | D14    | D14   |  |  |  |  |  |  |  |  |

| PD10                                     | D15    | D15                | DA15             | D15    | D15   |  |  |  |  |  |  |  |  |

| PH8                                      |        | D16                |                  |        | D16   |  |  |  |  |  |  |  |  |

| PH9                                      |        | D17                |                  |        | D17   |  |  |  |  |  |  |  |  |

| PH10                                     |        | D18                |                  |        | D18   |  |  |  |  |  |  |  |  |

| PH11                                     |        | D19                |                  |        | D19   |  |  |  |  |  |  |  |  |

| PH12                                     |        | D20                |                  |        | D20   |  |  |  |  |  |  |  |  |

| PH13                                     |        | D21                |                  |        | D21   |  |  |  |  |  |  |  |  |

| PH14                                     |        | D22                |                  |        | D22   |  |  |  |  |  |  |  |  |

| PH15                                     |        | D23                |                  |        | D23   |  |  |  |  |  |  |  |  |

| PI0                                      |        | D24                |                  |        | D24   |  |  |  |  |  |  |  |  |

| PI1                                      |        | D25                |                  |        | D25   |  |  |  |  |  |  |  |  |

| Pl2                                      |        | D26                |                  |        | D26   |  |  |  |  |  |  |  |  |

| PI3                                      |        | D27                |                  |        | D27   |  |  |  |  |  |  |  |  |

| PI6                                      |        | D28                |                  |        | D28   |  |  |  |  |  |  |  |  |

| PI7                                      |        | D29                |                  |        | D29   |  |  |  |  |  |  |  |  |

| PI9                                      |        | D30                |                  |        | D30   |  |  |  |  |  |  |  |  |

| PI10                                     |        | D31                |                  |        | D31   |  |  |  |  |  |  |  |  |

| PD7                                      |        | NE1                | NE1              | NCE2   |       |  |  |  |  |  |  |  |  |

| PG9                                      |        | NE2                | NE2              | NCE3   |       |  |  |  |  |  |  |  |  |

| PG10                                     | NCE4_1 | NE3                | NE3              |        |       |  |  |  |  |  |  |  |  |

| PG11                                     | NCE4_2 |                    |                  |        |       |  |  |  |  |  |  |  |  |

| PG12                                     |        | NE4                | NE4              |        |       |  |  |  |  |  |  |  |  |

| PD3                                      |        | CLK                | CLK              |        |       |  |  |  |  |  |  |  |  |

| PD4                                      | NOE    | NOE                | NOE              | NOE    |       |  |  |  |  |  |  |  |  |

| PD5                                      | NWE    | NWE                | NWE              | NWE    |       |  |  |  |  |  |  |  |  |

| PD6                                      | NWAIT  | NWAIT              | NWAIT            | NWAIT  |       |  |  |  |  |  |  |  |  |

| PB7                                      |        | NL(NADV)           | NL(NADV)         |        |       |  |  |  |  |  |  |  |  |

## Table 11. FMC pin definition (continued)

| Pin name | CF    | NOR/PSRAM/ | NOR/PSRAM | NAND16 | SDRAM  |

|----------|-------|------------|-----------|--------|--------|

|          |       | SRAM       | Mux       |        |        |

| PF6      | NIORD |            |           |        |        |

| PF7      | NREG  |            |           |        |        |

| PF8      | NIOWR |            |           |        |        |

| PF9      | CD    |            |           |        |        |

| PF10     | INTR  |            |           |        |        |

| PG6      |       |            |           | INT2   |        |

| PG7      |       |            |           | INT3   |        |

| PE0      |       | NBL0       | NBL0      |        | NBL0   |

| PE1      |       | NBL1       | NBL1      |        | NBL1   |

| PI4      |       | NBL2       |           |        | NBL2   |

| PI5      |       | NBL3       |           |        | NBL3   |

| PG8      |       |            |           |        | SDCLK  |

| PC0      |       |            |           |        | SDNWE  |

| PF11     |       |            |           |        | SDNRAS |

| PG15     |       |            |           |        | SDNCAS |

| PH2      |       |            |           |        | SDCKE0 |

| PH3      |       |            |           |        | SDNE0  |

| PH6      |       |            |           |        | SDNE1  |

| PH7      |       |            |           |        | SDCKE1 |

| PH5      |       |            |           |        | SDNWE  |

| PC2      |       |            |           |        | SDNE0  |

| PC3      |       |            |           |        | SDCKE0 |

| PB5      |       |            |           |        | SDCKE1 |

| PB6      |       |            |           |        | SDNE1  |

Table 11. FMC pin definition (continued)

77/240

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

| 77/240             |           |      | AF0  | AF1    | AF2          | AF3              | AF4          | AF5                       | AF6                       | AF7                     | AF8                        | AF9                            | AF10                    | AF11 | AF12                 | AF13         | AF14   | AF15         |

|--------------------|-----------|------|------|--------|--------------|------------------|--------------|---------------------------|---------------------------|-------------------------|----------------------------|--------------------------------|-------------------------|------|----------------------|--------------|--------|--------------|

| 0                  | P         | ort  | SYS  | TIM1/2 | TIM3/4/5     | TIM8/9/<br>10/11 | I2C1/<br>2/3 | SPI1/2/<br>3/4/5/6        | SPI2/3/<br>SAI1           | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН  | FMC/SDIO<br>/OTG2_FS | DCMI         | LCD    | SYS          |

|                    |           | PC8  | -    | -      | TIM3_<br>CH3 | TIM8_<br>CH3     | -            | -                         | -                         | -                       | USART6_<br>CK              | -                              | -                       | -    | SDIO_D0              | DCMI_<br>D2  | -      | EVEN<br>TOUT |

|                    |           | PC9  | MCO2 | -      | TIM3_<br>CH4 | TIM8_<br>CH4     | I2C3_<br>SDA | I2S_<br>CKIN              | -                         | -                       | -                          | -                              | -                       | -    | SDIO_D1              | DCMI_<br>D3  | -      | EVEN<br>TOUT |

|                    |           | PC10 | -    | -      | -            | -                | -            | -                         | SPI3_<br>SCK/I2S<br>3_CK  | USART3_<br>TX           | UART4_TX                   | -                              | -                       | -    | SDIO_D2              | DCMI_<br>D8  | LCD_R2 | EVEN<br>TOUT |

|                    | Port      | PC11 | -    | -      | -            | -                | -            | I2S3ext<br>_SD            | SPI3_<br>MISO             | USART3_<br>RX           | UART4_RX                   | -                              | -                       | -    | SDIO_D3              | DCMI_<br>D4  | -      | EVEN<br>TOUT |

| D                  | Port<br>C | PC12 | -    | -      | -            | -                | -            | -                         | SPI3_<br>MOSI/I2<br>S3_SD | USART3_<br>CK           | UART5_TX                   | -                              | -                       | -    | SDIO_CK              | DCMI_<br>D9  | -      | EVEN<br>TOUT |

| ocID0              |           | PC13 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

| 2424               |           | PC14 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

| DocID024244 Rev 10 |           | PC15 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

| 10                 |           | PD0  | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | CAN1_RX                        | -                       | -    | FMC_D2               | -            | -      | EVEN<br>TOUT |

|                    |           | PD1  | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | CAN1_TX                        | -                       | -    | FMC_D3               | -            | -      | EVEN<br>TOUT |

|                    |           | PD2  | -    | -      | TIM3_<br>ETR | -                | -            | -                         | -                         | -                       | UART5_RX                   | -                              | -                       | -    | SDIO_<br>CMD         | DCMI_<br>D11 | -      | EVEN<br>TOUT |

|                    | Port<br>D | PD3  | -    | -      | -            | -                | -            | SPI2_S<br>CK/I<br>2S2_CK  | -                         | USART2_<br>CTS          | -                          | -                              | -                       | -    | FMC_CLK              | DCMI_<br>D5  | LCD_G7 | EVEN<br>TOUT |

|                    |           | PD4  | -    | -      | -            | -                | -            | -                         | -                         | USART2_<br>RTS          | -                          | -                              | -                       | -    | FMC_NOE              | -            | -      | EVEN<br>TOUT |

|                    |           | PD5  | -    | -      | -            | -                | -            | -                         | -                         | USART2_<br>TX           | -                          | -                              | -                       | -    | FMC_NWE              | -            | -      | EVEN<br>TOUT |

|                    |           | PD6  | -    | -      | -            | -                | -            | SPI3_<br>MOSI/I2<br>S3_SD | SAI1_<br>SD_A             | USART2_<br>RX           | -                          | -                              | -                       | -    | FMC_<br>NWAIT        | DCMI_<br>D10 | LCD_B2 | EVEN<br>TOUT |

Pinouts and pin description

STM32F437xx and STM32F439xx

DocID024244 Rev 10

80/240

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

|           |      | AF0 | AF1    | AF2      | AF3              | AF4          | AF5                | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11            | AF12                 | AF13         | AF14        | AF15         |

|-----------|------|-----|--------|----------|------------------|--------------|--------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|-----------------|----------------------|--------------|-------------|--------------|

| P         | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11 | l2C1/<br>2/3 | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН             | FMC/SDIO<br>/OTG2_FS | DCMI         | LCD         | sys          |

|           | PF8  | -   | -      | -        | -                | -            | SPI5_<br>MISO      | SAI1_<br>SCK_B  | -                       | -                          | TIM13_CH1                      | -                       | -               | FMC_<br>NIOWR        | -            | -           | EVEN<br>TOUT |

|           | PF9  | -   | -      | -        | -                | -            | SPI5_<br>MOSI      | SAI1_<br>FS_B   | -                       | -                          | TIM14_CH1                      | -                       | -               | FMC_CD               | -            | -           | EVEN<br>TOUT |

|           | PF10 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_INTR             | DCMI_<br>D11 | LCD_DE      | EVEN<br>TOU  |

| Port F    | PF11 | -   | -      | -        | -                | -            | SPI5_<br>MOSI      | -               | -                       | -                          | -                              | -                       | -               | FMC_<br>SDNRAS       | DCMI_<br>D12 | -           | EVEN<br>TOU  |

| PORF      | PF12 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A6               | -            | -           | EVEI<br>TOU  |

|           | PF13 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A7               | -            | -           | EVEI<br>TOU  |

|           | PF14 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A8               | -            | -           | EVE<br>TOU   |

|           | PF15 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A9               | -            | -           | EVE<br>TOU   |

|           | PG0  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A10              | -            | -           | EVEI<br>TOU  |

|           | PG1  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A11              | -            | -           | EVE<br>TOU   |

|           | PG2  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A12              | -            | -           | EVE<br>TOU   |

|           | PG3  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A13              | -            | -           | EVE<br>TOU   |

| Port<br>G | PG4  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A14/<br>FMC_BA0  | -            | -           | EVE<br>TOU   |

|           | PG5  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A15/<br>FMC_BA1  | -            | -           | EVEI<br>TOU  |

|           | PG6  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_INT2             | DCMI_<br>D12 | LCD_R7      | EVE<br>TOU   |

|           | PG7  | -   | -      | -        | -                | -            | -                  | -               | -                       | USART6_<br>CK              | -                              | -                       | -               | FMC_INT3             | DCMI_<br>D13 | LCD_<br>CLK | EVE<br>TOU   |

|           | PG8  | -   | -      | -        | -                | -            | SPI6_<br>NSS       | -               | -                       | USART6_<br>RTS             | -                              | -                       | ETH_PPS<br>_OUT | FMC_SDC<br>LK        | -            | -           | EVE<br>TOU   |

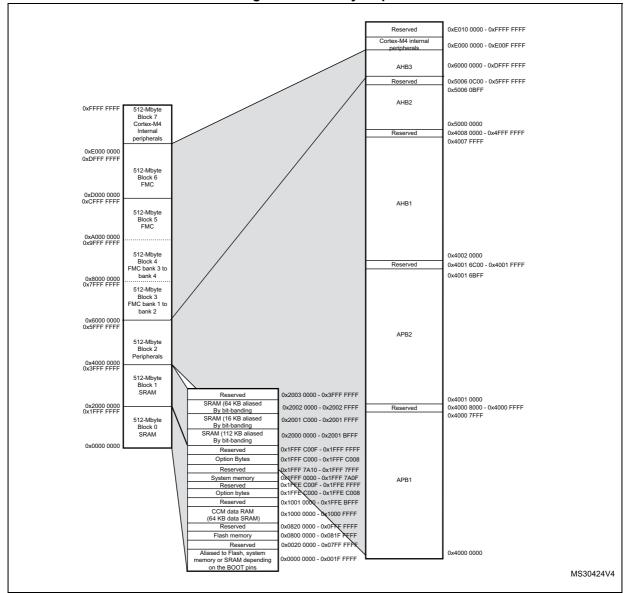

# 5 Memory mapping

The memory map is shown in *Figure 19*.

Figure 19. Memory map

DocID024244 Rev 10

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 8000- 0x4000 FFFF  | Reserved            |

|      | 0x4000 7C00 - 0x4000 7FFF | UART8               |

|      | 0x4000 7800 - 0x4000 7BFF | UART7               |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | Reserved            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | I2C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | Reserved            |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 13. STM32F437xx and STM32F439xx register boundary addresses (continued)

| Symbol          | Parameter                                                          | Conditions <sup>(1)</sup>            | Min   | Тур | Мах                       | Unit |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------|--------------------------------------|-------|-----|---------------------------|------|--|--|--|--|--|

|                 | Input voltage on RST and FT                                        | 2 V ≤V <sub>DD</sub> ≤3.6 V          | - 0.3 | -   | 5.5                       |      |  |  |  |  |  |

|                 | pins <sup>(7)</sup>                                                | V <sub>DD</sub> ≤2 V                 | - 0.3 | -   | 5.2                       |      |  |  |  |  |  |

| V <sub>IN</sub> | Input voltage on TTa pins                                          |                                      | - 0.3 | -   | V <sub>DDA</sub> +<br>0.3 | V    |  |  |  |  |  |

|                 | Input voltage on BOOT0 pin                                         |                                      | 0     | -   | 9                         |      |  |  |  |  |  |

|                 |                                                                    | LQFP100                              | -     | -   | 465                       |      |  |  |  |  |  |

|                 |                                                                    | WLCSP143                             | -     | -   | 641                       |      |  |  |  |  |  |

|                 |                                                                    | LQFP144                              | -     | -   | 500                       |      |  |  |  |  |  |

| -               | Power dissipation at $T_A = 85 \degree C$                          | UFBGA169                             | -     | -   | 385                       | mW   |  |  |  |  |  |

| $P_D$           | for suffix 6 or $T_A = 105 \text{ °C}$ for suffix 7 <sup>(8)</sup> | LQFP176                              | -     | -   | 526                       |      |  |  |  |  |  |

|                 |                                                                    | UFBGA176                             | -     | -   | 513                       | 1    |  |  |  |  |  |

|                 |                                                                    | LQFP208                              | -     | -   | 1053                      |      |  |  |  |  |  |

|                 |                                                                    | TFBGA216                             | -     | -   |                           |      |  |  |  |  |  |

|                 | Ambient temperature for 6 suffix                                   | Maximum power dissipation            | - 40  |     | 85                        | °C   |  |  |  |  |  |

| т.              | version                                                            | Low power dissipation <sup>(9)</sup> | - 40  |     | 105                       |      |  |  |  |  |  |

| ΤΑ              | Ambient temperature for 7 suffix                                   | Maximum power dissipation            | - 40  |     | 105                       | °C   |  |  |  |  |  |

|                 | version                                                            | Low power dissipation <sup>(9)</sup> | - 40  |     | 125                       | C    |  |  |  |  |  |

| ТJ              | lunction tomporature range                                         | 6 suffix version                     | - 40  |     | 105                       | °C   |  |  |  |  |  |

| IJ              | Junction temperature range                                         | 7 suffix version                     | - 40  |     | 125                       |      |  |  |  |  |  |

Table 17. General operating conditions (continued)

1. The over-drive mode is not supported at the voltage ranges from 1.7 to 2.1 V.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

3. When the ADC is used, refer to *Table 74: ADC characteristics*.

4. If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF+} < 1.2$  V.

5. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

- 6. The over-drive mode is not supported when the internal regulator is OFF.

- 7. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

8. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

9. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

|                      |                                      |                                                               |                            | Тур <sup>(1)</sup>         |                            |                           |                           |                            |      |

|----------------------|--------------------------------------|---------------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                            | Conditions                                                    | т                          | A = 25 °(                  | C                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      |                                      |                                                               | V <sub>DD</sub> =<br>1.7 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | v                         |                           |                            |      |

|                      | Supply current<br>in Standby<br>mode | Backup SRAM ON, low-speed oscillator (LSE) and RTC ON         | 2.80                       | 3.00                       | 3.60                       | 7.00                      | 19.00                     | 36.00                      |      |

| I <sub>DD_STBY</sub> |                                      | Backup SRAM OFF, low-<br>speed oscillator (LSE) and<br>RTC ON | 2.30                       | 2.60                       | 3.10                       | 6.00                      | 16.00                     | 31.00                      | μA   |

| _                    |                                      | Backup SRAM ON, RTC and LSE OFF                               | 2.30                       | 2.50                       | 2.90                       | 6.00 <sup>(3)</sup>       | 18.00 <sup>(3)</sup>      | 35.00 <sup>(3)</sup>       |      |

|                      |                                      | Backup SRAM OFF, RTC and LSE OFF                              | 1.70                       | 1.90                       | 2.20                       | 5.00 <sup>(3)</sup>       | 15.00 <sup>(3)</sup>      | 30.00 <sup>(3)</sup>       |      |

## Table 28. Typical and maximum current consumptions in Standby mode

The typical current consumption values are given with PDR OFF (internal reset OFF). When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2 μA.

2. Based on characterization, not tested in production unless otherwise specified.

3. Based on characterization, tested in production.

## Table 29. Typical and maximum current consumptions in $\ensuremath{\mathsf{V}_{\mathsf{BAT}}}$ mode

|                      |                                    |                                                        | Тур                         |                                                   |                             | Max <sup>(2)</sup> |         | Unit |

|----------------------|------------------------------------|--------------------------------------------------------|-----------------------------|---------------------------------------------------|-----------------------------|--------------------|---------|------|

| Symbol               | Parameter                          | V <sub>BAT</sub> = V <sub>BAT</sub> = V <sub>BAT</sub> | С                           | T <sub>A</sub> = 85 °C<br>T <sub>A</sub> = 105 °C |                             |                    |         |      |

|                      |                                    |                                                        | V <sub>BAT</sub> =<br>1.7 V |                                                   | V <sub>BAT</sub> =<br>3.3 V | V <sub>BAT</sub> = | = 3.6 V |      |

| I <sub>DD_VBAT</sub> | Backup<br>domain supply<br>current | Backup SRAM ON, low-speed oscillator (LSE) and RTC ON  | 1.28                        | 1.40                                              | 1.62                        | 6                  | 11      |      |

|                      |                                    | Backup SRAM OFF, low-speed oscillator (LSE) and RTC ON | 0.66                        | 0.76                                              | 0.97                        | 3                  | 5       | μA   |

|                      |                                    | Backup SRAM ON, RIC and                                | 0.70                        | 0.72                                              | 0.74                        | 5                  | 10      | μΛ   |

|                      |                                    | Backup SRAM OFF, RTC and LSE OFF                       | 0.10                        | 0.10                                              | 0.10                        | 2                  | 4       |      |

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a  $\rm C_L$  of 6 pF for typical values.

2. Guaranteed by characterization results.

| Symbol                             | Deremeter                                                      | Conditions                  | 6 (MII-)                | VDD=3.3 V         |                 | VDD=1.7 V         |                 | Unit |

|------------------------------------|----------------------------------------------------------------|-----------------------------|-------------------------|-------------------|-----------------|-------------------|-----------------|------|

| Cymbol                             | Parameter                                                      | Conditions                  | f <sub>HCLK</sub> (MHz) | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub> | I <sub>DD</sub> |      |

|                                    |                                                                |                             | 180                     | 61.5              | 1.4             | -                 | -               |      |

|                                    |                                                                |                             | 168                     | 59.4              | 1.3             | 59.4              | 1.0             |      |

|                                    |                                                                |                             | 150                     | 53.9              | 1.3             | 53.9              | 1.0             |      |

|                                    |                                                                |                             | 144                     | 49.0              | 1.3             | 49.0              | 1.0             |      |

|                                    |                                                                | All Peripherals<br>enabled  | 120                     | 38.0              | 1.2             | 38.0              | 0.9             |      |

|                                    | Supply current in Sleep mode from $V_{12}$ and $V_{DD}$ supply |                             | 90                      | 29.3              | 1.4             | 29.3              | 1.1             |      |

|                                    |                                                                |                             | 60                      | 20.2              | 1.2             | 20.2              | 0.9             |      |

|                                    |                                                                |                             | 30                      | 11.9              | 1.2             | 11.9              | 0.9             |      |

| 1 /1                               |                                                                |                             | 25                      | 10.4              | 1.2             | 10.4              | 0.9             |      |

| I <sub>DD12</sub> /I <sub>DD</sub> |                                                                | All Peripherals<br>disabled | 180                     | 14.9              | 1.4             | -                 | -               | mA   |

|                                    |                                                                |                             | 168                     | 14.0              | 1.3             | 14.0              | 1.0             | -    |

|                                    |                                                                |                             | 150                     | 12.6              | 1.3             | 12.6              | 1.0             |      |

|                                    |                                                                |                             | 144                     | 11.5              | 1.3             | 11.5              | 1.0             | -    |

|                                    |                                                                |                             | 120                     | 8.7               | 1.2             | 8.7               | 0.9             |      |

|                                    |                                                                | aloubiou                    | 90                      | 7.1               | 1.4             | 7.1               | 1.1             |      |

|                                    |                                                                |                             | 60                      | 5.0               | 1.2             | 5.0               | 0.9             |      |

|                                    |                                                                |                             | 30                      | 3.1               | 1.2             | 3.1               | 0.9             |      |

|                                    |                                                                |                             | 25                      | 2.8               | 1.2             | 2.8               | 0.9             |      |

| Table 33. Tyical current consumption in Sleep mode, regulator OFF <sup>(1)</sup> |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

| Symbol           | Parameter         | Conditions                                                                              | Value              | Unit    |

|------------------|-------------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Farameter         | Conditions                                                                              | Min <sup>(1)</sup> | Onit    |

| N <sub>END</sub> | Endurance         | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

| t <sub>RET</sub> |                   | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

|                  | ET Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                   | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

Table 50. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

## 6.3.14 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                         | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2                                            | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP176}, \text{T}_{\text{A}} = +25 \text{ °C}, \text{f}_{\text{HCLK}} = 168 \text{ MHz}, \text{ conforms to} \text{IEC 61000-4-2}$ | 4A              |

Table 51. EMS characteristics

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, PH2, PH3, PH4, PH5, PA3, PA4, PA5, PA6, PA7, PC4, and PC5.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

DocID024244 Rev 10

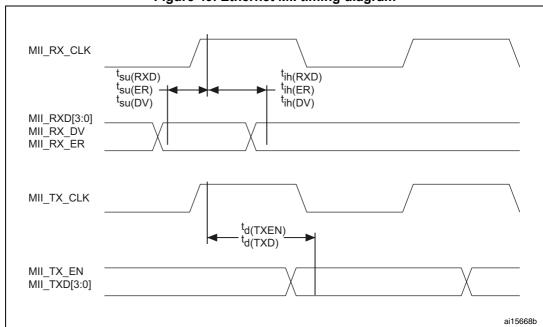

Figure 49. Ethernet MII timing diagram

| Table 73. Dynamics characteristics: Ethernet MAC signals for MII <sup>(1)</sup> |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Symbol               | Parameter                        | Condition                        | Min                              | Тур | Max | Unit |

|----------------------|----------------------------------|----------------------------------|----------------------------------|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          |                                  | 9                                | -   | -   |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           |                                  | 10                               | -   | -   |      |

| t <sub>su(DV)</sub>  | Data valid setup time            | 1.71 V < V <sub>DD</sub> < 3.6 V | 9                                | -   | -   |      |

| t <sub>ih(DV)</sub>  | Data valid hold time             |                                  | 8                                | -   | -   |      |

| t <sub>su(ER)</sub>  | Error setup time                 |                                  | 6                                | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  |                                  | 8                                | -   | -   | 115  |

| +                    | Transmit anable valid delay time | 2.7 V < V <sub>DD</sub> < 3.6 V  | .7 V < V <sub>DD</sub> < 3.6 V 8 | 10  | 14  |      |

| <sup>t</sup> d(TXEN) | Transmit enable valid delay time | 1.71 V < V <sub>DD</sub> < 3.6 V | 8                                | 10  | 16  |      |

| 4                    | Transmit data valid delay time   | 2.7 V < V <sub>DD</sub> < 3.6 V  | 7.5                              | 10  | 15  |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 1.71 V < V <sub>DD</sub> < 3.6 V | 7.5                              | 10  | 17  |      |

1. Guaranteed by characterization results.

## CAN (controller area network) interface

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (CANx\_TX and CANx\_RX).

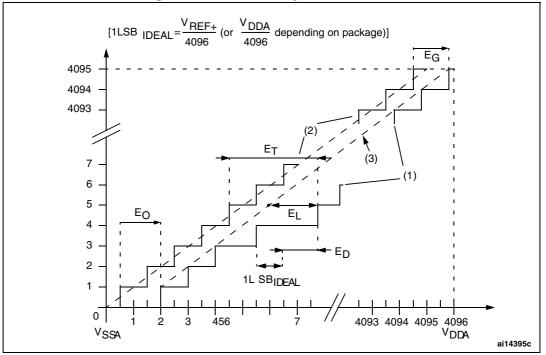

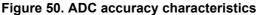

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.17 does not affect the ADC accuracy.

- 1. See also Table 76.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4. End point correlation line.

- E<sub>T</sub> = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

## 6.3.26 FMC characteristics

Unless otherwise specified, the parameters given in *Table 86* to *Table 101* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10 except at V<sub>DD</sub> range 1.7 to 2.1V where OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

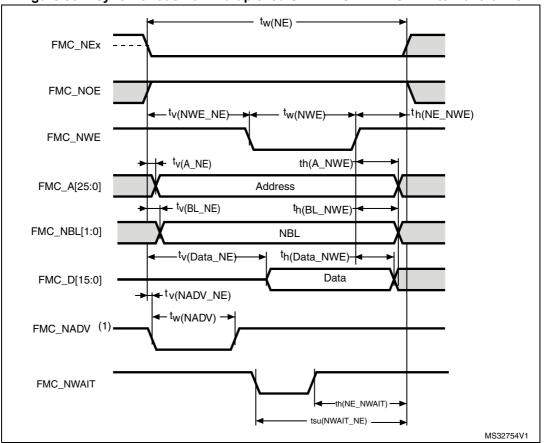

## Asynchronous waveforms and timings

*Figure 55* through *Figure 58* represent asynchronous waveforms and *Table 86* through *Table 93* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode , DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

- For SDRAM memories, V<sub>DD</sub> ranges from 2.7 to 3.6 V and maximum frequency FMC\_SDCLK = 90 MHz

- For Mobile LPSDR SDRAM memories, V<sub>DD</sub> ranges from 1.7 to 1.95 V and maximum frequency FMC\_SDCLK = 84 MHz

Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

| Table 88. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings <sup>(1)(2)</sup> |

|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|

| Symbol                   | Parameter                             | Min                     | Max                     | Unit |

|--------------------------|---------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FMC_NE low time                       | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> +1   | ns   |

| $t_{v(NWE_NE)}$          | FMC_NEx low to FMC_NWE low            | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                      | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> +1.5  | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid            | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid           | -                       | 1.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid     | -                       | T <sub>HCLK</sub> + 2   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low           | -                       | 0.5                     | ns   |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                     | -                       | T <sub>HCLK</sub> + 0.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

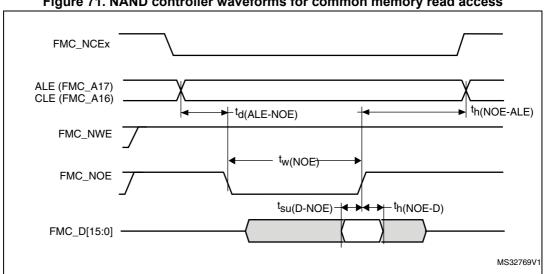

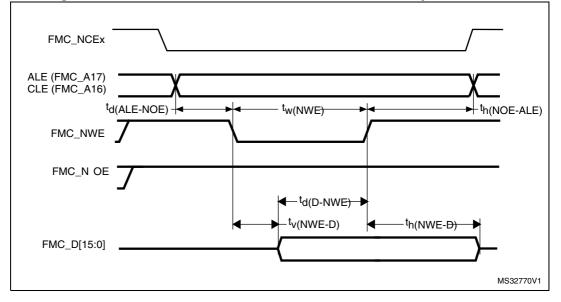

Figure 71. NAND controller waveforms for common memory read access

Figure 72. NAND controller waveforms for common memory write access

Table 100. Switching characteristics for NAND Flash read cycles<sup>(1)</sup>

| Symbol                  | Parameter                                  | Min                      | Мах                      | Unit |

|-------------------------|--------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> – 0.5 | 4T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 9                        | -                        | ns   |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 0                        | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                        | 3T <sub>HCLK</sub> – 0.5 | ns   |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> – 2   | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

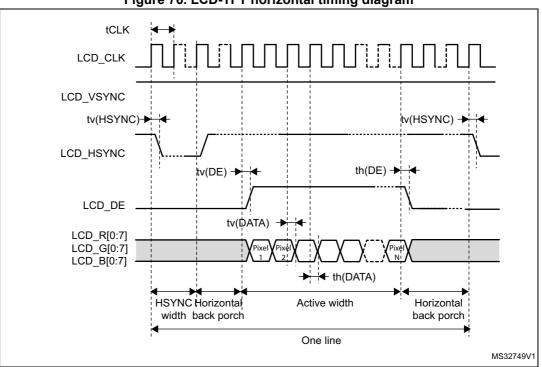

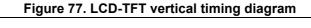

Figure 76. LCD-TFT horizontal timing diagram

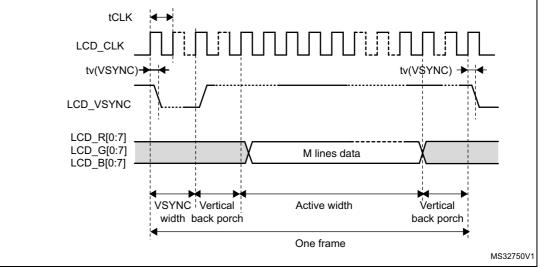

#### **Device marking for LQFP144**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

### Figure 88. LQFP144 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.