Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 140                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | ·                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 201-UFBGA                                                                           |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f439iih6tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode: MR operates in normal mode (default mode of MR in stop mode) MR operates in under-drive mode (reduced leakage mode).

LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to Table 3 for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 22: Power supply scheme* and *Table 19: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. - means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

### 3.18.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 17: General operating conditions*. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 22: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

|         |         |          | Pin nu   | ımbeı   |          |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 35      | 46      | N4       | R5       | 56      | N8       | 61      | R5       | PB0                                                  | I/O      | FT              | (5)   | TIM1_CH2N,<br>TIM3_CH3,<br>TIM8_CH2N, LCD_R3,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>EVENTOUT | ADC12_<br>IN8           |

| 36      | 47      | K5       | R4       | 57      | K7       | 62      | R4       | PB1                                                  | I/O      | FT              | (5)   | TIM1_CH3N,<br>TIM3_CH4,<br>TIM8_CH3N, LCD_R6,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>EVENTOUT | ADC12_<br>IN9           |

| 37      | 48      | L5       | M6       | 58      | L7       | 63      | M5       | PB2-BOOT1<br>(PB2)                                   | I/O      | FT              | -     | EVENTOUT                                                                                      | -                       |

| -       | -       | -        | -        | -       | -        | 64      | G4       | PI15                                                 | I/O      | FT              | -     | LCD_R0, EVENTOUT                                                                              | -                       |

| -       | -       | -        | -        | -       | -        | 65      | R6       | PJ0                                                  | I/O      | FT              | -     | LCD_R1, EVENTOUT                                                                              | -                       |

| -       | -       | -        | -        | -       | -        | 66      | R7       | PJ1                                                  | I/O      | FT              | -     | LCD_R2, EVENTOUT                                                                              | -                       |

| -       | -       | -        | -        | -       | -        | 67      | P7       | PJ2                                                  | I/O      | FT              | -     | LCD_R3, EVENTOUT                                                                              | -                       |

| -       | -       | -        | -        | -       | -        | 68      | N8       | PJ3                                                  | I/O      | FT              | -     | LCD_R4, EVENTOUT                                                                              | -                       |

| -       | -       | -        | -        | -       | -        | 69      | M9       | PJ4                                                  | I/O      | FT              | -     | LCD_R5, EVENTOUT                                                                              | -                       |

| -       | 49      | M5       | R6       | 59      | M7       | 70      | P8       | PF11                                                 | I/O      | FT              | -     | SPI5_MOSI,<br>FMC_SDNRAS,<br>DCMI_D12,<br>EVENTOUT                                            | -                       |

| -       | 50      | N5       | P6       | 60      | N7       | 71      | M6       | PF12                                                 | I/O      | FT              | -     | FMC_A6, EVENTOUT                                                                              | -                       |

| -       | 51      | G9       | M8       | 61      | -        | 72      | K7       | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 52      | D10      | N8       | 62      | -        | 73      | L8       | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 53      | M6       | N6       | 63      | K6       | 74      | N6       | PF13                                                 | I/O      | FT              | -     | FMC_A7, EVENTOUT                                                                              | -                       |

| -       | 54      | K7       | R7       | 64      | L6       | 75      | P6       | PF14                                                 | I/O      | FT              | -     | FMC_A8, EVENTOUT                                                                              | -                       |

| -       | 55      | L7       | P7       | 65      | M6       | 76      | M8       | PF15                                                 | I/O      | FT              | -     | FMC_A9, EVENTOUT                                                                              | -                       |

| -       | 56      | N6       | N7       | 66      | N6       | 77      | N7       | PG0                                                  | I/O      | FT              | -     | FMC_A10, EVENTOUT                                                                             | -                       |

| -       | 57      | M7       | M7       | 67      | K5       | 78      | M7       | PG1                                                  | I/O      | FT              | -     | FMC_A11, EVENTOUT                                                                             | -                       |

| Table 10. | STM32F437xx and | STM32F439xx pin | and ball definitions | (continued) |

|-----------|-----------------|-----------------|----------------------|-------------|

|           |                 |                 |                      |             |

|         |         |          | Pin nu   | ımbeı   | -        |         |          |                                                      |          |                 |       |                                                                                                                                                         |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                                                                     | Additional<br>functions |

| 51      | 73      | N12      | P12      | 92      | M2       | 104     | L13      | PB12                                                 | I/O      | FT              | _     | TIM1_BKIN,<br>I2C2_SMBA,<br>SPI2_NSS/I2S2_WS,<br>USART3_CK,<br>CAN2_RX,<br>OTG_HS_ULPI_D5,<br>ETH_MII_TXD0/ETH_R<br>MII_TXD0,<br>OTG_HS_ID,<br>EVENTOUT | -                       |

| 52      | 74      | M12      | P13      | 93      | N1       | 105     | K14      | PB13                                                 | I/O      | FT              | -     | TIM1_CH1N,<br>SPI2_SCK/I2S2_CK,<br>USART3_CTS,<br>CAN2_TX,<br>OTG_HS_ULPI_D6,<br>ETH_MII_TXD1/ETH_R<br>MII_TXD1, EVENTOUT                               | OTG_HS_<br>VBUS         |

| 53      | 75      | M13      | R14      | 94      | K3       | 106     | R14      | PB14                                                 | I/O      | FT              | -     | TIM1_CH2N,<br>TIM8_CH2N,<br>SPI2_MISO,<br>I2S2ext_SD,<br>USART3_RTS,<br>TIM12_CH1,<br>OTG_HS_DM,<br>EVENTOUT                                            | -                       |

| 54      | 76      | L13      | R15      | 95      | J3       | 107     | R15      | PB15                                                 | I/O      | FT              | -     | RTC_REFIN,<br>TIM1_CH3N,<br>TIM8_CH3N,<br>SPI2_MOSI/I2S2_SD,<br>TIM12_CH2,<br>OTG_HS_DP,<br>EVENTOUT                                                    | -                       |

| 55      | 77      | L12      | P15      | 96      | L2       | 108     | L15      | PD8                                                  | I/O      | FT              | -     | USART3_TX,<br>FMC_D13, EVENTOUT                                                                                                                         | -                       |

| 56      | 78      | K13      | P14      | 97      | M1       | 109     | L14      | PD9                                                  | I/O      | FT              | -     | USART3_RX,<br>FMC_D14, EVENTOUT                                                                                                                         | -                       |

| 57      | 79      | K11      | N15      | 98      | H4       | 110     | K15      | PD10                                                 | I/O      | FT              | -     | USART3_CK,<br>FMC_D15, LCD_B3,<br>EVENTOUT                                                                                                              | -                       |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

5

# DocID024244 Rev 10

74/240

|        |      |      |                           | Та           | able 12.         | STM3          | 82F437             | xx and \$                | STM32F                  | 439xx alte                 | ernate fun                     | ction ma                | pping                                       |                      |                 |               |              |

|--------|------|------|---------------------------|--------------|------------------|---------------|--------------------|--------------------------|-------------------------|----------------------------|--------------------------------|-------------------------|---------------------------------------------|----------------------|-----------------|---------------|--------------|

|        |      | AF0  | AF1                       | AF2          | AF3              | AF4           | AF5                | AF6                      | AF7                     | AF8                        | AF9                            | AF10                    | AF11                                        | AF12                 | AF13            | AF14          | AF15         |

| Po     | ort  | SYS  | TIM1/2                    | TIM3/4/5     | TIM8/9/<br>10/11 | I2C1/<br>2/3  | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1          | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН                                         | FMC/SDIO<br>/OTG2_FS | DCMI            | LCD           | SYS          |

|        | PA0  | -    | TIM2_<br>CH1/TIM2<br>_ETR | TIM5_<br>CH1 | TIM8_<br>ETR     | -             | -                  | -                        | USART2_<br>CTS          | UART4_TX                   | -                              | -                       | ETH_MII_<br>CRS                             | -                    | -               | -             | EVEN<br>TOUT |

|        | PA1  | -    | TIM2_<br>CH2              | TIM5_<br>CH2 | -                | -             | -                  | -                        | USART2_<br>RTS          | UART4_RX                   | -                              | -                       | ETH_MII_<br>RX_CLK/E<br>TH_RMII_<br>REF_CLK | -                    | -               | -             | EVEN<br>TOUT |

|        | PA2  | -    | TIM2_<br>CH3              | TIM5_<br>CH3 | TIM9_<br>CH1     | -             | -                  | -                        | USART2_<br>TX           | -                          | -                              | -                       | ETH_<br>MDIO                                | -                    | -               | -             | EVEN<br>TOUT |

|        | PA3  | -    | TIM2_<br>CH4              | TIM5_<br>CH4 | TIM9_<br>CH2     | -             | -                  | -                        | USART2_<br>RX           | -                          | -                              | OTG_HS_<br>ULPI_D0      | ETH_MII_<br>COL                             | -                    | -               | LCD_B5        | EVEN<br>TOUT |

|        | PA4  | -    | -                         | -            | -                | -             | SPI1_<br>NSS       | SPI3_<br>NSS/<br>I2S3_WS | USART2_<br>CK           | -                          | -                              | -                       | -                                           | OTG_HS_<br>SOF       | DCMI_<br>HSYNC  | LCD_<br>VSYNC | EVEN<br>TOUT |

| Port A | PA5  | -    | TIM2_<br>CH1/TIM2<br>_ETR | -            | TIM8_<br>CH1N    | -             | SPI1_<br>SCK       | -                        | -                       | -                          | -                              | OTG_HS_<br>ULPI_CK      | -                                           | -                    | -               | -             | EVEN<br>TOUT |

| FUILA  | PA6  | -    | TIM1_<br>BKIN             | TIM3_<br>CH1 | TIM8_<br>BKIN    | -             | SPI1_<br>MISO      | -                        | -                       | -                          | TIM13_CH1                      | -                       | -                                           | -                    | DCMI_<br>PIXCLK | LCD_G2        | EVEN<br>TOUT |

|        | PA7  | -    | TIM1_<br>CH1N             | TIM3_<br>CH2 | TIM8_<br>CH1N    | -             | SPI1_<br>MOSI      | -                        | -                       | -                          | TIM14_CH1                      | -                       | ETH_MII_<br>RX_DV/<br>ETH_RMII<br>_CRS_DV   | -                    | -               | -             | EVEN<br>TOUT |

|        | PA8  | MCO1 | TIM1_<br>CH1              | -            | -                | I2C3_<br>SCL  | -                  | -                        | USART1_<br>CK           | -                          | -                              | OTG_FS_<br>SOF          | -                                           | -                    | -               | LCD_R6        | EVEN<br>TOUT |

|        | PA9  | -    | TIM1_<br>CH2              | -            | -                | I2C3_<br>SMBA | -                  | -                        | USART1_<br>TX           | -                          | -                              | -                       | -                                           | -                    | DCMI_<br>D0     | -             | EVEN<br>TOUT |

|        | PA10 | -    | TIM1_<br>CH3              | -            | -                | -             | -                  | -                        | USART1_<br>RX           | -                          | -                              | OTG_FS_<br>ID           | -                                           | -                    | DCMI_<br>D1     | -             | EVEN<br>TOUT |

|        | PA11 | -    | TIM1_<br>CH4              | -            | -                | -             | -                  | -                        | USART1_<br>CTS          | -                          | CAN1_RX                        | OTG_FS_<br>DM           | -                                           | -                    | -               | LCD_R4        | EVEN<br>TOUT |

|        | PA12 | -    | TIM1_<br>ETR              | -            | -                | -             | -                  | -                        | USART1_<br>RTS          | -                          | CAN1_TX                        | OTG_FS_<br>DP           | -                                           | -                    | -               | LCD_R5        | EVEN<br>TOUT |

STM32F437xx and STM32F439xx

Pinouts and pin description

DocID024244 Rev 10

80/240

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

|           |      | AF0 | AF1    | AF2      | AF3              | AF4          | AF5                | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11            | AF12                 | AF13         | AF14        | AF15         |

|-----------|------|-----|--------|----------|------------------|--------------|--------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|-----------------|----------------------|--------------|-------------|--------------|

| P         | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11 | l2C1/<br>2/3 | SPI1/2/<br>3/4/5/6 | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН             | FMC/SDIO<br>/OTG2_FS | DCMI         | LCD         | sys          |

|           | PF8  | -   | -      | -        | -                | -            | SPI5_<br>MISO      | SAI1_<br>SCK_B  | -                       | -                          | TIM13_CH1                      | -                       | -               | FMC_<br>NIOWR        | -            | -           | EVEN<br>TOUT |

|           | PF9  | -   | -      | -        | -                | -            | SPI5_<br>MOSI      | SAI1_<br>FS_B   | -                       | -                          | TIM14_CH1                      | -                       | -               | FMC_CD               | -            | -           | EVEN<br>TOUT |

|           | PF10 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_INTR             | DCMI_<br>D11 | LCD_DE      | EVEN<br>TOU  |

| Port F    | PF11 | -   | -      | -        | -                | -            | SPI5_<br>MOSI      | -               | -                       | -                          | -                              | -                       | -               | FMC_<br>SDNRAS       | DCMI_<br>D12 | -           | EVEN<br>TOU  |

| PORF      | PF12 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A6               | -            | -           | EVEI<br>TOU  |

|           | PF13 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A7               | -            | -           | EVEI<br>TOU  |

|           | PF14 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A8               | -            | -           | EVE<br>TOU   |

|           | PF15 | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A9               | -            | -           | EVE<br>TOU   |

|           | PG0  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A10              | -            | -           | EVEI<br>TOU  |

|           | PG1  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A11              | -            | -           | EVE<br>TOU   |

|           | PG2  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A12              | -            | -           | EVE<br>TOU   |

|           | PG3  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A13              | -            | -           | EVE<br>TOU   |

| Port<br>G | PG4  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A14/<br>FMC_BA0  | -            | -           | EVE<br>TOU   |

|           | PG5  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_A15/<br>FMC_BA1  | -            | -           | EVEI<br>TOU  |

|           | PG6  | -   | -      | -        | -                | -            | -                  | -               | -                       | -                          | -                              | -                       | -               | FMC_INT2             | DCMI_<br>D12 | LCD_R7      | EVE<br>TOU   |

|           | PG7  | -   | -      | -        | -                | -            | -                  | -               | -                       | USART6_<br>CK              | -                              | -                       | -               | FMC_INT3             | DCMI_<br>D13 | LCD_<br>CLK | EVE<br>TOU   |

|           | PG8  | -   | -      | -        | -                | -            | SPI6_<br>NSS       | -               | -                       | USART6_<br>RTS             | -                              | -                       | ETH_PPS<br>_OUT | FMC_SDC<br>LK        | -            | -           | EVE<br>TOU   |

#### 6.3.8 Wakeup time from low-power modes

The wakeup times given in *Table 36* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

| Symbol                              | Parameter                                   | Conditions                                                                              | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                  |

|-------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup> | Wakeup from Sleep                           | -                                                                                       | 6                  | -                  | CPU<br>clock<br>cycle |

|                                     |                                             | Main regulator is ON                                                                    | 13.6               | -                  | _                     |

| . (2)                               | Wakeup from Stop mode                       | Main regulator is ON and Flash memory in Deep power down mode                           | 93                 | 111                |                       |

| t <sub>WUSTOP</sub> <sup>(2)</sup>  | with MR/LP regulator in<br>normal mode      | Low power regulator is ON                                                               | 22                 | 32                 |                       |

|                                     |                                             | Low power regulator is ON and Flash memory in Deep power down mode                      | 103                | 126                | μs                    |

|                                     | Wakeup from Stop mode                       | Main regulator in under-drive mode<br>(Flash memory in Deep power-down<br>mode)         | 105                | 128                |                       |

| t <sub>WUSTOP</sub> <sup>(2)</sup>  | with MR/LP regulator in<br>Under-drive mode | Low power regulator in under-drive<br>mode<br>(Flash memory in Deep power-down<br>mode) | 125                | 155                |                       |

| tWUSTDBY<br>(2)(3)                  | Wakeup from Standby mode                    |                                                                                         | 318                | 412                |                       |

#### Table 36. Low-power mode wakeup timings

1. Guaranteed by characterization results.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first

3.  $t_{WUSTDBY}$  maximum value is given at -40 °C.

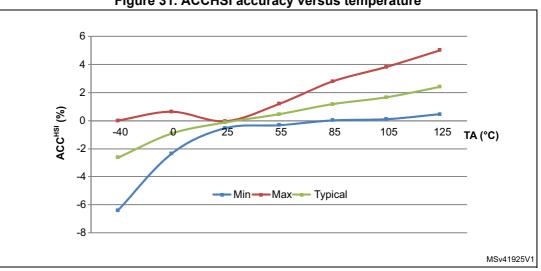

Figure 31. ACCHSI accuracy versus temperature

1. Guaranteed by characterization results.

#### Low-speed internal (LSI) RC oscillator

| Table 42. LSI | oscillator | characteristics <sup>(1)</sup> |

|---------------|------------|--------------------------------|

|---------------|------------|--------------------------------|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1. V\_{DD} = 3 V, T\_A = -40 to 105 °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

| Symbol                               | Parameter                                    | Condition                              | 5                  | Min          | Тур         | Мах          | Unit |

|--------------------------------------|----------------------------------------------|----------------------------------------|--------------------|--------------|-------------|--------------|------|

|                                      |                                              |                                        | RMS                | -            | 25          | -            |      |

|                                      | Cycle-to-cycle jitter                        | System clock                           | peak<br>to<br>peak | -            | ±150        | -            |      |

|                                      |                                              | 120 MHz                                | RMS                | -            | 15          | -            |      |

| Jitter <sup>(3)</sup>                | Period Jitter                                |                                        | peak<br>to<br>peak | -            | <u>+200</u> | -            | ps   |

|                                      | Main clock output (MCO) for<br>RMII Ethernet | Cycle to cycle at 5<br>on 1000 samples | -                  | 32           | -           |              |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet  | Cycle to cycle at 2 on 1000 samples    | -                  | 40           | -           |              |      |

|                                      | Bit Time CAN jitter                          | Cycle to cycle at 2<br>on 1000 samples | -                  | 330          | -           |              |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                 | VCO freq = 100 M                       | 1Hz                | 0.15         | _           | 0.40         | mA   |

| יטט(PLL)                             |                                              |                                        | 1Hz                | 0.45         | _           | 0.75         |      |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA                | VCO freq = 100 M<br>VCO freq = 432 M   |                    | 0.30<br>0.55 | -           | 0.40<br>0.85 | mA   |

#### Table 43. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results.

| Symbol                  | Parameter                         | Conditions                                                              |                    | Min                 | Тур  | Мах  | Unit |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> |                                                                         |                    | 0.95 <sup>(2)</sup> | 1    | 2.10 | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock    |                                                                         |                    | -                   | -    | 216  | MHz  |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 |                                                                         |                    | 100                 | -    | 432  | MHz  |

|                         | DLLIOC look time                  | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 75                  | -    | 200  |      |

| t <sub>LOCK</sub>       | PLLI2S lock time                  |                                                                         |                    | 100                 | -    | 300  | - μs |

| Jitter <sup>(3)</sup>   | Maataa 190 alaak iittaa           | Cycle to cycle at<br>12.288 MHz on<br>48KHz period,<br>N=432, R=5       | RMS                | -                   | 90   | -    |      |

|                         |                                   |                                                                         | peak<br>to<br>peak | -                   | ±280 | -    | ps   |

|                         | Master I2S clock jitter           | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples |                    | -                   | 90   | -    | ps   |

|                         | WS I2S clock jitter               | Cycle to cycle at 48 on 1000 samples                                    | KHz                | -                   | 400  | -    | ps   |

#### Table 44. PLLI2S (audio PLL) characteristics

| Symbol            | Parameter       | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------|---------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>BE</sub>   |                 | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 16  | 32                 |      |

|                   | Bank erase time | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 11  | 22                 | s    |

|                   |                 | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 8   | 16                 |      |

|                   |                 | 32-bit program operation                    | 2.7                | -   | 3.6                | V    |

| V <sub>prog</sub> |                 | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |

|                   |                 | 8-bit program operation                     | 1.7                | -   | 3.6                | V    |

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 100K erase operations.

| Table 49. Flash memory programming with V <sub>PP</sub> |                                                  |                                                    |                    |     |                    |      |  |  |  |

|---------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|--------------------|-----|--------------------|------|--|--|--|

| Symbol                                                  | Parameter                                        | Conditions                                         | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |  |  |  |

| t <sub>prog</sub>                                       | Double word programming                          |                                                    | -                  | 16  | 100 <sup>(2)</sup> | μs   |  |  |  |

| t <sub>ERASE16KB</sub>                                  | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C                       | -                  | 230 | -                  |      |  |  |  |

| t <sub>ERASE64KB</sub>                                  | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V<br>V <sub>PP</sub> = 8.5 V | -                  | 490 | -                  | ms   |  |  |  |

| t <sub>ERASE128KB</sub>                                 | Sector (128 KB) erase time                       |                                                    | -                  | 875 | -                  |      |  |  |  |

| t <sub>ME</sub>                                         | Mass erase time                                  |                                                    | -                  | 6.9 | -                  | s    |  |  |  |

| t <sub>BE</sub>                                         | Bank erase time                                  |                                                    | -                  | 6.9 | -                  | s    |  |  |  |

| V <sub>prog</sub>                                       | Programming voltage                              |                                                    | 2.7                | -   | 3.6                | V    |  |  |  |

| V <sub>PP</sub>                                         | V <sub>PP</sub> voltage range                    |                                                    | 7                  | -   | 9                  | V    |  |  |  |

| I <sub>PP</sub>                                         | Minimum current sunk on the $V_{\rm PP}$ pin     |                                                    | 10                 | -   | -                  | mA   |  |  |  |

| t <sub>VPP</sub> <sup>(3)</sup>                         | Cumulative time during which $V_{PP}$ is applied |                                                    | -                  | -   | 1                  | hour |  |  |  |

| Table 49. Flash memory | v programming | with $V_{PP}$ |

|------------------------|---------------|---------------|

|------------------------|---------------|---------------|

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol                         | Paran                                                 | neter                                                            | Conditions                        | Min | Тур | Мах | Unit |

|--------------------------------|-------------------------------------------------------|------------------------------------------------------------------|-----------------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup> | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID) | V <sub>IN</sub> = V <sub>SS</sub> | 30  | 40  | 50  |      |

|                                | resiston                                              | PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                           |                                   | 7   | 10  | 14  | kΩ   |

| R <sub>PD</sub>                | Weak pull-<br>down<br>equivalent                      | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID) | V <sub>IN</sub> = V <sub>DD</sub> | 30  | 40  | 50  | N22  |

|                                | resistor <sup>(7)</sup>                               | PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                           |                                   | 7   | 10  | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacita                                      | nce                                                              | -                                 | -   | 5   | -   | pF   |

Table 56. I/O static characteristics (continued)

1. Guaranteed by design.

2. Tested in production.

3. With a minimum of 200 mV.

4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 55: I/O current injection susceptibility

To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 55: I/O current injection susceptibility

6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 7. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT I/Os is shown in *Figure 35*.

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                | Conditions                                               | Min                                 | Max                | Unit |

|--------------------------------|------------------------------------------|----------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup>                                 | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = +8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V | V <sub>DD</sub> - 0.4               | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup>                                  | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> =+ 8mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V  | 2.4                                 | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +20 mA                                 | -                                   | 1.3 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 2.7 V ≤V <sub>DD</sub> ≤3.6 V                            | $V_{DD}$ - 1.3 <sup>(4)</sup>       | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +6 mA                                  | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.8 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA                                  | -                                   | 0.4 <sup>(5)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.7 V ≤V <sub>DD</sub> ≤3.6V                             | $V_{DD}$ -0.4 <sup>(5)</sup>        | -                  | v    |

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 15*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 15 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data.

5. Guaranteed by design.

#### **Electrical characteristics**

| Symbol               | Parameter                                                                             | Conditions | Min | Тур   | Max | Unit  | Comments                                                                                                                |

|----------------------|---------------------------------------------------------------------------------------|------------|-----|-------|-----|-------|-------------------------------------------------------------------------------------------------------------------------|

| eysoi                |                                                                                       | Conditione |     | .,,,, | max | ••••• |                                                                                                                         |

| twakeup <sup>(</sup> | Wakeup time from off<br>state (Setting the ENx<br>bit in the DAC Control<br>register) | -          | -   | 6.5   | 10  | μs    | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |

| PSRR+<br>(2)         | Power supply rejection<br>ratio (to V <sub>DDA</sub> ) (static<br>DC measurement)     | -          | -   | -67   | -40 | dB    | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |

#### Table 85. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization.

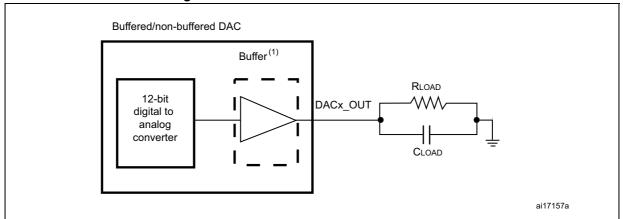

#### Figure 54. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

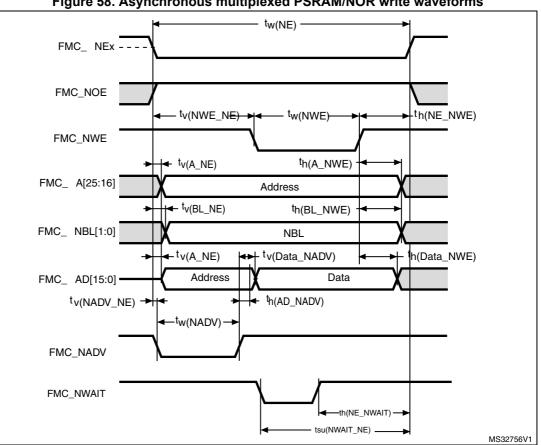

Figure 58. Asynchronous multiplexed PSRAM/NOR write waveforms

| Table 92. Asynchror | nous multiplexed PSRAM/NOR write timing | js <sup>(1)(2)</sup> |

|---------------------|-----------------------------------------|----------------------|

|---------------------|-----------------------------------------|----------------------|

| Symbol                    | Parameter                                           | Min                     | Мах                     | Unit |

|---------------------------|-----------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                     | 4T <sub>HCLK</sub>      | 4T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>v(NWE_NE)</sub>    | FMC_NEx low to FMC_NWE low                          | T <sub>HCLK</sub> – 1   | T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                    | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>h(NE_NWE)</sub>    | FMC_NWE high to FMC_NE high hold time               | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                          | -                       | 0                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                         | 0.5                     | 1                       | ns   |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                   | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(adress) valid hold time after FMC_NADV high) | T <sub>HCLK</sub> – 2   | -                       | ns   |

| t <sub>h(A_NWE)</sub>     | Address hold time after FMC_NWE high                | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NWE)</sub>    | FMC_BL hold time after FMC_NWE high                 | T <sub>HCLK</sub> – 2   | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                         | -                       | 2                       | ns   |

| t <sub>v(Data_NADV)</sub> | FMC_NADV high to Data valid                         | -                       | T <sub>HCLK</sub> +1.5  | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FMC_NWE high                   | T <sub>HCLK</sub> +0.5  | -                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

| Symbol                      | Parameter                                | Min                    | Max | Unit |

|-----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | 0                      | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                      | 0   | ns   |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                      | 2.5 | ns   |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | 0                      | -   | ns   |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 4                      |     |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 0                      |     |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

#### PC Card/CompactFlash controller waveforms and timings

*Figure 63* through *Figure 68* represent synchronous waveforms, and *Table 98* and *Table 99* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x04;

- COM.FMC\_WaitSetupTime = 0x07;

- COM.FMC\_HoldSetupTime = 0x04;

- COM.FMC\_HiZSetupTime = 0x00;

- ATT.FMC\_SetupTime = 0x04;

- ATT.FMC\_WaitSetupTime = 0x07;

- ATT.FMC\_HoldSetupTime = 0x04;

- ATT.FMC\_HiZSetupTime = 0x00;

- IO.FMC\_SetupTime = 0x04;

- IO.FMC\_WaitSetupTime = 0x07;

- IO.FMC\_HoldSetupTime = 0x04;

- IO.FMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period.

| Symbol                        | Parameter               | Min                      | Мах                     | Unit |

|-------------------------------|-------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period        | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time 2 |                          | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time    | 0                        | -                       |      |

| $t_{d(SDCLKL\_Add)}$          | Address valid time      | -                        | 1.5                     |      |

| t <sub>d(SDCLKL</sub> - SDNE) | Chip select valid time  | -                        | 0.5                     | ns   |

| $t_{h(SDCLKL\_SDNE)}$         | Chip select hold time   | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time       | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time        | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time       | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time        | 0                        | -                       |      |

# Table 102. SDRAM read timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

#### Table 103. LPSDR SDRAM read timings<sup>(1)(2)</sup>

| Symbol                        | Parameter                 | Min                      | Мах                     | Unit |

|-------------------------------|---------------------------|--------------------------|-------------------------|------|

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period          | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time     | 2.5                      | -                       |      |

| <sup>t</sup> h(SDCLKH_Data)   | Data input hold time 0    |                          | -                       |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time -      |                          | 1                       |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time    | -                        | 1                       | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time     | 1                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time         | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time          | 1                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS) SDNCAS valid time |                          | 1                       |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time          | 1 -                      |                         |      |

1. CL = 10 pF.

2. Guaranteed by characterization results.

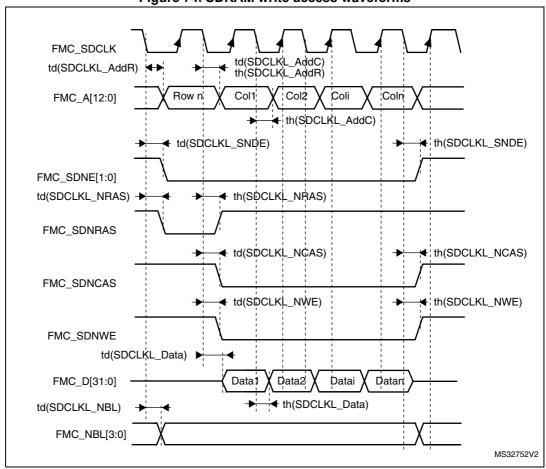

Figure 74. SDRAM write access waveforms

## 7.2 WLCSP143 package information

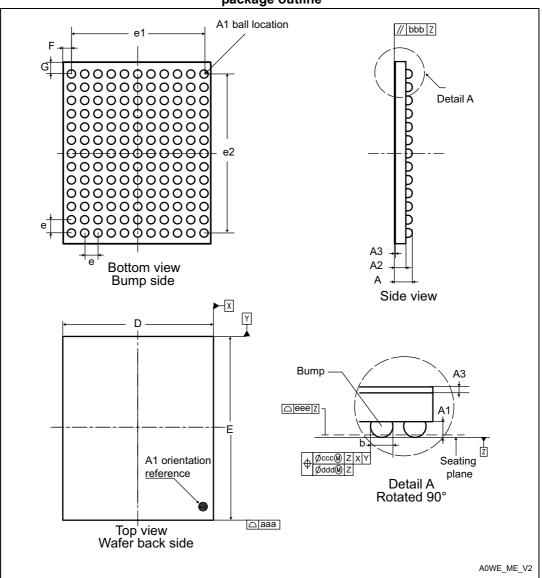

Figure 83. WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

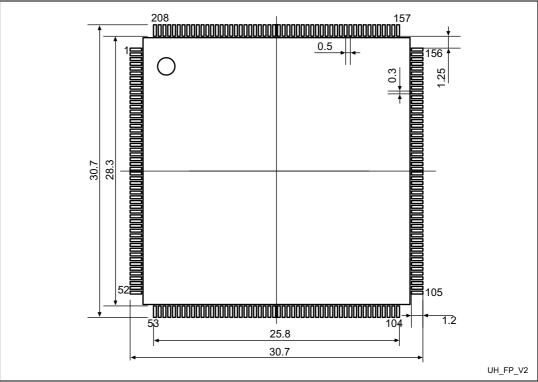

# Figure 93. LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

# Table 118. UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch,ultra fine pitch ball grid array package mechanical data (continued)

| Symbol | millimeters |      |       |      |      |        |

|--------|-------------|------|-------|------|------|--------|

| Symbol | Min.        | Тур. | Max.  | Min. | Тур. | Max.   |

| eee    | -           | -    | 0.150 | -    | -    | 0.0059 |

| fff    | -           | -    | 0.050 | -    | -    | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### Figure 99. UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package recommended footprint

| 000000000000000000000000000000000000    |            |

|-----------------------------------------|------------|

| 0000 0000                               |            |

| 000000000000000000000000000000000000000 |            |

| 000000000000000000000000000000000000000 | A0E7_FP_V1 |

#### Table 119. UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA) Image: Commended PCB design rules (0.65 mm pitch BGA) Image: Commended PCB design rules (0.65 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.65 mm                                                          |

| Dpad              | 0.300 mm                                                         |

| Dsm               | 0.400 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.300 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

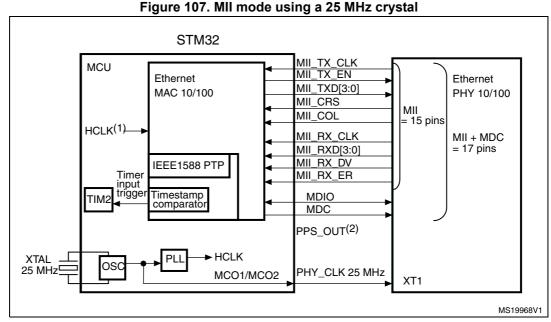

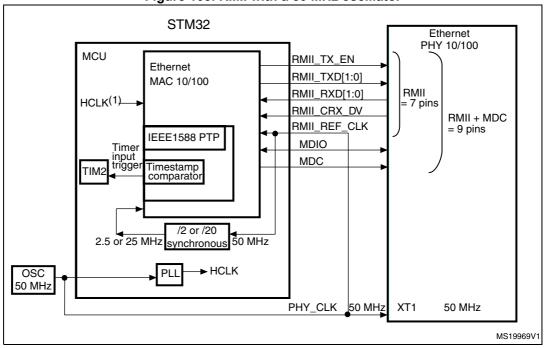

## **B.3** Ethernet interface solutions

1.  $f_{HCLK}$  must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

#### Figure 108. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.