# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details |

|---------|

|---------|

| 20000                      |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Active                                                                              |

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f439vgt6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.4 Embedded Flash memory

The devices embed a Flash memory of up to 2 Mbytes available for storing programs and data.

## 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.6 Embedded SRAM

All devices embed:

- Up to 256Kbytes of system SRAM including 64 Kbytes of CCM (core coupled memory) data RAM

- RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

- 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM, FMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 180 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 180 MHz while the maximum frequency of the high-speed APB domains is 90 MHz. The maximum allowed frequency of the low-speed APB domain is 45 MHz.

The devices embed a dedicated PLL (PLLI2S) and PLLSAI which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

## 3.15 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface. Refer to application note AN2606 for details.

## 3.16 Power supply schemes

- $V_{DD}$  = 1.7 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Note: V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

## 3.17 **Power supply supervisor**

### 3.17.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other package, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is

DocID024244 Rev 10

reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

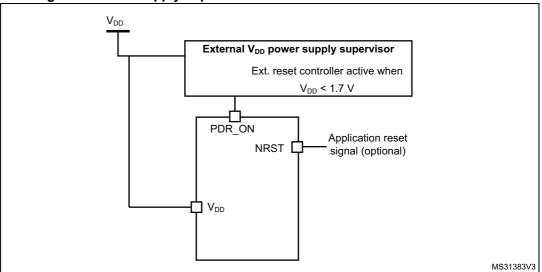

### 3.17.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to this external power supply supervisor. Refer to *Figure 6: Power supply supervisor interconnection with internal reset OFF*.

Figure 6. Power supply supervisor interconnection with internal reset OFF

The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.7 V (see *Figure 7*).

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry must be disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>.

All packages, except for the LQFP100, allow to disable the internal reset through the PDR\_ON signal.

|         |         |          | Pin nu   | ımbei   | r        |         |          |                                                      |          |                 |       |                                                                                           |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                       | Additional<br>functions |

| 49      | 71      | N9       | M10      | 81      | N2       | 92      | L11      | V <sub>CAP_1</sub>                                   | S        | -               | -     | -                                                                                         | -                       |

| -       | I       | -        | -        | -       | H2       | 93      | K9       | V <sub>SS</sub>                                      | S        | -               | 1     | -                                                                                         | -                       |

| 50      | 72      | F8       | N10      | 82      | J6       | 94      | L10      | V <sub>DD</sub>                                      | S        | -               | I     | -                                                                                         | -                       |

| -       | I       | -        | -        | -       | -        | 95      | M14      | PJ5                                                  | I/O      | -               | I     | LCD_R6, EVENTOUT                                                                          | -                       |

| -       | -       | N10      | M11      | 83      | -        | 96      | P13      | PH6                                                  | I/O      | FT              | -     | I2C2_SMBA,<br>SPI5_SCK,<br>TIM12_CH1,<br>ETH_MII_RXD2,<br>FMC_SDNE1,<br>DCMI_D8, EVENTOUT | -                       |

| -       | -       | M10      | N12      | 84      | -        | 97      | N13      | PH7                                                  | I/O      | FT              | -     | I2C3_SCL, SPI5_MISO,<br>ETH_MII_RXD3,<br>FMC_SDCKE1,<br>DCMI_D9, EVENTOUT                 | -                       |

| -       | -       | L10      | M12      | 85      | -        | 98      | P14      | PH8                                                  | I/O      | FT              | -     | I2C3_SDA, FMC_D16,<br>DCMI_HSYNC,<br>LCD_R2, EVENTOUT                                     | -                       |

| -       | -       | K10      | M13      | 86      | -        | 99      | N14      | PH9                                                  | I/O      | FT              | -     | I2C3_SMBA,<br>TIM12_CH2,<br>FMC_D17, DCMI_D0,<br>LCD_R3, EVENTOUT                         | -                       |

| -       | -       | N11      | L13      | 87      | -        | 100     | P15      | PH10                                                 | I/O      | FT              | -     | TIM5_CH1, FMC_D18,<br>DCMI_D1, LCD_R4,<br>EVENTOUT                                        | -                       |

| -       | -       | M11      | L12      | 88      | -        | 101     | N15      | PH11                                                 | I/O      | FT              | -     | TIM5_CH2, FMC_D19,<br>DCMI_D2, LCD_R5,<br>EVENTOUT                                        | -                       |

| -       | -       | L11      | K12      | 89      | -        | 102     | M15      | PH12                                                 | I/O      | FT              | -     | TIM5_CH3, FMC_D20,<br>DCMI_D3, LCD_R6,<br>EVENTOUT                                        | -                       |

| -       | I       | E7       | H12      | 90      | -        | -       | K10      | V <sub>SS</sub>                                      | s        | -               | -     | -                                                                                         | -                       |

| -       | -       | H8       | J12      | 91      | -        | 103     | K11      | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                         | -                       |

| Table 10. | STM32F437xx and | STM32F439xx pin | and ball definitions | (continued) |

|-----------|-----------------|-----------------|----------------------|-------------|

|           |                 |                 |                      |             |

| 7 |  |

|---|--|

| Q |  |

| Ñ |  |

| 4 |  |

| 0 |  |

DocID024244 Rev 10

57

|           |      |               |               |              |                  |               |                           |                 |                         |                            | lanotion                       |                         | ) (*******                               |                      |             |               |

|-----------|------|---------------|---------------|--------------|------------------|---------------|---------------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|------------------------------------------|----------------------|-------------|---------------|

|           |      | AF0           | AF1           | AF2          | AF3              | AF4           | AF5                       | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11                                     | AF12                 | AF13        | AF14          |

| Po        | ort  | SYS           | TIM1/2        | TIM3/4/5     | TIM8/9/<br>10/11 | l2C1/<br>2/3  | SPI1/2/<br>3/4/5/6        | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН                                      | FMC/SDIO<br>/OTG2_FS | DCMI        | LCD           |

|           | PB11 | -             | TIM2_<br>CH4  | -            | -                | I2C2_<br>SDA  | -                         | -               | USART3_<br>RX           | -                          | -                              | OTG_HS_<br>ULPI_D4      | ETH_MII_<br>TX_EN/<br>ETH_RMII<br>_TX_EN | -                    | -           | LCD_G5        |

|           | PB12 | -             | TIM1_<br>BKIN | -            | -                | I2C2_<br>SMBA | SPI2_<br>NSS/I2<br>S2_WS  | -               | USART3_<br>CK           | -                          | CAN2_RX                        | OTG_HS_<br>ULPI_D5      | ETH_MII_<br>TXD0/ETH<br>_RMII_<br>TXD0   | OTG_HS_<br>ID        | -           | -             |

| Port B    | PB13 | -             | TIM1_<br>CH1N | -            | -                | -             | SPI2_<br>SCK/I2<br>S2_CK  | -               | USART3_<br>CTS          | -                          | CAN2_TX                        | OTG_HS_<br>ULPI_D6      | ETH_MII_<br>TXD1/ETH<br>_RMII_TX<br>_D1  | -                    | -           | -             |

|           | PB14 | -             | TIM1_<br>CH2N | -            | TIM8_<br>CH2N    | -             | SPI2_<br>MISO             | I2S2ext_<br>SD  | USART3_<br>RTS          | -                          | TIM12_CH1                      | -                       | -                                        | OTG_HS_<br>DM        | -           | -             |

|           | PB15 | RTC_<br>REFIN | TIM1_<br>CH3N | -            | TIM8_<br>CH3N    | -             | SPI2_<br>MOSI/I2<br>S2_SD | -               | -                       | -                          | TIM12_CH2                      | -                       | -                                        | OTG_HS_<br>DP        | -           | -             |

|           | PC0  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | OTG_HS_<br>ULPI_STP     | -                                        | FMC_SDN<br>WE        | -           | -             |

|           | PC1  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | ETH_MDC                                  | -                    | -           | -             |

|           | PC2  | -             | -             | -            | -                | -             | SPI2_<br>MISO             | I2S2ext_<br>SD  | -                       | -                          | -                              | OTG_HS_<br>ULPI_DIR     | ETH_MII_<br>TXD2                         | FMC_<br>SDNE0        | -           | -             |

|           | PC3  | -             | -             | -            | -                | -             | SPI2_<br>MOSI/I2<br>S2_SD | -               | -                       | -                          | -                              | OTG_HS_<br>ULPI_NXT     | ETH_MII_<br>TX_CLK                       | FMC_<br>SDCKE0       | -           | -             |

| Port<br>C | PC4  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>RXD0/ETH<br>_RMII_<br>RXD0   | -                    | -           | -             |

|           | PC5  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>RXD1/ETH<br>_RMII_<br>RXD1   | -                    | -           | -             |

|           | PC6  | -             | -             | TIM3_<br>CH1 | TIM8_<br>CH1     | -             | I2S2_<br>MCK              | -               | -                       | USART6_<br>TX              | -                              | -                       | -                                        | SDIO_D6              | DCMI_<br>D0 | LCD_<br>HSYNC |

|           | PC7  | -             | -             | TIM3_<br>CH2 | TIM8_<br>CH2     | -             | -                         | I2S3_<br>MCK    | -                       | USART6_<br>RX              | -                              | -                       | -                                        | SDIO_D7              | DCMI_<br>D1 | LCD_G6        |

# Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

AF15

SYS

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT EVEN TOUT EVEN TOUT EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

77/240

Table 12. STM32F437xx and STM32F439xx alternate function mapping (continued)

| 77/240             |           |      | AF0  | AF1    | AF2          | AF3              | AF4          | AF5                       | AF6                       | AF7                     | AF8                        | AF9                            | AF10                    | AF11 | AF12                 | AF13         | AF14   | AF15         |

|--------------------|-----------|------|------|--------|--------------|------------------|--------------|---------------------------|---------------------------|-------------------------|----------------------------|--------------------------------|-------------------------|------|----------------------|--------------|--------|--------------|

| 0                  | P         | ort  | SYS  | TIM1/2 | TIM3/4/5     | TIM8/9/<br>10/11 | I2C1/<br>2/3 | SPI1/2/<br>3/4/5/6        | SPI2/3/<br>SAI1           | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН  | FMC/SDIO<br>/OTG2_FS | DCMI         | LCD    | SYS          |

|                    |           | PC8  | -    | -      | TIM3_<br>CH3 | TIM8_<br>CH3     | -            | -                         | -                         | -                       | USART6_<br>CK              | -                              | -                       | -    | SDIO_D0              | DCMI_<br>D2  | -      | EVEN<br>TOUT |

|                    |           | PC9  | MCO2 | -      | TIM3_<br>CH4 | TIM8_<br>CH4     | I2C3_<br>SDA | I2S_<br>CKIN              | -                         | -                       | -                          | -                              | -                       | -    | SDIO_D1              | DCMI_<br>D3  | -      | EVEN<br>TOUT |

|                    |           | PC10 | -    | -      | -            | -                | -            | -                         | SPI3_<br>SCK/I2S<br>3_CK  | USART3_<br>TX           | UART4_TX                   | -                              | -                       | -    | SDIO_D2              | DCMI_<br>D8  | LCD_R2 | EVEN<br>TOUT |

|                    | Port      | PC11 | -    | -      | -            | -                | -            | I2S3ext<br>_SD            | SPI3_<br>MISO             | USART3_<br>RX           | UART4_RX                   | -                              | -                       | -    | SDIO_D3              | DCMI_<br>D4  | -      | EVEN<br>TOUT |

| DocID024244 Rev 10 | Port<br>C | PC12 | -    | -      | -            | -                | -            | -                         | SPI3_<br>MOSI/I2<br>S3_SD | USART3_<br>CK           | UART5_TX                   | -                              | -                       | -    | SDIO_CK              | DCMI_<br>D9  | -      | EVEN<br>TOUT |

|                    |           | PC13 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

|                    |           | PC14 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

|                    |           | PC15 | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | -                              | -                       | -    | -                    | -            | -      | EVEN<br>TOUT |

|                    |           | PD0  | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | CAN1_RX                        | -                       | -    | FMC_D2               | -            | -      | EVEN<br>TOUT |

|                    |           | PD1  | -    | -      | -            | -                | -            | -                         | -                         | -                       | -                          | CAN1_TX                        | -                       | -    | FMC_D3               | -            | -      | EVEN<br>TOUT |

|                    |           | PD2  | -    | -      | TIM3_<br>ETR | -                | -            | -                         | -                         | -                       | UART5_RX                   | -                              | -                       | -    | SDIO_<br>CMD         | DCMI_<br>D11 | -      | EVEN<br>TOUT |

|                    | Port<br>D | PD3  | -    | -      | -            | -                | -            | SPI2_S<br>CK/I<br>2S2_CK  | -                         | USART2_<br>CTS          | -                          | -                              | -                       | -    | FMC_CLK              | DCMI_<br>D5  | LCD_G7 | EVEN<br>TOUT |

|                    |           | PD4  | -    | -      | -            | -                | -            | -                         | -                         | USART2_<br>RTS          | -                          | -                              | -                       | -    | FMC_NOE              | -            | -      | EVEN<br>TOUT |

|                    |           | PD5  | -    | -      | -            | -                | -            | -                         | -                         | USART2_<br>TX           | -                          | -                              | -                       | -    | FMC_NWE              | -            | -      | EVEN<br>TOUT |

|                    |           | PD6  | -    | -      | -            | -                | -            | SPI3_<br>MOSI/I2<br>S3_SD | SAI1_<br>SD_A             | USART2_<br>RX           | -                          | -                              | -                       | -    | FMC_<br>NWAIT        | DCMI_<br>D10 | LCD_B2 | EVEN<br>TOUT |

Pinouts and pin description

STM32F437xx and STM32F439xx

#### **Operating conditions** 6.3

#### 6.3.1 **General operating conditions**

| Table 17 | . General operating conditions |  |

|----------|--------------------------------|--|

|          |                                |  |

| Symbol                     | Parameter                                                                           | Conditions <sup>(1)</sup>                                                                                                    |                    | Min                | Тур  | Max  | Unit |

|----------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|------|------|

|                            |                                                                                     | Power Scale 3 (VOS[1:0] bits<br>PWR_CR register = 0x01), Re<br>ON, over-drive OFF                                            |                    | 0                  | -    | 120  |      |

|                            | Internal AHB clock frequency                                                        | Power Scale 2 (VOS[1:0] bits                                                                                                 | Over-<br>drive OFF | 0                  | -    | 144  |      |

| f <sub>HCLK</sub>          |                                                                                     | in PWR_CR register = 0x10),<br>Regulator ON                                                                                  | Over-<br>drive ON  | 0                  | -    | 168  |      |

|                            |                                                                                     | Power Scale 1 (VOS[1:0] bits<br>in PWR_CR register= 0x11),                                                                   | Over-<br>drive OFF | 0                  | -    | 168  | MHz  |

|                            |                                                                                     | Regulator ON                                                                                                                 | Over-<br>drive ON  | 0                  | -    | 180  |      |

| f                          | Internal ADD1 clock froquency                                                       | Over-drive OFF                                                                                                               |                    | 0                  | -    | 42   |      |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                                                       | Over-drive ON                                                                                                                |                    | 0                  | -    | 45   |      |

| f                          | Internal ADP2 clock frequency                                                       | Over-drive OFF                                                                                                               |                    | 0                  | -    | 84   |      |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                                                       | Over-drive ON                                                                                                                |                    | 0                  | -    | 90   |      |

| $V_{DD}$                   | Standard operating voltage                                                          |                                                                                                                              |                    | 1.7 <sup>(2)</sup> | -    | 3.6  |      |

| V <sub>DDA</sub><br>(3)(4) | Analog operating voltage<br>(ADC limited to 1.2 M samples)                          |                                                                                                                              | 1.7 <sup>(2)</sup> | -                  | 2.4  |      |      |

| (3)(4)                     | Analog operating voltage<br>(ADC limited to 2.4 M samples)                          | Must be the same potential as                                                                                                | 2.4                | -                  | 3.6  | v    |      |

| $V_{BAT}$                  | Backup operating voltage                                                            |                                                                                                                              |                    | 1.65               | -    | 3.6  |      |

|                            |                                                                                     | Power Scale 3 ((VOS[1:0] bits<br>PWR_CR register = 0x01), 12<br>HCLK max frequency                                           | 1.08               | 1.14               | 1.20 |      |      |

|                            | Regulator ON: 1.2 V internal voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins | Power Scale 2 ((VOS[1:0] bits<br>PWR_CR register = 0x10), 14<br>HCLK max frequency with ove<br>OFF or 168 MHz with over-driv | 1.20               | 1.26               | 1.32 | V    |      |

| V <sub>12</sub>            |                                                                                     | Power Scale 1 ((VOS[1:0] bits<br>PWR_CR register = 0x11), 16<br>HCLK max frequency with ove<br>OFF or 180 MHz with over-driv | 1.26               | 1.32               | 1.40 |      |      |

|                            | Regulator OFF: 1.2 V external                                                       | Max frequency 120 MHz                                                                                                        |                    | 1.10               | 1.14 | 1.20 |      |

|                            | voltage must be supplied from external regulator on                                 | Max frequency 144 MHz                                                                                                        |                    | 1.20               | 1.26 | 1.32 |      |

|                            | $V_{CAP_1}/V_{CAP_2} pins^{(6)}$                                                    | Max frequency 168 MHz                                                                                                        |                    | 1.26               | 1.32 | 1.38 | 1    |

| Symbol                             | Deremeter                                                                             | Conditions                  | £ (MU-)                 | VDD:              | =3.3 V          | VDD               | =1.7 V          | Unit |

|------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|-------------------------|-------------------|-----------------|-------------------|-----------------|------|

| Symbol                             | Parameter                                                                             | Conditions                  | f <sub>HCLK</sub> (MHz) | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub> | I <sub>DD</sub> |      |

|                                    |                                                                                       |                             | 180                     | 61.5              | 1.4             | -                 | -               |      |

|                                    |                                                                                       |                             | 168                     | 59.4              | 1.3             | 59.4              | 1.0             |      |

|                                    |                                                                                       |                             | 150                     | 53.9              | 1.3             | 53.9              | 1.0             |      |

|                                    |                                                                                       |                             | 144                     | 49.0              | 1.3             | 49.0              | 1.0             |      |

|                                    |                                                                                       | All Peripherals<br>enabled  | 120                     | 38.0              | 1.2             | 38.0              | 0.9             |      |

|                                    | Supply current<br>in Sleep mode<br>from V <sub>12</sub> and<br>V <sub>DD</sub> supply | enableu                     | 90                      | 29.3              | 1.4             | 29.3              | 1.1             |      |

|                                    |                                                                                       |                             | 60                      | 20.2              | 1.2             | 20.2              | 0.9             | - mA |

|                                    |                                                                                       |                             | 30                      | 11.9              | 1.2             | 11.9              | 0.9             |      |

| 1 /1                               |                                                                                       |                             | 25                      | 10.4              | 1.2             | 10.4              | 0.9             |      |

| I <sub>DD12</sub> /I <sub>DD</sub> |                                                                                       |                             | 180                     | 14.9              | 1.4             | -                 | -               |      |

|                                    |                                                                                       |                             | 168                     | 14.0              | 1.3             | 14.0              | 1.0             |      |

|                                    |                                                                                       |                             | 150                     | 12.6              | 1.3             | 12.6              | 1.0             |      |

|                                    |                                                                                       |                             | 144                     | 11.5              | 1.3             | 11.5              | 1.0             |      |

|                                    |                                                                                       | All Peripherals<br>disabled | 120                     | 8.7               | 1.2             | 8.7               | 0.9             |      |

|                                    |                                                                                       | disabled                    | 90                      | 7.1               | 1.4             | 7.1               | 1.1             |      |

|                                    |                                                                                       |                             | 60                      | 5.0               | 1.2             | 5.0               | 0.9             | -    |

|                                    |                                                                                       |                             | 30                      | 3.1               | 1.2             | 3.1               | 0.9             |      |

|                                    |                                                                                       |                             | 25                      | 2.8               | 1.2             | 2.8               | 0.9             |      |

| Table 33. Tyical current consumption in Sleep mode, regulator OFF <sup>(1)</sup> |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

|                            | I <sub>DD</sub> ( Typ) <sup>(1)</sup> |         |         |         |        |  |  |  |  |  |  |  |

|----------------------------|---------------------------------------|---------|---------|---------|--------|--|--|--|--|--|--|--|

| Б                          | eripheral                             |         | – Unit  |         |        |  |  |  |  |  |  |  |

| F                          | enpheral                              | Scale 1 | Scale 2 | Scale 3 |        |  |  |  |  |  |  |  |

|                            | OTG_FS                                | 25.67   | 26.67   | 23.58   |        |  |  |  |  |  |  |  |

| AHB2                       | DCMI                                  | 3.72    | 3.40    | 3.00    |        |  |  |  |  |  |  |  |

| (up to                     | RNG                                   | 2.28    | 2.36    | 2.17    | µA/MHz |  |  |  |  |  |  |  |

| 180 MHz)                   | Hash                                  | 4.39    | 4.03    | 3.58    |        |  |  |  |  |  |  |  |

|                            | Crypto                                | 3.00    | 2.78    | 2.42    |        |  |  |  |  |  |  |  |

| AHB3<br>(up to<br>180 MHz) | FMC                                   | 21.39   | 19.79   | 17.50   | µA/MHz |  |  |  |  |  |  |  |

| В                          | us matrix <sup>(2)</sup>              | 14.06   | 13.19   | 11.75   | µA/MHz |  |  |  |  |  |  |  |

| Table 35. Peripheral current consumption (continued) | Table 35 | . Peripheral | current consum | notion | (continued) |

|------------------------------------------------------|----------|--------------|----------------|--------|-------------|

|------------------------------------------------------|----------|--------------|----------------|--------|-------------|

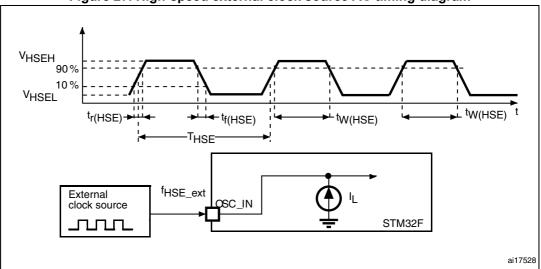

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 28*.

The characteristics given in *Table 38* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

| Symbol                                     | Parameter                                              | Conditions                       | Min             | Тур             | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|-----------------|-----------------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> | -                                | 32.768          | 1000            | kHz                |      |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  | 0.7V <sub>DD</sub>               | -               | V <sub>DD</sub> | V                  |      |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   |                                  | V <sub>SS</sub> | -               | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               | 450                              | -               | -               | ns                 |      |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -               | -               | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              |                                  | -               | 5               | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             |                                  | 30              | -               | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -               | -               | ±1                 | μA   |

| Table 38. | Low-speed | external us | ser clock chara | acteristics |

|-----------|-----------|-------------|-----------------|-------------|

|-----------|-----------|-------------|-----------------|-------------|

1. Guaranteed by design.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 36* and *Table 58*, respectively.

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Мах                | Unit |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|--------------------|------|

|                                               |                                                  |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$             | -   | -   | 4                  |      |

|                                               |                                                  |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$             | -   | -   | 2                  |      |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | $C_L$ = 10 pF, $V_{DD} \ge 2.7 V$                           | -   | -   | 8                  | MHz  |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -   | -   | 4                  |      |

|                                               |                                                  |                                                                                 | $C_L$ = 10 pF, $V_{DD} \ge 1.7 V$                           | -   | -   | 3                  |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V to<br>3.6 V | -   | -   | 100                | ns   |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.7 V             | -   | -   | 25                 |      |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.8 V             | -   | -   | 12.5               | MHz  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 10                 |      |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -   | -   | 50                 |      |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -   | -   | 20                 |      |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 12.5               |      |

|                                               | t <sub>f(IO)out</sub> /                          |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$             | -   | -   | 10                 |      |

|                                               |                                                  | Output high to low level fall time and output low to high                       | $C_L$ = 10 pF, $V_{DD} \ge 2.7 V$                           | -   | -   | 6                  | ns   |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$             | -   | -   | 20                 | 115  |

|                                               |                                                  |                                                                                 | $C_L$ = 10 pF, $V_{DD} \ge 1.7 V$                           | -   | -   | 10                 |      |

|                                               |                                                  |                                                                                 | $C_L$ = 40 pF, $V_{DD} \ge 2.7$ V                           | -   | -   | 50 <sup>(4)</sup>  |      |

|                                               |                                                  |                                                                                 | $C_L$ = 10 pF, $V_{DD} \ge 2.7 V$                           | -   | -   | 100 <sup>(4)</sup> |      |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | $C_L = 40 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$             | -   | -   | 25                 | MHz  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -   | -   | 50                 |      |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 42.5               |      |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥2.7 V              | -   | -   | 6                  |      |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | $C_L$ = 10 pF, $V_{DD} \ge 2.7 V$                           | -   | -   | 4                  | ns   |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | $C_L$ = 40 pF, $V_{DD} \ge 1.7 V$                           | -   | -   | 10                 |      |

|                                               |                                                  |                                                                                 | $C_L$ = 10 pF, $V_{DD} \ge 1.7 V$                           | -   | -   | 6                  |      |

Table 58. I/O AC characteristics<sup>(1)(2)</sup>

| Symbol          | Parameter                                                              | Min               | Max                | Unit |  |  |  |  |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|--|--|--|--|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |  |  |  |  |

| Table 61 | . I2C | analog | filter | characte | eristics <sup>(1)</sup> |

|----------|-------|--------|--------|----------|-------------------------|

|----------|-------|--------|--------|----------|-------------------------|

- 1. Guaranteed by design.

- 2. Spikes with widths below  $t_{AF(min)}$  are filtered.

- 3. Spikes with widths above  $t_{AF(max)}$  are not filtered

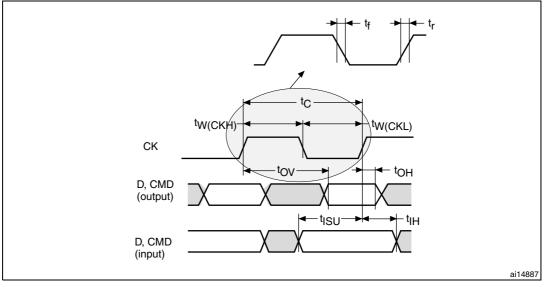

#### **SPI interface characteristics**

Unless otherwise specified, the parameters given in *Table 62* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| r                                         |                                      |                                                              |                             |     |     |                   |      |  |

|-------------------------------------------|--------------------------------------|--------------------------------------------------------------|-----------------------------|-----|-----|-------------------|------|--|

| Symbol                                    | Parameter                            | Condition                                                    | Min                         | Тур | Max | Unit              |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> |                                      | Master mode, SPI1/4/5/6,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V     |                             |     |     | 45                |      |  |

|                                           |                                      | Slave mode,                                                  | Receiver                    | -   | -   | 45                |      |  |

|                                           | SPI clock frequency                  | SPI1/4/5/6,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V                  | Transmitter/<br>full-duplex |     |     | 38 <sup>(2)</sup> | MHz  |  |

|                                           |                                      | Master mode, SPI1/2/3/4/5/6,<br>1.7 V≤V <sub>DD</sub> ≤3.6 V |                             |     |     | 22.5              |      |  |

|                                           |                                      | Slave mode, SPI1/2/3/4/5/6,<br>1.7 V≤V <sub>DD</sub> ≤3.6 V  |                             |     | -   | -                 | 22.5 |  |

| Duty(SCK)                                 | Duty cycle of SPI clock<br>frequency | Slave mode                                                   |                             | 30  | 50  | 70                | %    |  |

Table 62. SPI dynamic characteristics<sup>(1)</sup>

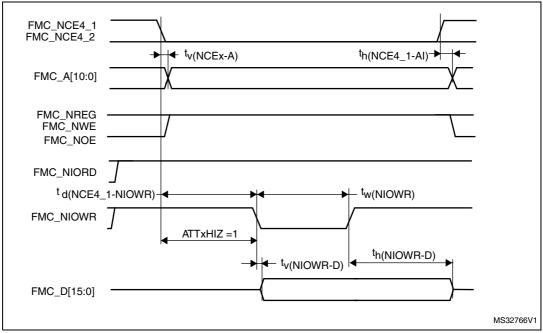

Figure 68. PC Card/CompactFlash controller waveforms for I/O space write access

# Table 98. Switching characteristics for PC Card/CF read and write cycles in attribute/common space $^{(1)(2)}$

| Symbol                    | Parameter                                  | Min                       | Мах                      | Unit |

|---------------------------|--------------------------------------------|---------------------------|--------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FMC_Ncex low to FMC_Ay valid               | -                         | 0                        | ns   |

| t <sub>h(NCEx_AI)</sub>   | FMC_NCEx high to FMC_Ax invalid            | 0                         | -                        | ns   |

| t <sub>d(NREG-NCEx)</sub> | FMC_NCEx low to FMC_NREG valid             | -                         | 1                        | ns   |

| t <sub>h(NCEx-NREG)</sub> | FMC_NCEx high to FMC_NREG invalid          | T <sub>HCLK</sub> – 2     | -                        | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FMC_NCEx low to FMC_NWE low                | -                         | 5T <sub>HCLK</sub>       | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low width                          | 8T <sub>HCLK</sub> – 0.5  | 8T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>d(NWE_NCEx)</sub>  | FMC_NWE high to FMC_NCEx high              | 5T <sub>HCLK</sub> +1     | -                        | ns   |

| t <sub>V(NWE-D)</sub>     | FMC_NWE low to FMC_D[15:0] valid           | -                         | 0                        | ns   |

| t <sub>h(NWE-D)</sub>     | FMC_NWE high to FMC_D[15:0] invalid        | 9T <sub>HCLK</sub> – 0.5  | -                        | ns   |

| t <sub>d(D-NWE)</sub>     | FMC_D[15:0] valid before FMC_NWE high      | 13T <sub>HCLK</sub> – 3   |                          | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FMC_NCEx low to FMC_NOE low                | -                         | 5T <sub>HCLK</sub>       | ns   |

| t <sub>w(NOE)</sub>       | FMC_NOE low width                          | 8 T <sub>HCLK</sub> – 0.5 | 8 T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FMC_NOE high to FMC_NCEx high              | 5T <sub>HCLK</sub> – 1    | -                        | ns   |

| t <sub>su (D-NOE)</sub>   | FMC_D[15:0] valid data before FMC_NOE high | T <sub>HCLK</sub>         | -                        | ns   |

| t <sub>h(NOE-D)</sub>     | FMC_NOE high to FMC_D[15:0] invalid        | 0                         | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

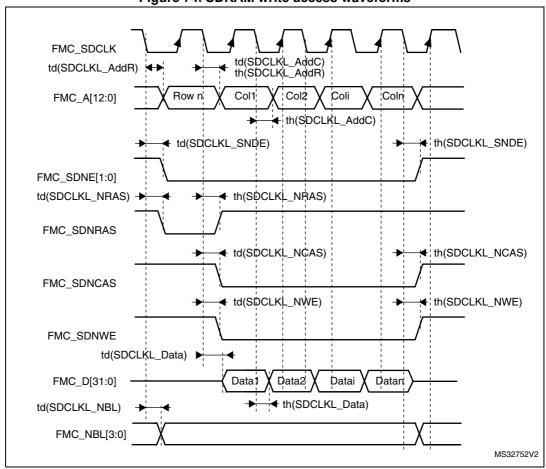

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 2                        | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |

| $t_{d(SDCLKL\_Add)}$          | Address valid time     | -                        | 1.5                     |      |

| $t_{d(SDCLKL-SDNE)}$          | Chip select valid time | -                        | 0.5                     | ns   |

| $t_{h(SDCLKL\_SDNE)}$         | Chip select hold time  | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                       |      |

## Table 102. SDRAM read timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

### Table 103. LPSDR SDRAM read timings<sup>(1)(2)</sup>

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |  |  |

|-------------------------------|------------------------|--------------------------|-------------------------|------|--|--|

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |  |  |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time  | 2.5                      | -                       |      |  |  |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |  |  |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                        | 1                       |      |  |  |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 1                       | ns   |  |  |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 1                        | -                       | 115  |  |  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time      | -                        | 1                       |      |  |  |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 1                        | -                       |      |  |  |

| td(SDCLKL_SDNCAS)             | SDNCAS valid time      | -                        | 1                       | ]    |  |  |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 1                        | -                       |      |  |  |

1. CL = 10 pF.

2. Guaranteed by characterization results.

Figure 74. SDRAM write access waveforms

#### 6.3.29 SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 108* for the SDIO/MMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

#### Figure 78. SDIO high-speed mode

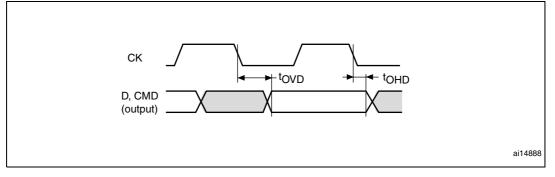

Figure 79. SD default mode

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

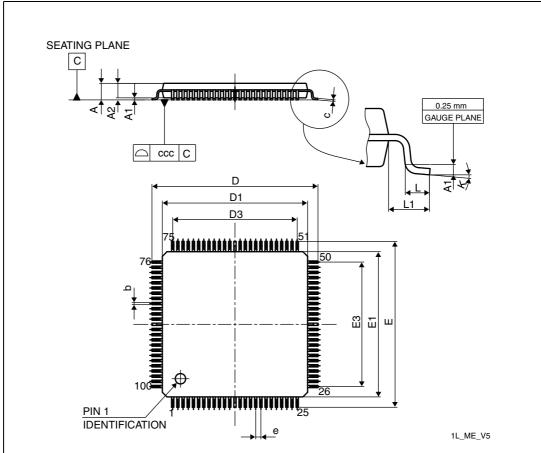

## 7.1 LQFP100 package information

Figure 80. LQFP100 -100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

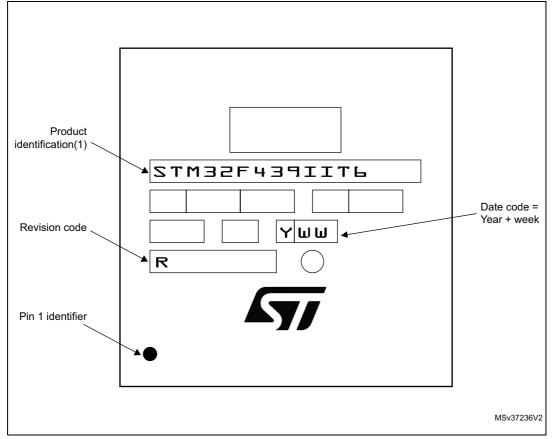

#### **Device marking for LQFP176**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Figure 91. LQFP176 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

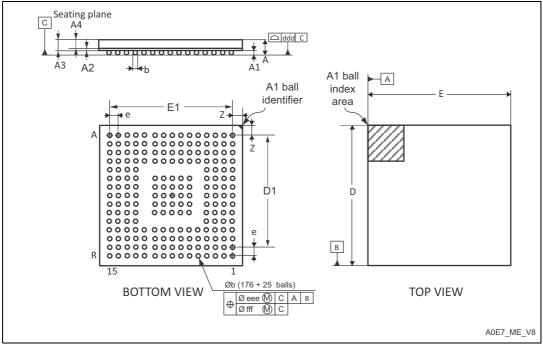

## 7.7 UFBGA176+25 package information

Figure 98. UFBGA176+25 - ball 10 x 10 mm, 0.65 mm pitch ultra thin fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 118. UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch, |

|-----------------------------------------------------------|

| ultra fine pitch ball grid array package mechanical data  |

| Gumbal | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | Min.        | Тур.   | Max.   | Min.                  | Тур.   | Max.   |  |

| А      | -           | -      | 0.600  | -                     | -      | 0.0236 |  |

| A1     | -           | -      | 0.110  | -                     | -      | 0.0043 |  |

| A2     | -           | 0.130  | -      | -                     | 0.0051 | -      |  |

| A3     | -           | 0.450  | -      | -                     | 0.0177 | -      |  |

| A4     | -           | 0.320  | -      | -                     | 0.0126 | -      |  |

| b      | 0.240       | 0.290  | 0.340  | 0.0094                | 0.0114 | 0.0134 |  |

| D      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| D1     | -           | 9.100  | -      | -                     | 0.3583 | -      |  |

| E      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| E1     | -           | 9.100  | -      | -                     | 0.3583 | -      |  |

| е      | -           | 0.650  | -      | -                     | 0.0256 | -      |  |

| Z      | -           | 0.450  | -      | -                     | 0.0177 | -      |  |

| ddd    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

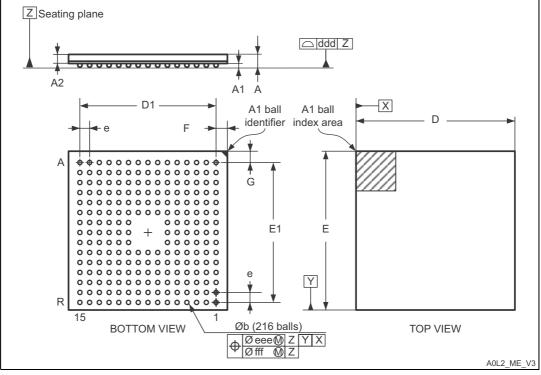

## 7.8 **TFBGA216** package information

Figure 101. TFBGA216 - 216 ball 13 × 13 mm 0.8 mm pitch thin fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 120. TFBGA216 - 216 ball 13 × 13 mm 0.8 mm pitch thin fine pitch ball grid arraypackage mechanical data

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Мах    |

| A      | -           | -      | 1.100  | -                     | -      | 0.0433 |

| A1     | 0.150       | -      | -      | 0.0059                | -      | -      |

| A2     | -           | 0.760  | -      | -                     | 0.0299 | -      |

| b      | 0.350       | 0.400  | 0.450  | 0.0138                | 0.0157 | 0.0177 |

| D      | 12.850      | 13.000 | 13.150 | 0.5118                | 0.5118 | 0.5177 |

| D1     | -           | 11.200 | -      | -                     | 0.4409 | -      |

| E      | 12.850      | 13.000 | 13.150 | 0.5118                | 0.5118 | 0.5177 |

| E1     | -           | 11.200 | -      | -                     | 0.4409 | -      |

| е      | -           | 0.800  | -      | -                     | 0.0315 | -      |

| F      | -           | 0.900  | -      | -                     | 0.0354 | -      |

| ddd    | -           | -      | 0.100  | -                     | -      | 0.0039 |