#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                |                                                                                     |

| RAM Size                   | 256K × 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 144-LQFP                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f439zgt6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.26 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available. They can be operated in master or slave mode, in full duplex and simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

Note: For I2S2 full-duplex mode, I2S2\_CK and I2S2\_WS signals can be used only on GPIO Port B and GPIO Port D.

# 3.27 Serial Audio interface (SAI1)

The serial audio interface (SAI1) is based on two independent audio sub-blocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both sub-blocks can be configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

SAI1 can be served by the DMA controller.

## 3.28 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S/SAI flow with an external PLL (or Codec output).

# 3.29 Audio and LCD PLL(PLLSAI)

An additional PLL dedicated to audio and LCD-TFT is used for SAI1 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the LCD-TFT clock.

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

## 3.42 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

## 3.43 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F43x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

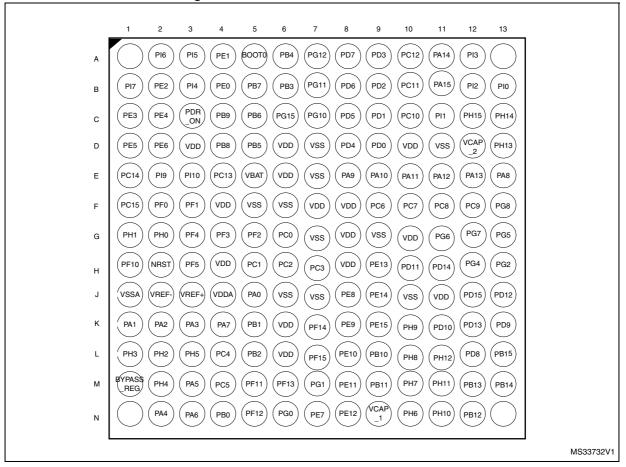

#### Figure 16. STM32F43x UFBGA169 ballout

1. The above figure shows the package top view.

2. The 4 corners balls, A1,A13, N1 and N13, are not bonded internally and should be left not connected on the PCB.

|         |         |          | Pin nı   | Imbe    | r        |         |          |                                                      |          |                 |       |                                                                                                                     |                             |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                                 | Additional<br>functions     |

| -       | _       | M1       | L4       | 48      | N11      | -       | L5       | BYPASS_<br>REG                                       | I        | FT              | -     | -                                                                                                                   | -                           |

| 28      | 39      | J11      | K4       | 49      | J8       | 52      | K5       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| 29      | 40      | N2       | N4       | 50      | M10      | 53      | N4       | PA4                                                  | I/O      | ТТа             | (5)   | SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK,<br>OTG_HS_SOF,<br>DCMI_HSYNC,<br>LCD_VSYNC,<br>EVENTOUT                | ADC12_<br>IN4 /DAC_<br>OUT1 |

| 30      | 41      | М3       | P4       | 51      | M9       | 54      | P4       | PA5                                                  | I/O      | ТТа             | (5)   | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK,<br>OTG_HS_ULPI_CK,<br>EVENTOUT                                        | ADC12_<br>IN5/DAC_<br>OUT2  |

| 31      | 42      | N3       | P3       | 52      | N10      | 55      | P3       | PA6                                                  | I/O      | FT              | (5)   | TIM1_BKIN,<br>TIM3_CH1,<br>TIM8_BKIN,<br>SPI1_MISO,<br>TIM13_CH1,<br>DCMI_PIXCLK,<br>LCD_G2, EVENTOUT               | ADC12_<br>IN6               |

| 32      | 43      | K4       | R3       | 53      | L8       | 56      | R3       | PA7                                                  | I/O      | FT              | (5)   | TIM1_CH1N,<br>TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI,<br>TIM14_CH1,<br>ETH_MII_RX_DV/ETH_<br>RMII_CRS_DV,<br>EVENTOUT | ADC12_<br>IN7               |

| 33      | 44      | L4       | N5       | 54      | M8       | 57      | N5       | PC4                                                  | I/O      | FT              | (5)   | ETH_MII_RXD0/ETH_<br>RMII_RXD0,<br>EVENTOUT                                                                         | ADC12_<br>IN14              |

| 34      | 45      | M4       | P5       | 55      | N9       | 58      | P5       | PC5                                                  | I/O      | FT              | (5)   | ETH_MII_RXD1/ETH_<br>RMII_RXD1,<br>EVENTOUT                                                                         | ADC12_<br>IN15              |

| -       | -       | -        | -        | -       | J7       | 59      | L7       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| -       | -       | -        | -        | -       | -        | 60      | L6       | VSS                                                  | S        | -               | -     | -                                                                                                                   | -                           |

Table 10. STM32F437xx and STM32F439xx pin and ball definitions (continued)

#### Pinouts and pin description

- 4. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F4xx reference manual, available from the STMicroelectronics website: www.st.com.

- 5. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- If the device is delivered in an WLCSP143, UFBGA169, UFBGA176, LQFP176 or TFBGA216 package, and the BYPASS\_REG pin is set to V<sub>DD</sub> (Regulator OFF/internal reset ON mode), then PA0 is used as an internal Reset (active low).

- 7. PI0 and PI1 cannot be used for I2S2 full-duplex mode.

- 8. The DCMI\_VSYNC alternate function on PG9 is only available on silicon revision 3.

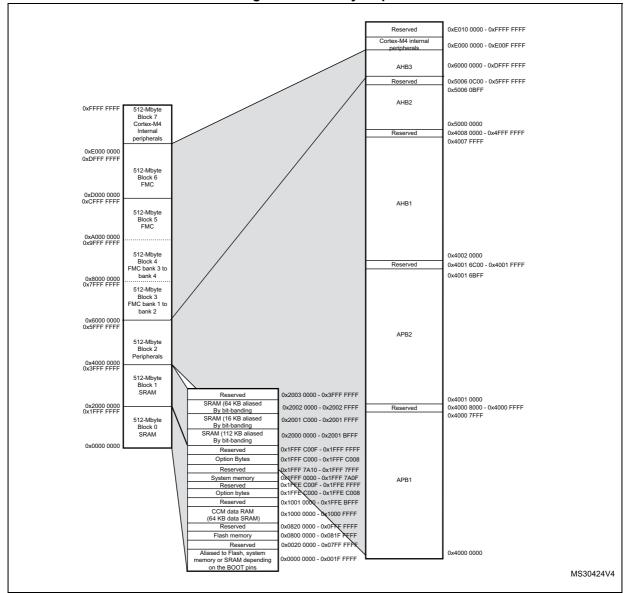

# 5 Memory mapping

The memory map is shown in *Figure 19*.

Figure 19. Memory map

DocID024244 Rev 10

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

|      | 0x4008 0000- 0x4FFF FFFF  | Reserved                 |

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 BC00- 0x4003 FFFF  | Reserved                 |

|      | 0x4002 B000 - 0x4002 BBFF | DMA2D                    |

|      | 0x4002 9400 - 0x4002 AFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0X4002 5000 - 0X4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| АПВТ | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0X4002 3400 - 0X4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2C00 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2800 - 0x4002 2BFF | GPIOK                    |

|      | 0x4002 2400 - 0x4002 27FF | GPIOJ                    |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0X4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

# Table 13. STM32F437xx and STM32F439xx register boundary addresses (continued)

|                 |                   |                        |                         |     |                           | Max <sup>(1)</sup>        |                            |      |

|-----------------|-------------------|------------------------|-------------------------|-----|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter         | Conditions             | f <sub>HCLK</sub> (MHz) | Тур | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                   |                        | 180                     | 78  | 89 <sup>(3)</sup>         | 110                       | 130 <sup>(3)</sup>         |      |

|                 |                   |                        | 168                     | 66  | 75 <sup>(3)</sup>         | 93                        | 110 <sup>(3)</sup>         |      |

|                 |                   |                        | 150                     | 56  | 61                        | 80                        | 96                         |      |

|                 |                   |                        | 144                     | 54  | 58                        | 78                        | 94                         |      |

|                 |                   |                        | 120                     | 40  | 44                        | 59                        | 72                         |      |

|                 |                   | All                    | 90                      | 32  | 34                        | 46                        | 56                         |      |

|                 |                   | Peripherals            | 60                      | 22  | 23                        | 31                        | 38                         |      |

|                 |                   | enabled <sup>(2)</sup> | 30                      | 10  | 16                        | 30                        | 43                         |      |

|                 |                   |                        | 25                      | 9   | 14                        | 28                        | 40                         |      |

|                 |                   |                        | 16                      | 5   | 12                        | 25                        | 40                         | -    |

|                 |                   |                        | 8                       | 3   | 8                         | 22                        | 35                         |      |

|                 |                   |                        | 4                       | 3   | 7                         | 21                        | 34                         |      |

| 1               | Supply current in |                        | 2                       | 2   | 6.5                       | 20                        | 33                         | mA   |

| I <sub>DD</sub> | Sleep mode        |                        | 180                     | 21  | 26 <sup>(3)</sup>         | 54                        | 76 <sup>(3)</sup>          |      |

|                 |                   |                        | 168                     | 16  | 20 <sup>(3)</sup>         | 41                        | 58 <sup>(3)</sup>          |      |

|                 |                   |                        | 150                     | 14  | 17                        | 36                        | 52                         |      |

|                 |                   |                        | 144                     | 13  | 16.5                      | 35                        | 51                         |      |

|                 |                   |                        | 120                     | 10  | 14                        | 28                        | 41                         |      |

|                 |                   | All                    | 90                      | 8   | 13                        | 26                        | 37                         |      |

|                 |                   | Peripherals            | 60                      | 6   | 9                         | 17                        | 25                         |      |

|                 |                   | disabled               | 30                      | 5   | 8                         | 22                        | 35                         |      |

|                 |                   |                        | 25                      | 3   | 7                         | 21                        | 34                         |      |

|                 |                   |                        | 16                      | 3   | 7                         | 21                        | 34                         |      |

|                 |                   |                        | 8                       | 2   | 6                         | 20                        | 33                         |      |

|                 |                   |                        | 4                       | 2   | 6                         | 20                        | 33                         |      |

|                 |                   |                        | 2                       | 2   | 6                         | 20                        | 33                         |      |

| Table 26 | . Typical and | l maximum | current | consump | otion in | Sleep | mode |

|----------|---------------|-----------|---------|---------|----------|-------|------|

|----------|---------------|-----------|---------|---------|----------|-------|------|

1. Guaranteed by characterization unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. Based on characterization, tested in production.

## 6.3.12 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 52: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup>  | Unit |

|-------------------|-----------------------|------|-----|---------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                  | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                   | %    |

| MODEPER * INCSTEP |                       | -    | -   | 2 <sup>15</sup> – 1 | -    |

| Table 46. S | SCG param | eters constraint |

|-------------|-----------|------------------|

|-------------|-----------|------------------|

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

MODEPER = round[ $f_{PLL IN} / (4 \times f_{Mod})$ ]

$f_{PLL}$  IN and  $f_{Mod}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN}$  = 1 MHz, and  $f_{MOD}$  = 1 kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15}-1) \times md \times PLLN) / (100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$md_{guantized} \% = (250 \times 126 \times 100 \times 5)/((2^{15} - 1) \times 240) = 2.002\%$ (peak)

DocID024244 Rev 10

STM32F

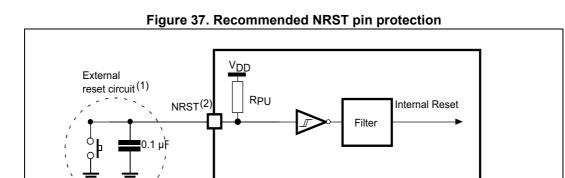

## 6.3.18 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 56: I/O static characteristics*).

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       |                         | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 59. NRST pin characteristics

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

#### 2. Guaranteed by design.

1. The reset network protects the device against parasitic resets.

- 2. The external capacitor must be placed as close as possible to the device.

- 3. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 59*. Otherwise the reset is not taken into account by the device.

ai14132c

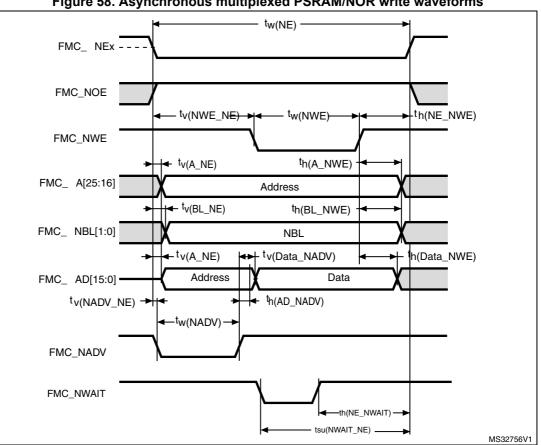

Figure 58. Asynchronous multiplexed PSRAM/NOR write waveforms

| Table 92. Asynchror | nous multiplexed PSRAM/NOR write timing | js <sup>(1)(2)</sup> |

|---------------------|-----------------------------------------|----------------------|

|---------------------|-----------------------------------------|----------------------|

| Symbol                    | Parameter                                           | Min                     | Мах                     | Unit |

|---------------------------|-----------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                     | 4T <sub>HCLK</sub>      | 4T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>v(NWE_NE)</sub>    | FMC_NEx low to FMC_NWE low                          | T <sub>HCLK</sub> – 1   | T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                    | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>h(NE_NWE)</sub>    | FMC_NWE high to FMC_NE high hold time               | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                          | -                       | 0                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                         | 0.5                     | 1                       | ns   |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                   | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(adress) valid hold time after FMC_NADV high) | T <sub>HCLK</sub> – 2   | -                       | ns   |

| t <sub>h(A_NWE)</sub>     | Address hold time after FMC_NWE high                | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NWE)</sub>    | FMC_BL hold time after FMC_NWE high                 | T <sub>HCLK</sub> – 2   | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                         | -                       | 2                       | ns   |

| t <sub>v(Data_NADV)</sub> | FMC_NADV high to Data valid                         | -                       | T <sub>HCLK</sub> +1.5  | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FMC_NWE high                   | T <sub>HCLK</sub> +0.5  | -                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

|                           | -                                         |                         |                         |      |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 9T <sub>HCLK</sub>      | 9T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 7T <sub>HCLK</sub>      | 7T <sub>HCLK</sub> +2   | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                       | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> –1   | -                       | ns   |

Table 93. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

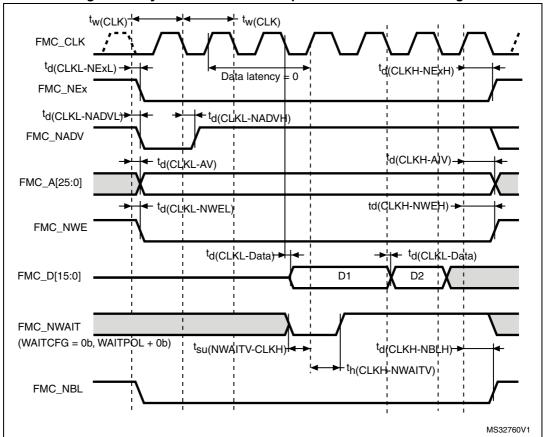

## Synchronous waveforms and timings

*Figure 59* through *Figure 62* represent synchronous waveforms and *Table 94* through *Table 97* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F4xx reference manual : RM0090)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period (with maximum FMC\_CLK = 90 MHz).

| Symbol                         | Parameter                                 | Min | Мах | Unit |

|--------------------------------|-------------------------------------------|-----|-----|------|

| t <sub>h(CLKH-DV)</sub>        | FMC_D[15:0] valid data after FMC_CLK high | 0   | -   | ns   |

| t <sub>(NWAIT-CLKH)</sub>      | FMC_NWAIT valid before FMC_CLK high       | 4   |     |      |

| t <sub>h(CLKH-</sub><br>NWAIT) | FMC_NWAIT valid after FMC_CLK high        | 0   |     |      |

|  | Table 96. Synchronous non-multip | lexed NOR/PSRAM read timings <sup>(1)(2)</sup> (continued) |

|--|----------------------------------|------------------------------------------------------------|

|--|----------------------------------|------------------------------------------------------------|

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

## Figure 62. Synchronous non-multiplexed PSRAM write timings

|                            |                                      | V                      |     |      |

|----------------------------|--------------------------------------|------------------------|-----|------|

| Symbol                     | Parameter                            | Min                    | Мах | Unit |

| t <sub>(CLK)</sub>         | FMC_CLK period                       | 2T <sub>HCLK</sub> – 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FMC_CLK low to FMC_NEx low (x=02)    | -                      | 0.5 | ns   |

| t <sub>(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02) | T <sub>HCLK</sub>      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FMC_CLK low to FMC_NADV low          | -                      | 0   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FMC_CLK low to FMC_NADV high         | 0                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FMC_CLK low to FMC_Ax valid (x=1625) | -                      | 0   | ns   |

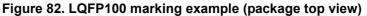

## **Device marking for LQFP100**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

1. Dimensions are expressed in millimeters.

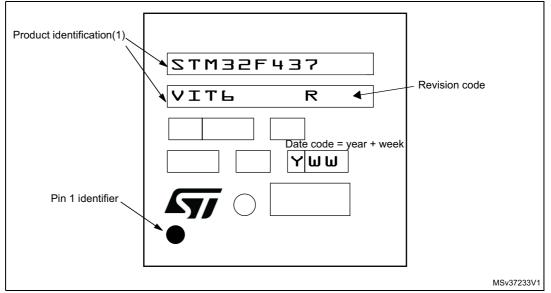

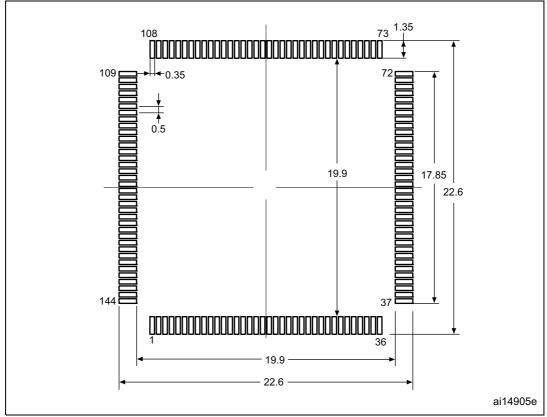

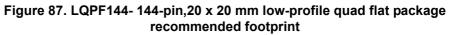

#### **Device marking for LQFP144**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

### Figure 88. LQFP144 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

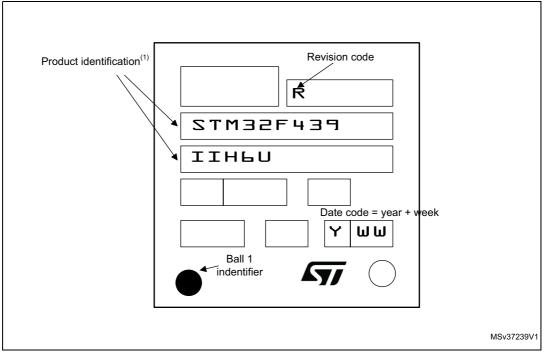

### **Device marking for UFBGA176+25**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# Appendix A Recommendations when using internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

- The over-drive mode is not supported.

# A.1 Operating conditions

# Table 123. Limitations depending on the operating power supply range

| Operating<br>power<br>supply<br>range           | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                           | Possible Flash<br>memory<br>operations        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup> | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(4)</sup>                                                                                   | 168 MHz with 8<br>wait states and<br>over-drive OFF                               | <ul> <li>No I/O compensation</li> </ul> | 8-bit erase and<br>program<br>operations only |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.17.1: Internal reset ON).

4. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

| Date                | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>19-Feb-2015 | 6<br>Revision | Changes           Update SPI/IS2 in Table 2: STM32F437xx and STM32F439xx features<br>and peripheral counts.           Updated LQFP208 in Table 4: Regulator ON/OFF and internal reset<br>ON/OFF availability.           Updated Figure 19: Memory map.           Changed PLS[2:0]=101 (falling edge) maximum value in Table 22:<br>reset and power control block characteristics.           Updated current consumption with all peripherals disabled in Table 24:<br>Typical and maximum current consumption in Run mode, code with<br>data processing running from Flash memory (ART accelerator<br>enabled except prefetch) or RAM.           Updated note 1. in Table 28: Typical and maximum current<br>consumptions in Standby mode.           Updated Table 56: I/O static characteristics.           Section : I2C interface characteristics: updated section introduction,<br>removed Table 12C characteristics, Figure 12C bus AC waveforms and<br>measurement circuit and Table SCL frequency; added Table 61: I2C<br>analog filter characteristics.           Updated Figure 51: Typical connection diagram using the ADC.           Updated Figure 51: Typical connection diagram using the ADC.           Updated Figure 83: WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm<br>pitch wafer level chip scale package outline and Table 111: WLCSP143<br>- 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale<br>package mechanical data; added Figure 84: WLCSP143 - 143-ball,<br>4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale recommended<br>footprint and Table 112: WLCSP143 recommended PCB design rules<br>(0.4 mm pitch). Updated Figure 85: WLCSP143 marking example<br>(package top view) and related note. Updated Section : Device<br>marking for WLCSP143.           Updated Se |

Table 124. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID024244 Rev 10