Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | FR60 RISC                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 96MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                              |

| Peripherals                | DMA, LVD, PWM, WDT                                                                 |

| Number of I/O              | 108                                                                                |

| Program Memory Size        | 1.0625MB (1.0625M x 8)                                                             |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 48K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 32x10b                                                                         |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 144-LQFP                                                                           |

| Supplier Device Package    | 144-LQFP (20x20)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f467bapmc-gse2-w019 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

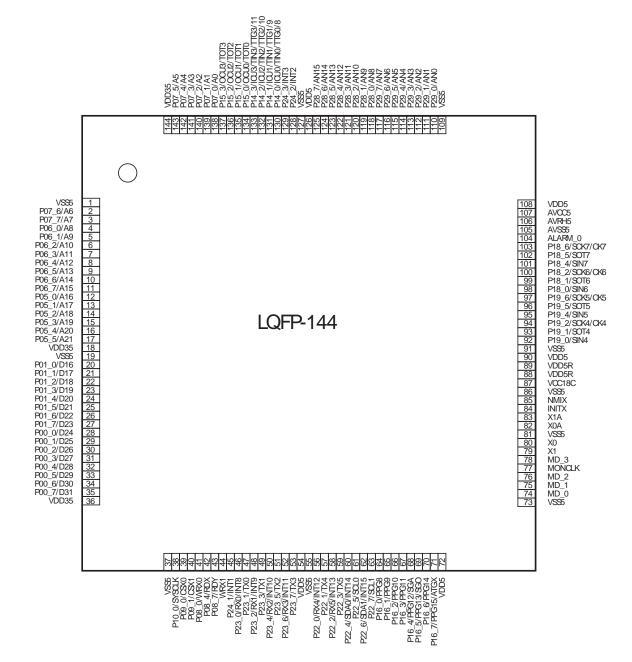

# 2. Pin Assignment

## 2.1 MB91F467BA/466BA with MD 3=1

(TOP VIEW)

# 3. Pin Description

# 3.1 MB91F467BA/466BA AND MB91F465BB/464BB with MD\_3=1

| Pin no.  | Pin name                                     | I/O | I/O circuit type <sup>[1]</sup> | Function                                                                   |

|----------|----------------------------------------------|-----|---------------------------------|----------------------------------------------------------------------------|

| 2, 3     | P07_6, P07_7                                 | I/O | В                               | General-purpose input/output port                                          |

| 2, 3     | A6, A7                                       | 1/0 | Б                               | Signal pins of external address bus (bit6 to bit7)                         |

| 4 to 11  | P06_0 to P06_7                               | I/O | В                               | General-purpose input/output port                                          |

| 4 to 11  | A8 to A15                                    | 1/0 | В                               | Signal pins of external address bus (bit8 to bit15)                        |

| 10 to 17 | P05_0 to P05_5                               | 1/0 | ^                               | General-purpose input/output port                                          |

| 12 to 17 | A16 to A21                                   | I/O | A                               | Signal pins of external address bus (bit16 to bit21)                       |

| 20 4- 27 | P01_0 to P01_7                               | 1/0 | Δ.                              | General-purpose input/output port                                          |

| 20 to 27 | D16 to D23                                   | I/O | A                               | Signal pins of external data bus (bit16 to bit23)                          |

| 20 4- 25 | P00_0 to P00_7                               | 1/0 | Δ.                              | General-purpose input/output port                                          |

| 28 to 35 | D24 to D31                                   | I/O | A                               | Signal pins of external data bus (bit24 to bit31)                          |

| 20       | P10_0                                        | 1/0 | ^                               | General-purpose input/output port                                          |

| 38       | SYSCLK                                       | I/O | A                               | External bus clock output pin                                              |

| 00       | P09_0                                        | 1/0 |                                 | General-purpose input/output port                                          |

| 39       | CSX0                                         | I/O | A                               | Chip select output pins                                                    |

| 40       | P09_1                                        | 1/0 |                                 | General-purpose input/output port                                          |

| 40       | CSX1                                         | I/O | Α                               | Chip select output pins                                                    |

| 44       | P08_0                                        | 1/0 | ^                               | General-purpose input/output port                                          |

| 41       | WRX0                                         | I/O | A                               | External write strobe output pins                                          |

| 40       | P08_4                                        | 1/0 | ^                               | General-purpose input/output port                                          |

| 42       | RDX                                          | I/O | A                               | External read strobe output pin                                            |

| 40       | P08_7                                        | 1/0 |                                 | General-purpose input/output port                                          |

| 43       | RDY                                          | I/O | A                               | External ready input pin                                                   |

|          | P08_1<br>Not on<br>MB91F467BA/MB91F466<br>BA |     |                                 | General-purpose input/output port                                          |

| 44       | WRX1                                         | I/O | Α                               | External write strobe output pins                                          |

|          | INT0<br>Not on<br>MB91F467BA/MB91F466<br>BA  |     |                                 | External interrupt input, can only be used in general-purpose IO port mode |

|          | P24_1                                        |     |                                 | General-purpose input/output port                                          |

| 45       | INT1                                         | I/O | Α                               | External interrupt input pins                                              |

|          | P23_0                                        |     |                                 | General-purpose input/output port                                          |

| 46       | RX0                                          | I/O | Α                               | RX input pin of CAN0                                                       |

|          | INT8                                         |     |                                 | External interrupt input pins                                              |

| 4-       | P23_1                                        | 1/0 |                                 | General-purpose input/output port                                          |

| 47       | TX0                                          | I/O | Α                               | TX output pin of CAN0                                                      |

Document Number: 002-04608 Rev. \*A

| Pin no.    | Pin name              | I/O | I/O circuit type <sup>[1]</sup> | Function                                           |

|------------|-----------------------|-----|---------------------------------|----------------------------------------------------|

|            | P19_6                 |     |                                 | General-purpose input/output port                  |

| 97         | SCK5                  | I/O | Α                               | Clock input/output pin of USART5                   |

|            | CK5                   |     |                                 | External clock input pin of free-run timer 5       |

| 00         | P18_0                 | 1/0 | Δ.                              | General-purpose input/output port                  |

| 98         | SIN6                  | I/O | A                               | Data input pin of USART6                           |

| 00         | P18_1                 | 1/0 | Δ.                              | General-purpose input/output port                  |

| 99         | SOT6                  | I/O | A                               | Data output pin of USART6                          |

|            | P18_2                 |     |                                 | General-purpose input/output port                  |

| 100        | SCK6                  | I/O | Α                               | Clock input/output pin of USART6                   |

|            | CK6                   |     |                                 | External clock input pin of free-run timer 6       |

| 101        | P18_4                 | 1/0 |                                 | General-purpose input/output port                  |

| 101        | SIN7                  | I/O | A                               | Data input pin of USART7                           |

| 100        | P18_5                 | 1/0 |                                 | General-purpose input/output port                  |

| 102        | SOT7                  | I/O | Α                               | Data output pin of USART7                          |

|            | P18_6                 |     |                                 | General-purpose input/output port                  |

| 103        | SCK7                  | I/O | А                               | Clock input/output pin of USART7                   |

|            | CK7                   |     |                                 | External clock input pin of free-run timer 7       |

| 104        | ALARM_0               | 0   | N                               | Alarm comparator input pin                         |

| 440 1 447  | P29_0 to P29_7        | I/O | -                               | General-purpose input/output port                  |

| 110 to 117 | 110 to 117 AN0 to AN7 |     | В                               | Analog input pins of A/D converter                 |

| 4404 405   | P28_0 to P28_7        | 1/0 |                                 | General-purpose input/output port                  |

| 118 to 125 | AN8 to AN15           | I/O | В                               | Analog input pins of A/D converter                 |

| 100        | P24_2                 | 1/0 |                                 | General-purpose input/output port                  |

| 128        | INT2                  | I/O | Α                               | External interrupt input pin                       |

| 100        | P24_3                 | 1/0 |                                 | General-purpose input/output port                  |

| 129        | INT3                  | I/O | Α                               | External interrupt input pin                       |

|            | P14_0 to P14_3        |     |                                 | General-purpose input/output port                  |

| 4004 400   | ICU0 to ICU3          |     |                                 | Input capture input pins                           |

| 130 to 133 | TIN0 to TIN3          | I/O | Α                               | External trigger input pins of reload timer        |

|            | TTG0/8 to TTG3/11     |     |                                 | External trigger input pins of PPG timer           |

|            | P15_0 to P15_3        |     |                                 | General-purpose input/output port                  |

| 134 to 137 | OCU0 to OCU3          | I/O | Α                               | Output compare output pins                         |

|            | TOT0 to TOT3          |     |                                 | Reload timer output pins                           |

| 1001 115   | P07_0 to P07_5        | 1/0 | _                               | General-purpose input/output port                  |

| 138 to 143 | A0 to A5              | I/O | В                               | Signal pins of external address bus (bit0 to bit5) |

# 5.6 Mode Pins (MD\_x)

These pins should be connected directly to the power supply or ground pins. To prevent the device from entering test mode accidentally due to noise, minimize the lengths of the patterns between each mode pin and power supply pin or ground pin on the printed circuit board as possible and connect them with low impedance.

# 5.7 Notes on Operating in PLL Clock Mode

If the oscillator is disconnected or the clock input stops when the PLL clock is selected, the microcontroller may continue to operate at the free-running frequency of the self-oscillating circuit of the PLL. However, this self-running operation cannot be guaranteed.

# 5.8 Pull-up Control

The AC standard is not guaranteed in case a pull-up resistor is connected to the pin serving as an external bus pin.

Document Number: 002-04608 Rev. \*A Page 28 of 126

# 7.3 MB91F465BB/464BB with MD\_3=1

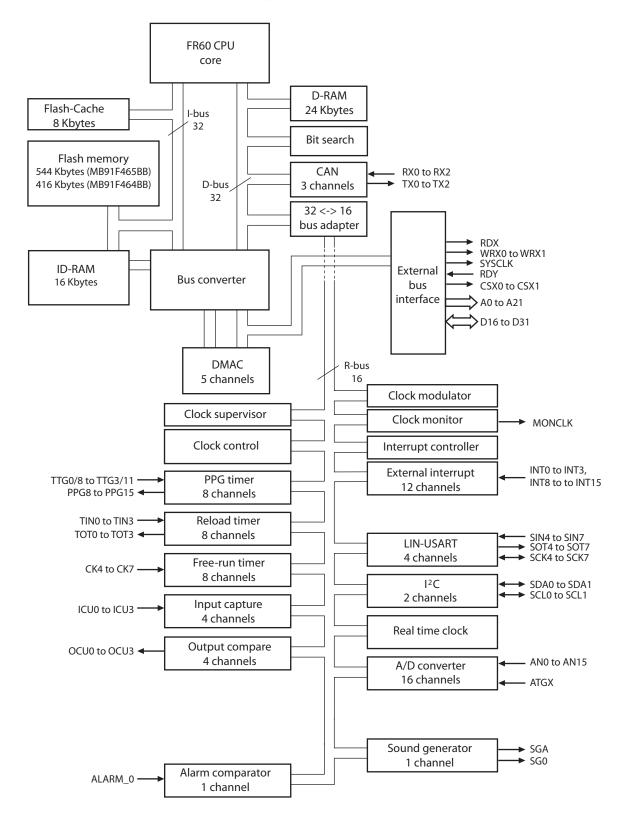

### 8. CPU and Control Unit

The FR family CPU is a high performance core that is designed based on the RISC architecture with advanced instructions for embedded applications.

### 8.1 Features

■ Adoption of RISC architecture Basic instruction: 1 instruction per cycle

■ General-purpose registers: 32-bit × 16 registers

■ 4 Gbytes linear memory space

■ Multiplier installed

32-bit × 32-bit multiplication: 5 cycles 16-bit × 16-bit multiplication: 3 cycles

■ Enhanced interrupt processing function Quick response speed (6 cycles) Multiple-interrupt support Level mask function (16 levels)

■ Enhanced instructions for I/O operation Memory-to-memory transfer instruction Bit processing instruction Basic instruction word length: 16 bits

■ Low-power consumption Sleep mode/stop mode

### 8.2 Internal Architecture

- The FR family CPU uses the Harvard architecture in which the instruction bus and data bus are independent of each other.

- A 32-bit ↔ 16-bit buffer is connected to the 32-bit bus (D-bus) to provide an interface between the CPU and peripheral resources.

- A Harvard ↔ Princeton bus converter is connected to both the I-bus and D-bus to provide an interface between the CPU and the bus controller.

Document Number: 002-04608 Rev. \*A Page 34 of 126

# 9. Embedded Program/Data Memory (Flash)

#### 9.1 Flash features

- MB91F467BA: 1088 Kbytes (16 × 64 Kbytes + 8 × 8 Kbytes = 8.5 Mbits)

- MB91F466BA: 832 Kbytes (12 × 64 Kbytes + 8 × 8 Kbytes = 6.5 Mbits)

- MB91F465BB: 544 Kbytes (8 × 64 Kbytes + 4 × 8 Kbytes = 4.25 Mbits)

- MB91F464BB: 416 Kbytes (6 × 64 Kbytes + 4 × 8 Kbytes = 3.25 Mbits)

- Programmable wait states for read/write access

- Flash and Boot security with security vector at 0x0014:8000 0x0014:800F

- Boot security

- Basic specification: Same as MBM29LV400TC (except size and part of sector configuration)

## 9.2 Operation Modes

### 9.2.1 64-bit CPU mode (available on MB91F467BA/466BA only):

- CPU reads and executes programs in word (32-bit) length units.

- Flash writing is not possible.

- Actual Flash Memory access is performed in d-word (64-bit) length units.

### 9.2.2 32-bit CPU mode:

- CPU reads and executes programs in word (32-bit) length units.

- Actual Flash Memory access is performed in word (32-bit) length units.

### 9.2.3 16-bit CPU mode:

- CPU reads and writes in half-word (16-bit) length units.

- Program execution from the Flash is not possible.

- Actual Flash Memory access is performed in word (16-bit) length units.

### 9.2.4 Flash Memory Mode (External Access to Flash Memory Enabled)

**Note**: The operation mode of the flash memory can be selected using a Boot-ROM function. The function start address is 0xBF60. The parameter description is given in the Hardware Manual in chapter 54.6 "Flash Access Mode Switching".

Document Number: 002-04608 Rev. \*A Page 39 of 126

# 9.3.1.2 Flash Memory Map MB91F466BA

| Addr                     |                             |                 |                   |        |             |               |                  |       |         |

|--------------------------|-----------------------------|-----------------|-------------------|--------|-------------|---------------|------------------|-------|---------|

| 0014:FFFFh<br>0014:C000h |                             | SA6             | (8KB)             |        |             | SA7           | (8KB)            |       |         |

| 0014:BFFFh<br>0014:8000h |                             | SA4             | (8KB)             |        | SA5 (8KB)   |               |                  |       | ROMS7   |

| 0014:7FFFh<br>0014:4000h |                             | SA2             | (8KB)             |        | SA3 (8KB)   |               |                  |       |         |

| 0014:3FFFh<br>0014:0000h |                             | SA0             | (8KB)             |        |             | SA1           | (8KB)            |       |         |

| 0013:FFFFh<br>0012:0000h |                             | SA22            | (64KB)            |        |             | SA23          | (64KB)           |       | ROMS6   |

| 0011:FFFFh<br>0010:0000h |                             | SA20            | (64KB)            |        | SA21 (64KB) |               |                  |       | ROIVISO |

| 000F:FFFFh<br>000E:0000h |                             | SA18            | (64KB)            |        | SA19 (64KB) |               |                  | ROMS5 |         |

| 000D:FFFFh<br>000C:0000h |                             | SA16            | (64KB)            |        | SA17 (64KB) |               |                  |       | ROMS4   |

| 000B:FFFFh<br>000A:0000h |                             | SA14            | (64KB)            |        | SA15 (64KB) |               |                  |       | ROMS3   |

| 0009:FFFFh<br>0008:0000h |                             | SA12            | (64KB)            |        | SA13 (64KB) |               |                  |       | ROMS2   |

| 0007:FFFFh<br>0006:0000h |                             | SA10            | (64KB)            |        | SA11 (64KB) |               |                  | ROMS1 |         |

| 0005:FFFFh<br>0004:0000h | SA8 (64KB)                  |                 |                   |        | SA9 (64KB)  |               |                  |       | ROMS0   |

| '                        | addr+0 addr+1 addr+2 addr+3 |                 |                   | addr+4 | addr+5      | addr+6        | addr+7           |       |         |

| 16bit read/write         | dat[31:16] dat[15:0]        |                 |                   | dat[3  | 1:16]       | dat[          | 15:0]            |       |         |

| 32bit read               | dat[31:0] dat[31:0]         |                 |                   |        |             |               |                  |       |         |

| 64bit read               |                             |                 |                   | dat[   | 63:0]       |               |                  |       |         |

| Legend                   | М                           | lemory not avai | lable in this are | a      |             | Memory availa | ble in this area |       |         |

# 9.3.2 Flash Access Timing Settings in CPU mode

The following tables list all settings for a given maximum Core Frequency (through the setting of CLKB or maximum clock modulation) for Flash read and write access.

### 9.3.2.1 Flash Read Timing Settings (Synchronous Read)

| Core clock (CLKB) | ATD | ALEH | EQ | WEXH | WTC | Remark                                    |

|-------------------|-----|------|----|------|-----|-------------------------------------------|

| to 24 MHz         | 0   | 0    | 0  | -    | 1   |                                           |

| to 48 MHz         | 0   | 0    | 1  | -    | 2   |                                           |

| to 96 MHz         | 1   | 1    | 3  | -    | 4   |                                           |

| to 100 MHz        | 1   | 1    | 3  | -    | 4   | not available on<br>MB91F467BA/MB91F466BA |

# 9.3.2.2 Flash Write Timing Settings (Synchronous Write)

|                   |     | <u> </u> |    |      |     |                                           |

|-------------------|-----|----------|----|------|-----|-------------------------------------------|

| Core clock (CLKB) | ATD | ALEH     | EQ | WEXH | WTC | Remark                                    |

| to 16 MHz         | 0   | -        | -  | 0    | 3   |                                           |

| to 32 MHz         | 0   | -        | -  | 0    | 4   |                                           |

| to 48 MHz         | 0   | -        | -  | 0    | 5   |                                           |

| to 64 MHz         | 1   | -        | -  | 0    | 6   |                                           |

| to 96 MHz         | 1   | -        | -  | 0    | 7   |                                           |

| to 100 MHz        | 1   | -        | -  | 0    | 7   | not available on<br>MB91F467BA/MB91F466BA |

Document Number: 002-04608 Rev. \*A Page 44 of 126

### MB91F465BB

### MB91F464BB

| FA[20:0]                 |             |            |  |  |  |  |  |

|--------------------------|-------------|------------|--|--|--|--|--|

| 001F:FFFFh<br>001F:0000h | SA19        | (64KB)     |  |  |  |  |  |

| 001E:FFFFh<br>001E:0000h | SA18        | (64KB)     |  |  |  |  |  |

| 001D:FFFFh<br>001D:0000h | SA17 (64KB) |            |  |  |  |  |  |

| 001C:FFFFh<br>001C:0000h | SA16 (64KB) |            |  |  |  |  |  |

| 001B:FFFFh<br>001B:0000h | SA15        | (64KB)     |  |  |  |  |  |

| 001A:FFFFh<br>001A:0000h | SA14        | (64KB)     |  |  |  |  |  |

| 0019:FFFFh<br>0019:0000h | SA13        | (64KB)     |  |  |  |  |  |

| 0018:FFFFh<br>0018:0000h | SA12        | (64KB)     |  |  |  |  |  |

|                          | SA11        | (64KB)     |  |  |  |  |  |

|                          | SA10        | (64KB)     |  |  |  |  |  |

|                          | SA9 (       | 64KB)      |  |  |  |  |  |

|                          | SA8 (       | 64KB)      |  |  |  |  |  |

| 0017:FFFFh<br>0017:E000h | SA7         | (8KB)      |  |  |  |  |  |

| 0017:DFFFh<br>0017:C000h | SA6         | (8KB)      |  |  |  |  |  |

| 0017:BFFFh<br>0017:A000h | SA5         | (8KB)      |  |  |  |  |  |

| 0017:9FFFh<br>0017:8000h | SA4         | (8KB)      |  |  |  |  |  |

|                          | SA3         | (8KB)      |  |  |  |  |  |

|                          | SA2         | (8KB)      |  |  |  |  |  |

|                          | SA1 (8KB)   |            |  |  |  |  |  |

|                          | SA0         | (8KB)      |  |  |  |  |  |

|                          | FA[1:0]=00  | FA[1:0]=10 |  |  |  |  |  |

| 16bit write mode         | DQ[15:0]    | DQ[15:0]   |  |  |  |  |  |

| . 13% milodo             | 2 %[10.0]   | 2 3 [10.0] |  |  |  |  |  |

| FA[20:0]                 |             |            |  |  |  |  |

|--------------------------|-------------|------------|--|--|--|--|

| 001F:FFFFh<br>001F:0000h | SA19        | (64KB)     |  |  |  |  |

| 001E:FFFFh<br>001E:0000h | SA18        | (64KB)     |  |  |  |  |

| 001D:FFFFh<br>001D:0000h | SA17 (64KB) |            |  |  |  |  |

| 001C:FFFFh<br>001C:0000h | SA16        | (64KB)     |  |  |  |  |

| 001B:FFFFh<br>001B:0000h | SA15        | (64KB)     |  |  |  |  |

| 001A:FFFFh<br>001A:0000h | SA14        | (64KB)     |  |  |  |  |

|                          | SA13        | (64KB)     |  |  |  |  |

|                          | SA12        | (64KB)     |  |  |  |  |

|                          | SA11        | (64KB)     |  |  |  |  |

|                          | SA10        | (64KB)     |  |  |  |  |

|                          | SA9 (       | 64KB)      |  |  |  |  |

|                          | SA8 (       | 64KB)      |  |  |  |  |

| 0017:FFFFh<br>0017:E000h | SA7         | (8KB)      |  |  |  |  |

| 0017:DFFFh<br>0017:C000h | SA6         | (8KB)      |  |  |  |  |

| 0017:BFFFh<br>0017:A000h | SA5         | (8KB)      |  |  |  |  |

| 0017:9FFFh<br>0017:8000h | SA4         | (8KB)      |  |  |  |  |

|                          | SA3         | (8KB)      |  |  |  |  |

|                          | SA2 (8KB)   |            |  |  |  |  |

|                          | SA1 (8KB)   |            |  |  |  |  |

|                          | SA0         | (8KB)      |  |  |  |  |

|                          | FA[1:0]=00  | FA[1:0]=10 |  |  |  |  |

| 16bit write mode         | DQ[15:0]    | DQ[15:0]   |  |  |  |  |

|                          |             |            |  |  |  |  |

Remark: Always keep FA[0] = 0 and FA[20] = 1

Legend

| Memory available in this area     |  |

|-----------------------------------|--|

| Memory not available in this area |  |

Remark: Always keep FA[0] = 0 and FA[20] = 1

Legend

| Memory available in this area     |

|-----------------------------------|

| Memory not available in this area |

# 10. Memory Space

The FR family has 4 Gbytes of logical address space (2<sup>32</sup> addresses) available to the CPU by linear access.

#### ■ Direct addressing area

The following address space area is used for I/O.

This area is called direct addressing area, and the address of an operand can be specified directly in an instruction.

The size of directly addressable area depends on the length of the data being accessed as shown below.

Byte data access:  $000_{\rm H}$  to  $0{\rm FF}_{\rm H}$  Half word access:  $000_{\rm H}$  to  $1{\rm FF}_{\rm H}$  Word data access:  $000_{\rm H}$  to  $3{\rm FF}_{\rm H}$

Document Number: 002-04608 Rev. \*A Page 53 of 126

| Address                                       |                             | Block                    |                             |                             |                                    |

|-----------------------------------------------|-----------------------------|--------------------------|-----------------------------|-----------------------------|------------------------------------|

|                                               | +0                          | +1                       | +2                          | +3                          |                                    |

| 000EC0 <sub>H</sub>                           | PPER00 [R/W]<br>00000000    | PPER01 [R/W]<br>00000000 | Rese                        | erved                       |                                    |

| 000EC4 <sub>H</sub>                           | Reserved                    | PPER05 [R/W]<br>000000   | PPER06 [R/W]<br>00000000    | PPER07 [R/W]<br>00000000    |                                    |

| 000EC8 <sub>H</sub>                           | PPER08 [R/W]<br>0 0 0       | PPER09 [R/W]<br>00       | PPER10 [R/W]<br>0           | Reserved                    |                                    |

| 000ECC <sub>H</sub>                           | Rese                        | rved                     | PPER14 [R/W]<br>00000000    | PPER15 [R/W]<br>00000000    | R-bus Port Pull-Up/Down Enable     |

| 000ED0 <sub>H</sub>                           | PPER16 [R/W]<br>00000000    | PPER17 [R/W]<br>00000000 | PPER18 [R/W]<br>- 000 - 000 | PPER19 [R/W]<br>- 000 - 000 | Register                           |

| 000ED4 <sub>H</sub>                           | PPER20 [R/W]<br>- 000 - 000 | PPER21 [R/W]<br>00       | PPER22 [R/W]<br>00000000    | PPER23 [R/W]<br>00000000    |                                    |

| 000ED8 <sub>H</sub>                           | PPER24 [R/W]<br>00000000    | Reserved                 | PPER26 [R/W]<br>00000000    | PPER27 [R/W]<br>00000000    |                                    |

| 000EDC <sub>H</sub>                           | PPER28 [R/W]<br>00000000    | PPER29 [R/W]<br>00000000 | Rese                        |                             |                                    |

| 000EE0 <sub>H</sub> to<br>000EFC <sub>H</sub> |                             | Rese                     | rved                        | Reserved                    |                                    |

| 000F00 <sub>H</sub>                           | PPCR00 [R/W]<br>11111111    | PPCR01 [R/W]<br>11111111 | Rese                        | erved                       |                                    |

| 000F04 <sub>H</sub>                           | Reserved                    | PPCR05 [R/W]<br>111111   | PPCR06 [R/W]<br>11111111    | PPCR07 [R/W]<br>11111111    |                                    |

| 000F08 <sub>H</sub>                           | PPCR08 [R/W]<br>1 1 1       | PPCR09 [R/W]<br>11       | PPCR10 [R/W]<br>1           | Reserved                    |                                    |

| 000F0C <sub>H</sub>                           | Rese                        | rved                     | PPCR14 [R/W]<br>00000000    | PPCR15 [R/W]<br>11111111    | R-bus Port                         |

| 000F10 <sub>H</sub>                           | PPCR16 [R/W]<br>00000000    | PPCR17 [R/W]<br>00000000 | PPCR18 [R/W]<br>- 111- 111  | PPCR19 [R/W]<br>- 111- 111  | – Pull-Up/Down Control<br>Register |

| 000F14 <sub>H</sub>                           | PPCR20 [R/W]<br>- 111- 111  | PPCR21 [R/W]             | PPCR22 [R/W]<br>11111111    | PPCR23 [R/W]<br>11111111    |                                    |

| 000F18 <sub>H</sub>                           | PPCR24 [R/W]<br>11111111    | Reserved                 | PPCR26 [R/W]<br>11111111    | PPCR27 [R/W]<br>11111111    |                                    |

| 000F1C <sub>H</sub>                           | PPCR28 [R/W]<br>11111111    | PPCR29 [R/W]<br>11111111 | Rese                        |                             |                                    |

| 000F20 <sub>H</sub> to<br>000F3C <sub>H</sub> |                             | Rese                     | rved                        | Reserved                    |                                    |

| Address                                       |                                                           | Block                                                             |                                     |                           |                        |  |

|-----------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------|---------------------------|------------------------|--|

|                                               | +0                                                        | +0 +1 +2 +3                                                       |                                     |                           |                        |  |

| 00C010 <sub>H</sub>                           |                                                           | IF1CREQ0 [R/W] IF1CMSK0 [R/W] 00000000 00000001 00000000 00000000 |                                     |                           |                        |  |

| 00C014 <sub>H</sub>                           | IF1MSK2<br>11111111                                       |                                                                   |                                     | SK10 [R/W]<br>I1 11111111 |                        |  |

| 00C018 <sub>H</sub>                           | IF1ARB2<br>00000000                                       |                                                                   |                                     | RB10 [R/W]<br>00 00000000 |                        |  |

| 00C01C <sub>H</sub>                           | IF1MCTR<br>00000000                                       |                                                                   | Re                                  | eserved                   |                        |  |

| 00C020 <sub>H</sub>                           | IF1DTA1<br>00000000                                       |                                                                   |                                     | FA20 [R/W]<br>00 00000000 | CAN 0                  |  |

| 00C024 <sub>H</sub>                           | IF1DTB1<br>00000000                                       |                                                                   |                                     | FB20 [R/W]<br>00 00000000 | IF 1 Register          |  |

| 00C028 <sub>H</sub><br>to 00C02C <sub>H</sub> |                                                           | Rese                                                              | rved                                |                           |                        |  |

| 00C030 <sub>H</sub>                           | IF1DTA2<br>00000000                                       |                                                                   | IF1D7<br>0000000                    |                           |                        |  |

| 00C034 <sub>H</sub>                           | IF1DTB20 [R/W] IF1DTB10 [R/W] 00000000 00000000 000000000 |                                                                   |                                     |                           |                        |  |

| 00C038 <sub>H</sub><br>to 00C03C <sub>H</sub> |                                                           | Reserved                                                          |                                     |                           |                        |  |

| 00C040 <sub>H</sub>                           | IF2CREQ<br>00000000                                       |                                                                   |                                     | MSK0 [R/W]<br>00 00000000 |                        |  |

| 00C044 <sub>H</sub>                           | IF2MSK2<br>11111111                                       |                                                                   |                                     | SK10 [R/W]<br>I1 11111111 | CAN 0<br>IF 2 Register |  |

| 00C048 <sub>H</sub>                           | IF2ARB2<br>00000000                                       |                                                                   | IF2ARB10 [R/W]<br>00000000 00000000 |                           |                        |  |

| 00C04C <sub>H</sub>                           | IF2MCTR<br>00000000                                       |                                                                   | Re                                  | eserved                   |                        |  |

| 00C050 <sub>H</sub>                           | IF2DTA1<br>00000000                                       |                                                                   |                                     | FA20 [R/W]<br>00 00000000 |                        |  |

| 00C054 <sub>H</sub>                           | IF2DTB1<br>00000000                                       |                                                                   |                                     | FB20 [R/W]<br>00 00000000 |                        |  |

| 00C058 <sub>H</sub><br>to 00C05C <sub>H</sub> |                                                           | Reserved                                                          |                                     |                           |                        |  |

| 00C060 <sub>H</sub>                           |                                                           | IF2DTA20 [R/W]                                                    |                                     |                           |                        |  |

| 00C064 <sub>H</sub>                           |                                                           | IF2DTB20 [R/W]                                                    |                                     |                           |                        |  |

| 00C068 <sub>H</sub><br>to 00C07C <sub>H</sub> |                                                           | Reserved                                                          |                                     |                           |                        |  |

| Address                                       |                                                                                                                   | Block |                                     |                         |                    |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------|-------------------------|--------------------|--|--|

|                                               | +0                                                                                                                | +1    | +2                                  | +3                      |                    |  |  |

| 00C140 <sub>H</sub>                           | IF2CREQ<br>00000000                                                                                               |       |                                     | SK1 [R/W]<br>0 00000000 |                    |  |  |

| 00C144 <sub>H</sub>                           | IF2MSK2<br>11111111                                                                                               |       | IF2MSK11 [R/W]<br>11111111 11111111 |                         |                    |  |  |

| 00C148 <sub>H</sub>                           | IF2ARB21 [R/W] 00000000 00000000  IF2MCTR1 [R/W] 00000000 00000000                                                |       | IF2ARB11 [R/W]<br>00000000 00000000 |                         |                    |  |  |

| 00C14C <sub>H</sub>                           |                                                                                                                   |       | Re                                  | served                  |                    |  |  |

| 00C150 <sub>H</sub>                           | IF2DTA1<br>00000000                                                                                               |       |                                     | A21 [R/W]<br>0 00000000 | CAN 1              |  |  |

| 00C154 <sub>H</sub>                           | IF2DTB11 [R/W]<br>00000000 00000000                                                                               |       |                                     | B21 [R/W]<br>0 00000000 | IF 2 Register      |  |  |

| 00C158 <sub>H</sub><br>to 00C15C <sub>H</sub> |                                                                                                                   | Rese  | erved                               |                         |                    |  |  |

| 00C160 <sub>H</sub>                           | IF2DTA2<br>00000000                                                                                               |       |                                     | A11 [R/W]<br>0 00000000 |                    |  |  |

| 00C164 <sub>H</sub>                           | IF2DTB2<br>00000000                                                                                               |       | IF2DTB11 [R/W]<br>00000000 00000000 |                         |                    |  |  |

| 00C168 <sub>H</sub><br>to 00C17C <sub>H</sub> |                                                                                                                   |       |                                     |                         |                    |  |  |

| 00C180 <sub>H</sub>                           | TREQR21 [R] TREQR11 [R] 00000000 00000000 00000000                                                                |       |                                     |                         |                    |  |  |

| 00C184 <sub>H</sub> to<br>00C18C <sub>H</sub> | Rese                                                                                                              | ved   | Reserved                            |                         |                    |  |  |

| 00C190 <sub>H</sub>                           | NEWDT21 [R] 00000000 00000000  Reserved  INTPND21 [R] 00000000 00000000  Reserved  MSGVAL21 [R] 00000000 00000000 |       | NEWDT11 [R]<br>00000000 00000000    |                         |                    |  |  |

| 00C194 <sub>H</sub> to<br>00C19C <sub>H</sub> |                                                                                                                   |       | Res                                 | served                  | CAN 1 Status Flags |  |  |

| 00C1A0 <sub>H</sub>                           |                                                                                                                   |       |                                     | ND11 [R]<br>0 00000000  |                    |  |  |

| 00C1A4 <sub>H</sub> to<br>00C1AC <sub>H</sub> |                                                                                                                   |       | Res                                 | served                  |                    |  |  |

| 00C1B0 <sub>H</sub>                           |                                                                                                                   |       | MSGVAL11 [R]<br>00000000 00000000   |                         |                    |  |  |

| 00C1B4 <sub>H</sub> to<br>00C1FC <sub>H</sub> | Rese                                                                                                              | rved  | Res                                 | served                  |                    |  |  |

| 00C200 <sub>H</sub>                           | CTRLR2<br>00000000                                                                                                |       |                                     | R2 [R/W]                |                    |  |  |

| 00C204 <sub>H</sub>                           | 00C204 <sub>H</sub>                                                                                               |       | BTR2 [R/W]<br>00100011 00000001     |                         | CAN 2              |  |  |

| 00C208 <sub>H</sub>                           |                                                                                                                   |       |                                     | R2 [R/W]<br>) X0000000  | Control Register   |  |  |

| 00C20C <sub>H</sub>                           | BRPE2<br>00000000                                                                                                 |       | CBSYNC2                             |                         |                    |  |  |

| Address                                          |                                     | Block                                                    |                                     |                                     |                           |  |

|--------------------------------------------------|-------------------------------------|----------------------------------------------------------|-------------------------------------|-------------------------------------|---------------------------|--|

|                                                  | +0                                  | +1                                                       | +2                                  | +3                                  |                           |  |

| 00C510 <sub>H</sub>                              |                                     | Q5 [R/W]<br>00000001                                     |                                     | K5 [R/W]<br>00000000                |                           |  |

| 00C514 <sub>H</sub>                              |                                     | 25 [R/W]<br>11111111                                     |                                     | (15 [R/W]<br>11111111               |                           |  |

| 00C518 <sub>H</sub>                              |                                     | 25 [R/W]<br>00000000                                     |                                     | IF1ARB15 [R/W]<br>00000000 00000000 |                           |  |

| 00C51C <sub>H</sub>                              |                                     | R5 [R/W]<br>00000000                                     | Res                                 | Reserved                            |                           |  |

| 00C520 <sub>H</sub>                              |                                     | 15 [R/W]<br>00000000                                     |                                     | 25 [R/W]<br>00000000                | CAN 5 IF 1 Register       |  |

| 00C524 <sub>H</sub>                              |                                     | 15 [R/W]<br>00000000                                     |                                     | IF1DTB25 [R/W]<br>00000000 00000000 |                           |  |

| 00C528 <sub>H</sub><br>to<br>00C52C <sub>H</sub> |                                     | Res                                                      | served                              |                                     | MB91F465BB/MB91F464<br>BB |  |

| 00C530 <sub>H</sub>                              |                                     | 25 [R/W]<br>00000000                                     |                                     | .15 [R/W]<br>00000000               |                           |  |

| 00C534 <sub>H</sub>                              |                                     | 25 [R/W]<br>00000000                                     | IF1DTB15 [R/W]<br>00000000 00000000 |                                     |                           |  |

| 00C538 <sub>H</sub><br>to<br>00C53C <sub>H</sub> |                                     | Res                                                      |                                     |                                     |                           |  |

| 00C540 <sub>H</sub>                              |                                     | F2CREQ5 [R/W] IF2CMSK5 [R/W] 0000000 000000000 000000000 |                                     |                                     |                           |  |

| 00C544 <sub>H</sub>                              |                                     | IF2MSK25 [R/W]<br>11111111 11111111                      |                                     | (15 [R/W]<br>11111111               |                           |  |

| 00C548 <sub>H</sub>                              | IF2ARB25 [R/W]<br>00000000 00000000 |                                                          |                                     | 15 [R/W]<br>00000000                |                           |  |

| 00C54C <sub>H</sub>                              |                                     | R5 [R/W]<br>00000000                                     | Res                                 | erved                               |                           |  |

| 00C550 <sub>H</sub>                              | IF2DTA15 [R/W]<br>00000000 00000000 |                                                          |                                     | 25 [R/W]<br>00000000                | CAN 5<br>IF 2 Register    |  |

| 00C554 <sub>H</sub>                              | IF2DTB15 [R/W]<br>00000000 00000000 |                                                          |                                     | 25 [R/W]<br>00000000                | Note: Not on              |  |

| 00C558 <sub>H</sub><br>to<br>00C55C <sub>H</sub> |                                     | Reserved                                                 |                                     |                                     | MB91F465BB/MB91F464<br>BB |  |

| 00C560 <sub>H</sub>                              |                                     | 25 [R/W]<br>00000000                                     |                                     | .15 [R/W]<br>00000000               |                           |  |

| 00C564 <sub>H</sub>                              |                                     | DTB25 [R/W] IF2DTB15 [R/W] 000 00000000 0000000          |                                     |                                     |                           |  |

| 00C568 <sub>H</sub><br>to<br>00C57C <sub>H</sub> |                                     | Reserved                                                 |                                     |                                     |                           |  |

| Address                                          |                                                    | Block                                                |        |                      |                                         |

|--------------------------------------------------|----------------------------------------------------|------------------------------------------------------|--------|----------------------|-----------------------------------------|

|                                                  | +0                                                 | +1                                                   | +2     | +3                   |                                         |

| 00C580 <sub>H</sub>                              | TREQR25 [R] TREQR15 [R] 00000000 00000000 00000000 |                                                      |        |                      |                                         |

| 00C584 <sub>H</sub> to<br>00C58C <sub>H</sub>    |                                                    |                                                      |        |                      |                                         |

| 00C590 <sub>H</sub>                              | NEWD<br>00000000                                   |                                                      |        | 0T15 [R]<br>00000000 |                                         |

| 00C594 <sub>H</sub> to<br>00C59C <sub>H</sub>    |                                                    | Reserved                                             |        |                      | CAN 5<br>Status Flags                   |

| 00C5A0 <sub>H</sub>                              | INTPNI<br>00000000                                 |                                                      |        | D15 [R]<br>00000000  | <b>Note:</b> Not on MB91F465BB/MB91F464 |

| 00C5A4 <sub>H</sub> to<br>00C5AC <sub>H</sub>    |                                                    | Reserved                                             |        |                      | BB                                      |

| 00C5B0 <sub>H</sub>                              |                                                    | MSGVAL25 [R] MSGVAL15 [R] 00000000 00000000 00000000 |        |                      |                                         |

| 00C5B4 <sub>H</sub><br>to<br>00EFFC <sub>H</sub> |                                                    | Reserved                                             |        |                      |                                         |

| 00F000 <sub>H</sub>                              | BCTRL [R/W]                                        |                                                      |        |                      |                                         |

| 00F004 <sub>H</sub>                              | -                                                  | BSTAT [R/W]<br>000 00000000 10000000                 |        |                      |                                         |

| 00F008 <sub>H</sub>                              |                                                    | BIAC [R]                                             |        |                      |                                         |

| 00F00C <sub>H</sub>                              |                                                    | BOAC [R]                                             |        |                      |                                         |

| 00F010 <sub>H</sub>                              |                                                    | EDSU / MPU                                           |        |                      |                                         |

| 00F014 <sub>H</sub><br>to 00F01C <sub>H</sub>    | Reserved                                           |                                                      |        |                      | EDSO / INIFO                            |

| 00F020 <sub>H</sub>                              | BCR0 [R/W]<br>00000000 00000000 00000000           |                                                      |        |                      |                                         |

| 00F024 <sub>H</sub>                              | BCR1 [R/W]<br>00000000 00000000 00000000           |                                                      |        |                      |                                         |

| 00F028 <sub>H</sub>                              | BCR2 [R/W]<br>00000000 00000000 00000000           |                                                      |        |                      |                                         |

| 00F02C <sub>H</sub>                              |                                                    |                                                      |        |                      |                                         |

| 00F030 <sub>H</sub> to<br>00F07C <sub>H</sub>    |                                                    | Re                                                   | served |                      | Reserved                                |

| Modulation<br>Degree<br>(k) | Random No<br>(N) | CMPR<br>[hex] | Baseclk<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz] |

|-----------------------------|------------------|---------------|------------------|---------------|---------------|

| 9                           | 3                | 1267          | 36               | 22.8          | 85.8          |

| 1                           | 3                | 026F          | 32               | 29.7          | 34.7          |

| 1                           | 5                | 02AE          | 32               | 28            | 37.3          |

| 1                           | 7                | 02ED          | 32               | 26.6          | 40.2          |

| 1                           | 9                | 032C          | 32               | 25.3          | 43.6          |

| 1                           | 11               | 036B          | 32               | 24.1          | 47.7          |

| 1                           | 13               | 03AA          | 32               | 23            | 52.5          |

| 1                           | 15               | 03E9          | 32               | 22            | 58.6          |

| 2                           | 3                | 046E          | 32               | 28            | 37.3          |

| 2                           | 5                | 04AC          | 32               | 25.3          | 43.6          |

| 2                           | 7                | 04EA          | 32               | 23            | 52.5          |

| 2                           | 9                | 0528          | 32               | 21.1          | 66.1          |

| 2                           | 11               | 0566          | 32               | 19.5          | 89.1          |

| 3                           | 3                | 066D          | 32               | 26.6          | 40.2          |

| 3                           | 5                | 06AA          | 32               | 23            | 52.5          |

| 3                           | 7                | 06E7          | 32               | 20.3          | 75.9          |

| 4                           | 3                | 086C          | 32               | 25.3          | 43.6          |

| 4                           | 5                | 08A8          | 32               | 21.1          | 66.1          |

| 5                           | 3                | 0A6B          | 32               | 24.1          | 47.7          |

| 5                           | 5                | 0AA6          | 32               | 19.5          | 89.1          |

| 6                           | 3                | 0C6A          | 32               | 23            | 52.5          |

| 7                           | 3                | 0E69          | 32               | 22            | 58.6          |

| 8                           | 3                | 1068          | 32               | 21.1          | 66.1          |

| 9                           | 3                | 1267          | 32               | 20.3          | 75.9          |

| 10                          | 3                | 1466          | 32               | 19.5          | 89.1          |

- 4. Maximum output current is defined as the value of the peak current flowing through any one of the corresponding pins.

- 5. Average output current is defined as the value of the average current flowing through any one of the corresponding pins for a 100 ms period.

- 6. Total average output current is defined as the value of the average current flowing through all of the corresponding pins for a 100 ms period.

- 7. The maximum permitted power dissipation depends onm the ambient temperature, the air flow velocity and the thermal conductance of the package on the PCB.

The actual power dissipation depends on the customer application and can be calculated as follows:

$P_D = P_{IO} + P_{INT}$

- $P_{IO} = \Sigma (V_{OL} * I_{OL} + V_{OH} + I_{OH})$  (IO load power dissipation, sum is performed on all IO ports)  $P_{INT} = V_{DD}5R * I_{CC} + AV_{CC}5 * I_A + AVRH5 * I_R$  (internal power dissipation) 8. Worst case value for the QFP package mounted on a 4-layer PCB at specified  $T_A$  without air flow.

- 9. Please contact Fujitsu for reliability limitations when using under these conditions.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

Document Number: 002-04608 Rev. \*A Page 99 of 126

| Parameter                                   | Symbol          | Pin name           | Value                     |     |                           | Unit  | Remarks                        |

|---------------------------------------------|-----------------|--------------------|---------------------------|-----|---------------------------|-------|--------------------------------|

| Farameter                                   |                 |                    | Min                       | Тур | Max                       | Oilit | Remarks                        |

| Reference voltage range                     | AVRH            | AVRH5              | 0.75 × AV <sub>CC</sub> 5 | -   | AV <sub>CC</sub> 5        | V     |                                |

|                                             | AVRL            | AV <sub>SS</sub> 5 | AV <sub>SS</sub> 5        | -   | AV <sub>CC</sub> 5 × 0.25 | V     |                                |

| Power supply current per ADC macro [3]      | I <sub>A</sub>  | AV <sub>CC</sub> 5 | -                         | 2.5 | 5                         | mA    | A/D Converter active           |

|                                             | I <sub>AH</sub> | AV <sub>CC</sub> 5 | -                         | -   | 5                         | μΑ    | A/D Converter not operated [1] |

| Reference voltage current per ADC macro [3] | I <sub>R</sub>  | AVRH5              | -                         | 0.7 | 1                         | mA    | A/D Converter active           |

|                                             | I <sub>RH</sub> | AVRH5              | -                         | -   | 5                         | μA    | A/D Converter not operated [2] |

<sup>1.</sup> Supply current at  $AV_{CC}5$ , if A/D converter and ALARM comparator are not operating,  $(V_{DD}5 = AV_{CC}5 = AVRH = 5.0 \text{ V})$

### Sampling Time Calculation

$$T_{samp}$$

= ( 2.6 kOhm + R<sub>EXT</sub>) × 11pF × 7; for 4.5V ≤ AV<sub>CC</sub>5 ≤ 5.5V  $T_{samp}$  = (12.1 kOhm + R<sub>EXT</sub>) × 11pF × 7; for 3.0V ≤ AV<sub>CC</sub>5 ≤ 4.5V

#### **Conversion Time Calculation**

$$T_{conv} = T_{samp} + T_{comp}$$

### 15.4.1 Definition of A/D Converter Terms

#### ■ Resolution

Analog variation that is recognizable by the A/D converter.

#### ■ Nonlinearity error

Deviation between actual conversion characteristics and a straight line connecting the zero transition point (00 0000  $0000_B \leftrightarrow 00\ 0000\ 0001_B$ ) and the full scale transition point (11 1111  $1111_B \leftrightarrow 11\ 1111\ 1111_B$ ).

#### ■ Differential nonlinearity error

Deviation of the input voltage from the ideal value that is required to change the output code by 1 LSB.

#### ■ Total error

This error indicates the difference between actual and theoretical values, including the zero transition error, full scale transition error, and nonlinearity error.

<sup>2.</sup> Input current at AVRH5, if A/D converter is not operating,  $(V_{DD}5 = AV_{CC}5 = AVRH = 5.0 \text{ V})$

<sup>3.</sup> The current consumption per ADC macro is given here. On devices having more then one A/D converter, the current values have to be multiplied by the number of macros.

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/usb

cypress.com/wireless

#### **Products**

**USB Controllers**

Wireless/RF

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc Touch Sensing cypress.com/touch

### PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | Projects | Video | Blogs | Training | Components

### **Technical Support**

cypress.com/support

ARM and Cortex are the trademarks of ARM Limited in the EU and other countries

© Cypress Semiconductor Corporation 2009-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.