# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 266MHz                                                                  |

| Co-Processors/DSP               | · .                                                                     |

| RAM Controllers                 | SDRAM                                                                   |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | Keypad, LCD                                                             |

| Ethernet                        | ·                                                                       |

| SATA                            | -                                                                       |

| USB                             | USB 1.x (2)                                                             |

| Voltage - I/O                   | 1.8V, 3.0V                                                              |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                       |

| Security Features               | -                                                                       |

| Package / Case                  | 289-LFBGA                                                               |

| Supplier Device Package         | 289-LFBGA (14x14)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9328mx21cvkr2 |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Order Number | Package Size | Package Type | Operating Range |  |

|-------------------|--------------|--------------|-----------------|--|

| Introduction      | U            | 0 71         |                 |  |

| MC9328MX21DVK! | 289-lead MAPBGA<br>0.65mm, 14mm x 14mm | Lead-free | -30°C–70°C |

|----------------|----------------------------------------|-----------|------------|

| MC9328MX21DVM! | 289-lead MAPBGA<br>0.8mm, 17mm x 17mm  | Lead-free | -30°C–70°C |

| MC9328MX21CVK! | 289-lead MAPBGA<br>0.65mm, 14mm x 14mm | Lead-free | -40°C–85°C |

| MC9328MX21CVM! | 289-lead MAPBGA<br>0.8mm, 17mm x 17mm  | Lead-free | -40°C–85°C |

| MC9328MX21CJM  | 289-lead MAPBGA<br>0.8mm, 17mm x 17mm  | Lead-free | -40°C–85°C |

### 1.5 Features

The i.MX21 boasts a robust array of features that can support a wide variety of applications. Below is a brief description of i.MX21 features.

- ARM926EJ-S Core Complex

- enhanced Multimedia Accelerator (eMMA)

- Display and Video Modules

- LCD Controller (LCDC)

- Smart LCD Controller (SLCDC)

- CMOS Sensor Interface (CSI)

- Bus Master Interface (BMI)

- Wireless Connectivity

- Fast Infra-Red Interface (FIRI)

- Wired Connectivity

- USB On-The-Go (USBOTG) Controller

- Four Universal Asynchronous Receiver/Transmitters (UARTx)

- Three Configurable Serial Peripheral Interfaces (CSPIx) for High Speed Data Transfer

- Inter-IC  $(I^2C)$  Bus Module

- Two Synchronous Serial Interfaces (SSI) with Inter-IC Sound  $(I^2S)$

- Digital Audio Mux

- One-Wire Controller

- Keypad Interface

- Memory Expansion and I/O Card Support

- Two Multimedia Card and Secure Digital (MMC/SD) Host Controller Modules

- Memory Interface

- External Interface Module (EIM)

- SDRAM Controller (SDRAMC)

- NAND Flash Controller (NFC)

- PCMCIA/CF Interface

- Standard System Resources

- Clock Generation Module (CGM) and Power Control Module

- Three General-Purpose 32-Bit Counters/Timers

- Watchdog Timer

- Real-Time Clock/Sampling Timer (RTC)

- Pulse-Width Modulator (PWM) Module

- Direct Memory Access Controller (DMAC)

- General-Purpose I/O (GPIO) Ports

- Debug Capability

# 2 Signal Descriptions

Table 2 identifies and describes the i.MX21 signals. Pin assignment is provided in Section 4, "Pin Assignment and Package Information" and in the "Signal Multiplexing Scheme" table within the reference manual.

The connections of the pins in Table 2 depends solely upon the user application, however there are a few factory test signals that are not used in a normal application. Following is a list of these signals and how they are to be terminated for proper operation of the i.MX21 processor:

- CLKMODE[1:0]: To ensure proper operation, leave these signals as no connects.

- OSC26M\_TEST: To ensure proper operation, leave this signal as no connect.

- EXT\_48M: To ensure proper operation, connect this signal to ground.

- EXT\_266M: To ensure proper operation, connect this signal to ground.

- TEST\_WB[2:0]: These signals are also multiplexed with GPIO PORT E as well as alternate keypad signals. If not utilizing these signals for GPIO functionality or for their other multiplexed function, then configure as GPIO input with pull up enabled, and leave as a no connect.

- TEST\_WB[4:3]: To ensure proper operation, leave these signals as no connects.

| Signal Name | Function/Notes                                                                                          |  |  |

|-------------|---------------------------------------------------------------------------------------------------------|--|--|

|             | External Bus/Chip Select (EIM)                                                                          |  |  |

| A [25:0]    | Address bus signals                                                                                     |  |  |

| D [31:0]    | Data bus signals                                                                                        |  |  |

| EB0         | MSB Byte Strobe—Active low external enable byte signal that controls D [31:24], shared with SDRAM DQM0. |  |  |

### Table 2. i.MX21 Signal Descriptions

| Signal Name   | Function/Notes                                                                                                                                                                                |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PC_RST        | PCMCIA Reset output signal. This signal is multiplexed with NFRB signal of NF.                                                                                                                |  |

| PC_OE         | PCMCIA Memory Read Enable output signal asserted during common or attribute memory read cyc<br>This signal is multiplexed with NFALE signal of NF.                                            |  |

| PC_WE         | PCMCIA Memory Write Enable output signal asserted during common or attribute memory cycles. This signal is shared with RW of the EIM.                                                         |  |

| PC_VS1        | PCMCIA Voltage Sense1 input signal. This signal is multiplexed with NFIO[2] signal of NF.                                                                                                     |  |

| PC_VS2        | PCMCIA Voltage Sense2 input signal. This signal is multiplexed with NFIO[1] signal of NF.                                                                                                     |  |

| PC_BVD1       | PCMCIA Battery Voltage Detect1 input signal. This signal is multiplexed with NFIO[0] signal of NF.                                                                                            |  |

| PC_BVD2       | PCMCIA Battery Voltage Detect2 input signal. This signal is multiplexed with NF_WE signal of NF.                                                                                              |  |

| PC_SPKOUT     | PCMCIA Speaker Out output signal. This signal is multiplexed with PWMO signal.                                                                                                                |  |

| PC_REG        | PCMCIA Register Select output signal. This signal is shared with $\overline{\text{EB2}}$ of EIM.                                                                                              |  |

| PC_CE1        | PCMCIA Card Enable1 output signal. This signal is multiplexed with NFCE signal of NF.                                                                                                         |  |

| PC_CE2        | PCMCIA Card Enable2 output signal. This signal is multiplexed with NFWP signal of NF.                                                                                                         |  |

| PC_IORD       | PCMCIA IO Read output signal. This signal is shared with EB3 of EIM.                                                                                                                          |  |

| PC_IOWR       | PCMCIA IO Write output signal. This signal is shared with $\overline{OE}$ signal of EIM.                                                                                                      |  |

| PC_WP         | PCMCIA Write Protect input signal. This signal is multiplexed with NFIO[3] signal of NF.                                                                                                      |  |

| PC_POE        | PCMCIA Output Enable signal to enable voltage translation buffers and transceivers. This signal is multiplexed with NFCLE signal of NF.                                                       |  |

| PC_RW         | PCMCIA Read Write output signal to control external transceiver direction. Asserted high for read access and negated low for write access. This signal is multiplexed with NFRE signal of NF. |  |

| PC_PWRON      | PCMCIA input signal to indicate that the card power has been applied and stabilized.                                                                                                          |  |

|               | CSPI                                                                                                                                                                                          |  |

| CSPI1_MOSI    | Master Out/Slave In signal                                                                                                                                                                    |  |

| CSPI1_MISO    | Master In/Slave Out signal                                                                                                                                                                    |  |

| CSPI1_SS[2:0] | Slave Select (Selectable polarity) signal. CSPI1_SS2 is also multiplexed with USBG_RXDAT and CSPI1_SS1 is multiplexed with EXT_DMAGRANT.                                                      |  |

| CSPI1_SCLK    | Serial Clock signal                                                                                                                                                                           |  |

| CSPI1_RDY     | Serial Data Ready signal. Also multiplexed with EXT_DMAREQ.                                                                                                                                   |  |

| CSPI2_MOSI    | Master Out/Slave In signal. This signal is multiplexed with USBH2_TXDP signal of USB OTG.                                                                                                     |  |

| CSPI2_MISO    | Master In/Slave Out signal. This signal is multiplexed with USBH2_TXDM signal of USB OTG.                                                                                                     |  |

| CSPI2_SS[2:0] | Slave Select (Selectable polarity) signals. These signals are multiplexed with USBH2_FS, USBH2_RXDP and USBH2_RXDM signal of USB OTG                                                          |  |

| CSPI2_SCLK    | Serial Clock signal. This signal is multiplexed with USBH2_OE signal of USB OTG                                                                                                               |  |

| CSPI3_MOSI    | Master Out/Slave In signal. This signal is multiplexed with SD1_CMD.                                                                                                                          |  |

| CSPI3_MISO    | Master In/Slave Out signal. This signal is multiplexed with SD1_D0.                                                                                                                           |  |

| CSPI3_SS      | Slave Select (Selectable polarity) signal multiplexed with SD1_D3.                                                                                                                            |  |

| CSPI3_SCLK    | Serial Clock signal. This signal is multiplexed with SD1_CLK.                                                                                                                                 |  |

### Table 2. i.MX21 Signal Descriptions (Continued)

| Table 2. i.MX21 Signal | Descriptions (Continued) |

|------------------------|--------------------------|

|------------------------|--------------------------|

| Signal Name  | Function/Notes                                                                                                                                                                                                                                                       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USBH2_FS     | USB Host2 Full Speed output signal. This signal is multiplexed with CSPI2_SS[0] of CSPI2.                                                                                                                                                                            |

| USBG_SCL     | USB OTG I <sup>2</sup> C Clock input/output signal. This signal is multiplexed with SLCDC1_DAT8.                                                                                                                                                                     |

| USBG_SDA     | USB OTG I <sup>2</sup> C Data input/output signal. This signal is multiplexed with SLCDC1_DAT7.                                                                                                                                                                      |

| USBG_TXR_INT | USB OTG transceiver interrupt input. Multiplexed with USBG_FS.                                                                                                                                                                                                       |

|              | Secure Digital Interface                                                                                                                                                                                                                                             |

| SD1_CMD      | SD Command bidirectional signal—If the system designer does not want to make use of the internal pull-<br>up, via the Pull-up enable register, a 4.7k–69k external pull-up resistor must be added. This signal is<br>multiplexed with CSPI3_MOSI.                    |

| SD1_CLK      | SD Output Clock. This signal is multiplexed with CSPI3_SCLK.                                                                                                                                                                                                         |

| SD1_D[3:0]   | SD Data bidirectional signals—If the system designer does not want to make use of the internal pull-up, via the Pull-up enable register, a 50k–69k external pull-up resistor must be added. SD1_D[3] is muxed with CSPI3_SS while SD1_D[0] is muxed with CSPI3_MISO. |

| SD2_CMD      | SD Command bidirectional signal. This signal is multiplexed with SLCDC1_CS signal from SLCDC1.                                                                                                                                                                       |

| SD2_CLK      | SD Output Clock signal. This signal is multiplexed with SLCDC1_CLK signal from SLCDC1.                                                                                                                                                                               |

| SD2_D[3:0]   | SD Data bidirectional signals. SD2_D[3:2] are multiplexed with SLCDC1_RS and SLCDC_D0 signals from SLCDC1.                                                                                                                                                           |

|              | UARTs – IrDA/Auto-Bauding                                                                                                                                                                                                                                            |

| UART1_RXD    | Receive Data input signal                                                                                                                                                                                                                                            |

| UART1_TXD    | Transmit Data output signal                                                                                                                                                                                                                                          |

| UART1_RTS    | Request to Send input signal                                                                                                                                                                                                                                         |

| UART1_CTS    | Clear to Send output signal                                                                                                                                                                                                                                          |

| UART2_RXD    | Receive Data input signal. This signal is multiplexed with KP_ROW6 signal from KPP.                                                                                                                                                                                  |

| UART2_TXD    | Transmit Data output signal. This signal is multiplexed with KP_COL6 signal from KPP.                                                                                                                                                                                |

| UART2_RTS    | Request to Send input signal. This signal is multiplexed with KP_ROW7 signal from KPP.                                                                                                                                                                               |

| UART2_CTS    | Clear to Send output signal. This signal is multiplexed with KP_COL7 signal from KPP.                                                                                                                                                                                |

| UART3_RXD    | Receive Data input signal. This signal is multiplexed with IR_RXD from FIRI.                                                                                                                                                                                         |

| UART3_TXD    | Transmit Data output signal. This signal is multiplexed with IR_TXD from FIRI.                                                                                                                                                                                       |

| UART3_RTS    | Request to Send input signal                                                                                                                                                                                                                                         |

| UART3_CTS    | Clear to Send output signal                                                                                                                                                                                                                                          |

| UART4_RXD    | Receive Data input signal which is multiplexed with USBH1_RXDP and USBH1_TXDP.                                                                                                                                                                                       |

| UART4_TXD    | Transmit Data output signal which is multiplexed with USBH1_TXDM.                                                                                                                                                                                                    |

| UART4_RTS    | Request to Send input signal which is multiplexed with USBH1_FS and USBH1_RXDP.                                                                                                                                                                                      |

| UART4_CTS    | Clear to Send output signal which is multiplexed with USBH1_TXDP and USBH1_RXDM.                                                                                                                                                                                     |

|              | Serial Audio Port – SSI (configurable to I <sup>2</sup> S protocol and AC97)                                                                                                                                                                                         |

| SSI1_CLK     | Serial clock signal which is output in master or input in slave                                                                                                                                                                                                      |

| SSI1_TXD     | Transmit serial data                                                                                                                                                                                                                                                 |

| SSI1_RXD     | Receive serial data                                                                                                                                                                                                                                                  |

| SSI1_FS      | Frame Sync signal which is output in master and input in slave                                                                                                                                                                                                       |

### **Signal Descriptions**

| Table 2. i.MX21 Si | ignal Descriptions | (Continued) |

|--------------------|--------------------|-------------|

|--------------------|--------------------|-------------|

| Signal Name | Function/Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS_CLK1    | SSI1 master clock. Multiplexed with TOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SSI2_CLK    | Serial clock signal which is output in master or input in slave.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SSI2_TXD    | Transmit serial data signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SSI2_RXD    | Receive serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SSI2_FS     | Frame Sync signal which is output in master and input in slave.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SYS_CLK2    | SSI2 master clock. Multiplexed with TOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SSI3_CLK    | Serial clock signal which is output in master or input in slave. Multiplexed with SLCDC2_CLK                                                                                                                                                                                                                                                                                                                                                                                                |

| SSI3_TXD    | Transmit serial data signal which is multiplexed with SLCDC2_CS                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SSI3_RXD    | Receive serial data which is multiplexed with SLCDC2_RS                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SSI3_FS     | Frame Sync signal which is output in master and input in slave. Multiplexed with SLCDC2_D0.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SAP_CLK     | Serial clock signal which is output in master or input in slave.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SAP_TXD     | Transmit serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SAP_RXD     | Receive serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SAP_FS      | Frame Sync signal which is output in master and input in slave.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | l <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| I2C_CLK     | I <sup>2</sup> C Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I2C_DATA    | I <sup>2</sup> C Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | 1-Wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OWIRE       | 1-Wire input and output signal. This signal is multiplexed with JTAG RTCK.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PWMO        | PWM Output. This signal is multiplexed with PC_SPKOUT of PCMCIA, as well as TOUT2 and TOUT3 of the General Purpose Timer module.                                                                                                                                                                                                                                                                                                                                                            |

|             | General Purpose Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PF[16]      | Dedicated GPIO. When unused, program this signal as an input with the on-chip pull-up resistor enabled.                                                                                                                                                                                                                                                                                                                                                                                     |

|             | Keypad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| KP_COL[7:0] | Keypad Column selection signals. KP_COL[7:6] are multiplexed with UART2_CTS and UART2_TXD respectively. Alternatively, KP_COL6 is also available on the internal factory test signal TEST_WB2. The Function Multiplexing Control Register in the System Control chapter must be used in conjunction with programming the GPIO multiplexing (to select the alternate signal multiplexing) to choose which signal KP_COL6 is available.                                                       |

| KP_ROW[7:0] | Keypad Row selection signals. KP_ROW[7:6] are multiplexed with UART2_RTS and UART2_RXD signals respectively. Alternatively, KP_ROW7 and KP_ROW6 are available on the internal factory test signals TEST_WB0 and TEST_WB1 respectively. The Function Multiplexing Control Register in the System Control chapter must be used in conjunction with programming the GPIO multiplexing (to select the alternate signal multiplexing) to choose which signals KP_ROW6 and KP_ROW7 are available. |

|             | Noisy Supply Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NVDD        | Noisy Supply for the I/O pins. There are six (6) I/O voltages, NVDD1 through NVDD6.                                                                                                                                                                                                                                                                                                                                                                                                         |

| NVSS        | Noisy Ground for the I/O pins                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

For more information about I/O pads grouping per VDD, please refer to Table 4.

| Rating                                   |                 | Symbol            | Minimum | Maximum | Unit |

|------------------------------------------|-----------------|-------------------|---------|---------|------|

| Operating temperature range              | Part No. Suffix |                   |         |         | 1    |

|                                          | VK, VM          | T <sub>A</sub>    | 0       | 70      | °C   |

|                                          | DVK, DVM        | T <sub>A</sub>    | -30     | 70      | °C   |

|                                          | CVK, CVM        | T <sub>A</sub>    | - 40    | 85      | °C   |

| I/O supply voltage NVDD 1–6              |                 | NVDD <sub>x</sub> | 1.70    | 3.30    | V    |

| Internal supply voltage (Core = 266 MHz) |                 | QVDD, QVDDx       | 1.45    | 1.65    | V    |

| Analog supply voltage                    |                 | VDDA              | 1.70    | 3.30    | V    |

### Table 4. 266 MHz Recommended Operating Range

### 3.3 DC Electrical Characteristics

Table 5 contains the DC characteristics of the i.MX21.

**Table 5. DC Characteristics**

| Parameter                                | Symbol            | Test Conditions                                                                                 | Min                          | Typ <sup>1</sup> | Max     | Units |

|------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------|------------------------------|------------------|---------|-------|

| High-level input voltage                 | V <sub>IH</sub>   | _                                                                                               | 0.7NVDD                      | _                | NVDD    |       |

| Low-level Input voltage                  | V <sub>IL</sub>   | _                                                                                               | 0                            | _                | 0.3NVDD |       |

| High-level output voltage                | V <sub>OH</sub>   | I <sub>OH</sub> = spec'ed Drive                                                                 | 0.8NVDD                      | _                | _       | V     |

| Low-level output voltage                 | V <sub>OL</sub>   | I <sub>OL</sub> = spec'ed Drive                                                                 | -                            | _                | 0.2NVDD | V     |

| High-level output current, slow I/O      | I <sub>OH_S</sub> | V <sub>out</sub> =0.8NVDD<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111  | -2<br>-4<br>-8<br>-12        | _                | -       | mA    |

| High-level output current, fast I/O      | I <sub>OH_F</sub> | V <sub>out</sub> =0.8NVDD1<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111 | -3.5<br>-4.5<br>-5.5<br>-6.5 | _                | -       | mA    |

| Low-level output current, slow I/O       | I <sub>OL_S</sub> | V <sub>out</sub> =0.2NVDD<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111  | 2<br>4<br>8<br>12            |                  | -       | mA    |

| Low-level output current, fast I/O       | I <sub>OL_F</sub> | V <sub>out</sub> =0.2NVDD1<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111 | 3.5<br>4.5<br>5.5<br>6.5     | _                | -       | mA    |

| Schmitt trigger Positive-input threshold | V <sub>T</sub> +  | _                                                                                               | -                            | _                | 2.15    | V     |

| Schmitt trigger Negative-input threshold | V <sub>T</sub> -  |                                                                                                 | 0.75                         | _                | -       | V     |

| Hysteresis                               | V <sub>HYS</sub>  | _                                                                                               | -                            | 0.3              | _       | V     |

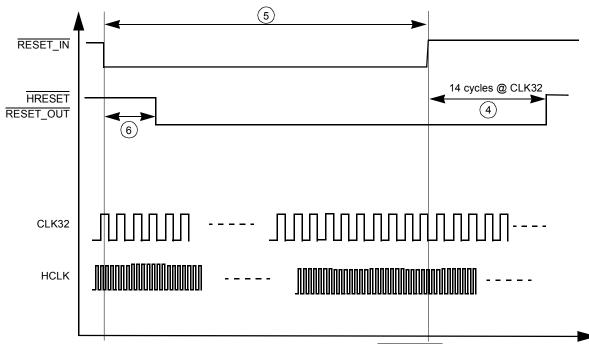

Figure 3. Timing Relationship with RESET\_IN

| Table 12. R | Reset Module | Timing | Parameters |

|-------------|--------------|--------|------------|

|-------------|--------------|--------|------------|

| Ref | Parameter                                                                                         | 1.8 V ± | = 0.10 V | 3.0 V ± | = 0.30 V | Unit            |  |

|-----|---------------------------------------------------------------------------------------------------|---------|----------|---------|----------|-----------------|--|

| No. | Falameter                                                                                         | Min     | Max      | Min     | Max      |                 |  |

| 1   | Width of input POWER_ON_RESET                                                                     | 800     | -        | 800     | -        | ms              |  |

| 2   | Width of internal POWER_ON_RESET<br>(CLK32 at 32 kHz)                                             | 300     | 300      | 300     | 300      | ms              |  |

| 3   | 7k to 32k-cycle stretcher for SDRAM reset                                                         | 7       | 7        | 7       | 7        | Cycles of CLK32 |  |

| 4   | 14k to 32k-cycle stretcher for internal system reset HRESERT<br>and output reset at pin RESET_OUT | 14      | 14       | 14      | 14       | Cycles of CLK32 |  |

| 5   | Width of external hard-reset RESET_IN                                                             | 4       | -        | 4       | -        | Cycles of CLK32 |  |

| 6   | 4k to 32k-cycle qualifier                                                                         | 4       | 4        | 4       | 4        | Cycles of CLK32 |  |

### 3.7 External DMA Request and Grant

The External DMA request is an active low signal to be used by devices external to i.MX21 processor to request the DMAC for data transfer.

After assertion of External DMA request the DMA burst will start when the channel on which the External request is the source (as per the RSSR settings) becomes the current highest priority channel. The external device using the External DMA request should keep its request asserted until it is serviced by the DMAC. One External DMA request will initiate one DMA burst.

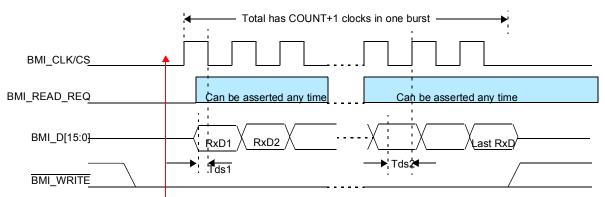

A 1 is written to READ bit of control register

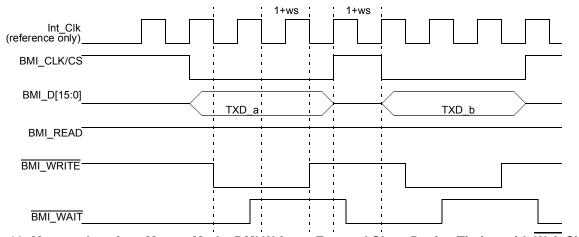

Figure 9. BMI Drives Clock, MMD Write BMI Timing (MASTER\_MODE\_SEL=0, MMD\_MODE\_SEL=1, MMD\_CLKOUT=1)

| Item                     | Symbol | Minimum | Typical | Maximum | Unit |

|--------------------------|--------|---------|---------|---------|------|

| Receive data setup time1 | Tds1   | 14      | -       | -       | ns   |

| Receive data setup time2 | Tds2   | 14      | _       | -       | ns   |

**Note:** The BMI\_CLK/CS can only be up to 30MHz if BMI latch data at the falling edge and can be up to 36MHz (double as max data pad speed) if BMI latch data at the next rising edge.

Note: Tds1 is the receive data setup time when BMI latch data at the falling edge.

Note: Tds2 is the receive data setup time when BMI latch data at the next rising edge.

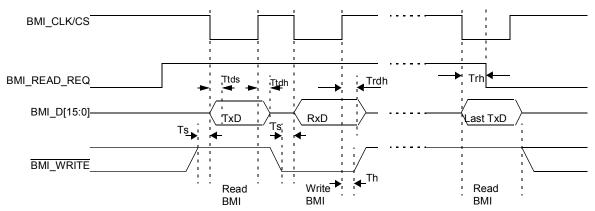

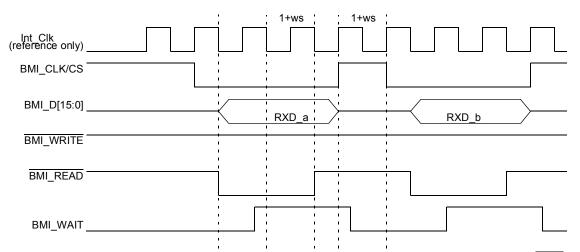

### 3.8.2 Connecting BMI to External Bus Master Devices

In this mode both MASTER\_SEL bit and MMD\_MODE\_SEL bit are cleared and the MMD\_CLKOUT bit is no useful. BMI\_WRITE and BMI\_CLK/CS are input signals driving by the external bus master. The Output signal BMI\_READ\_REQ can be used as an interrupt signal to inform external bus master that data is ready in the BMI TxFIFO for a read access. The external bus master can write data to the BMI RxFIFO anytime since the CPU or DMA can move data out from RxFIFO much faster than the BMI interface. An overflow interrupt is generated if RxFIFO overflow is detected. Once this happens, the new coming data is ignored.

Each falling edge of BMI\_CLK/CS will determine if the current cycle is read or write cycle. It drives data and enables data out if BMI\_WRITE is logic high. The D\_EN signal remains active only while BMI\_CLK/CS is logic low and BMI\_WRITE is logic high.

Each rising edge of BMI\_CLK/CS will determine if data should be latched to RxFIFO from the data bus.

Figure 10. Memory Interface Slave Mode, External Bus Master Read/Write to BMI Timing (MMD\_MODE\_SEL=0, MASTER\_MODE\_SEL=0)

| Item                     | Symbol | Minimum | Typical | Maximum | Unit |

|--------------------------|--------|---------|---------|---------|------|

| Write setup time         | Ts     | 11      | -       | -       | ns   |

| Write hold time          | Th     | 0       | -       | -       | ns   |

| Receive data hold time   | Trdh   | 3       | -       | -       | ns   |

| Transfer data setup time | Ttds   | 6       | -       | 14      | ns   |

| Transfer data hold time  | Ttdh   | 6       | -       | 14      | ns   |

| Read_req hold time       | Trh    | 6       | _       | 24      | ns   |

Table 18. External Bus Master Read/Write to BMI Timing Table

Note: All the timings are assumed that the hclk is running at 133 MHz.

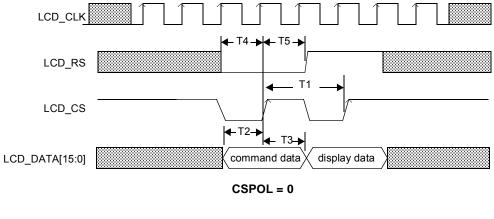

### 3.8.3 Connecting BMI to External Bus Slave Devices

In this mode the <u>BMI\_WRITE</u>, <u>BMI\_READ</u> and <u>BMI\_CLK/CS</u> are output signals driving by the <u>BMI</u> module. The output signal <u>BMI\_READ\_REQ</u> is still driving active-in on a write cycle, but it can be ignored in this case. Instead, it is used to trigger internal logic to generate the read or write signals. Data write cycles are continuously generated when TxFIFO is not emptied.

To issue a read cycle, the user can write a value of 1 to the READ bit of control register. This bit is cleared automatically when the read operation is completed. A read cycle reads COUNT+1 data from the external bus slave. The user can write a 1 to the READ bit while there is still data in the TxFIFO, but the read cycle will not start until all data in the TxFIFO is emptied. If the read cycle begins, the write operation also cannot begin until this read cycle complete.

In this master mode operation, Int\_Clk is derived from HCLK through an integer divider DIV of BMI control register and it is used to control the read/write cycle timing by generate  $\overline{WRITE}$  and CLK/CS signals.

Figure 12. Memory Interface Master Mode, BMI Write to External Slave Device Timing with Wait Signal (MMD\_MODE\_SEL=0, MASTER\_MODE\_SEL=1,WAIT=1)

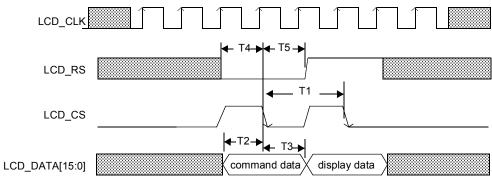

Figure 13 shows the BMI read timing when the WAIT bit is set. As write timing, when the BMI\_READ is asserted, the BMI will detect the BMI\_WAIT signal on every falling edge of the Int\_Clk. When it detected the high level of the BMI\_WAIT, the BMI\_READ will be negated after 1+WS Int\_Clk period. If the BMI\_WAIT is always high or already high before BMI\_READ is asserted, this timing will same as without WAIT signal. So the BMI\_READ will be asserted at least for 1+WS Int\_Clk period.

Figure 13. Memory Interface Master Mode, BMI Read to External Slave Device Timing with Wait Signal (MMD\_MODE\_SEL=0, MASTER\_MODE\_SEL=1,WAIT=1)

### 3.9 CSPI Timing Diagrams

To use the internal transmit (TX) and receive (RX) data FIFOs when the CSPI1 module is configured as a master, two control signals are used for data transfer rate control: the  $\overline{SS}$  signal (output) and the  $\overline{SPI}_RDY$  signal (input). The SPI 1 Sample Period Control Register (PERIODREG1) and the SPI 2 Sample Period Control Register (PERIODREG2) can also be programmed to a fixed data transfer rate for either CSPI1 or CSPI2. When the CSPI1 module is configured as a slave, the user can configure the SPI 1 Control Register (CONTROLREG1) to match the external CSPI master's timing. In this configuration,  $\overline{SS}$

| Symbol | Description                | Minimum | Maximum | Unit |

|--------|----------------------------|---------|---------|------|

| T1     | Pixel clock period         | 42      | 962     | ns   |

| T2     | Chip select setup time     | 5       | -       | ns   |

| Т3     | Chip select hold time      | 5       | -       | ns   |

| T4     | Data setup time            | 5       | -       | ns   |

| T4     | Data hold time             | 5       | -       | ns   |

| Т6     | Register select setup time | 5       | -       | ns   |

| T7     | Register select hold time  | 5       | -       | ns   |

CSPOL = 1 Figure 24. SLCDC Parallel Transfers Timing

| Symbol | Description                | Minimum | Maximum | Unit |

|--------|----------------------------|---------|---------|------|

| T1     | Pixel clock period         | 23      | 962     | ns   |

| T2     | Data setup time            | 5       | -       | ns   |

| Т3     | Data hold time             | 5       | -       | ns   |

| T4     | Register select setup time | 5       | -       | ns   |

| T5     | Register select hold time  | 5       | -       | ns   |

Table 25. SLCDC Parallel Transfers Timing

| Ref | Barranta                                       | 1.8 V           | ± 0.1 V          | 3.0 V   | ± 0.3 V | 11   |  |

|-----|------------------------------------------------|-----------------|------------------|---------|---------|------|--|

| No. | Parameter                                      | Minimum         | Maximum          | Minimum | Maximum | Unit |  |

| 11a | (Tx) CK high to STXD high                      | 0.34            | 0.72             | 0.34    | 0.72    | ns   |  |

| 11b | (Tx) CK high to STXD low                       | 0.34            | 0.72             | 0.34    | 0.72    | ns   |  |

| 12  | (Tx) CK high to STXD high impedance            | 0.34            | 0.48             | 0.34    | 0.48    | ns   |  |

| 13  | SRXD setup time before (Rx) CK low             | 21.50           | -                | 21.50   | -       | ns   |  |

| 14  | SRXD hold time after (Rx) CK low               | 0               | -                | 0       | -       | ns   |  |

|     | External Clock O                               | peration (SSI2  | Ports)           |         |         |      |  |

| 15  | (Tx/Rx) CK clock period <sup>1</sup> 90        | .91             | -                | 90.91   | -       | ns   |  |

| 16  | (Tx/Rx) CK clock high period                   | 36.36           | -                | 36.36   | -       | ns   |  |

| 17  | (Tx/Rx) CK clock low period                    | 36.36           | _                | 36.36   | _       | ns   |  |

| 18  | (Tx) CK high to FS (bl) high                   | 10.40           | 17.37            | 8.67    | 15.88   | ns   |  |

| 19  | (Rx) CK high to FS (bl) high                   | 11.00           | 19.70            | 9.28    | 18.21   | ns   |  |

| 20  | (Tx) CK high to FS (bl) low                    | 10.40           | 17.37            | 8.67    | 15.88   | ns   |  |

| 21  | (Rx) CK high to FS (bl) low                    | 11.00           | 11.00 19.70      |         | 18.21   | ns   |  |

| 22  | (Tx) CK high to FS (wl) high                   | 10.40           | 10.40 17.37 8.67 |         | 15.88   | ns   |  |

| 23  | (Rx) CK high to FS (wI) high                   | 11.00           | 19.70            | 9.28    | 18.21   | ns   |  |

| 24  | (Tx) CK high to FS (wl) low                    | 10.40           | 17.37            | 8.67    | 15.88   | ns   |  |

| 25  | (Rx) CK high to FS (wl) low                    | 11.00           | 19.70            | 9.28    | 18.21   | ns   |  |

| 26  | (Tx) CK high to STXD valid from high impedance | 9.59            | 17.08            | 7.86    | 15.59   | ns   |  |

| 27a | (Tx) CK high to STXD high                      | 9.59            | 17.08            | 7.86    | 15.59   | ns   |  |

| 27b | (Tx) CK high to STXD low                       | 9.59            | 17.08            | 7.86    | 15.59   | ns   |  |

| 28  | (Tx) CK high to STXD high impedance            | 9.59            | 16.84            | 7.86    | 15.35   | ns   |  |

| 29  | SRXD setup time before (Rx) CK low             | 2.52            | -                | 2.52    | -       | ns   |  |

| 30  | SRXD hole time after (Rx) CK low               | 0               | -                | 0       | -       | ns   |  |

|     | Synchronous Internal C                         | Clock Operation | n (SSI2 Ports)   |         |         |      |  |

| 31  | SRXD setup before (Tx) CK falling              | 20.78           | _                | 20.78   | _       | ns   |  |

| 32  | SRXD hold after (Tx) CK falling                | 0               | -                | 0       | -       | ns   |  |

|     | Synchronous External (                         | Clock Operatio  | n (SSI2 Ports    | )       | •       |      |  |

| 33  | SRXD setup before (Tx) CK falling              | 4.42            | _                | 4.42    | _       | ns   |  |

| 34  | SRXD hold after (Tx) CK falling                | 0               | -                | 0       | -       | ns   |  |

### Table 36. SSI to SSI2 Ports Timing Parameters (Continued)

1. All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

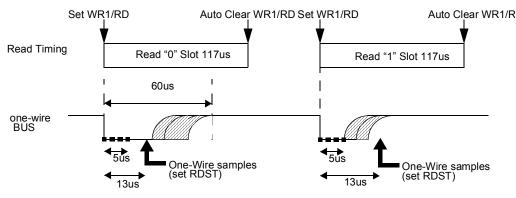

Figure 49. Read Timing

The precision of the generated clock is very important to get a proper behavior of the one-wire module. This module is based on a state machine which undertakes actions at defined times.

| Times       | Values<br>(Microsec) | Minimum<br>(Microsec) | Maximum<br>(microsec) | Absolute<br>Precision | Relative<br>Precision |

|-------------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| RSTL        | 511                  | 480                   | -                     | 31                    | 0.0645                |

| PST         | 68                   | 60                    | 75                    | 7                     | 0.1                   |

| RSTH        | 512                  | 480                   | -                     | 32                    | 0.0645                |

| LOW0        | 100                  | 60                    | 120                   | 20                    | 0.2                   |

| LOWR        | 5                    | 1                     | 15                    | 4                     | 0.8                   |

| READ_sample | 13                   | -                     | 15                    | 2                     | 0.15                  |

Table 38. System Timing Requirements

The most stringent constraint is 0.0645 as a relative time imprecision.

The time relative precision is directly derived from the frequency of the derivative clock (f):

Time relative precision = 1/f - 1 = divider/clock (MHz) - 1

The Figure 39 gathers relative time precision for different main clock frequencies.

| Table 39 | . System | Clock | Requirements |

|----------|----------|-------|--------------|

|----------|----------|-------|--------------|

| Main Clock Frequency (MHz) | 13 | 16.8   | 19.44 |

|----------------------------|----|--------|-------|

| Clock divide ratio         | 13 | 17     | 19    |

| Generated frequency (MHz)  | 1  | 0.9882 | 1.023 |

| Relative time imprecision  | 0  | 0.0117 | 0.023 |

This shows that the user should take care of the main clock frequency when using the one-wire module. If the main clock is an exact integer multiple of 1 MHz, then the generated frequency will be exactly 1 MHz.

### NOTE

A main clock frequency below 10 MHz might cause a misbehavior of the module.

MC9328MX21 Technical Data, Rev. 3.4

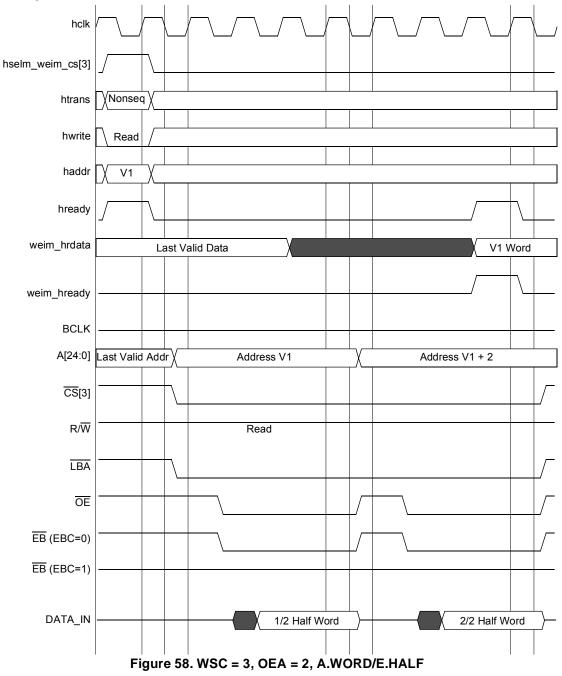

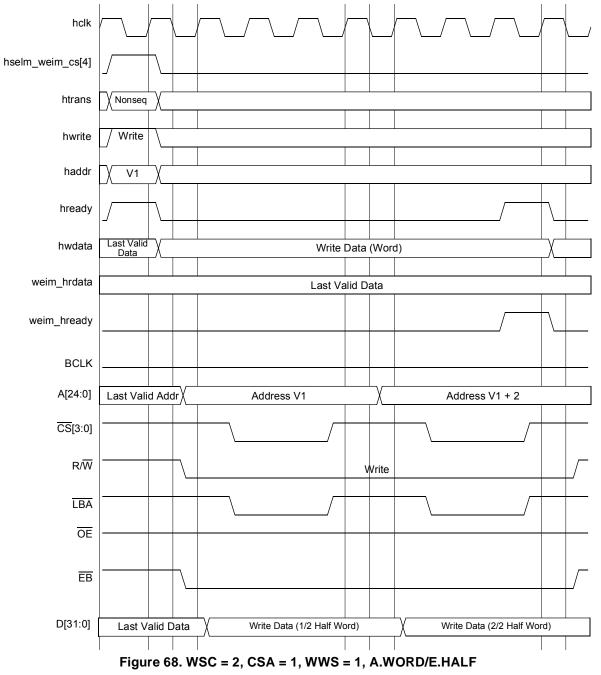

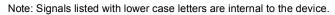

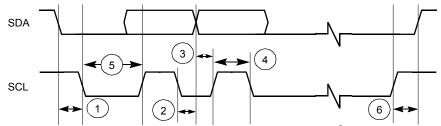

Note: Signals listed with lower case letters are internal to the device.

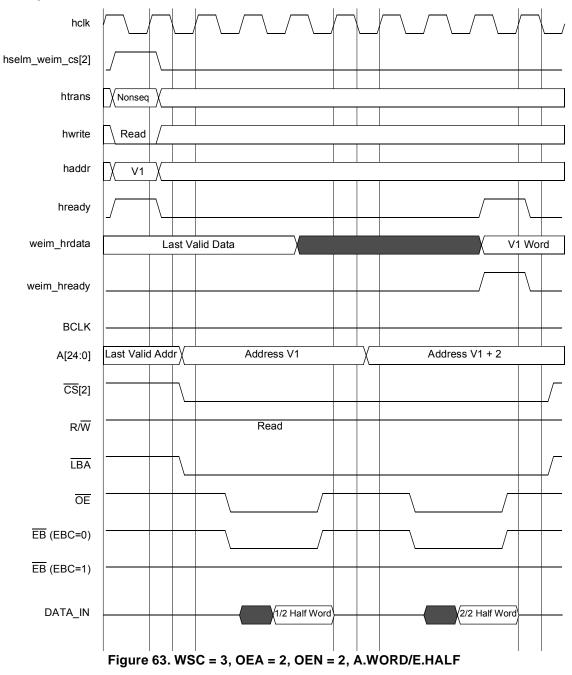

Note: Signals listed with lower case letters are internal to the device.

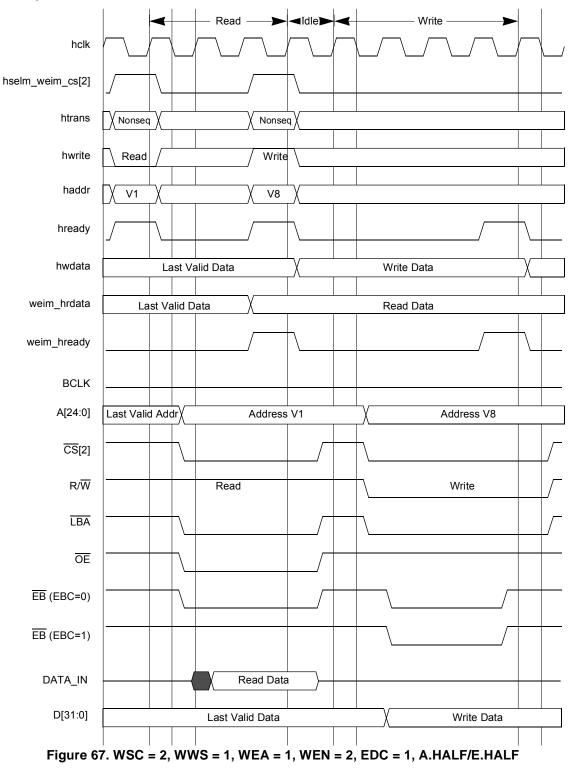

Note: Signals listed with lower case letters are internal to the device.

Note: Signals listed with lower case letters are internal to the device.

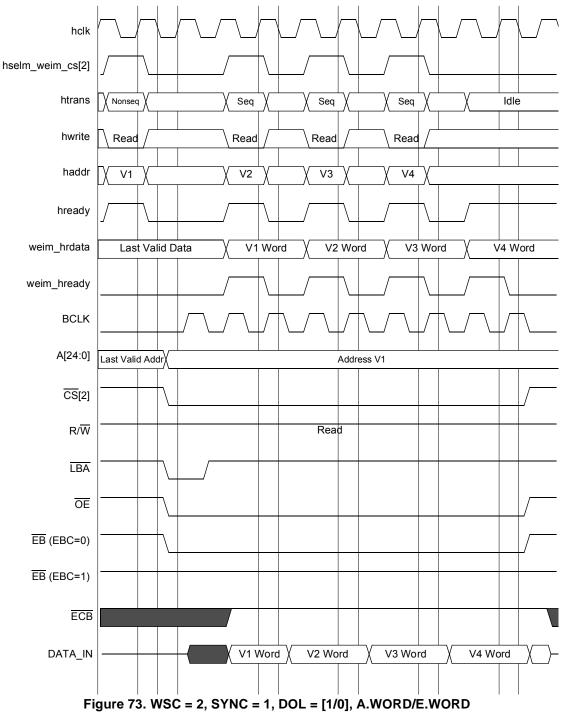

## 3.21 I<sup>2</sup>C Module

The I<sup>2</sup>C communication protocol consists of seven elements: START, Data Source/Recipient, Data Direction, Slave Acknowledge, Data, Data Acknowledge, and STOP.

Figure 80. Definition of Bus Timing for I<sup>2</sup>C

Table 44. I<sup>2</sup>C Bus Timing Parameters

| Ref | Parameter                            | 1.8 V   | ± 0.1 V | 3.0 V   | Unit    |      |

|-----|--------------------------------------|---------|---------|---------|---------|------|

| No. | i arameter                           | Minimum | Maximum | Minimum | Maximum | Onic |

|     | SCL Clock Frequency                  | 0       | 100     | 0       | 100     | kHz  |

| 1   | Hold time (repeated) START condition | 114.8   | -       | 111.1   | -       | ns   |

| 2   | Data hold time                       | 0       | 69.7    | 0       | 72.3    | ns   |

| 3   | Data setup time                      | 3.1     | -       | 1.76    | -       | ns   |

| 4   | HIGH period of the SCL clock         | 69.7    | -       | 68.3    | -       | ns   |

| 5   | LOW period of the SCL clock          | 336.4   | -       | 335.1   | -       | ns   |

| 6   | Setup time for STOP condition        | 110.5   | _       | 111.1   | _       | ns   |

### 3.22 CMOS Sensor Interface

The CSI module consists of a control register to configure the interface timing, a control register for statistic data generation, a status register, interface logic, a  $32 \times 32$  image data receive FIFO, and a  $16 \times 32$  statistic data FIFO.

### 3.22.1 Gated Clock Mode

Figure 81 shows the timing diagram when the CMOS sensor output data is configured for negative edge and the CSI is programmed to received data on the positive edge. Figure 82 shows the timing diagram when the CMOS sensor output data is configured for positive edge and the CSI is programmed to received data in negative edge. The parameters for the timing diagrams are listed in Table 45. The formula for calculating the pixel clock rise and fall time is located in Section 3.22.3, "Calculation of Pixel Clock Rise/Fall Time."

# 4 Pin Assignment and Package Information

Table 47. i.MX21 Pin Assignment

|   | 1              | 2              | 3              | 4           | 5     | 6            | 7      | 8           | 9              | 10             | 11                | 12             | 13            | 14            | 15             | 16             | 17              | 18         | 19             |

|---|----------------|----------------|----------------|-------------|-------|--------------|--------|-------------|----------------|----------------|-------------------|----------------|---------------|---------------|----------------|----------------|-----------------|------------|----------------|

| A | LD9            | LD12           | LD14           | REV         | HSYNC | OE_<br>ACD   | SD2_D2 | CSI_<br>D0  | CSI_<br>PIXCLK | CSI_<br>VSYNC  | USBH1_<br>FS      | USBH1_<br>OE   | USBG_<br>FS   | TOUT          | SAP_<br>TXDAT  | SSI1_<br>CLK   | SSI2_<br>RXDAT  | SSI2_TXDAT | SSI3_<br>FS    |

| В | LD7            | LD5            | LD11           | LD16        | PS    | CON<br>TRAST | SD2_D0 | SD2_<br>CMD | CSI_<br>D4     | CSI_D6         | USB_<br>PWR       | USBG_<br>SCL   | USBG_<br>TXDM | SAP_<br>FS    | SSI1_<br>FS    | SSI2_<br>FS    | SSI3_<br>TXDAT  | I2C_DATA   | CSPI2_<br>SS2  |

| С | LD1            | LD3            | LD6            | LD10        | LD17  | VSYNC        | SD2_D3 | CSI_<br>D1  | CSI_<br>MCLK   | CSI_<br>HSYNC  | U <u>SB</u><br>OC | USBH1_<br>RXDM | USBG_<br>RXDM | TIN           | SSI1_<br>TXDAT | SSI3_<br>RXDAT | SSI3_<br>CLK    | I2C_CLK    | CSPI2_<br>SS1  |

| D | LD2            | LD0            | LD13           | CLS         | QVDD  | QVSS         | SD2_D1 | SD2_<br>CLK | CSI_<br>D2     | CSI_D7         | USBH1_<br>TXDM    | USBH1_<br>RXDP | USBG_<br>ON   | USBG_<br>RXDP | SAP_<br>RXDAT  | SSI1_<br>RXDAT | SSI2_<br>CLK    | CSPI2_SS0  | CSPI2_<br>SCLK |

| Ε | LD8            | LD4            | LD15           | SPL_<br>SPR |       |              |        |             |                |                |                   |                |               |               |                | SAP_<br>CLK    | CSPI2_<br>MISO  | CSPI1_SS2  | CSPI2_<br>MOSI |

| F | A24_<br>NFIO14 | D31            | A25_<br>NFIO15 | LSCLK       |       |              |        |             |                |                |                   |                |               |               |                | CSPI1_<br>SS1  | CSPI1_<br>MISO  | KP_ROW0    | CSPI1_<br>SS0  |

| G | A22_<br>NFIO12 | D29            | A23_<br>NFIO13 | D30         |       |              | NVDD6  | NVSS6       | CSI_D3         | USB_<br>BYP    | USBH_<br>ON       | USBG_<br>SDA   | USBG_<br>TXDP |               |                | KP_<br>ROW1    | KP_<br>ROW3     | UART2_CTS  | KP_<br>ROW4    |

| н | A20            | D27            | A21_<br>NFIO11 | D28         |       |              | NVDD1  | NVSS5       | CSI_D5         | CSPI1_<br>SCLK | CSPI1_<br>RDY     | USBH1_<br>TXDP | USBG_<br>OE   |               |                | TEST_<br>WB4   | TEST_<br>WB2    | TEST_WB3   | PWMO           |

| J | A19            | A18            | D25            | D26         |       |              | NVDD1  | NVDD5       | NVDD4          | KP_<br>ROW5    | KP_<br>ROW2       | CSPI1_<br>MOSI | TEST_<br>WB0  |               |                | UART2_<br>RTS  | KP_COL1         | KP_COL0    | TEST_<br>WB1   |

| к | A16            | A17            | D23            | D24         |       |              | NVSS1  | NVSS4       | QVDDX          | UART1_<br>RXD  | TDO               | QVDD           | QVSS          |               |                | KP_<br>COL3    | KP_COL5         | KP_COL4    | KP_<br>COL2    |

| L | A14_<br>NFIO9  | A15_<br>NFIO10 | D21            | D22         |       |              | NVSS1  | NVDD3       | QVDD           | QVSS           | NFIO2             | NFWP           | UART1_<br>TXD |               |                | UART2_<br>TXD  | UART3_<br>RTS   | UART3_CTS  | UART3_<br>TXD  |

| М | D19            | A13_<br>NFIO8  | D20            | D18         |       |              | NVDD2  | NVDD3       | NVSS3          | QVSS           | NFIO7             | NFRB           | EXT_<br>48M   |               |                | UART2_<br>RXD  | UART3_<br>RXD   | UART1_RTS  | UART1_<br>CTS  |

| N | A11            | A12            | D17            | D16         |       |              | LBA    | NVSS3       | SDCKE0         | NVSS1          | NVSS1             | NVDD1          | NVDD1         |               |                | SD1_<br>D0     | тск             | SD1_D1     | RTCK           |

| Р | A9             | A10            | D15            | D14         |       |              |        |             |                |                |                   |                |               |               |                | SD1_<br>D2     | SD1_<br>CMD     | TDI        | TMS            |

| R | A7             | A8             | D13            | D12         |       |              |        |             |                |                |                   |                |               |               |                | SD1_<br>CLK    | EXT_<br>266M    | NVSS2      | TRST           |

| т | A5             | A6             | EB3            | D10         | CS3   | CS1          | BCLK   | MA11        | RAS            | CAS            | NFIO5             | NFIO3          | NFWE          | RESET_<br>IN  | NFCE           | BOOT1          | SD1_D3          | CLKMODE1   | CLK<br>MODE0   |

| U | D11            | EB1            | EB2            | ŌĒ          | CS4   | D6           | ECB    | D3          | MA10           | PC_<br>PWRON   | PF16              | NFIO4          | NFIO1         | NFALE         | NFCLE          | POR            | BOOT2           | BOOT3      | XTAL32K        |

| v | A4             | EB0            | D9             | D8          | CS5   | D5           | CS0    | RW          | D1             | JTAG_<br>CTRL  | SDWE              | CLKO           | NFIO6         | QVSS          | RESET_<br>OUT  | BOOT0          | OSC26M_<br>TEST | VDDA       | EXTAL<br>32K   |

| w | A3             | A2             | D7             | A1          | CS2   | A0           | D4     | D2          | D0             | SDCLK          | SDCKE1            | NFIO0          | NFRE          | QVDD          | QVSS           | EXTAL<br>26M   | XTAL26M         | QVDD       | QVSS           |

Pin Assignment and Package Information