#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

EXF

| Product Status                  | Active                                                     |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 266MHz                                                     |

| Co-Processors/DSP               | -                                                          |

| RAM Controllers                 | SDRAM                                                      |

| Graphics Acceleration           | Νο                                                         |

| Display & Interface Controllers | Keypad, LCD                                                |

| Ethernet                        |                                                            |

| SATA                            |                                                            |

| USB                             | USB 1.x (2)                                                |

| Voltage - I/O                   | 1.8V, 3.0V                                                 |

| Operating Temperature           | -40°C ~ 85°C (TA)                                          |

| Security Features               | -                                                          |

| Package / Case                  | 289-LFBGA                                                  |

| Supplier Device Package         | 289-PBGA (17x17)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9328mx21cvm |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

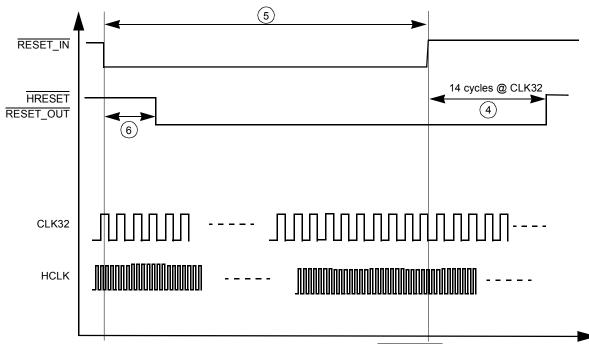

Figure 3. Timing Relationship with RESET\_IN

| Table 12. R | Reset Module | Timing | Parameters |

|-------------|--------------|--------|------------|

|-------------|--------------|--------|------------|

| Ref | Parameter                                                                                         | $1.8~V\pm0.10~V$ |     | $\textbf{3.0 V} \pm \textbf{0.30 V}$ |     | Unit            |  |

|-----|---------------------------------------------------------------------------------------------------|------------------|-----|--------------------------------------|-----|-----------------|--|

| No. | i arameter                                                                                        |                  | Max | Min                                  | Max | Ont             |  |

| 1   | Width of input POWER_ON_RESET                                                                     | 800              | -   | 800                                  | -   | ms              |  |

| 2   | Width of internal POWER_ON_RESET<br>(CLK32 at 32 kHz)                                             | 300              | 300 | 300                                  | 300 | ms              |  |

| 3   | 7k to 32k-cycle stretcher for SDRAM reset                                                         | 7                | 7   | 7                                    | 7   | Cycles of CLK32 |  |

| 4   | 14k to 32k-cycle stretcher for internal system reset HRESERT<br>and output reset at pin RESET_OUT | 14               | 14  | 14                                   | 14  | Cycles of CLK32 |  |

| 5   | Width of external hard-reset RESET_IN                                                             | 4                | -   | 4                                    | -   | Cycles of CLK32 |  |

| 6   | 4k to 32k-cycle qualifier                                                                         | 4                | 4   | 4                                    | 4   | Cycles of CLK32 |  |

## 3.7 External DMA Request and Grant

The External DMA request is an active low signal to be used by devices external to i.MX21 processor to request the DMAC for data transfer.

After assertion of External DMA request the DMA burst will start when the channel on which the External request is the source (as per the RSSR settings) becomes the current highest priority channel. The external device using the External DMA request should keep its request asserted until it is serviced by the DMAC. One External DMA request will initiate one DMA burst.

The output External Grant signal from the DMAC is an active-low signal. When the following conditions are true, the External DMA Grant signal is asserted with the initiation of the DMA burst.

- The DMA channel for which the DMA burst is ongoing has request source as external DMA Request

- (as per source select register setting).

- REN and CEN bit of this channel are set.

- External DMA Request is asserted.

After the grant is asserted, the External DMA request will not be sampled until completion of the DMA burst. As the external request is synchronized, the request synchronization will not be done during this period. The priority of the external request becomes low for the next consecutive burst, if another DMA request signal is asserted.

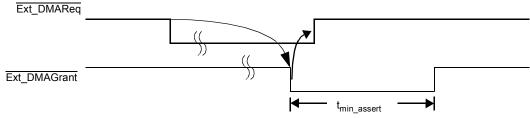

Worst case—that is, the smallest burst (1 byte read/write) timing diagrams are shown in Figure 4 and Figure 5. Minimum and maximum timings for the External request and External grant signals are present in Table 13.

Figure 4 shows the minimum time for which the External Grant signal remains asserted when an External DMA request is de-asserted immediately after sensing grant signal active.

Figure 4. Assertion of DMA External Grant Signal

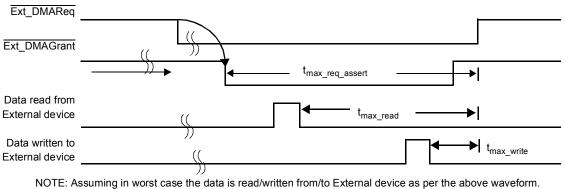

Figure 5 shows the safe maximum time for which External DMA request can be kept asserted, after sensing grant signal active such that a new burst is not initiated.

Figure 5. Safe Maximum Timings for External Request De-Assertion

| Parameter                   | Description                                                             | 3.0            | V             | 1.8            | Unit          |      |

|-----------------------------|-------------------------------------------------------------------------|----------------|---------------|----------------|---------------|------|

|                             | Description                                                             | WCS            | BCS           | WCS            | BCS           | onne |

| t <sub>min_assert</sub>     | Minimum assertion time of External Grant signal                         | 8 hclk + 8.6   | 8 hclk + 2.74 | 8 hclk + 7.17  | 8 hclk + 3.25 | ns   |

| t <sub>max_req_assert</sub> | Maximum External request assertion time after assertion of Grant signal | 9 hclk - 20.66 | 9 hclk - 6.7  | 9 hclk - 17.96 | 9 hclk - 8.16 | ns   |

| t <sub>max_read</sub>       | Maximum External request assertion time after first read completion     | 8 hclk - 6.21  | 8 hclk - 0.77 | 8 hclk - 5.84  | 8 hclk - 0.66 | ns   |

| t <sub>max_write</sub>      | Maximum External request assertion time after completion of first write | 3 hclk - 15.87 | 3 hclk - 8.83 | 3 hclk - 15.9  | 3 hclk - 9.12 | ns   |

Table 13. DMA External Request and Grant Timing Parameters

# 3.8 BMI Interface Timing Diagram

### 3.8.1 Connecting BMI to ATI MMD Devices

### 3.8.1.1 ATI MMD Devices Drive the BMI\_CLK/CS

In this mode MMD\_MODE\_SEL bit is set and MMD\_CLKOUT bit is cleared. BMI\_WRITE and BMI\_CLK/CS are input signals to BMI driving by ATI MMD chip set. Output signal BMI\_READ\_REQ can be used as interrupt signal to inform MMD that data is ready in BMI TxFIFO for read access. MMD can write data to BMI RxFIFO anytime as CPU or DMA can move data out from RxFIFO much faster than the BMI interface. Overflow interrupt is generated if RxFIFO overflow is detected. Once this happens, the new coming data is ignored.

### 3.8.1.1.1 MMD Read BMI Timing

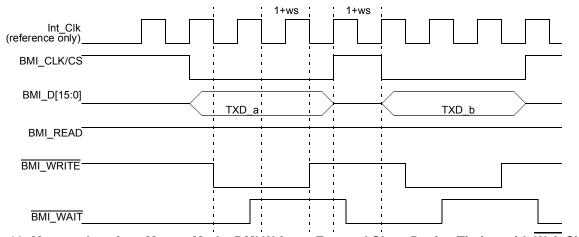

Figure 6 shows the MMD read BMI timing when the MMD drives clock.

On each rising edge of BMI\_CLK/CS BMI checks the BMI\_WRITE logic level to determine if the current cycle is a read cycle. It puts data into the data bus and enables the data out on the rising edge of BMI\_CLK/CS if BMI\_WRITE is logic high. The BMI\_READ\_REQ is negated one hclk cycle after the BMI\_CLK/CS rising edge of last data read. The MMD cannot issues read command when BMI\_READ\_REQ is low (no data in TxFIFO).

Figure 12. Memory Interface Master Mode, BMI Write to External Slave Device Timing with Wait Signal (MMD\_MODE\_SEL=0, MASTER\_MODE\_SEL=1,WAIT=1)

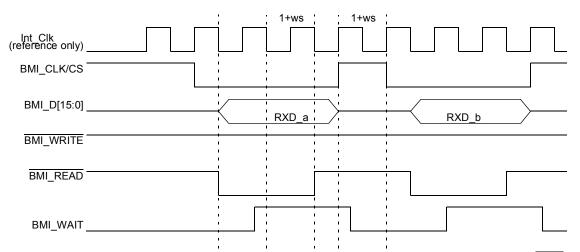

Figure 13 shows the BMI read timing when the WAIT bit is set. As write timing, when the BMI\_READ is asserted, the BMI will detect the BMI\_WAIT signal on every falling edge of the Int\_Clk. When it detected the high level of the BMI\_WAIT, the BMI\_READ will be negated after 1+WS Int\_Clk period. If the BMI\_WAIT is always high or already high before BMI\_READ is asserted, this timing will same as without WAIT signal. So the BMI\_READ will be asserted at least for 1+WS Int\_Clk period.

Figure 13. Memory Interface Master Mode, BMI Read to External Slave Device Timing with Wait Signal (MMD\_MODE\_SEL=0, MASTER\_MODE\_SEL=1,WAIT=1)

# 3.9 CSPI Timing Diagrams

To use the internal transmit (TX) and receive (RX) data FIFOs when the CSPI1 module is configured as a master, two control signals are used for data transfer rate control: the  $\overline{SS}$  signal (output) and the  $\overline{SPI}_RDY$  signal (input). The SPI 1 Sample Period Control Register (PERIODREG1) and the SPI 2 Sample Period Control Register (PERIODREG2) can also be programmed to a fixed data transfer rate for either CSPI1 or CSPI2. When the CSPI1 module is configured as a slave, the user can configure the SPI 1 Control Register (CONTROLREG1) to match the external CSPI master's timing. In this configuration,  $\overline{SS}$

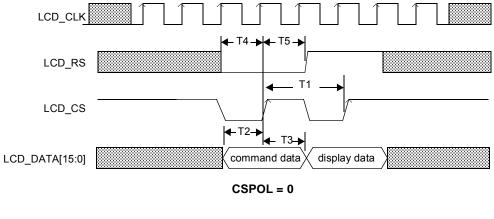

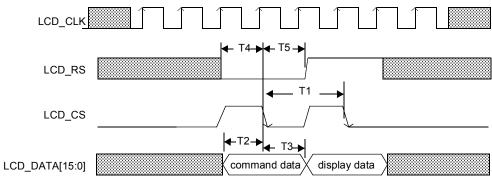

| Symbol | Description                | Minimum | Maximum | Unit |

|--------|----------------------------|---------|---------|------|

| T1     | Pixel clock period         | 42      | 962     | ns   |

| T2     | Chip select setup time     | 5       | -       | ns   |

| Т3     | Chip select hold time      | 5       | -       | ns   |

| T4     | Data setup time            | 5       | -       | ns   |

| T4     | Data hold time             | 5       | -       | ns   |

| Т6     | Register select setup time | 5       | -       | ns   |

| T7     | Register select hold time  | 5       | -       | ns   |

CSPOL = 1 Figure 24. SLCDC Parallel Transfers Timing

| Symbol | Description                | Minimum | Maximum | Unit |

|--------|----------------------------|---------|---------|------|

| T1     | Pixel clock period         | 23      | 962     | ns   |

| T2     | Data setup time            | 5       | -       | ns   |

| Т3     | Data hold time             | 5       | -       | ns   |

| T4     | Register select setup time | 5       | -       | ns   |

| T5     | Register select hold time  | 5       | -       | ns   |

Table 25. SLCDC Parallel Transfers Timing

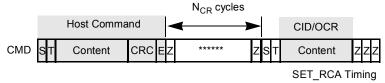

## 3.12.1 Command Response Timing on MMC/SD Bus

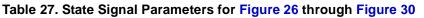

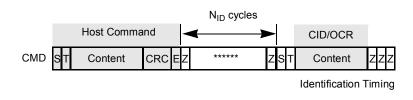

The card identification and card operation conditions timing are processed in open-drain mode. The card response to the host command starts after exactly  $N_{ID}$  clock cycles. For the card address assignment, SET\_RCA is also processed in the open-drain mode. The minimum delay between the host command and card response is NCR clock cycles as illustrated in Figure 26. The symbols for Figure 26 through Figure 30 are defined in Table 27.

|        | Card Active                           | Host Active |                                         |  |

|--------|---------------------------------------|-------------|-----------------------------------------|--|

| Symbol | Definition                            | Symbol      | Definition                              |  |

| Z      | High impedance state                  | S           | Start bit (0)                           |  |

| D      | Data bits                             | т           | Transmitter bit<br>(Host = 1, Card = 0) |  |

| *      | Repetition                            | Р           | One-cycle pull-up (1)                   |  |

| CRC    | Cyclic redundancy check bits (7 bits) | E           | End bit (1)                             |  |

Figure 26. Timing Diagrams at Identification Mode

After a card receives its RCA, it switches to data transfer mode. As shown on the first diagram in Figure 27, SD\_CMD lines in this mode are driven with push-pull drivers. The command is followed by a period of two Z bits (allowing time for direction switching on the bus) and then by P bits pushed up by the responding card. The other two diagrams show the separating periods  $N_{RC}$  and  $N_{CC}$ .

Figure 28 shows basic read operation timing. In a read operation, the sequence starts with a single block read command (which specifies the start address in the argument field). The response is sent on the SD\_CMD lines as usual. Data transmission from the card starts after the access time delay  $N_{AC}$ , beginning from the last bit of the read command. If the system is in multiple block read mode, the card sends a continuous flow of data blocks with distance  $N_{AC}$  until the card sees a stop transmission command. The data stops two clock cycles after the end bit of the stop command.

| ID   | Parameter           | Symbol | Relationship to NFC<br>Clock Period<br>(T) |     | NFC Clock<br>22.17 MHz<br>T = 45 ns |     | NFC Clock<br>33.25 MHz<br>T = 30 ns |     | Unit |

|------|---------------------|--------|--------------------------------------------|-----|-------------------------------------|-----|-------------------------------------|-----|------|

|      |                     |        | Min                                        | Max | Min                                 | Max | Min                                 | Мах |      |

| NF1  | NFCLE Setup Time    | tCLS   | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF2  | NFCLE Hold Time     | tCLH   | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF3  | NFCE Setup Time     | tCS    | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF4  | NFCE Hold Time      | tCH    | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF5  | NF_WP Pulse Width   | tWP    | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF6  | NFALE Setup Time    | tALS   | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF7  | NFALE Hold Time     | tALH   | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF8  | Data Setup Time     | tDS    | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF9  | Data Hold Time      | tDH    | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF10 | Write Cycle Time    | tWC    | 2T                                         | -   | 90                                  | -   | 60                                  | -   | ns   |

| NF11 | NFWE Hold Time      | tWH    | Т                                          | -   | 45                                  | -   | 30                                  | -   | ns   |

| NF12 | Ready to NFRE Low   | tRR    | 4T                                         | -   | 180                                 | -   | 120                                 | -   | ns   |

| NF13 | NFRE Pulse Width    | tRP    | 1.5T                                       | -   | 67.5                                | -   | 45                                  | -   | ns   |

| NF14 | READ Cycle Time     | tRC    | 2T                                         | -   | 90                                  | -   | 60                                  | -   | ns   |

| NF15 | NFRE High Hold Time | tREH   | 0.5T                                       | -   | 22.5                                | -   | 15                                  | -   | ns   |

| NF16 | Data Setup on READ  | tDSR   | 15                                         | -   | 15                                  | -   | 15                                  | -   | ns   |

| NF17 | Data Hold on READ   | tDHR   | 0                                          | -   | 0                                   | -   | 0                                   | -   | ns   |

1. High is defined as 80% of signal value and low is defined as 20% of signal value. All timings are listed according to this NFC clock frequency (multiples of NFC clock period) except NF16, which is not NFC clock related.

2. The read data is generated by the NAND Flash device and sampled with the internal NFC clock.

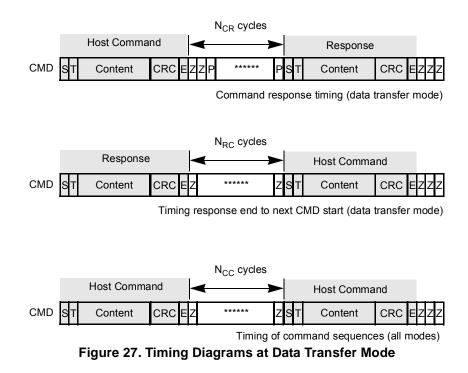

# 3.14 Pulse-Width Modulator

The PWM can be programmed to select one of two clock signals as its source frequency. The selected clock signal is passed through a divider and a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

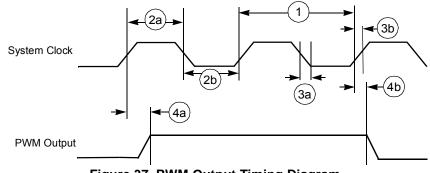

Figure 37. PWM Output Timing Diagram

| Ref No. | Parameter            | 1.8 V   | ± 0.1 V | 3.0 V   | Unit    |      |

|---------|----------------------|---------|---------|---------|---------|------|

|         | Faiameter            | Minimum | Maximum | Minimum | Maximum | Unit |

| 1       | System CLK frequency | 0       | 45      | 0       | 45      | MHz  |

| 2a      | Clock high time      | 12.29   | -       | 12.29   | _       | ns   |

| 2b      | Clock low time       | 9.91    | _       | 9.91    | _       | ns   |

| 3a      | Clock fall time      | -       | 0.5     | -       | 0.5     | ns   |

| 3b      | Clock ise time r     | -       | 0.5     | -       | 0.5     | ns   |

| 4a      | Output delay time    | 9.37    | -       | 3.61    | _       | ns   |

| 4b      | Output setup time    | 8.71    | -       | 3.03    | _       | ns   |

Table 30. PWM Output Timing Parameters

| Ref<br>No.                                       | Parameter                         | <b>1.8 V</b> : | ± 0.1 V | 3.0 V $\pm$ 0.3 V |         | Linit |  |

|--------------------------------------------------|-----------------------------------|----------------|---------|-------------------|---------|-------|--|

|                                                  |                                   | Minimum        | Maximum | Minimum           | Maximum | Unit  |  |

| Synchronous Internal Clock Operation (SAP Ports) |                                   |                |         |                   |         |       |  |

| 31                                               | SRXD setup before (Tx) CK falling | 23.00          | _       | 21.41             | _       | ns    |  |

| 32                                               | SRXD hold after (Tx) CK falling   | 0              | _       | 0                 | -       | ns    |  |

| Synchronous External Clock Operation (SAP Ports) |                                   |                |         |                   |         |       |  |

| 33                                               | SRXD setup before (Tx) CK falling | 1.20           | -       | 0.88              | -       | ns    |  |

| 34                                               | SRXD hold after (Tx) CK falling   | 0              | _       | 0                 | -       | ns    |  |

#### Table 34. SSI to SAP Ports Timing Parameters (Continued)

1. All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

| Ref                                                | Parameter                                      | 1.8 V :       | ± 0.1 V | 3.0 V   | Unit    |      |  |  |

|----------------------------------------------------|------------------------------------------------|---------------|---------|---------|---------|------|--|--|

| No.                                                |                                                | Minimum       | Maximum | Minimum | Maximum | Unit |  |  |

| Internal Clock Operation <sup>1</sup> (SSI1 Ports) |                                                |               |         |         |         |      |  |  |

| 1                                                  | (Tx/Rx) CK clock period <sup>1</sup> 9         | 0.91          | _       | 90.91   | -       | ns   |  |  |

| 2                                                  | (Tx) CK high to FS (bl) high                   | -0.68         | -0.15   | -0.68   | -0.15   | ns   |  |  |

| 3                                                  | (Rx) CK high to FS (bl) high                   | -0.96         | -0.27   | -0.96   | -0.27   | ns   |  |  |

| 4                                                  | (Tx) CK high to FS (bl) low                    | -0.68         | -0.15   | -0.68   | -0.15   | ns   |  |  |

| 5                                                  | (Rx) CK high to FS (bl) low                    | -0.96         | -0.27   | -0.96   | -0.27   | ns   |  |  |

| 6                                                  | (Tx) CK high to FS (wl) high                   | -0.68         | -0.15   | -0.68   | -0.15   | ns   |  |  |

| 7                                                  | (Rx) CK high to FS (wl) high                   | -0.96         | -0.27   | -0.96   | -0.27   | ns   |  |  |

| 8                                                  | (Tx) CK high to FS (wl) low                    | -0.68         | -0.15   | -0.68   | -0.15   | ns   |  |  |

| 9                                                  | (Rx) CK high to FS (wI) low                    | -0.96         | -0.27   | -0.96   | -0.27   | ns   |  |  |

| 10                                                 | (Tx) CK high to STXD valid from high impedance | -1.68         | -0.36   | -1.68   | -0.36   | ns   |  |  |

| 11a                                                | (Tx) CK high to STXD high                      | -1.68         | -0.36   | -1.68   | -0.36   | ns   |  |  |

| 11b                                                | (Tx) CK high to STXD low                       | -1.68         | -0.36   | -1.68   | -0.36   | ns   |  |  |

| 12                                                 | (Tx) CK high to STXD high impedance            | -1.58         | -0.31   | -1.58   | -0.31   | ns   |  |  |

| 13                                                 | SRXD setup time before (Rx) CK low             | 20.41         | -       | 20.41   | -       | ns   |  |  |

| 14                                                 | SRXD hold time after (Rx) CK low               | 0             | -       | 0       | -       | ns   |  |  |

|                                                    | External Clock Op                              | eration (SSI1 | Ports)  |         |         |      |  |  |

| 15                                                 | (Tx/Rx) CK clock period <sup>1</sup> 9         | 0.91          | _       | 90.91   | _       | ns   |  |  |

| 16                                                 | (Tx/Rx) CK clock high period                   | 36.36         | _       | 36.36   | -       | ns   |  |  |

| 17                                                 | (Tx/Rx) CK clock low period                    | 36.36         | -       | 36.36   | -       | ns   |  |  |

| 18                                                 | (Tx) CK high to FS (bl) high                   | 10.22         | 17.63   | 8.82    | 16.24   | ns   |  |  |

| 19                                                 | (Rx) CK high to FS (bl) high                   | 10.79         | 19.67   | 9.39    | 18.28   | ns   |  |  |

#### Table 35. SSI to SSI1 Ports Timing Parameters

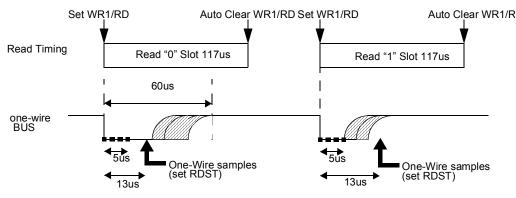

Figure 49. Read Timing

The precision of the generated clock is very important to get a proper behavior of the one-wire module. This module is based on a state machine which undertakes actions at defined times.

| Times       | Values<br>(Microsec) | Minimum<br>(Microsec) | Maximum<br>(microsec) | Absolute<br>Precision | Relative<br>Precision |

|-------------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| RSTL        | 511                  | 480                   | -                     | 31                    | 0.0645                |

| PST         | 68                   | 60                    | 75                    | 7                     | 0.1                   |

| RSTH        | 512                  | 480                   | -                     | 32                    | 0.0645                |

| LOW0        | 100                  | 60                    | 120                   | 20                    | 0.2                   |

| LOWR        | 5                    | 1                     | 15                    | 4                     | 0.8                   |

| READ_sample | 13                   | _                     | 15                    | 2                     | 0.15                  |

Table 38. System Timing Requirements

The most stringent constraint is 0.0645 as a relative time imprecision.

The time relative precision is directly derived from the frequency of the derivative clock (f):

Time relative precision = 1/f - 1 = divider/clock (MHz) - 1

The Figure 39 gathers relative time precision for different main clock frequencies.

| Table 39 | . System | Clock | Requirements |

|----------|----------|-------|--------------|

|----------|----------|-------|--------------|

| Main Clock Frequency (MHz) | 13 | 16.8   | 19.44 |

|----------------------------|----|--------|-------|

| Clock divide ratio         | 13 | 17     | 19    |

| Generated frequency (MHz)  | 1  | 0.9882 | 1.023 |

| Relative time imprecision  | 0  | 0.0117 | 0.023 |

This shows that the user should take care of the main clock frequency when using the one-wire module. If the main clock is an exact integer multiple of 1 MHz, then the generated frequency will be exactly 1 MHz.

### NOTE

A main clock frequency below 10 MHz might cause a misbehavior of the module.

MC9328MX21 Technical Data, Rev. 3.4

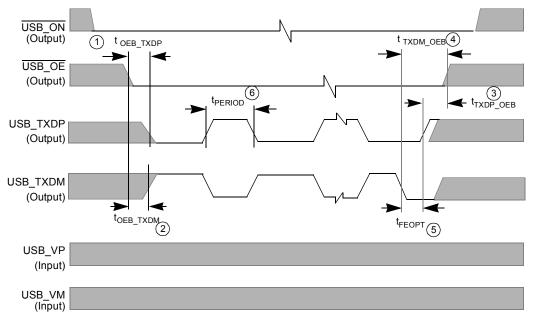

## 3.18 USB On-The-Go

Four types of data transfer modes exist for the USB module: control transfers, bulk transfers, isochronous transfers and interrupt transfers. From the perspective of the USB module, the interrupt transfer type is identical to the bulk data transfer mode, and no additional hardware is supplied to support it. This section covers the transfer modes and how they work from the ground up.

Data moves across the USB in packets. Groups of packets are combined to form data transfers. The same packet transfer mechanism applies to bulk, interrupt, and control transfers. Isochronous data is also moved in the form of packets, but because isochronous pipes are given a fixed portion of the USB bandwidth at all times, there is no end-of-transfer.

Figure 50. USB Timing Diagram for Data Transfer to USB Transceiver (TX)

| Ref<br>No. | Parameter                                                              | 3.0 V $\pm$ 0.3 V |         | Unit |

|------------|------------------------------------------------------------------------|-------------------|---------|------|

|            | raiameter                                                              | Minimum           | Maximum | Unit |

| 1          | t <sub>OEB_TXDP</sub> ; USBD_OE active to USBD_TXDP low                | 83.14             | 83.47   | ns   |

| 2          | t <sub>OEB_TXDM</sub> ; USBD_OE active to USBD_TXDM high               | 81.55             | 81.98   | ns   |

| 3          | t <sub>TXDP_OEB</sub> ; USBD_TXDP high to USBD_OE deactivated          | 83.54             | 83.8    | ns   |

| 4          | $t_{TXDM_{OEB}}$ ; USBD_TXDM low to USBD_OE deactivated (includes SE0) | 248.9             | 249.13  | ns   |

| 5          | t <sub>FEOPT</sub> ; SE0 interval of EOP                               | 160               | 175     | ns   |

| 6          | t <sub>PERIOD</sub> ; Data transfer rate                               | 11.97             | 12.03   | Mb/s |

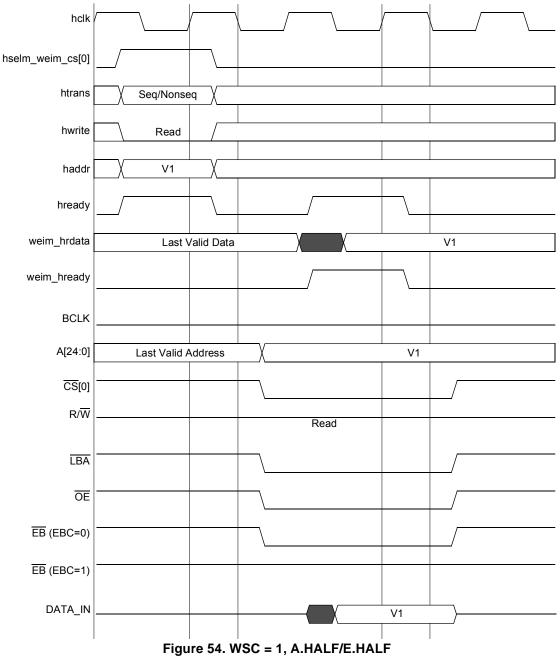

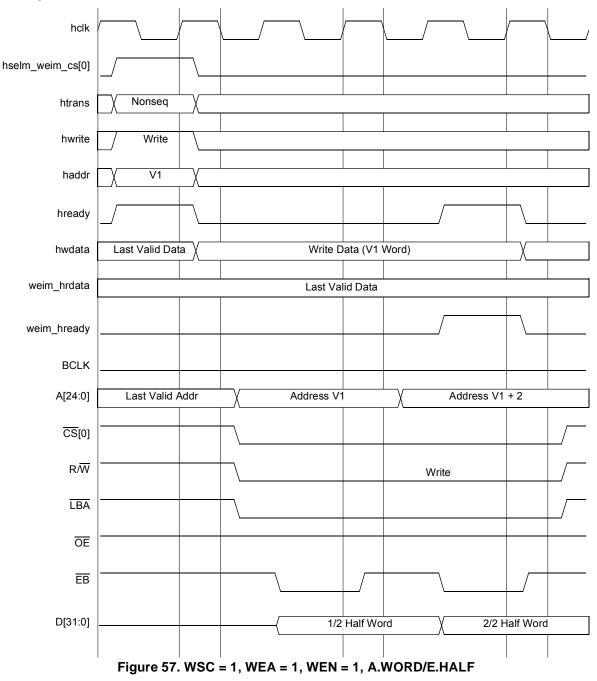

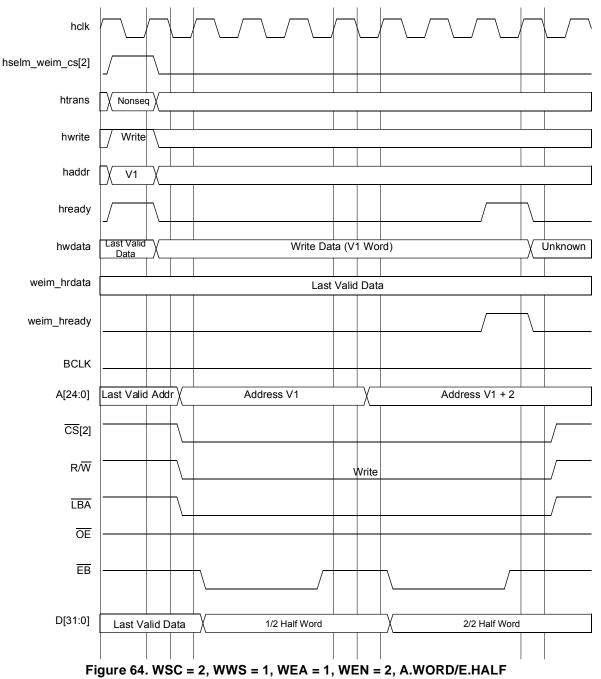

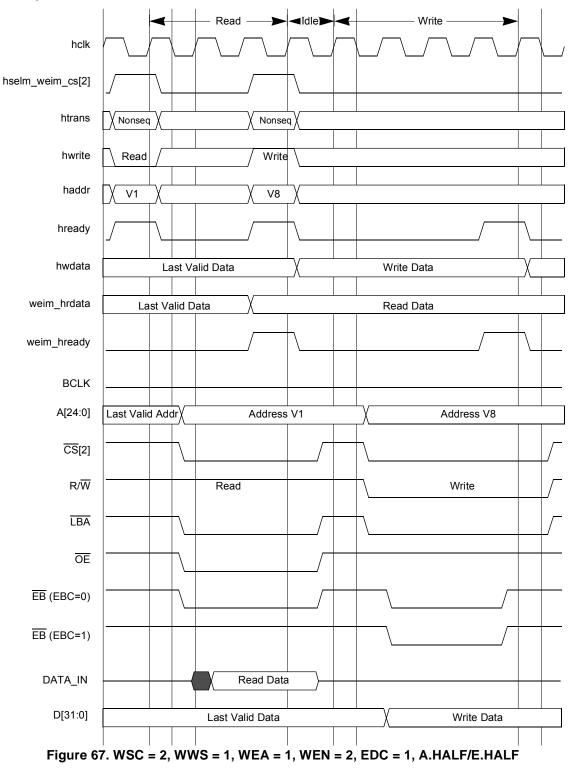

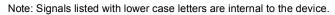

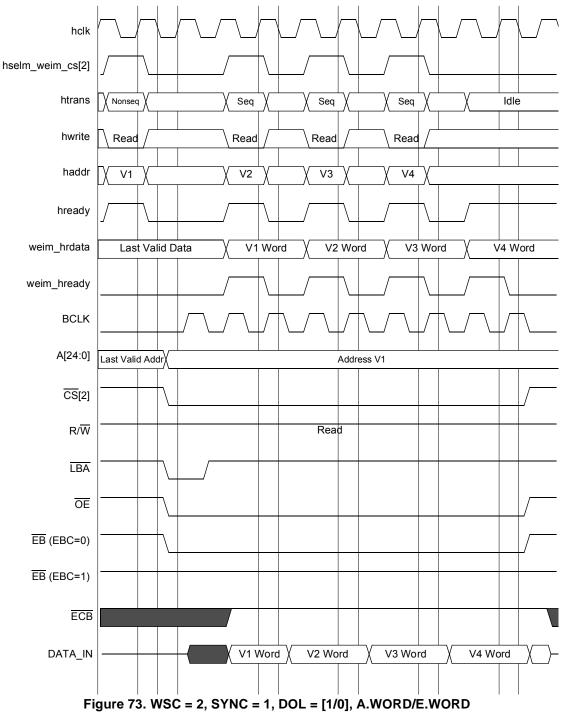

### 3.19.1 EIM External Bus Timing Diagrams

The following timing diagrams show the timing of accesses to memory or a peripheral.

Note: Signals listed with lower case letters are internal to the device.

Note: Signals listed with lower case letters are internal to the device.

Note: Signals listed with lower case letters are internal to the device.

Note: Signals listed with lower case letters are internal to the device.

# 3.21 I<sup>2</sup>C Module

The I<sup>2</sup>C communication protocol consists of seven elements: START, Data Source/Recipient, Data Direction, Slave Acknowledge, Data, Data Acknowledge, and STOP.

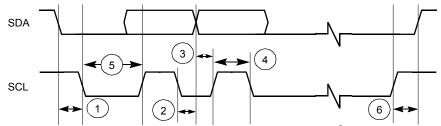

Figure 80. Definition of Bus Timing for I<sup>2</sup>C

Table 44. I<sup>2</sup>C Bus Timing Parameters

| Ref<br>No. | Parameter                            | 1.8 V $\pm$ 0.1 V |         | 3.0 V $\pm$ 0.3 V |         | Unit |

|------------|--------------------------------------|-------------------|---------|-------------------|---------|------|

|            | i arameter                           | Minimum           | Maximum | Minimum           | Maximum | Onic |

|            | SCL Clock Frequency                  | 0                 | 100     | 0                 | 100     | kHz  |

| 1          | Hold time (repeated) START condition | 114.8             | -       | 111.1             | -       | ns   |

| 2          | Data hold time                       | 0                 | 69.7    | 0                 | 72.3    | ns   |

| 3          | Data setup time                      | 3.1               | -       | 1.76              | -       | ns   |

| 4          | HIGH period of the SCL clock         | 69.7              | -       | 68.3              | -       | ns   |

| 5          | LOW period of the SCL clock          | 336.4             | -       | 335.1             | -       | ns   |

| 6          | Setup time for STOP condition        | 110.5             | _       | 111.1             | _       | ns   |

# 3.22 CMOS Sensor Interface

The CSI module consists of a control register to configure the interface timing, a control register for statistic data generation, a status register, interface logic, a  $32 \times 32$  image data receive FIFO, and a  $16 \times 32$  statistic data FIFO.

### 3.22.1 Gated Clock Mode

Figure 81 shows the timing diagram when the CMOS sensor output data is configured for negative edge and the CSI is programmed to received data on the positive edge. Figure 82 shows the timing diagram when the CMOS sensor output data is configured for positive edge and the CSI is programmed to received data in negative edge. The parameters for the timing diagrams are listed in Table 45. The formula for calculating the pixel clock rise and fall time is located in Section 3.22.3, "Calculation of Pixel Clock Rise/Fall Time."

Pin Assignment and Package Information

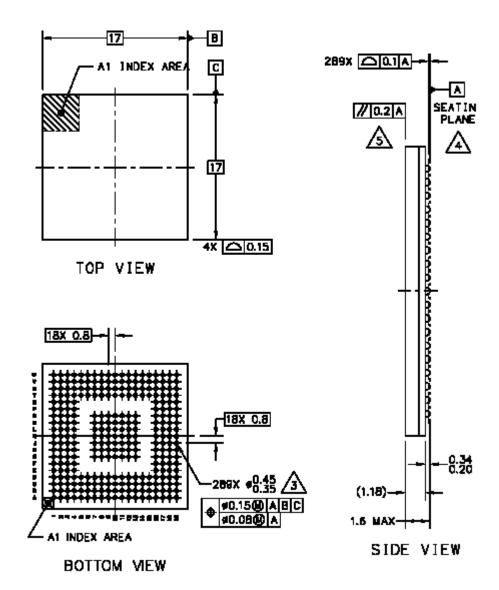

### 4.2 MAPBGA Package Dimensions

Figure 86 illustrates the MAPBGA 17 mm  $\times$  17 mm  $\times$  1.45 mm package, which has 0.8 mm spacing between the pads.

NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14. 5N-1994.

3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

4 DATUM A. THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

5. PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

Figure 86. i.MX21 MAPBGA Mechanical Drawing

# 5 Document Revision History

Table 48 provides the document changes for the MC9328MX21 Rev. 3.4.

| Location            | Description of Change                             |

|---------------------|---------------------------------------------------|

| Table 30 on page 46 | Updated the table by removing the table footnote  |

| Table 1 on page 3   | Added VM and CVM devices.                         |

| Table 7 on page 16  | Updated Sleep Current values.                     |

| Table 1 on page 4   | Added a part number MC9328MX21CJM and a footnote. |

#### Table 48. Document Revision History