# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 100MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 66                                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 128K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                         |

| Data Converters            | A/D 33x16b; D/A 1x12b                                                                |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | 100-LQFP (14x14)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk60dn512zvll10              |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communication interfaces

- Ethernet controller with MII and RMII interface to external PHY and hardware IEEE 1588 capability

- USB full-/low-speed On-the-Go controller with on-chip transceiver

- Two Controller Area Network (CAN) modules

- Three SPI modules

- Two I2C modules

- Five UART modules

- Secure Digital host controller (SDHC)

- I2S module

| 8 | Pinc |                                               |   |

|---|------|-----------------------------------------------|---|

|   | 8.1  | K60 Signal Multiplexing and Pin Assignments68 | 5 |

|   | 8.2 | K60 Pin   | outs | <br> | <br> | <br> | 72 |

|---|-----|-----------|------|------|------|------|----|

| 9 | Rev | ision His | tory | <br> | <br> | <br> | 73 |

# 3.1.1 Example

This is an example of an operating requirement:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

# 3.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

### 3.2.1 Example

This is an example of an operating behavior:

| Symbol          | Description                                  | Min. | Max. | Unit |

|-----------------|----------------------------------------------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μΑ   |

# 3.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

# 3.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

#### General

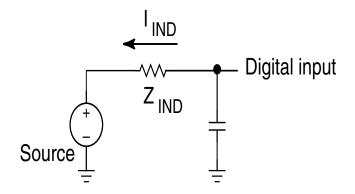

| Symbol           | Description                                 | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |

|------------------|---------------------------------------------|------|-------------------|------|------|-------|

| I <sub>IND</sub> | Input leakage current, digital pins         |      |                   |      |      | 4, 5  |

|                  | • V <sub>DD</sub> < V <sub>IN</sub> < 5.5 V | _    | 1                 | 50   | μA   |       |

| Z <sub>IND</sub> | Input impedance examples, digital pins      |      |                   |      |      | 4, 7  |

|                  | • V <sub>DD</sub> = 3.6 V                   | _    | —                 | 48   | kΩ   |       |

|                  | • V <sub>DD</sub> = 3.0 V                   | _    | —                 | 55   | kΩ   |       |

|                  | • V <sub>DD</sub> = 2.5 V                   | _    | —                 | 57   | kΩ   |       |

|                  | • V <sub>DD</sub> = 1.7 V                   | _    | _                 | 85   | kΩ   |       |

| R <sub>PU</sub>  | Internal pullup resistors                   | 20   | 35                | 50   | kΩ   | 8     |

| R <sub>PD</sub>  | Internal pulldown resistors                 | 20   | 35                | 50   | kΩ   | 9     |

### Table 4. Voltage and current operating behaviors (continued)

- 1. Typical values characterized at  $25^{\circ}$ C and VDD = 3.6 V unless otherwise noted.

- 2. Open drain outputs must be pulled to  $V_{\text{DD}}$ .

- 3. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

- 4. Digital pins have an associated GPIO port function and have 5V tolerant inputs, except EXTAL and XTAL.

- 5. Internal pull-up/pull-down resistors disabled.

- 6. Characterized, not tested in production.

- 7. Examples calculated using  $V_{IL}$  relation,  $V_{DD}$ , and max  $I_{IND}$ :  $Z_{IND}=V_{IL}/I_{IND}$ . This is the impedance needed to pull a high signal to a level below  $V_{IL}$  due to leakage when  $V_{IL} < V_{IN} < V_{DD}$ . These examples assume signal source low = 0 V.

- 8. Measured at V<sub>DD</sub> supply voltage = V<sub>DD</sub> min and Vinput = V<sub>SS</sub>

- 9. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{DD}$

### 5.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 100 MHz

- Bus clock = 50 MHz

- FlexBus clock = 50 MHz

- Flash clock = 25 MHz

- MCG mode: FEI

- 2.  $V_{DD} = 3.3 \text{ V}, T_A = 25 \text{ °C}, f_{OSC} = 12 \text{ MHz} \text{ (crystal)}, f_{SYS} = 96 \text{ MHz}, f_{BUS} = 48 \text{ MHz}$

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

### 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 5.2.8 Capacitance attributes

### Table 8. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | _    | 7    | pF   |

# 5.3 Switching specifications

### 5.3.1 Device clock specifications

### Table 9. Device clock specifications

| Symbol               | Description                                            | Min. | Max. | Unit | Notes |  |  |  |  |

|----------------------|--------------------------------------------------------|------|------|------|-------|--|--|--|--|

|                      | Normal run mode                                        |      |      |      |       |  |  |  |  |

| f <sub>SYS</sub>     | System and core clock                                  | —    | 100  | MHz  |       |  |  |  |  |

| f <sub>SYS_USB</sub> | System and core clock when Full Speed USB in operation | 20   | _    | MHz  |       |  |  |  |  |

| f <sub>ENET</sub>    | System and core clock when ethernet in operation       |      |      | MHz  |       |  |  |  |  |

|                      | • 10 Mbps                                              | 5    | —    |      |       |  |  |  |  |

|                      | • 100 Mbps                                             | 50   | _    |      |       |  |  |  |  |

| f <sub>BUS</sub>     | Bus clock                                              | _    | 50   | MHz  |       |  |  |  |  |

| FB_CLK               | FlexBus clock                                          | _    | 50   | MHz  |       |  |  |  |  |

| f <sub>FLASH</sub>   | Flash clock                                            | —    | 25   | MHz  |       |  |  |  |  |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | —    | 25   | MHz  |       |  |  |  |  |

# 5.4.1 Thermal operating requirements

Table 11.

Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| TJ             | Die junction temperature | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   |

# 5.4.2 Thermal attributes

| Board type        | Symbol            | Description                                                                                                       | 100 LQFP | Unit | Notes |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|----------|------|-------|

| Single-layer (1s) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)                                             | 47       | °C/W | 1     |

| Four-layer (2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)                                             | 35       | °C/W | 1     |

| Single-layer (1s) | R <sub>θJMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed)                                        | 37       | °C/W | 1     |

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed)                                        | 29       | °C/W | 1     |

| _                 | R <sub>θJB</sub>  | Thermal<br>resistance, junction<br>to board                                                                       | 20       | °C/W | 2     |

| _                 | R <sub>θJC</sub>  | Thermal<br>resistance, junction<br>to case                                                                        | 9        | °C/W | 3     |

| _                 | Ψ <sub>JT</sub>   | Thermal<br>characterization<br>parameter, junction<br>to package top<br>outside center<br>(natural<br>convection) | 2        | °C/W | 4     |

- 1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

Peripheral operating requirements and behaviors

## 6.4.1.5 Write endurance to FlexRAM for EEPROM

When the FlexNVM partition code is not set to full data flash, the EEPROM data set size can be set to any of several non-zero values.

The bytes not assigned to data flash via the FlexNVM partition code are used by the flash memory module to obtain an effective endurance increase for the EEPROM data. The built-in EEPROM record management system raises the number of program/erase cycles that can be attained prior to device wear-out by cycling the EEPROM data through a larger EEPROM NVM storage space.

While different partitions of the FlexNVM are available, the intention is that a single choice for the FlexNVM partition code and EEPROM data set size is used throughout the entire lifetime of a given application. The EEPROM endurance equation and graph shown below assume that only one configuration is ever used.

$Writes\_subsystem = \frac{EEPROM - 2 \times EEESPLIT \times EEESIZE}{EEESPLIT \times EEESIZE} \times Write\_efficiency \times n_{nvmcycd}$

where

- Writes\_subsystem minimum number of writes to each FlexRAM location for subsystem (each subsystem can have different endurance)

- EEPROM allocated FlexNVM for each EEPROM subsystem based on DEPART; entered with the Program Partition command

- EEESPLIT FlexRAM split factor for subsystem; entered with the Program Partition command

- EEESIZE allocated FlexRAM based on DEPART; entered with the Program Partition command

- Write\_efficiency

- 0.25 for 8-bit writes to FlexRAM

- 0.50 for 16-bit or 32-bit writes to FlexRAM

- n<sub>nvmcycd</sub> data flash cycling endurance (the following graph assumes 10,000 cycles)

2. Specification is valid for all FB\_AD[31:0] and FB\_TA.

Table 26. Flexbus full voltage range switching specifications

| Num | Description                             | Min.     | Max.   | Unit | Notes |

|-----|-----------------------------------------|----------|--------|------|-------|

|     | Operating voltage                       | 1.71     | 3.6    | V    |       |

|     | Frequency of operation                  | —        | FB_CLK | MHz  |       |

| FB1 | Clock period                            | 1/FB_CLK | _      | ns   |       |

| FB2 | Address, data, and control output valid | —        | 13.5   | ns   | 1     |

| FB3 | Address, data, and control output hold  | 0        | _      | ns   | 1     |

| FB4 | Data and FB_TA input setup              | 13.7     | _      | ns   | 2     |

| FB5 | Data and FB_TA input hold               | 0.5      | —      | ns   | 2     |

1. Specification is valid for all FB\_AD[31:0], FB\_BE/BWEn, FB\_CSn, FB\_OE, FB\_R/W, FB\_TBST, FB\_TSIZ[1:0], FB\_ALE, and FB\_TS.

2. Specification is valid for all FB\_AD[31:0] and  $\overline{\text{FB}_{-}\text{TA}}.$

#### Peripheral operating requirements and behaviors

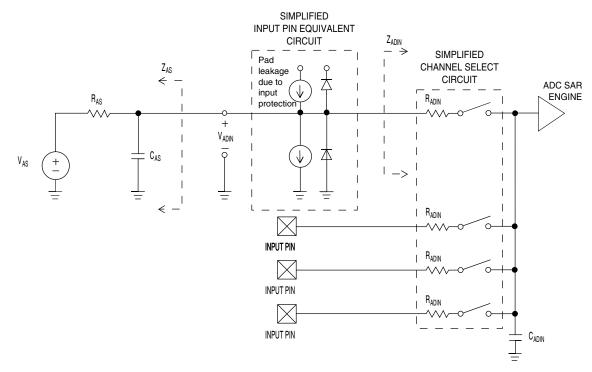

| Symbol            | Description         | Conditions                                                       | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|-------------------|---------------------|------------------------------------------------------------------|--------|-------------------|---------|------|-------|

| C <sub>rate</sub> | ADC conversion rate | 16-bit mode                                                      |        |                   |         |      | 5     |

|                   | Tale                | No ADC hardware averaging                                        | 37.037 | —                 | 461.467 | Ksps |       |

|                   |                     | Continuous conversions<br>enabled, subsequent<br>conversion time |        |                   |         |      |       |

Table 27. 16-bit ADC operating conditions (continued)

- 1. Typical values assume  $V_{DDA}$  = 3.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8 Ω analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.</li>

- 4. To use the maximum ADC conversion clock frequency, the ADHSC bit must be set and the ADLPC bit must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

Figure 13. ADC input impedance equivalency diagram

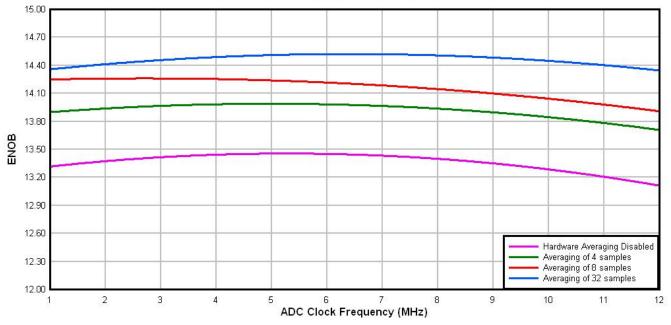

### 6.6.1.2 16-bit ADC electrical characteristics Table 28. 16-bit ADC characteristics (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> = V<sub>SSA</sub>)

| Symbol               | Description    | Conditions <sup>1</sup> | Min.  | Typ. <sup>2</sup> | Max. | Unit | Notes |

|----------------------|----------------|-------------------------|-------|-------------------|------|------|-------|

| I <sub>DDA_ADC</sub> | Supply current |                         | 0.215 |                   | 1.7  | mA   | 3     |

Table continues on the next page ...

#### Peripheral operating requirements and behaviors

| Symbol              | Description            | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup>      | Max. | Unit  | Notes                                                                     |

|---------------------|------------------------|-------------------------------------------------|------|------------------------|------|-------|---------------------------------------------------------------------------|

| E <sub>IL</sub>     | Input leakage<br>error |                                                 |      | $I_{ln} \times R_{AS}$ |      | mV    | I <sub>In</sub> =<br>leakage<br>current                                   |

|                     |                        |                                                 |      |                        |      |       | (refer to<br>the MCU's<br>voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor<br>slope   | Across the full temperature range of the device | 1.55 | 1.62                   | 1.69 | mV/°C |                                                                           |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage | 25 °C                                           | 706  | 716                    | 726  | mV    |                                                                           |

### Table 28. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and the ADLPC bit (low power). For lowest power operation the ADLPC bit must be set, the HSC bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

| Symbol               | Description                                   | Conditions                            | Min. | Typ. <sup>1</sup>                                                                          | Max. | Unit                                 | Notes                                                                  |

|----------------------|-----------------------------------------------|---------------------------------------|------|--------------------------------------------------------------------------------------------|------|--------------------------------------|------------------------------------------------------------------------|

| G                    | Gain <sup>4</sup>                             | • PGAG=0                              | 0.95 | 1                                                                                          | 1.05 |                                      | R <sub>AS</sub> < 100Ω                                                 |

|                      |                                               | • PGAG=1                              | 1.9  | 2                                                                                          | 2.1  |                                      |                                                                        |

|                      |                                               | • PGAG=2                              | 3.8  | 4                                                                                          | 4.2  |                                      |                                                                        |

|                      |                                               | • PGAG=3                              | 7.6  | 8                                                                                          | 8.4  |                                      |                                                                        |

|                      |                                               | • PGAG=4                              | 15.2 | 16                                                                                         | 16.6 |                                      |                                                                        |

|                      |                                               | • PGAG=5                              | 30.0 | 31.6                                                                                       | 33.2 |                                      |                                                                        |

|                      |                                               | • PGAG=6                              | 58.8 | 63.3                                                                                       | 67.8 |                                      |                                                                        |

| BW                   | Input signal                                  | 16-bit modes                          |      |                                                                                            | 4    | kHz                                  |                                                                        |

|                      | bandwidth                                     | <ul> <li>&lt; 16-bit modes</li> </ul> | _    | _                                                                                          | 40   | kHz                                  |                                                                        |

| PSRR                 | Power supply rejection ratio                  | Gain=1                                | _    | -84                                                                                        |      | dB                                   | V <sub>DDA</sub> = 3V<br>±100mV,<br>f <sub>VDDA</sub> = 50Hz,<br>60Hz  |

| CMRR                 | Common mode                                   | Gain=1                                | _    | -84                                                                                        | _    | dB                                   | V <sub>CM</sub> =                                                      |

|                      | rejection ratio                               | • Gain=64                             | _    | -85                                                                                        | _    | dB                                   | 500mVpp,<br>f <sub>VCM</sub> = 50Hz,<br>100Hz                          |

| V <sub>OFS</sub>     | Input offset<br>voltage                       |                                       | _    | 0.2                                                                                        | —    | mV                                   | Output offset =<br>V <sub>OFS</sub> *(Gain+1)                          |

| T <sub>GSW</sub>     | Gain switching settling time                  |                                       | —    | -                                                                                          | 10   | μs                                   | 5                                                                      |

| EIL                  | Input leakage All modes<br>error              |                                       |      | $I_{In} \times R_{AS}$                                                                     | mV   | I <sub>In</sub> = leakage<br>current |                                                                        |

|                      |                                               |                                       |      |                                                                                            |      |                                      | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

| V <sub>PP,DIFF</sub> | Maximum<br>differential input<br>signal swing |                                       |      | $\frac{V_{x}V_{\text{DDA}} - V_{x}}{\text{Gain}}$ $\mathbf{x} = \mathbf{V}_{\text{REFPG}}$ | )    | V                                    | 6                                                                      |

| SNR                  | Signal-to-noise                               | Gain=1                                | 80   | 90                                                                                         |      | dB                                   | 16-bit                                                                 |

| eru i                | ratio                                         | • Gain=64                             | 52   | 66                                                                                         | _    | dB                                   | differential<br>mode,<br>Average=32                                    |

| THD                  | Total harmonic                                | Gain=1                                | 85   | 100                                                                                        |      | dB                                   | 16-bit                                                                 |

|                      | distortion                                    | • Gain=64                             | 49   | 95                                                                                         | _    | dB                                   | differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz         |

| SFDR                 | Spurious free                                 | Gain=1                                | 85   | 105                                                                                        |      | dB                                   | 16-bit                                                                 |

|                      | dynamic range                                 | • Gain=64                             | 53   | 88                                                                                         |      | dB                                   | differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz         |

### Table 30. 16-bit ADC with PGA characteristics (continued)

Table continues on the next page...

| Symbol | Description                                 | Conditions                             | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes                                     |

|--------|---------------------------------------------|----------------------------------------|------|-------------------|------|------|-------------------------------------------|

| ENOB   | Effective number                            | Gain=1, Average=4                      | 11.6 | 13.4              | —    | bits | 16-bit                                    |

|        | of bits                                     | • Gain=64, Average=4                   | 7.2  | 9.6               | _    | bits | differential mode, f <sub>in</sub> =100Hz |

|        |                                             | <ul> <li>Gain=1, Average=32</li> </ul> | 12.8 | 14.5              |      | bits |                                           |

|        |                                             | Gain=2, Average=32                     | 11.0 | 14.3              |      | bits |                                           |

|        |                                             | Gain=4, Average=32                     | 7.9  | 13.8              | _    | bits |                                           |

|        |                                             | Gain=8, Average=32                     | 7.3  | 13.1              | _    | bits |                                           |

|        |                                             | Gain=16, Average=32                    | 6.8  | 12.5              |      | bits |                                           |

|        |                                             | Gain=32, Average=32                    | 6.8  | 11.5              | _    | bits |                                           |

|        |                                             | • Gain=64, Average=32                  | 7.5  | 10.6              | _    | bits |                                           |

| SINAD  | Signal-to-noise<br>plus distortion<br>ratio | See ENOB                               | 6.02 | × ENOB +          | 1.76 | dB   |                                           |

Table 30. 16-bit ADC with PGA characteristics (continued)

1. Typical values assume V\_{DDA} =3.0V, Temp=25°C, f\_{ADCK}=6MHz unless otherwise stated.

- 2. This current is a PGA module adder, in addition to ADC conversion currents.

- Between IN+ and IN-. The PGA draws a DC current from the input terminals. The magnitude of the DC current is a strong function of input common mode voltage (V<sub>CM</sub>) and the PGA gain.

- 4. Gain =  $2^{PGAG}$

- 5. After changing the PGA gain setting, a minimum of 2 ADC+PGA conversions should be ignored.

- 6. Limit the input signal swing so that the PGA does not saturate during operation. Input signal swing is dependent on the PGA reference voltage and gain setting.

# 6.6.2 CMP and 6-bit DAC electrical specifications

### Table 31. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                        | Min.                  | Тур. | Max.            | Unit |

|--------------------|----------------------------------------------------|-----------------------|------|-----------------|------|

| V <sub>DD</sub>    | Supply voltage                                     | 1.71                  | _    | 3.6             | V    |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)    | —                     | _    | 200             | μA   |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)     | —                     | _    | 20              | μA   |

| V <sub>AIN</sub>   | Analog input voltage                               | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>   | Analog input offset voltage                        | —                     | _    | 20              | mV   |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>          |                       |      |                 |      |

|                    | • CR0[HYSTCTR] = 00                                | _                     | 5    | _               | mV   |

|                    | • CR0[HYSTCTR] = 01                                | _                     | 10   | _               | mV   |

|                    | • CR0[HYSTCTR] = 10                                | _                     | 20   | _               | mV   |

|                    | • CR0[HYSTCTR] = 11                                | —                     | 30   | _               | mV   |

| V <sub>CMPOh</sub> | Output high                                        | V <sub>DD</sub> – 0.5 | _    | _               | V    |

| V <sub>CMPOI</sub> | Output low                                         | —                     | _    | 0.5             | V    |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1) | 20                    | 50   | 200             | ns   |

Table continues on the next page...

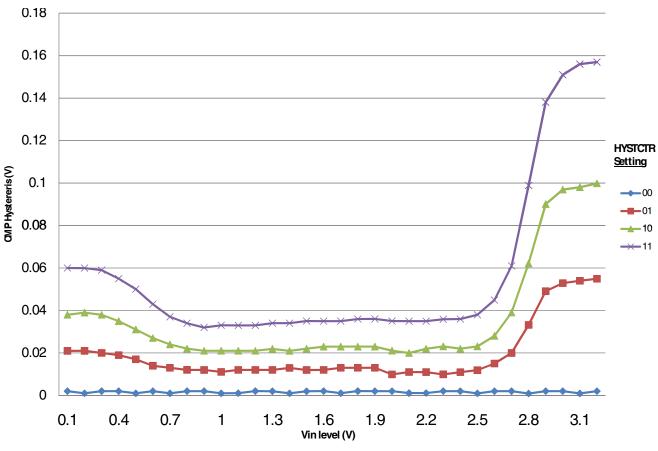

Peripheral operating requirements and behaviors

Figure 17. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=1)

### 6.6.3 12-bit DAC electrical characteristics

### 6.6.3.1 12-bit DAC operating requirements Table 32. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min.  | Max.                    | Unit | Notes |

|-------------------|-------------------------|-------|-------------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71  | 3.6                     | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13  | 3.6                     | V    | 1     |

| T <sub>A</sub>    | Temperature             |       | emperature<br>he device | °C   |       |

| CL                | Output load capacitance | — 100 |                         | pF   | 2     |

| ١L                | Output load current     | —     | 1                       | mA   |       |

1. The DAC reference can be selected to be V<sub>DDA</sub> or the voltage output of the VREF module (VREF\_OUT)

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

### 6.6.3.2 12-bit DAC operating behaviors Table 33. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                         | Min. | Тур.     | Max.              | Unit   | Notes |

|----------------------------|-------------------------------------------------------------------------------------|------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub><br>P | Supply current — low-power mode                                                     |      | —        | 150               | μΑ     |       |

| I <sub>DDA_DACH</sub><br>P | Supply current — high-speed mode                                                    | _    | —        | 700               | μΑ     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) — low-power mode                          |      | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                         | _    | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to 0xC08)<br>— low-power mode and high-speed mode | _    | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-speed mode, no load, DAC set to 0x000           | _    | —        | 100               | mV     |       |

| V <sub>dacouth</sub>       | speed mode, no load, DAC set to 0xFFF                                               |      | —        | V <sub>DACR</sub> | mV     |       |

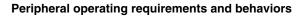

| INL                        | Integral non-linearity error — high speed mode                                      | _    | —        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — $V_{DACR} > 2$<br>V                              | —    | —        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                     | _    | —        | ±1                | LSB    | 4     |

| V <sub>OFFSET</sub>        | Offset error                                                                        | —    | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                          | _    | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, $V_{DDA} \ge 2.4 \text{ V}$                           | 60   | —        | 90                | dB     |       |

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                              | _    | 3.7      | _                 | μV/C   | 6     |

| $T_{GE}$                   | Temperature coefficient gain error                                                  | —    | 0.000421 | —                 | %FSR/C |       |

| Rop                        | Output resistance load = 3 k $\Omega$                                               |      | —        | 250               | Ω      |       |

| SR                         | Slew rate -80h→ F7Fh→ 80h                                                           |      |          |                   | V/µs   |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                    | 1.2  | 1.7      | —                 |        |       |

|                            | <ul> <li>Low power (SP<sub>LP</sub>)</li> </ul>                                     | 0.05 | 0.12     | —                 |        |       |

| СТ                         | Channel to channel cross talk                                                       |      |          | -80               | dB     |       |

| BW                         | 3dB bandwidth                                                                       |      |          |                   | kHz    |       |

|                            | • High power (SP <sub>HP</sub> )                                                    | 550  | _        | _                 |        |       |

|                            | <ul> <li>Low power (SP<sub>LP</sub>)</li> </ul>                                     | 40   | _        | _                 |        |       |

1. Settling within ±1 LSB

- 2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 3. The DNL is measured for 0 + 100 mV to  $V_{\text{DACR}}$  –100 mV

- 4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V

- 5. Calculated by a best fit curve from V\_{SS} + 100 mV to V\_{DACR} 100 mV

- V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

Figure 18. Typical INL error vs. digital code

6.  $C_b$  = total capacitance of the one bus line in pF.

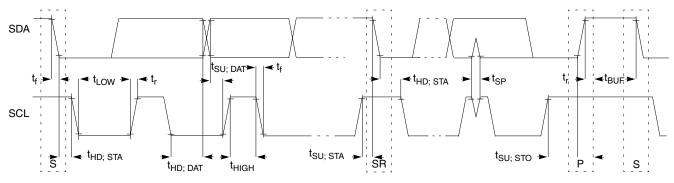

Figure 26. Timing definition for fast and standard mode devices on the I<sup>2</sup>C bus

# 6.8.9 UART switching specifications

See General switching specifications.

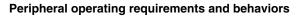

### 6.8.10 SDHC specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

| Num | Symbol                                     | Description                                     | Min.          | Max.      | Unit |

|-----|--------------------------------------------|-------------------------------------------------|---------------|-----------|------|

|     |                                            | Card input clock                                |               |           |      |

| SD1 | fpp                                        | Clock frequency (low speed)                     | 0             | 400       | kHz  |

|     | fpp                                        | Clock frequency (SD\SDIO full speed\high speed) | 0             | 25\50     | MHz  |

|     | fpp                                        | Clock frequency (MMC full speed\high speed)     | 0             | 20\50     | MHz  |

|     | f <sub>OD</sub>                            | Clock frequency (identification mode)           | 0             | 400       | kHz  |

| SD2 | t <sub>WL</sub>                            | Clock low time                                  | 7             | —         | ns   |

| SD3 | t <sub>WH</sub>                            | Clock high time                                 | 7             | —         | ns   |

| SD4 | t <sub>TLH</sub>                           | Clock rise time                                 | _             | 3         | ns   |

| SD5 | t <sub>THL</sub>                           | Clock fall time                                 | _             | 3         | ns   |

|     |                                            | SDHC output / card inputs SDHC_CMD, SDHC_DAT    | (reference to | SDHC_CLK) |      |

| SD6 | t <sub>OD</sub>                            | SDHC output delay (output valid)                | -5            | 8.3       | ns   |

|     |                                            | SDHC input / card inputs SDHC_CMD, SDHC_DAT (   | reference to  | SDHC_CLK) |      |

| SD7 | SD7 t <sub>ISU</sub> SDHC input setup time |                                                 | 5             | —         | ns   |

| SD8 | t <sub>IH</sub>                            | SDHC input hold time                            | 0             | —         | ns   |

Table 47. SDHC switching specifications

Figure 27. SDHC timing

### 6.8.11 I<sup>2</sup>S switching specifications

This section provides the AC timings for the I<sup>2</sup>S in master (clocks driven) and slave modes (clocks input). All timings are given for non-inverted serial clock polarity (TCR[TSCKP] = 0, RCR[RSCKP] = 0) and a non-inverted frame sync (TCR[TFSI] = 0, RCR[RFSI] = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timings remain valid by inverting the clock signal (I2S\_BCLK) and/or the frame sync (I2S\_FS) shown in the figures below.

| Num | Description                                | Min.                 | Max. | Unit        |

|-----|--------------------------------------------|----------------------|------|-------------|

|     | Operating voltage                          | 2.7                  | 3.6  | V           |

| S1  | I2S_MCLK cycle time                        | 2 x t <sub>SYS</sub> |      | ns          |

| S2  | I2S_MCLK pulse width high/low              | 45%                  | 55%  | MCLK period |

| S3  | I2S_BCLK cycle time                        | 5 x t <sub>SYS</sub> | —    | ns          |

| S4  | I2S_BCLK pulse width high/low              | 45%                  | 55%  | BCLK period |

| S5  | I2S_BCLK to I2S_FS output valid            | —                    | 15   | ns          |

| S6  | I2S_BCLK to I2S_FS output invalid          | -2.5                 | —    | ns          |

| S7  | I2S_BCLK to I2S_TXD valid                  | —                    | 15   | ns          |

| S8  | I2S_BCLK to I2S_TXD invalid                | -3                   | —    | ns          |

| S9  | I2S_RXD/I2S_FS input setup before I2S_BCLK | 20                   | —    | ns          |

| S10 | I2S_RXD/I2S_FS input hold after I2S_BCLK   | 0                    | —    | ns          |

Table 48. I<sup>2</sup>S master mode timing (limited voltage range)

| 100<br>LQFP | Pin Name                                         | Default                                          | ALTO                                             | ALT1             | ALT2        | ALT3        | ALT4                | ALT5 | ALT6       | ALT7                   | EzPort   |

|-------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------|-------------|-------------|---------------------|------|------------|------------------------|----------|

| 14          | ADC0_DP1                                         | ADC0_DP1                                         | ADC0_DP1                                         |                  |             |             |                     |      |            |                        |          |

| 15          | ADC0_DM1                                         | ADC0_DM1                                         | ADC0_DM1                                         |                  |             |             |                     |      |            |                        |          |

| 16          | ADC1_DP1                                         | ADC1_DP1                                         | ADC1_DP1                                         |                  |             |             |                     |      |            |                        |          |

| 17          | ADC1_DM1                                         | ADC1_DM1                                         | ADC1_DM1                                         |                  |             |             |                     |      |            |                        |          |

| 18          | PGA0_DP/<br>ADC0_DP0/<br>ADC1_DP3                | PGA0_DP/<br>ADC0_DP0/<br>ADC1_DP3                | PGA0_DP/<br>ADC0_DP0/<br>ADC1_DP3                |                  |             |             |                     |      |            |                        |          |

| 19          | PGA0_DM/<br>ADC0_DM0/<br>ADC1_DM3                | PGA0_DM/<br>ADC0_DM0/<br>ADC1_DM3                | PGA0_DM/<br>ADC0_DM0/<br>ADC1_DM3                |                  |             |             |                     |      |            |                        |          |

| 20          | PGA1_DP/<br>ADC1_DP0/<br>ADC0_DP3                | PGA1_DP/<br>ADC1_DP0/<br>ADC0_DP3                | PGA1_DP/<br>ADC1_DP0/<br>ADC0_DP3                |                  |             |             |                     |      |            |                        |          |

| 21          | PGA1_DM/<br>ADC1_DM0/<br>ADC0_DM3                | PGA1_DM/<br>ADC1_DM0/<br>ADC0_DM3                | PGA1_DM/<br>ADC1_DM0/<br>ADC0_DM3                |                  |             |             |                     |      |            |                        |          |

| 22          | VDDA                                             | VDDA                                             | VDDA                                             |                  |             |             |                     |      |            |                        |          |

| 23          | VREFH                                            | VREFH                                            | VREFH                                            |                  |             |             |                     |      |            |                        |          |

| 24          | VREFL                                            | VREFL                                            | VREFL                                            |                  |             |             |                     |      |            |                        |          |

| 25          | VSSA                                             | VSSA                                             | VSSA                                             |                  |             |             |                     |      |            |                        |          |

| 26          | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 |                  |             |             |                     |      |            |                        |          |

| 27          | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              |                  |             |             |                     |      |            |                        |          |

| 28          | XTAL32                                           | XTAL32                                           | XTAL32                                           |                  |             |             |                     |      |            |                        |          |

| 29          | EXTAL32                                          | EXTAL32                                          | EXTAL32                                          |                  |             |             |                     |      |            |                        |          |

| 30          | VBAT                                             | VBAT                                             | VBAT                                             |                  |             |             |                     |      |            |                        |          |

| 31          | PTE24                                            | ADC0_SE17                                        | ADC0_SE17                                        | PTE24            | CAN1_TX     | UART4_TX    |                     |      | EWM_OUT_b  |                        |          |

| 32          | PTE25                                            | ADC0_SE18                                        | ADC0_SE18                                        | PTE25            | CAN1_RX     | UART4_RX    |                     |      | EWM_IN     |                        |          |

| 33          | PTE26                                            | DISABLED                                         |                                                  | PTE26            |             | UART4_CTS_b | ENET_1588_<br>CLKIN |      | RTC_CLKOUT | USB_CLKIN              |          |

| 34          | PTAO                                             | JTAG_TCLK/<br>SWD_CLK/<br>EZP_CLK                | TSI0_CH1                                         | PTA0             | UARTO_CTS_b | FTM0_CH5    |                     |      |            | JTAG_TCLK/<br>SWD_CLK  | EZP_CLK  |

| 35          | PTA1                                             | JTAG_TDI/<br>EZP_DI                              | TSI0_CH2                                         | PTA1             | UARTO_RX    | FTM0_CH6    |                     |      |            | JTAG_TDI               | EZP_DI   |

| 36          | PTA2                                             | JTAG_TDO/<br>TRACE_SWO/<br>EZP_DO                | TSI0_CH3                                         | PTA2             | UARTO_TX    | FTM0_CH7    |                     |      |            | JTAG_TDO/<br>TRACE_SWO | EZP_DO   |

| 37          | PTA3                                             | JTAG_TMS/<br>SWD_DIO                             | TSI0_CH4                                         | PTA3             | UARTO_RTS_b | FTM0_CH0    |                     |      |            | JTAG_TMS/<br>SWD_DIO   |          |

| 38          | PTA4/<br>LLWU_P3                                 | NMI_b/<br>EZP_CS_b                               | TSI0_CH5                                         | PTA4/<br>LLWU_P3 |             | FTM0_CH1    |                     |      |            | NMI_b                  | EZP_CS_b |

#### **Revision History**

| Rev. No. | Date   | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | 3/2011 | Added sections that were inadvertently removed in previous revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4        | 3/2011 | Reworded I <sub>IC</sub> footnote in "Voltage and Current Operating Requirements" table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |        | Added paragraph to "Peripheral operating requirements and behaviors" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |        | Added "JTAG full voltage range electricals" table to the "JTAG electricals" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5        | 6/2011 | <ul> <li>Changed supported part numbers per new part number scheme</li> <li>Changed <i>DC injection current</i> specs in "Voltage and current operating requirements" table</li> <li>Changed <i>Input leakage current</i> and <i>internal pullup/pulldown resistor</i> specs in "Voltage and current operating behaviors" table</li> <li>Split <i>Low power stop mode current</i> specs by temperature range in "Power consumption operating behaviors" table</li> <li>Changed typical <i>I<sub>DD</sub> v<sub>BAT</sub></i> spec in "Power consumption operating behaviors" table</li> <li>Added ENET and LPTMR clock specs to "Device clock specifications" table</li> <li>Changed <i>PLL operating current</i> in "MCG specifications" table</li> <li>Changed <i>PLL operating current</i> in "MCG specifications" table</li> <li>Changed <i>Crystal startup time</i> in "Oscillator DC electrical specifications" table</li> <li>Changed <i>Crystal startup</i> time in "Scillator Trequency specifications" table</li> <li>Changed <i>Crystal startup</i> time in "Scillator Trequency specifications" table</li> <li>Changed <i>Crystal startup</i> time in "Scillator Trequency specifications" table</li> <li>Changed <i>Crystal startup</i> time in "Scillator Trequency specifications" table</li> <li>Changed <i>Crystal startup</i> time in "Carl switching specifications" table</li> <li>Changed <i>Aloc asynchronous clock source</i> specs in "16-bit ADC characteristics" table</li> <li>Changed <i>Aloc asynchronous clock source</i> specs in "16-bit ADC with PGA characteristics" table</li> <li>Changed <i>Analog comparator initialization delay</i> in "Comparator and 6-bit DAC electrical specifications" table</li> <li>Changed <i>Analog comparator initialization delay</i> in "Comparator and 6-bit DAC electrical specifications" table</li> <li>Changed <i>Analog comparator initialization delay</i> in "Comparator and 6-bit DAC electrical specifications" table</li> <li>Changed <i>Analog comparator initialization delay</i> in "Comparator and 6-bit DAC electrical specifications" table</li> <li>Changed <i>Analog</i></li></ul> |

### Table 53. Revision History (continued)

Table continues on the next page...

| Rev. No. | Date    | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

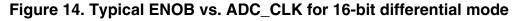

| 6        | 01/2012 | <ul> <li>Added AC electrical specifications.</li> <li>Replaced TBDs with silicon data throughout.</li> <li>In "Power mode transition operating behaviors" table, removed entry times.</li> <li>Updated "EMC radiated emissions operating behaviors" to remove SAE level and also added data for 144LQFP.</li> <li>Clarified "EP7" in "EzPort switching specifications" table and "EzPort Timing Diagram".</li> <li>Added "ENOB vs. ADC_CLK for 16-bit differential and 16-bit single-ended modes" figures.</li> <li>Updated I<sub>DD_RUN</sub> numbers in 'Power consumption operating behaviors' section.</li> <li>Clarified 'Diagram: Typical IDD_RUN operating behavior' section and updated 'Run mode supply current vs. core frequency — all peripheral clocks disabled' figure.</li> <li>In 'Voltage reference electrical specifications' section, updated V<sub>DP_SRC</sub>, I<sub>DDstby</sub>, and 'V<sub>Reg33out</sub> values.</li> </ul> |

| 7        | 02/2013 | <ul> <li>In "ESD handling ratings", added a note for I<sub>LAT</sub>.</li> <li>Updated "Voltage and current operating requirements".</li> <li>Updated "Voltage and current operating behaviors".</li> <li>Updated "Power mode transition operating behaviors".</li> <li>Updated "EMC radiated emissions operating behaviors" to add MAPBGA data.</li> <li>In "MCG specifications", updated the description of f<sub>ints_t</sub>.</li> <li>In "16-bit ADC operating conditions", updated the max spec of V<sub>ADIN</sub>.</li> <li>In "16-bit ADC electrical characteristics", updated the temp sensor slope and voltage specs.</li> <li>Updated "I2C switching specifications".</li> <li>In "SDHC specifications", removed the operating voltage limits and updated the SD1 and SD6 specs.</li> <li>In "I2S switching specifications", added separate specification tables for the full operating voltage range.</li> </ul>                         |

### Table 53. Revision History (continued)