Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | ARM® Cortex®-M4/M0                                                                |

| Core Size                  | 32-Bit Dual-Core                                                                  |

| Speed                      | 204MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 49                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 16K x 8                                                                           |

| RAM Size                   | 104К х 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 4x10b; D/A 1x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TFBGA                                                                         |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4312jet100e            |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 32-bit ARM Cortex-M4/M0 microcontroller

- Cortex-M0 Processor core

- ARM Cortex-M0 co-processor (version r0p0) capable of off-loading the main ARM Cortex-M4 application processor.

- ◆ Running at frequencies of up to 204 MHz.

- ♦ JTAG

- Built-in NVIC.

- On-chip memory

- ♦ Up to 1 MB on-chip dual bank flash memory with flash accelerator.

- ◆ 16 kB on-chip EEPROM data memory.

- ◆ 136 kB SRAM for code and data use.

- Multiple SRAM blocks with separate bus access. Two SRAM blocks can be powered down individually.

- ♦ 64 kB ROM containing boot code and on-chip software drivers.

- 64 bit+ 256 bit of One-Time Programmable (OTP) memory for general-purpose use.

- Configurable digital peripherals

- ◆ Serial GPIO (SGPIO) interface.

- ◆ State Configurable Timer (SCTimer/PWM) subsystem on AHB.

- Global Input Multiplexer Array (GIMA) allows to cross-connect multiple inputs and outputs to event driven peripherals like the timers, SCTimer/PWM, and ADC0/1.

- Serial interfaces

- ◆ Quad SPI Flash Interface (SPIFI) with four lanes and up to 52 MB per second.

- 10/100T Ethernet MAC with RMII and MII interfaces and DMA support for high throughput at low CPU load. Support for IEEE 1588 time stamping/advanced time stamping (IEEE 1588-2008 v2).

- One High-speed USB 2.0 Host/Device/OTG interface with DMA support and on-chip high-speed PHY.

- One High-speed USB 2.0 Host/Device interface with DMA support, on-chip full-speed PHY and ULPI interface to external high-speed PHY.

- ♦ USB interface electrical test software included in ROM USB stack.

- One 550 UART with DMA support and full modem interface.

- Three 550 USARTs with DMA and synchronous mode support and a smart card interface conforming to ISO7816 specification. One USART with IrDA interface.

- Up to two C\_CAN 2.0B controllers with one channel each.

- Two SSP controllers with FIFO and multi-protocol support. Both SSPs with DMA support.

- One SPI controller.

- One Fast-mode Plus I<sup>2</sup>C-bus interface with monitor mode and with open-drain I/O pins conforming to the full I<sup>2</sup>C-bus specification. Supports data rates of up to 1 Mbit/s.

- ♦ One standard I<sup>2</sup>C-bus interface with monitor mode and with standard I/O pins.

- ◆ Two I<sup>2</sup>S interfaces, each with DMA support and with one input and one output.

- Digital peripherals

- External Memory Controller (EMC) supporting external SRAM, ROM, NOR flash, and SDRAM devices.

32-bit ARM Cortex-M4/M0 microcontroller

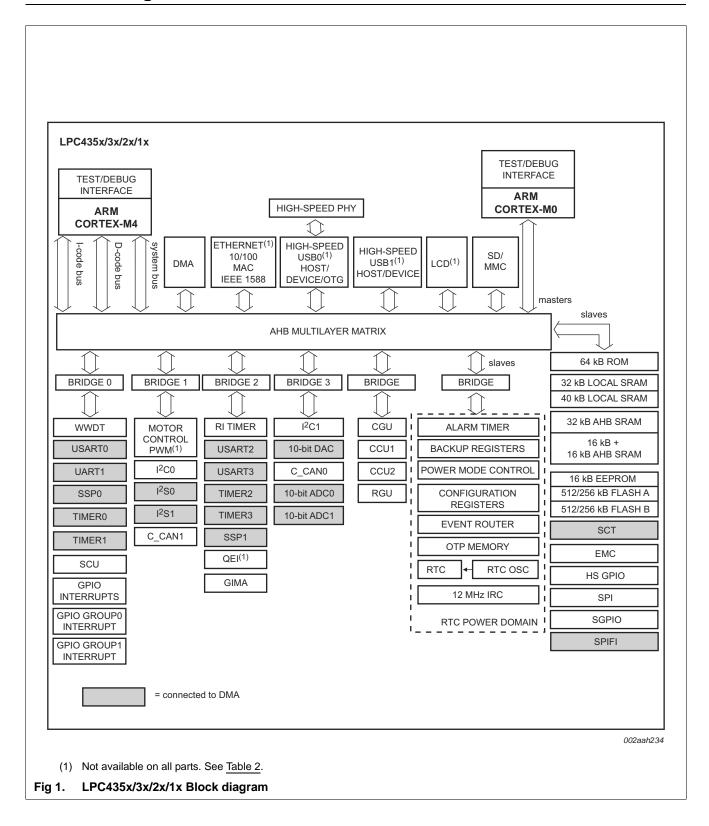

## 5. Block diagram

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Ø    | Description                                                                                                                                                               |

|----------|---------|----------|---------|---------|-----|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | LBG     | TFB      | LQF     | LQF     |     | Res<br>[1]         | Type |                                                                                                                                                                           |

| P1_16    | M7      | H9       | 90      | 64      | [2] | N;                 | I/O  | GPIO0[3] — General purpose digital input/output pin.                                                                                                                      |

|          |         |          |         |         |     | PU                 | I    | U2_RXD — Receiver input for USART2.                                                                                                                                       |

|          |         |          |         |         |     |                    | I/O  | SGPIO3 — General purpose digital input/output pin.                                                                                                                        |

|          |         |          |         |         |     |                    | I    | ENET_CRS — Ethernet Carrier Sense (MII interface).                                                                                                                        |

|          |         |          |         |         |     |                    | 0    | T0_MAT0 — Match output 0 of timer 0.                                                                                                                                      |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|          |         |          |         |         |     |                    | I/O  | EMC_D9 — External memory data line 9.                                                                                                                                     |

|          |         |          |         |         |     |                    | I    | <b>ENET_RX_DV</b> — Ethernet Receive Data Valid (RMII/MII interface).                                                                                                     |

| P1_17    | M8      | H10      | 93      | 66      | [3] | N;                 | I/O  | GPIO0[12] — General purpose digital input/output pin.                                                                                                                     |

|          |         |          |         |         |     | PU                 | I/O  | <b>U2_UCLK</b> — Serial clock input/output for USART2 in synchronous mode.                                                                                                |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|          |         |          |         |         |     |                    | I/O  | ENET_MDIO — Ethernet MIIM data input and output.                                                                                                                          |

|          |         |          |         |         |     |                    | I    | T0_CAP3 — Capture input 3 of timer 0.                                                                                                                                     |

|          |         |          |         |         |     |                    | 0    | CAN1_TD — CAN1 transmitter output.                                                                                                                                        |

|          |         |          |         |         |     |                    | I/O  | SGPI011 — General purpose digital input/output pin.                                                                                                                       |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

| P1_18    | N12     | J10      | 95      | 67      | [2] | N;                 | I/O  | GPIO0[13] — General purpose digital input/output pin.                                                                                                                     |

|          |         |          |         |         |     | PU                 | I/O  | <b>U2_DIR</b> — RS-485/EIA-485 output enable/direction control for USART2.                                                                                                |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|          |         |          |         |         |     |                    | 0    | <b>ENET_TXD0</b> — Ethernet transmit data 0 (RMII/MII interface).                                                                                                         |

|          |         |          |         |         |     |                    | 0    | T0_MAT3 — Match output 3 of timer 0.                                                                                                                                      |

|          |         |          |         |         |     |                    | I    | CAN1_RD — CAN1 receiver input.                                                                                                                                            |

|          |         |          |         |         |     |                    | I/O  | SGPIO12 — General purpose digital input/output pin.                                                                                                                       |

|          |         |          |         |         |     |                    | I/O  | EMC_D10 — External memory data line 10.                                                                                                                                   |

| P1_19    | M11     | К9       | 96      | 68      | [2] | N;<br>PU           | I    | <b>ENET_TX_CLK (ENET_REF_CLK)</b> — Ethernet Transmit<br>Clock (MII interface) or Ethernet Reference Clock (RMII<br>interface).                                           |

|          |         |          |         |         |     |                    | I/O  | SSP1_SCK — Serial clock for SSP1.                                                                                                                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|          |         |          |         |         |     |                    | 0    | CLKOUT — Clock output pin.                                                                                                                                                |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|          |         |          |         |         |     |                    | 0    | I2S0_RX_MCLK — I2S receive master clock.                                                                                                                                  |

|          |         |          |         |         |     |                    | I/O  | <b>I2S1_TX_SCK</b> — Transmit Clock. It is driven by the master<br>and received by the slave. Corresponds to the signal SCK in<br>the I <sup>2</sup> S-bus specification. |

#### Table 3. Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | 0        | Description                                                                                                                                                                                                  |

|----------|---------|----------|---------|---------|-----|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | LBG     | TFB      | LQFI    | LQFI    |     | Rese               | Type     |                                                                                                                                                                                                              |

| P3_5     | C12     | B7       | 173     | 121     | [2] | N;                 | I/O      | GPIO1[15] — General purpose digital input/output pin.                                                                                                                                                        |

|          |         |          |         |         |     | PU                 | -        | R — Function reserved.                                                                                                                                                                                       |

|          |         |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                                       |

|          |         |          |         |         |     |                    | I/O      | SPIFI_SIO2 — I/O lane 2 for SPIFI.                                                                                                                                                                           |

|          |         |          |         |         |     |                    | I        | U1_RXD — Receiver input for UART 1.                                                                                                                                                                          |

|          |         |          |         |         |     |                    | I/O      | <b>I2S0_TX_SDA</b> — I2S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification.                                             |

|          |         |          |         |         |     |                    | I/O      | <b>I2S1_RX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> S-bus specification.                                |

|          |         |          |         |         |     |                    | 0        | LCD_VD12 — LCD data.                                                                                                                                                                                         |

| P3_6     | B13     | C7       | 174     | 122     | [2] | N;                 | I/O      | GPIO0[6] — General purpose digital input/output pin.                                                                                                                                                         |

|          |         |          |         |         |     | PU                 | I/O      | SPI_MISO — Master In Slave Out for SPI.                                                                                                                                                                      |

|          |         |          |         |         |     |                    | I/O      | SSP0_SSEL — Slave Select for SSP0.                                                                                                                                                                           |

|          |         |          |         |         |     |                    | I/O      | <b>SPIFI_MISO</b> — Input 1 in SPIFI quad mode; SPIFI output IO1.                                                                                                                                            |

|          |         |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                                       |

|          |         |          |         |         |     |                    | I/O      | SSP0_MISO — Master In Slave Out for SSP0.                                                                                                                                                                    |

|          |         |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                                       |

|          |         |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                                       |

| P3_7     | C11     | D7       | 176     | 123     | [2] | N;<br>PU           | -        | R — Function reserved.                                                                                                                                                                                       |

|          |         |          |         |         |     | PU                 | I/O      | SPI_MOSI — Master Out Slave In for SPI.                                                                                                                                                                      |

|          |         |          |         |         |     |                    | I/O      | SSP0_MISO — Master In Slave Out for SSP0.                                                                                                                                                                    |

|          |         |          |         |         |     |                    | I/O      | <b>SPIFI_MOSI</b> — Input I0 in SPIFI quad mode; SPIFI output IO0.                                                                                                                                           |

|          |         |          |         |         |     |                    | I/O      | <b>GPIO5[10]</b> — General purpose digital input/output pin.                                                                                                                                                 |

|          |         |          |         |         |     |                    | I/O      | SSP0_MOSI — Master Out Slave in for SSP0.                                                                                                                                                                    |

|          |         |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                                       |

|          |         |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                                       |

| P3_8     | C10     | E7       | 179     | 124     | [2] | N;                 | -        | R — Function reserved.                                                                                                                                                                                       |

|          |         |          |         |         |     | PU                 | I        | <b>SPI_SSEL</b> — Slave Select for SPI. Note that this pin in an input pin only. The SPI in master mode cannot drive the CS input on the slave. Any GPIO pin can be used for SPI chip select in master mode. |

|          |         |          |         |         |     |                    | I/O      | SSP0_MOSI — Master Out Slave in for SSP0.                                                                                                                                                                    |

|          |         |          |         |         |     |                    | I/O      | SPIFI_CS — SPIFI serial flash chip select.                                                                                                                                                                   |

|          |         |          |         |         |     |                    | I/O      | GPI05[11] — General purpose digital input/output pin.                                                                                                                                                        |

|          |         |          |         |         |     |                    | I/O      | SSP0_SSEL — Slave Select for SSP0.                                                                                                                                                                           |

|          |         |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                                       |

| 1        | 1       |          |         |         | 1   |                    | <u> </u> |                                                                                                                                                                                                              |

Table 3.

Pin description ...continued

LPC435X\_3X\_2X\_1X

© NXP Semiconductors N.V. 2016. All rights reserved.

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                                                                                            |

|----------|---------|----------|---------|---------|-----|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| P5_0     | N3      | -        | 53      | 37      | [2] | N;          | I/O  | GPIO2[9] — General purpose digital input/output pin.                                                                                   |

|          |         |          |         |         |     | PU          | 0    | MCOB2 — Motor control PWM channel 2, output B.                                                                                         |

|          |         |          |         |         |     |             | I/O  | EMC_D12 — External memory data line 12.                                                                                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | I    | U1_DSR — Data Set Ready input for UART 1.                                                                                              |

|          |         |          |         |         |     |             | I    | T1_CAP0 — Capture input 0 of timer 1.                                                                                                  |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

| P5_1     | P3      | -        | 55      | 39      | [2] | N;          | I/O  | GPIO2[10] — General purpose digital input/output pin.                                                                                  |

|          |         |          |         |         |     | PU          | I    | MCI2 — Motor control PWM channel 2, input.                                                                                             |

|          |         |          |         |         |     |             | I/O  | EMC_D13 — External memory data line 13.                                                                                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | 0    | <b>U1_DTR</b> — Data Terminal Ready output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1. |

|          |         |          |         |         |     |             | I    | T1_CAP1 — Capture input 1 of timer 1.                                                                                                  |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

| P5_2     | R4      | -        | 63      | 46      | [2] | N;          | I/O  | GPIO2[11] — General purpose digital input/output pin.                                                                                  |

|          |         |          |         |         |     | PU          | I    | MCI1 — Motor control PWM channel 1, input.                                                                                             |

|          |         |          |         |         |     |             | I/O  | EMC_D14 — External memory data line 14.                                                                                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | 0    | <b>U1_RTS</b> — Request to Send output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1.     |

|          |         |          |         |         |     |             | I    | T1_CAP2 — Capture input 2 of timer 1.                                                                                                  |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

| P5_3     | T8      | -        | 76      | 54      | [2] | N;          | I/O  | GPIO2[12] — General purpose digital input/output pin.                                                                                  |

|          |         |          |         |         |     | PU          | I    | MCI0 — Motor control PWM channel 0, input.                                                                                             |

|          |         |          |         |         |     |             | I/O  | EMC_D15 — External memory data line 15.                                                                                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | I    | <b>U1_RI</b> — Ring Indicator input for UART 1.                                                                                        |

|          |         |          |         |         |     |             | I    | T1_CAP3 — Capture input 3 of timer 1.                                                                                                  |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                 |

Table 3.

Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

| Table 3. Pin | descrip | otion    | continu | ed      |     |                    |      |                                                                      |

|--------------|---------|----------|---------|---------|-----|--------------------|------|----------------------------------------------------------------------|

| Pin name     | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                          |

| P6_7         | J13     | -        | 123     | 85      | [2] | N;                 | -    | R — Function reserved.                                               |

|              |         |          |         |         |     | PU                 | I/O  | EMC_A15 — External memory address line 15.                           |

|              |         |          |         |         |     |                    | I/O  | SGPI06 — General purpose digital input/output pin.                   |

|              |         |          |         |         |     |                    | 0    | <b>USB0_IND1</b> — USB0 port indicator LED control output 1.         |

|              |         |          |         |         |     |                    | I/O  | GPIO5[15] — General purpose digital input/output pin.                |

|              |         |          |         |         |     |                    | 0    | T2_MAT0 — Match output 0 of timer 2.                                 |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

| P6_8         | H13     | -        | 125     | 86      | [2] | N;                 | -    | R — Function reserved.                                               |

|              |         |          |         |         |     | PU                 | I/O  | EMC_A14 — External memory address line 14.                           |

|              |         |          |         |         |     |                    | I/O  | SGPI07 — General purpose digital input/output pin.                   |

|              |         |          |         |         |     |                    | 0    | <b>USB0_IND0</b> — USB0 port indicator LED control output 0.         |

|              |         |          |         |         |     |                    | I/O  | GPIO5[16] — General purpose digital input/output pin.                |

|              |         |          |         |         |     |                    | 0    | T2_MAT1 — Match output 1 of timer 2.                                 |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

| P6_9         | J15     | F8       | 139     | 97      | [2] | N;                 | I/O  | GPIO3[5] — General purpose digital input/output pin.                 |

|              |         |          |         |         |     | PU                 | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | 0    | EMC_DYCS0 — SDRAM chip select 0.                                     |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | 0    | <b>T2_MAT2</b> — Match output 2 of timer 2.                          |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

| P6_10        | H15     | -        | 142     | 100     | [2] | N;                 | I/O  | <b>GPIO3[6]</b> — General purpose digital input/output pin.          |

|              |         |          |         |         |     | PU                 | 0    | <b>MCABORT</b> — Motor control PWM, LOW-active fast abort.           |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | 0    | <b>EMC_DQMOUT1</b> — Data mask 1 used with SDRAM and static devices. |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    | -    | R — Function reserved.                                               |

|              |         |          |         |         |     |                    |      |                                                                      |

Table 3. Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name   | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |            | Reset state | Type | Description                                                                                                                                                              |

|------------|---------|----------|---------|---------|------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock pins |         |          |         |         |            |             |      |                                                                                                                                                                          |

| CLK0       | N5      | K3       | 62      | 45      | <u>[4]</u> | О;          | 0    | EMC_CLK0 — SDRAM clock 0.                                                                                                                                                |

|            |         |          |         |         |            | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                               |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | I/O  | SD_CLK — SD/MMC card clock.                                                                                                                                              |

|            |         |          |         |         |            |             | 0    | EMC_CLK01 — SDRAM clock 0 and clock 1 combined.                                                                                                                          |

|            |         |          |         |         |            |             | I/O  | SSP1_SCK — Serial clock for SSP1.                                                                                                                                        |

|            |         |          |         |         |            |             | I    | <b>ENET_TX_CLK (ENET_REF_CLK)</b> — Ethernet Transmit<br>Clock (MII interface) or Ethernet Reference Clock (RMII<br>interface).                                          |

| CLK1       | T10     | -        | -       | -       | [4]        | О;          | 0    | EMC_CLK1 — SDRAM clock 1.                                                                                                                                                |

|            |         |          |         |         |            | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                               |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | 0    | CGU_OUT0 — CGU spare clock output 0.                                                                                                                                     |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | 0    | I2S1_TX_MCLK — I2S1 transmit master clock.                                                                                                                               |

| CLK2       | D14     | K6       | 141     | 99      | <u>[4]</u> | О;          | 0    | EMC_CLK3 — SDRAM clock 3.                                                                                                                                                |

|            |         |          |         |         |            | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                               |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | I/O  | SD_CLK — SD/MMC card clock.                                                                                                                                              |

|            |         |          |         |         |            |             | 0    | <b>EMC_CLK23</b> — SDRAM clock 2 and clock 3 combined.                                                                                                                   |

|            |         |          |         |         |            |             | 0    | I2S0_TX_MCLK — I2S transmit master clock.                                                                                                                                |

|            |         |          |         |         |            |             | I/O  | <b>I2S1_RX_SCK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the I <sup>2</sup> S-bus specification.       |

| CLK3       | P12     | -        | -       | -       | [4]        | O;          | 0    | EMC_CLK2 — SDRAM clock 2.                                                                                                                                                |

|            |         |          |         |         |            | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                               |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | 0    | CGU_OUT1 — CGU spare clock output 1.                                                                                                                                     |

|            |         |          |         |         |            |             | -    | R — Function reserved.                                                                                                                                                   |

|            |         |          |         |         |            |             | I/O  | <b>I2S1_RX_SCK</b> — Receive Clock. It is driven by the master<br>and received by the slave. Corresponds to the signal SCK in<br>the I <sup>2</sup> S-bus specification. |

#### Table 3. Pin description ...continued

32-bit ARM Cortex-M4/M0 microcontroller

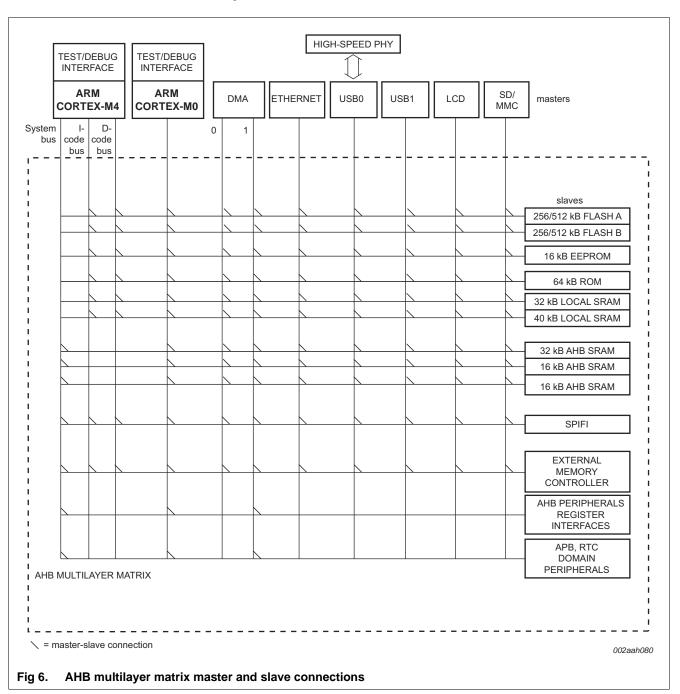

## 7.5 AHB multilayer matrix

## 7.6 Nested Vectored Interrupt Controller (NVIC)

The NVIC is an integral part of the Cortex-M4. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

The ARM Cortex-M0 co-processor has its own NVIC with 32 vectored interrupts. Most peripheral interrupts are shared between the Cortex-M0 and Cortex-M4 NVICs.

LPC435X\_3X\_2X\_1X

### 32-bit ARM Cortex-M4/M0 microcontroller

**Remark:** Any interrupt can wake up the ARM Cortex-M4 from sleep mode if enabled in the NVIC.

## 7.9 Global Input Multiplexer Array (GIMA)

The GIMA allows to route signals to event-driven peripheral targets like the SCTimer/PWM, timers, event router, or the ADCs.

### 7.9.1 Features

- Single selection of a source.

- Signal inversion.

- Can capture a pulse if the input event source is faster than the target clock.

- Synchronization of input event and target clock.

- Single-cycle pulse generation for target.

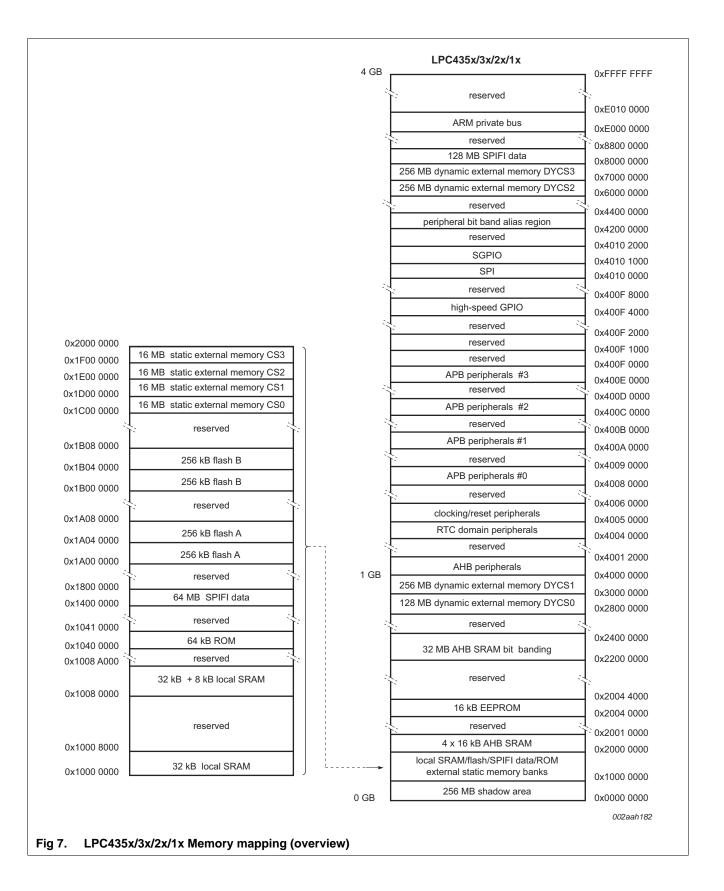

### 7.10 On-chip static RAM

The LPC435x/3x/2x/1x support up to 136 kB SRAM with separate bus master access for higher throughput and individual power control for low power operation.

## 7.11 On-chip flash memory

The LPC435x/3x/2x/1x contain up to 1 MB of dual-bank flash program memory. With dual-bank flash memory, the user code can write or erase one flash bank while reading the other flash bank without interruption. A two-port flash accelerator maximizes the flash performance.

In-System Programming (ISP) and In-Application Programming (IAP) routines for programming the flash memory are provided in the Boot ROM.

## 7.12 EEPROM

The LPC435x/3x/2x/1x contain 16 kB of on-chip byte-erasable and byte-programmable EEPROM memory.

The EEPROM memory is divided into 128 pages. The user can access pages 1 through 127. Page 128 is protected.

## 7.13 Boot ROM

The internal ROM memory is used to store the boot code of the LPC435x/3x/2x/1x. After a reset, the ARM processor will start its code execution from this memory.

The boot ROM memory includes the following features:

- The ROM memory size is 64 kB.

- Supports booting from external static memory such as NOR flash, SPI flash, quad SPI flash, USB0, and USB1.

- Includes API for OTP programming.

- Includes a flexible USB device stack that supports Human Interface Device (HID), Mass Storage Class (MSC), and Device Firmware Upgrade (DFU) drivers.

LPC435X 3X 2X 1X

### **NXP Semiconductors**

## LPC435x/3x/2x/1x

### 32-bit ARM Cortex-M4/M0 microcontroller

### 32-bit ARM Cortex-M4/M0 microcontroller

• Alarm interrupt can be generated for a specific date/time.

#### 7.22.1.2 Event monitor/recorder

The event monitor/recorder allows recording and creating a time stamp of events related to the WAKEUP pins. Sensors report changes to the state of the WAKEUP pins, and the event monitor/recorder stores records of such events. The event recorder can be powered by the backup battery.

The event monitor/recorder can monitor the integrity of the device and record any tampering events.

#### Features

- Supports three digital event inputs in the VBAT power domain.

- An event is defined as a level change at the digital event inputs.

- For each event channel, two timestamps mark the first and the last occurrence of an event. Each channel also has a dedicated counter tracking the total number of events. Timestamp values are taken from the RTC.

- Runs in VBAT power domain, independent of system power supply. The event/recorder/monitor can therefore operate in Deep power-down mode.

- Low power consumption.

- Interrupt available if system is running.

- A qualified event can be used as a wake-up trigger.

- State of event interrupts accessible by software through GPIO.

### 7.22.2 Alarm timer

The alarm timer is a 16-bit timer and counts down at 1 kHz from a preset value generating alarms in intervals of up to 1 min. The counter triggers a status bit when it reaches 0x00 and asserts an interrupt if enabled.

The alarm timer is part of the RTC power domain and can be battery powered.

### 7.23 System control

### 7.23.1 Configuration registers (CREG)

The following settings are controlled in the configuration register block:

- BOD trip settings

- Oscillator output

- DMA-to-peripheral muxing

- Ethernet mode

- Memory mapping

- Timer/USART inputs

- Enabling the USB controllers

In addition, the CREG block contains the part identification and part configuration information.

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol                | Parameter                                                                   | Conditions                                           |      | Min | Typ[1] | Max  | Unit |

|-----------------------|-----------------------------------------------------------------------------|------------------------------------------------------|------|-----|--------|------|------|

| V <sub>IC</sub>       | common-mode input                                                           | high-speed mode                                      |      | -50 | 200    | 500  | mV   |

|                       | voltage                                                                     | full-speed/low-speed<br>mode                         |      | 800 | -      | 2500 | mV   |

|                       |                                                                             | chirp mode                                           |      | -50 | -      | 600  | mV   |

| V <sub>i(dif)</sub>   | differential input voltage                                                  |                                                      |      | 100 | 400    | 1100 | mV   |

| USB1 pins (           | (USB1_DP/USB1_DM)[17]                                                       |                                                      |      | 1   | 4      |      | 1    |

| I <sub>OZ</sub>       | OFF-state output current                                                    | 0 V < V <sub>I</sub> < 3.3 V                         | [17] | -   | -      | ±10  | μΑ   |

| V <sub>BUS</sub>      | bus supply voltage                                                          |                                                      | [18] | -   | -      | 5.25 | V    |

| V <sub>DI</sub>       | differential input sensitivity voltage                                      | (D+) – (D–)                                          |      | 0.2 | -      | -    | V    |

| V <sub>CM</sub>       | differential common mode voltage range                                      | includes V <sub>DI</sub> range                       |      | 0.8 | -      | 2.5  | V    |

| V <sub>th(rs)se</sub> | single-ended receiver<br>switching threshold<br>voltage                     |                                                      |      | 0.8 | -      | 2.0  | V    |

| V <sub>OL</sub>       | LOW-level output<br>voltage for<br>low-/full-speed                          | $R_L$ of 1.5 k $\Omega$ to 3.6 V                     |      | -   | -      | 0.18 | V    |

| V <sub>OH</sub>       | HIGH-level output<br>voltage (driven) for<br>low-/full-speed                | $R_L$ of 15 k $\Omega$ to GND                        |      | 2.8 | -      | 3.5  | V    |

| C <sub>trans</sub>    | transceiver capacitance                                                     | pin to GND                                           |      | -   | -      | 20   | pF   |

| Z <sub>DRV</sub>      | driver output<br>impedance for driver<br>which is not high-speed<br>capable | with 33 $\Omega$ series resistor; steady state drive | [19] | 36  | -      | 44.1 | Ω    |

### Table 11. Static characteristics ...continued

$T_{amb} = -40 \ ^{\circ}C$  to +105  $^{\circ}C$ , unless otherwise specified.

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] The recommended operating condition for the battery supply is  $V_{DD(REG)(3V3)} > V_{BAT} + 0.2 V$ . Special conditions for  $V_{DD(REG)(3V3)}$  apply when writing to the flash and EEPROM. See <u>Table 14 and Table 15</u>.

[3] Pin VPP should either be not connected (when OTP does not need to be programmed) or tied to pins VDDIO and VDDREG to ensure the same ramp-up time for both supply voltages.

[4]  $V_{DD(REG)(3V3)} = 3.3 \text{ V}; V_{DD(IO)} = 3.3 \text{ V}; T_{amb} = 25 \text{ °C}.$

[5] PLL1 disabled; IRC running; CCLK = 12 MHz.

[6] V<sub>BAT</sub> = 3.6 V.

[7] T<sub>amb</sub> = -40 °C to +105 °C; V<sub>DD(IO)</sub> = V<sub>DDA</sub> = 3.6 V; over entire frequency range CCLK = 12 MHz to 204 MHz; in active mode, sleep mode; deep-sleep mode, power-down mode, and deep power-down mode.

[8] On pin VBAT;  $T_{amb} = 25 \circ C$ .

[9] V<sub>ps</sub> corresponds to the output of the power switch (see <u>Table 9</u>) which is determined by the greater of V<sub>BAT</sub> and V<sub>DD(Reg)(3V3)</sub>.

[10]  $V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = 25 \text{ °C}.$

- [11] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

- [12] To V<sub>SS</sub>.

LPC435X 3X 2X 1X

- [13] The values specified are simulated and absolute values.

- [14] The weak pull-up resistor is connected to the  $V_{DD(IO)}$  rail and pulls up the I/O pin to the  $V_{DD(IO)}$  level.

- [15] The input cell disables the weak pull-up resistor when the applied input voltage exceeds  $V_{DD(IO)}$ .

32-bit ARM Cortex-M4/M0 microcontroller

### 11.2 Wake-up times

## Table 17. Dynamic characteristic: Wake-up from Deep-sleep, Power-down, and Deep power-down modes

$T_{amb} = -40 \ ^{\circ}C \ to +105 \ ^{\circ}C$

| Symbol            | Parameter    | Conditions                             |     | Min                   | Typ <u>[1]</u>        | Max | Unit |

|-------------------|--------------|----------------------------------------|-----|-----------------------|-----------------------|-----|------|

| t <sub>wake</sub> | wake-up time | from Sleep mode                        | [2] | $3\times T_{cy(clk)}$ | $5\times T_{cy(clk)}$ | -   | ns   |

|                   |              | from Deep-sleep and<br>Power-down mode |     | 12                    | 51                    | -   | μS   |

|                   |              | from Deep power-down mode              |     | -                     | 200                   | -   | μs   |

|                   |              | after reset                            |     | -                     | 200                   | -   | μs   |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2]  $T_{cy(clk)} = 1/CCLK$  with CCLK = CPU clock frequency.

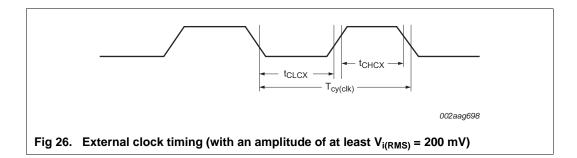

## **11.3** External clock for oscillator in slave mode

**Remark:** The input voltage on the XTAL1/2 pins must be  $\leq 1.2$  V (see <u>Table 11</u>). For connecting the oscillator to the XTAL pins, also see <u>Section 13.2</u> and <u>Section 13.4</u>.

#### Table 18. Dynamic characteristic: external clock

$T_{amb} = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C}; V_{DD(IO)} \text{ over specified ranges.}$

| Symbol               | Parameter            | Conditions |   | Min                     | Max                     | Unit |

|----------------------|----------------------|------------|---|-------------------------|-------------------------|------|

| f <sub>osc</sub>     | oscillator frequency |            |   | 1                       | 25                      | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     |            | 4 | 40                      | 1000                    | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      |            | - | $T_{cy(clk)} 	imes 0.4$ | $T_{cy(clk)} 	imes 0.6$ | ns   |

| t <sub>CLCX</sub>    | clock LOW time       |            | - | $T_{cy(clk)} 	imes 0.4$ | $T_{cy(clk)} 	imes 0.6$ | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

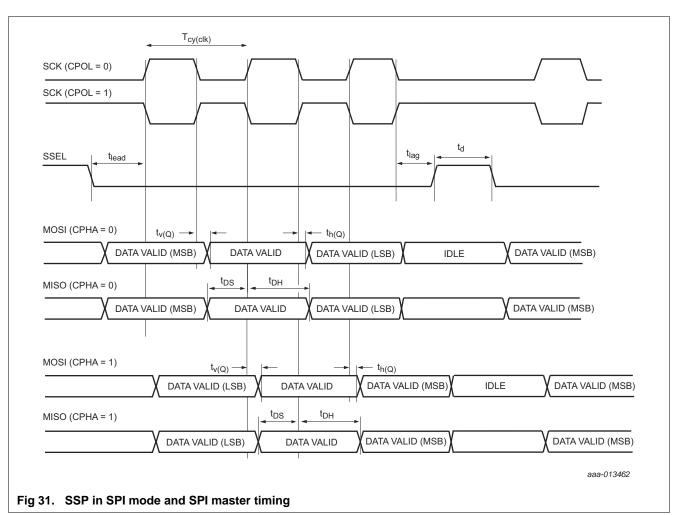

### 32-bit ARM Cortex-M4/M0 microcontroller

#### Table 27. Dynamic characteristics: SSP pins in SPI mode

$T_{amb} = -40 \degree C$  to +105  $\degree C$ ; 2.4 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V;  $C_L = 20 \ pF$ ; sampled at 10 % and 90 % of the signal level; EHS = 1 for all pins. Simulated values.

| Symbol           | Parameter                        | Conditions                      | Min                              | Тур                             | Max | Unit |

|------------------|----------------------------------|---------------------------------|----------------------------------|---------------------------------|-----|------|

| t <sub>lag</sub> | lag time                         | continuous transfer mode        | 0.5 x T <sub>cy(clk)</sub> + 1.5 | -                               | -   | ns   |

|                  |                                  | SPI mode; CPOL = 0;<br>CPHA = 0 |                                  |                                 |     |      |

|                  |                                  | SPI mode; CPOL = 0;<br>CPHA = 1 | T <sub>cy(clk)</sub> + 1.5       | -                               | -   | ns   |

|                  |                                  | SPI mode; CPOL = 1;<br>CPHA = 0 | $0.5 	imes T_{cy(clk)} + 1.5$    | -                               | -   | ns   |

|                  |                                  | SPI mode; CPOL = 1;<br>CPHA = 1 | T <sub>cy(clk)</sub> + 1.5       | -                               | -   | ns   |

|                  | synchronous serial<br>frame mode | T <sub>cy(clk)</sub> + 1.5      | -                                | -                               | ns  |      |

|                  |                                  | microwire frame format          | $0.5 \times T_{cy(clk)}$         | -                               | -   | ns   |

| t <sub>d</sub>   | delay time                       | continuous transfer mode        | -                                | $0.5\times T_{\text{cy(clk)}}$  | -   | ns   |

|                  |                                  | SPI mode; CPOL = 0;<br>CPHA = 0 |                                  |                                 |     |      |

|                  |                                  | SPI mode; CPOL = 0;<br>CPHA = 1 | -                                | n/a                             | -   | ns   |

|                  |                                  | SPI mode; CPOL = 1;<br>CPHA = 0 | -                                | $0.5 \times T_{\text{cy(clk)}}$ | -   | ns   |

|                  | SPI mode; CPOL = 1;<br>CPHA = 1  | -                               | n/a                              | -                               | ns  |      |

|                  |                                  | synchronous serial frame mode   | -                                | T <sub>cy(clk)</sub>            | -   | ns   |

|                  |                                  | microwire frame format          | -                                | n/a                             | -   | ns   |

[1]  $T_{cy(clk)} = (SSPCLKDIV \times (1 + SCR) \times CPSDVSR) / f_{main}$ . The clock cycle time derived from the SPI bit rate  $T_{cy(clk)}$  is a function of the main clock frequency  $f_{main}$ , the SSP peripheral clock divider (SSPCLKDIV), the SSP SCR parameter (specified in the SSP0CR0 register), and the SSP CPSDVSR parameter (specified in the SSP clock prescale register).

### 32-bit ARM Cortex-M4/M0 microcontroller

## 11.13 SPI interface

#### Table 28. Dynamic characteristics: SPI

$T_{amb} = -40$  °C to +105 °C; 2.4 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V. Simulated values.

| Symbol                | Parameter              | Conditions |     | Min                            | Тур      | Max                           | Unit |

|-----------------------|------------------------|------------|-----|--------------------------------|----------|-------------------------------|------|

| T <sub>cy(PCLK)</sub> | PCLK cycle time        |            |     | 5                              |          |                               | ns   |

| T <sub>cy(clk)</sub>  | clock cycle time       |            | [1] | 40                             | -        | -                             | ns   |

| Master                |                        |            |     |                                | <b>I</b> |                               | 4    |

| t <sub>DS</sub>       | data set-up time       |            |     | 7.2                            | -        | -                             | ns   |

| t <sub>DH</sub>       | data hold time         |            |     | 0                              | -        | -                             | ns   |

| t <sub>v(Q)</sub>     | data output valid time |            |     | -                              | -        | 3.7                           | ns   |

| t <sub>h(Q)</sub>     | data output hold time  |            |     | -                              | -        | 1.2                           | ns   |

| Slave                 |                        |            |     |                                | <u> </u> |                               |      |

| t <sub>DS</sub>       | data set-up time       |            |     | 1.2                            | -        | -                             | ns   |

| t <sub>DH</sub>       | data hold time         |            |     | $3 \times T_{cy(PCLK)}$ + 0.54 | -        | -                             | ns   |

| t <sub>v(Q)</sub>     | data output valid time |            |     | -                              | -        | $3 \times T_{cy(PCLK)}$ + 9.7 | ns   |

| t <sub>h(Q)</sub>     | data output hold time  |            |     | -                              | -        | $2 \times T_{cy(PCLK)} + 7.1$ | ns   |

[1]  $T_{cy(clk)} = 8/BASE\_SPI\_CLK. T_{cy(PCLK)} = 1/BASE\_SPI\_CLK.$

32-bit ARM Cortex-M4/M0 microcontroller

## 11.14 SSP/SPI timing diagrams

### 32-bit ARM Cortex-M4/M0 microcontroller

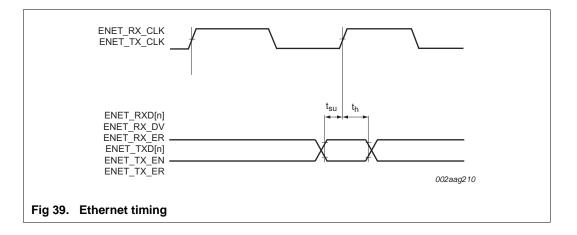

#### Table 36. Dynamic characteristics: Ethernet

$T_{amb} = -40$  °C to 105 °C, 2.4 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V. Values guaranteed by design.

| Symbol                | Parameter        | Conditions                                                         |        | Min | Max      | Unit     |

|-----------------------|------------------|--------------------------------------------------------------------|--------|-----|----------|----------|

| RMII mo               | de               |                                                                    |        |     |          | <b>I</b> |

| f <sub>clk</sub>      | clock frequency  | for ENET_RX_CLK                                                    | [1]    | -   | 50       | MHz      |

| $\delta_{clk}$        | clock duty cycle |                                                                    | [1]    | 50  | 50       | %        |

| t <sub>su</sub>       | set-up time      | for ENET_TXDn, ENET_TX_EN,<br>ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV | [1][2] | 4   | -        | ns       |

| t <sub>h</sub>        | hold time        | for ENET_TXDn, ENET_TX_EN,<br>ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV | [1][2] | 2   | -        | ns       |

| MII mod               | e                |                                                                    |        |     | <b>I</b> | <b>I</b> |

| f <sub>clk</sub>      | clock frequency  | for ENET_TX_CLK                                                    | [1]    | -   | 25       | MHz      |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | [1]    | 50  | 50       | %        |

| t <sub>su</sub>       | set-up time      | for ENET_TXDn, ENET_TX_EN,<br>ENET_TX_ER                           | [1][2] | 4   | -        | ns       |

| t <sub>h</sub>        | hold time        | for ENET_TXDn, ENET_TX_EN,<br>ENET_TX_ER                           | [1][2] | 2   | -        | ns       |

| f <sub>clk</sub>      | clock frequency  | for ENET_RX_CLK                                                    | [1]    | -   | 25       | MHz      |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | [1]    | 50  | 50       | %        |

| t <sub>su</sub>       | set-up time      | for ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV                           | [1][2] | 4   | -        | ns       |

| t <sub>h</sub>        | hold time        | for ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV                           | [1][2] | 2   | -        | ns       |

[1] Output drivers can drive a load ≥ 25 pF accommodating over 12 inch of PCB trace and the input capacitance of the receiving device.

[2] Timing values are given from the point at which the clock signal waveform crosses 1.4 V to the valid input or output level.

### 32-bit ARM Cortex-M4/M0 microcontroller

| External pin      | 4-bit mono STN dual panel |                  | 8-bit mono STN dual panel |                  | Color STN dual panel |                  |

|-------------------|---------------------------|------------------|---------------------------|------------------|----------------------|------------------|

|                   | LPC43xx pin<br>used       | LCD function     | LPC43xx pin<br>used       | LCD function     | LPC43xx pin<br>used  | LCD function     |

| LCD_VD2           | P4_3                      | UD[2]            | P4_3                      | UD[2]            | P4_3                 | UD[2]            |

| LCD_VD1           | P4_4                      | UD[1]            | P4_4                      | UD[1]            | P4_4                 | UD[1]            |

| LCD_VD0           | P4_1                      | UD[0]            | P4_1                      | UD[0]            | P4_1                 | UD[0]            |

| LCD_LP            | P7_6                      | LCDLP            | P7_6                      | LCDLP            | P7_6                 | LCDLP            |

| LCD_ENAB/<br>LCDM | P4_6                      | LCDENAB/<br>LCDM | P4_6                      | LCDENAB/<br>LCDM | P4_6                 | LCDENAB/<br>LCDM |

| LCD_FP            | P4_5                      | LCDFP            | P4_5                      | LCDFP            | P4_5                 | LCDFP            |

| LCD_DCLK          | P4_7                      | LCDDCLK          | P4_7                      | LCDDCLK          | P4_7                 | LCDDCLK          |

| LCD_LE            | P7_0                      | LCDLE            | P7_0                      | LCDLE            | P7_0                 | LCDLE            |

| LCD_PWR           | P7_7                      | LCDPWR           | P7_7                      | LCDPWR           | P7_7                 | LCDPWR           |

| GP_CLKIN          | PF_4                      | LCDCLKIN         | PF_4                      | LCDCLKIN         | PF_4                 | LCDCLKIN         |

### Table 42. LCD panel connections for STN dual panel mode

### Table 43. LCD panel connections for TFT panels

| External<br>pin | TFT 12 bit (4:4:4<br>mode) |                 | TFT 16 bit (5:6:5 mode) |                 | TFT 16 bit (1:5:5:5 mode) |                 | TFT 24 bit          |                 |

|-----------------|----------------------------|-----------------|-------------------------|-----------------|---------------------------|-----------------|---------------------|-----------------|

|                 | LPC43xx<br>pin used        | LCD<br>function | LPC43xx<br>pin used     | LCD<br>function | LPC43xx pin<br>used       | LCD<br>function | LPC43xx<br>pin used | LCD<br>function |

| LCD_VD23        | PB_0                       | BLUE3           | PB_0                    | BLUE4           | PB_0                      | BLUE4           | PB_0                | BLUE7           |

| LCD_VD22        | PB_1                       | BLUE2           | PB_1                    | BLUE3           | PB_1                      | BLUE3           | PB_1                | BLUE6           |

| LCD_VD21        | PB_2                       | BLUE1           | PB_2                    | BLUE2           | PB_2                      | BLUE2           | PB_2                | BLUE5           |

| LCD_VD20        | PB_3                       | BLUE0           | PB_3                    | BLUE1           | PB_3                      | BLUE1           | PB_3                | BLUE4           |

| LCD_VD19        | -                          | -               | P7_1                    | BLUE0           | P7_1                      | BLUE0           | P7_1                | BLUE3           |

| LCD_VD18        | -                          | -               | -                       | -               | P7_2                      | intensity       | P7_2                | BLUE2           |

| LCD_VD17        | -                          | -               | -                       | -               | -                         | -               | P7_3                | BLUE1           |

| LCD_VD16        | -                          | -               | -                       | -               | -                         | -               | P7_4                | BLUE0           |

| LCD_VD15        | PB_4                       | GREEN3          | PB_4                    | GREEN5          | PB_4                      | GREEN4          | PB_4                | GREEN7          |

| LCD_VD14        | PB_5                       | GREEN2          | PB_5                    | GREEN4          | PB_5                      | GREEN3          | PB_5                | GREEN6          |

| LCD_VD13        | PB_6                       | GREEN1          | PB_6                    | GREEN3          | PB_6                      | GREEN2          | PB_6                | GREEN5          |

| LCD_VD12        | P8_3                       | GREEN0          | P8_3                    | GREEN2          | P8_3                      | GREEN1          | P8_3                | GREEN4          |

| LCD_VD11        | -                          | -               | P4_9                    | GREEN1          | P4_9                      | GREEN0          | P4_9                | GREEN3          |

| LCD_VD10        | -                          | -               | P4_10                   | GREEN0          | P4_10                     | intensity       | P4_10               | GREEN2          |

| LCD_VD9         | -                          | -               | -                       | -               | -                         | -               | P4_8                | GREEN1          |

| LCD_VD8         | -                          | -               | -                       | -               | -                         | -               | P7_5                | GREEN0          |

| LCD_VD7         | P8_4                       | RED3            | P8_4                    | RED4            | P8_4                      | RED4            | P8_4                | RED7            |

| LCD_VD6         | P8_5                       | RED2            | P8_5                    | RED3            | P8_5                      | RED3            | P8_5                | RED6            |

| LCD_VD5         | P8_6                       | RED1            | P8_6                    | RED2            | P8_6                      | RED2            | P8_6                | RED5            |

| LCD_VD4         | P8_7                       | RED0            | P8_7                    | RED1            | P8_7                      | RED1            | P8_7                | RED4            |

| LCD_VD3         | -                          | -               | P4_2                    | RED0            | P4_2                      | RED0            | P4_2                | RED3            |

| LCD_VD2         | -                          | -               | -                       | -               | P4_3                      | intensity       | P4_3                | RED2            |

| LCD_VD1         | -                          | -               | -                       | -               | -                         | -               | P4_4                | RED1            |

32-bit ARM Cortex-M4/M0 microcontroller

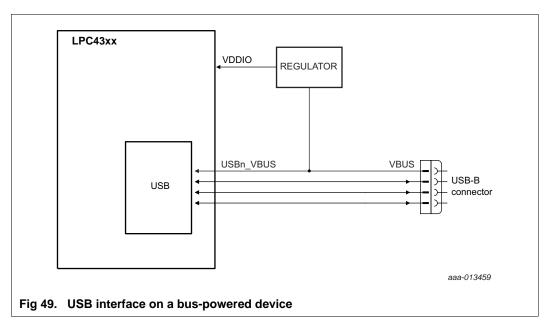

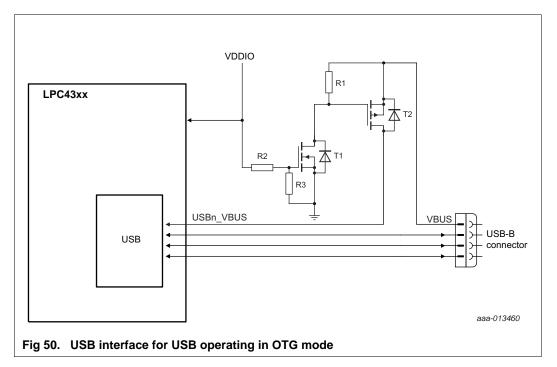

**Remark:** If the VBUS function of the USB1 interface is not connected, configure the pin function for GPIO using the function control bits in the SYSCON block.

**Remark:** In OTG mode, it is important to be able to detect the VBUS level and to charge and discharge VBUS. This requires adding active devices that disconnect the link when VDDIO is not present.

## 32-bit ARM Cortex-M4/M0 microcontroller