Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | ARM® Cortex®-M4/M0                                                                |

| Core Size                  | 32-Bit Dual-Core                                                                  |

| Speed                      | 204MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 49                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 16K x 8                                                                           |

| RAM Size                   | 104K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 4x10b; D/A 1x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TFBGA                                                                         |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4313jet100e            |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                                                        |

|----------|---------|----------|---------|---------|-----|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2_2     | M15     | F5       | 121     | 84      | [2] | N;          | I/O  | SGPIO6 — General purpose digital input/output pin.                                                                                                                                                 |

|          |         |          |         |         |     | PU          | I/O  | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                                         |

|          |         |          |         |         |     |             | I/O  | EMC_A11 — External memory address line 11.                                                                                                                                                         |

|          |         |          |         |         |     |             | 0    | <b>USB0_IND1</b> — USB0 port indicator LED control output 1.                                                                                                                                       |

|          |         |          |         |         |     |             | I/O  | GPIO5[2] — General purpose digital input/output pin.                                                                                                                                               |

|          |         |          |         |         |     |             | I    | CTIN_6 — SCT input 6. Capture input 1 of timer 3.                                                                                                                                                  |

|          |         |          |         |         |     |             | I    | T3_CAP2 — Capture input 2 of timer 3.                                                                                                                                                              |

|          |         |          |         |         |     |             | 0    | EMC_CS1 — LOW active Chip Select 1 signal.                                                                                                                                                         |

| P2_3     | J12     | D8       | 127     | 87      | [3] | N;          | I/O  | SGPI012 — General purpose digital input/output pin.                                                                                                                                                |

|          |         |          |         |         |     | PU          | I/O  | <b>I2C1_SDA</b> — I <sup>2</sup> C1 data input/output (this pin does not use a specialized I2C pad).                                                                                               |

|          |         |          |         |         |     |             | 0    | <b>U3_TXD</b> — Transmitter output for USART3. See <u>Table 4</u> for ISP mode.                                                                                                                    |

|          |         |          |         |         |     |             | I    | <b>CTIN_1</b> — SCT input 1. Capture input 1 of timer 0. Capture input 1 of timer 2.                                                                                                               |

|          |         |          |         |         |     |             | I/O  | GPIO5[3] — General purpose digital input/output pin.                                                                                                                                               |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                                                                             |

|          |         |          |         |         |     |             | 0    | T3_MAT0 — Match output 0 of timer 3.                                                                                                                                                               |

|          |         |          |         |         |     |             | 0    | <b>USB0_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active HIGH).                                                    |

|          |         |          |         |         |     |             |      | Add a pull-down resistor to disable the power switch at reset.<br><u>This signal has opposite polarity compared to the</u><br>USB_PPWR used on other NXP LPC parts.                                |

| P2_4     | K11     | D9       | 128     | 88      | [3] | N;          | I/O  | SGPI013 — General purpose digital input/output pin.                                                                                                                                                |

|          |         |          |         |         |     | PU          | I/O  | <b>I2C1_SCL</b> — I <sup>2</sup> C1 clock input/output (this pin does not use a specialized I2C pad).                                                                                              |

|          |         |          |         |         |     |             | I    | <b>U3_RXD</b> — Receiver input for USART3. See <u>Table 4</u> for ISP mode.                                                                                                                        |

|          |         |          |         |         |     |             | I    | CTIN_0 — SCT input 0. Capture input 0 of timer 0, 1, 2, 3.                                                                                                                                         |

|          |         |          |         |         |     |             | I/O  | GPIO5[4] — General purpose digital input/output pin.                                                                                                                                               |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                                                                             |

|          |         |          |         |         |     |             | 0    | T3_MAT1 — Match output 1 of timer 3.                                                                                                                                                               |

|          |         |          |         |         |     |             | I    | <b>USB0_PWR_FAULT</b> — Port power fault signal indicating overcurrent condition; this signal monitors over-current on the USB bus (external circuitry required to detect over-current condition). |

Table 3.

Pin description ...continued

## 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256                          | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                    |

|----------|----------------------------------|----------|---------|---------|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                  | Ë        |         |         | [0] |                    |      |                                                                                                                                                                |

| P4_0     | D5 - 1 1 <sup>[2]</sup> N;<br>PU |          |         |         | [2] | N;<br>PU           | I/O  | <b>GPIO2[0]</b> — General purpose digital input/output pin.                                                                                                    |

|          |                                  |          |         |         |     |                    | 0    | MCOA0 — Motor control PWM channel 0, output A.                                                                                                                 |

|          |                                  |          |         |         |     |                    | I    | <b>NMI</b> — External interrupt input to NMI.                                                                                                                  |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | 0    | LCD_VD13 — LCD data.                                                                                                                                           |

|          |                                  |          |         |         |     |                    | I/O  | <b>U3_UCLK</b> — Serial clock input/output for USART3 in synchronous mode.                                                                                     |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

| P4_1     | A1                               | -        | 3       | 3       | [5] | N;                 | I/O  | <b>GPIO2[1]</b> — General purpose digital input/output pin.                                                                                                    |

|          |                                  |          |         |         |     | PU                 | 0    | <b>CTOUT_1</b> — SCT output 1. Match output 3 of timer 3.                                                                                                      |

|          |                                  |          |         |         |     |                    | 0    | LCD_VD0 — LCD data.                                                                                                                                            |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | 0    | LCD_VD19 — LCD data.                                                                                                                                           |

|          |                                  |          |         |         |     |                    | 0    | <b>U3_TXD</b> — Transmitter output for USART3.                                                                                                                 |

|          |                                  |          |         |         |     |                    | I    | <b>ENET_COL</b> — Ethernet Collision detect (MII interface).                                                                                                   |

|          |                                  |          |         |         |     |                    | AI   | <b>ADC0_1</b> — ADC0 and ADC1, input channel 1. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.         |

| P4_2     | D3                               | -        | 12      | 8       | [2] | N;                 | I/O  | GPIO2[2] — General purpose digital input/output pin.                                                                                                           |

|          |                                  |          |         |         |     | PU                 | 0    | CTOUT_0 — SCT output 0. Match output 0 of timer 0.                                                                                                             |

|          |                                  |          |         |         |     |                    | 0    | LCD_VD3 — LCD data.                                                                                                                                            |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | 0    | LCD_VD12 — LCD data.                                                                                                                                           |

|          |                                  |          |         |         |     |                    | I    | U3_RXD — Receiver input for USART3.                                                                                                                            |

|          |                                  |          |         |         |     |                    | I/O  | SGPIO8 — General purpose digital input/output pin.                                                                                                             |

| P4_3     | C2                               | -        | 10      | 7       | [5] | N;                 | I/O  | GPIO2[3] — General purpose digital input/output pin.                                                                                                           |

|          |                                  |          |         |         |     | PU                 | 0    | CTOUT_3 — SCT output 3. Match output 3 of timer 0.                                                                                                             |

|          |                                  |          |         |         |     |                    | 0    | LCD_VD2 — LCD data.                                                                                                                                            |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |                                  |          |         |         |     |                    | 0    | LCD_VD21 — LCD data.                                                                                                                                           |

|          |                                  |          |         |         |     |                    | I/O  | U3_BAUD — Baud pin for USART3.                                                                                                                                 |

|          |                                  |          |         |         |     |                    | I/O  | SGPI09 — General purpose digital input/output pin.                                                                                                             |

|          |                                  |          |         |         |     |                    | AI   | <b>ADC0_0</b> — DAC, ADC0 and ADC1, input channel 0.<br>Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP208                | LQFP144 |     | Reset state<br>[1] | Type | Description                                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|----------|---------|----------|------------------------|---------|-----|--------------------|------|--------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|------------------------|

| P8_2     | K4      | -        | 36                     | -       | [3] | N;                 | I/O  | GPIO4[2] — General purpose digital input/output pin.         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     | PU                 | 0    | <b>USB0_IND0</b> — USB0 port indicator LED control output 0. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | I    | MCI0 — Motor control PWM channel 0, input.                   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | I/O  | SGPIO10 — General purpose digital input/output pin.          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | 0    | T0_MAT2 — Match output 2 of timer 0.                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| P8_3     | J3      | -        | 37                     | -       | [2] | N;                 | I/O  | GPIO4[3] — General purpose digital input/output pin.         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     | PU                 | I/O  | USB1_ULPI_D2 — ULPI link bidirectional data line 2.          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| -<br>-   |         | -        | R — Function reserved. |         |     |                    |      |                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         | 0        | LCD_VD12 — LCD data.   |         |     |                    |      |                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | 0    | LCD_VD19 — LCD data.                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | 0    | T0_MAT3 — Match output 3 of timer 0.                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| P8_4     | J2      | -        | 39                     | -       | [2] | N;<br>PU           | I/O  | GPIO4[4] — General purpose digital input/output pin.         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | I/O  | USB1_ULPI_D1 — ULPI link bidirectional data line 1.          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | 0    | LCD_VD7 — LCD data.                                          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | 0    | LCD_VD16 — LCD data.                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| 1        |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| 1        |         |          |                        |         |     |                    | I    | T0_CAP0 — Capture input 0 of timer 0.                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| P8_5     | J1      | -        | 40                     | -       | [2] | N;                 | I/O  | GPIO4[5] — General purpose digital input/output pin.         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     | PU                 | I/O  | USB1_ULPI_D0 — ULPI link bidirectional data line 0.          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | 0    | LCD_VD6 — LCD data.                                          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    | 0    | LCD_VD8 — LCD data.                                          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| l        |         |          |                        |         |     |                    | -    | R — Function reserved.                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |                        |         |     |                    |      |                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | - | R — Function reserved. |

|          |         |          |                        |         |     |                    | I    | T0_CAP1 — Capture input 1 of timer 0.                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |                        | Reset state | Type | Description                                                                                     |

|----------|---------|----------|---------|---------|------------------------|-------------|------|-------------------------------------------------------------------------------------------------|

| P8_6     | K3      | -        | 43      | -       | [2]                    | N;          | I/O  | GPIO4[6] — General purpose digital input/output pin.                                            |

|          |         |          |         |         |                        | PU          | I    | <b>USB1_ULPI_NXT</b> — ULPI link NXT signal. Data flow control signal from the PHY.             |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | 0    | LCD_VD5 — LCD data.                                                                             |

|          |         |          |         |         |                        |             | 0    | <b>LCD_LP</b> — Line synchronization pulse (STN). Horizontal synchronization pulse (TFT).       |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         | -       | R — Function reserved. |             |      |                                                                                                 |

|          |         |          |         |         |                        |             | I    | T0_CAP2 — Capture input 2 of timer 0.                                                           |

| P8_7     | K1      | -        | 45      | -       | [2]                    | N;          | I/O  | GPIO4[7] — General purpose digital input/output pin.                                            |

|          |         |          |         |         |                        | PU          | 0    | <b>USB1_ULPI_STP</b> — ULPI link STP signal. Asserted to end or interrupt transfers to the PHY. |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | 0    | LCD_VD4 — LCD data.                                                                             |

|          |         |          |         |         |                        |             | 0    | LCD_PWR — LCD panel power enable.                                                               |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | I    | <b>T0_CAP3</b> — Capture input 3 of timer 0.                                                    |

| P8_8     | L1      | -        | 49      | -       | [2]                    | N;          | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        | PU          | I    | <b>USB1_ULPI_CLK</b> — ULPI link CLK signal. 60 MHz clock generated by the PHY.                 |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | 0    | CGU_OUT0 — CGU spare clock output 0.                                                            |

|          |         |          |         |         |                        |             | 0    | I2S1_TX_MCLK — I2S1 transmit master clock.                                                      |

| P9_0     | T1      | -        | 59      | -       | [2]                    | N;          | I/O  | <b>GPIO4[12]</b> — General purpose digital input/output pin.                                    |

|          |         |          |         |         |                        | PU          | 0    | <b>MCABORT</b> — Motor control PWM, LOW-active fast abort.                                      |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | -    | R — Function reserved.                                                                          |

|          |         |          |         |         |                        |             | Ι    | <b>ENET_CRS</b> — Ethernet Carrier Sense (MII interface).                                       |

|          |         |          |         |         |                        |             | I/O  | SGPIO0 — General purpose digital input/output pin.                                              |

|          |         |          |         |         |                        |             | I/O  | SSP0_SSEL — Slave Select for SSP0.                                                              |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                                         |

|----------|---------|----------|---------|---------|-----|-------------|------|-------------------------------------------------------------------------------------|

| PC_6     | H6      | -        | 22      | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I/O  | USB1_ULPI_D2 — ULPI link bidirectional data line 2.                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | ENET_RXD2 — Ethernet receive data 2 (MII interface).                                |

|          |         |          |         |         |     |             | I/O  | GPIO6[5] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | T3_CAP3 — Capture input 3 of timer 3.                                               |

|          |         |          |         |         |     |             | I/O  | <b>SD_DAT2</b> — SD/MMC data bus line 2.                                            |

| PC_7     | G5      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I/O  | USB1_ULPI_D1 — ULPI link bidirectional data line 1.                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | ENET_RXD3 — Ethernet receive data 3 (MII interface).                                |

|          |         |          |         |         |     |             | I/O  | GPIO6[6] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | 0    | T3_MAT0 — Match output 0 of timer 3.                                                |

|          |         |          |         |         |     |             | I/O  | SD_DAT3 — SD/MMC data bus line 3.                                                   |

| PC_8     | N4      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I/O  | <b>USB1_ULPI_D0</b> — ULPI link bidirectional data line 0.                          |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | <b>ENET_RX_DV</b> — Ethernet Receive Data Valid (RMII/MII interface).               |

|          |         |          |         |         |     |             | I/O  | GPIO6[7] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | 0    | T3_MAT1 — Match output 1 of timer 3.                                                |

|          |         |          |         |         |     |             | I    | <b>SD_CD</b> — SD/MMC card detect input.                                            |

| PC_9     | K2      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I    | <b>USB1_ULPI_NXT</b> — ULPI link NXT signal. Data flow control signal from the PHY. |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | ENET_RX_ER — Ethernet receive error (MII interface).                                |

|          |         |          |         |         |     |             | I/O  | GPIO6[8] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | 0    | T3_MAT2 — Match output 2 of timer 3.                                                |

|          |         |          |         |         |     |             | 0    | <b>SD_POW</b> — SD/MMC power monitor output.                                        |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                          |   |                        |

|----------|---------|----------|---------|---------|-----|-------------|------|----------------------------------------------------------------------|---|------------------------|

| PC_14    | N1      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     | PU          | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | I    | U1_RXD — Receiver input for UART 1.                                  |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | I/O  | GPIO6[13] — General purpose digital input/output pin.                |   |                        |

|          |         |          |         |         |     |             | I/O  | SGPI013 — General purpose digital input/output pin.                  |   |                        |

|          |         |          |         |         |     |             | 0    | ENET_TX_ER — Ethernet Transmit Error (MII interface).                |   |                        |

|          |         |          |         |         |     |             | I/O  | SD_DAT7 — SD/MMC data bus line 7.                                    |   |                        |

| PD_0     | N2      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     | PU          | 0    | CTOUT_15 — SCT output 15. Match output 3 of timer 3.                 |   |                        |

|          |         |          |         |         |     |             | 0    | <b>EMC_DQMOUT2</b> — Data mask 2 used with SDRAM and static devices. |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | I/O  | GPIO6[14] — General purpose digital input/output pin.                |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | I/O  | SGPIO4 — General purpose digital input/output pin.                   |   |                        |

| PD_1     | P1      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     | PU          | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | 0    | EMC_CKEOUT2 — SDRAM clock enable 2.                                  |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | I/O  | GPIO6[15] — General purpose digital input/output pin.                |   |                        |

|          |         |          |         |         |     |             | 0    | <b>SD_POW</b> — SD/MMC power monitor output.                         |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | I/O  | SGPI05 — General purpose digital input/output pin.                   |   |                        |

| PD_2     | R1      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     | PU          | 0    | CTOUT_7 — SCT output 7. Match output 3 of timer 1.                   |   |                        |

|          |         |          |         |         |     |             | I/O  | EMC_D16 — External memory data line 16.                              |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             | I/O  | GPIO6[16] — General purpose digital input/output pin.                |   |                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                               |   |                        |

|          |         |          |         |         |     |             |      |                                                                      | - | R — Function reserved. |

|          |         |          |         |         |     |             | I/O  | SGPIO6 — General purpose digital input/output pin.                   |   |                        |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                 |

|----------|---------|----------|---------|---------|-----|-------------|------|-------------------------------------------------------------|

| PE_6     | M16     | -        | 124     | -       | [2] | N;          | -    | R — Function reserved.                                      |

|          |         |          |         |         |     | PU          | 0    | CTOUT_2 — SCT output 2. Match output 2 of timer 0.          |

|          |         |          |         |         |     |             | I    | <b>U1_RI</b> — Ring Indicator input for UART 1.             |

|          |         |          |         |         |     |             | I/O  | EMC_D25 — External memory data line 25.                     |

|          |         |          |         |         |     |             | I/O  | <b>GPIO7[6]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

| PE_7     | F15     | -        | 149     | -       | [2] | N;          | -    | R — Function reserved.                                      |

|          |         |          |         |         |     | PU          | 0    | <b>CTOUT_5</b> — SCT output 5. Match output 3 of timer 3.   |

|          |         |          |         |         |     |             | I    | <b>U1_CTS</b> — Clear to Send input for UART1.              |

|          |         |          |         |         |     |             | I/O  | EMC_D26 — External memory data line 26.                     |

|          |         |          |         |         |     |             | I/O  | GPI07[7] — General purpose digital input/output pin.        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

| PE_8     | F14     | -        | 150     | -       | [2] | N;          | -    | R — Function reserved.                                      |

|          |         |          |         |         |     | PU          | 0    | <b>CTOUT_4</b> — SCT output 4. Match output 3 of timer 3.   |

|          |         |          |         |         |     |             | I    | <b>U1_DSR</b> — Data Set Ready input for UART 1.            |

|          |         |          |         |         |     |             | I/O  | EMC_D27 — External memory data line 27.                     |

|          |         |          |         |         |     |             | I/O  | GPIO7[8] — General purpose digital input/output pin.        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

| PE_9     | E16     | -        | 152     | -       | [2] | N;          | -    | R — Function reserved.                                      |

|          |         |          |         |         |     | PU          | I    | <b>CTIN_4</b> — SCT input 4. Capture input 2 of timer 1.    |

|          |         |          |         |         |     |             | I    | <b>U1_DCD</b> — Data Carrier Detect input for UART 1.       |

|          |         |          |         |         |     |             | I/O  | EMC_D28 — External memory data line 28.                     |

|          |         |          |         |         |     |             | I/O  | <b>GPIO7[9]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

Table 3.

Pin description ...continued

## 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |                                | Reset state | Type     | Description                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|----------|---------|----------|---------|---------|--------------------------------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|------------------------|--|--|--|--|-----|----------------------------------------------------|

| PF_6     | E7      | -        | 192     | -       | [5]                            | N;          | -        | R — Function reserved.                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                | PU          | I/O      | <b>U3_DIR</b> — RS-485/EIA-485 output enable/direction control for USART3.                                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | 0        | TRACEDATA[1] — Trace data, bit 1.                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | GPI07[20] — General purpose digital input/output pin.                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | -        | R — Function reserved.                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | SGPI05 — General purpose digital input/output pin.                                                                                                                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | <b>I2S1_TX_SDA</b> — I2S1 transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>PS-bus specification</i> .      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | AI       | <b>ADC1_3</b> — ADC1 and ADC0, input channel 3. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

| PF_7     | B7      | -        | 193     | -       | [5]                            | N;          | -        | R — Function reserved.                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          | PU      |          | PU      | I/O     | U3_BAUD — Baud pin for USART3. |             |          |                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | SSP1_MOSI — Master Out Slave in for SSP1.                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | 0        | TRACEDATA[2] — Trace data, bit 2.                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | GPI07[21] — General purpose digital input/output pin.                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | -        | R — Function reserved.                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | SGPIO6 — General purpose digital input/output pin.                                                                                                                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | <b>I2S1_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>PS-bus specification</i> .         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | AI/<br>O | <b>ADC1_7</b> — ADC1 and ADC0, input channel 7 or band gap output. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

| PF_8     | E6      | -        | -       | -       | [5]                            | N;          | -        | R — Function reserved.                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                | PU          | I/O      | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I        | CTIN_2 — SCT input 2. Capture input 2 of timer 0.                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | 0        | TRACEDATA[3] — Trace data, bit 3.                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | I/O      | GPIO7[22] — General purpose digital input/output pin.                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | -        | R — Function reserved.                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             |          |                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  | I/O | SGPI07 — General purpose digital input/output pin. |

|          |         |          |         |         |                                |             |          |                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | - | R — Function reserved. |  |  |  |  |     |                                                    |

|          |         |          |         |         |                                |             | AI       | <b>ADC0_2</b> — ADC0 and ADC1, input channel 2. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |  |  |  |  |     |                                                    |

#### Table 3. Pin description ...continued

32-bit ARM Cortex-M4/M0 microcontroller

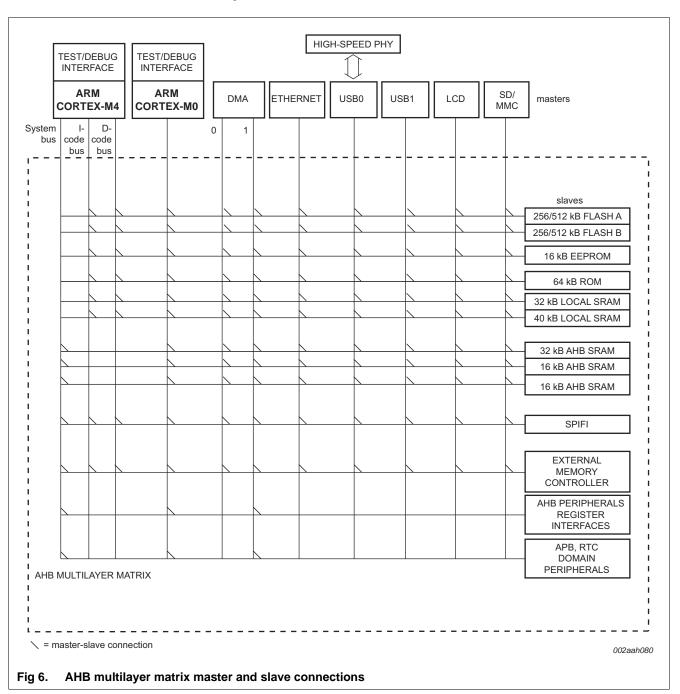

## 7.5 AHB multilayer matrix

## 7.6 Nested Vectored Interrupt Controller (NVIC)

The NVIC is an integral part of the Cortex-M4. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

The ARM Cortex-M0 co-processor has its own NVIC with 32 vectored interrupts. Most peripheral interrupts are shared between the Cortex-M0 and Cortex-M4 NVICs.

LPC435X\_3X\_2X\_1X

#### 32-bit ARM Cortex-M4/M0 microcontroller

### 7.6.1 Features

- ARM Cortex-M4 core:

- Controls system exceptions and peripheral interrupts

- Support for up to 53 vectored interrupts

- Eight programmable interrupt priority levels with hardware priority level masking

- Relocatable vector table

- Non-Maskable Interrupt (NMI)

- Software interrupt generation

- ARM Cortex-M0 core:

- Support for up to 32 interrupts

- Four programmable interrupt priority levels with hardware priority level masking

### 7.6.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

# 7.7 System Tick timer (SysTick)

The ARM Cortex-M4 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a 10 ms interval.

Remark: The SysTick is not included in the ARM Cortex-M0 core implementation.

### 7.8 Event router

The event router combines various internal signals, interrupts, and the external interrupt pins (WAKEUP[3:0]) to create an interrupt in the NVIC, if enabled. In addition, the event router creates a wake-up signal to the ARM core and the CCU for waking up from Sleep, Deep-sleep, Power-down, and Deep power-down modes. Individual events can be configured as edge or level sensitive and can be enabled or disabled in the event router. The event router can be battery powered.

The following events if enabled in the event router can create a wake-up signal from sleep, deep-sleep, power-down, and deep power-down modes and/or create an interrupt:

- External pins WAKEUP0/1/2/3 and RESET

- Alarm timer, RTC (32 kHz oscillator running)

The following events if enabled in the event router can create a wake-up signal from sleep mode only and/or create an interrupt:

- WWDT, BOD interrupts.

- C\_CAN0/1 and QEI interrupts.

- Ethernet, USB0, USB1 signals.

- Selected outputs of combined timers (SCTimer/PWM and timer0/1/3).

### 32-bit ARM Cortex-M4/M0 microcontroller

The timer/counter is designed to count cycles of the system derived clock or an externally-supplied clock. It can optionally generate interrupts, generate timed DMA requests, or perform other actions at specified timer values, based on four match registers. Each timer/counter also includes two capture inputs to trap the timer value when an input signal transitions, optionally generating an interrupt.

### 7.20.1.1 Features

- A 32-bit timer/counter with a programmable 32-bit prescaler.

- Counter or timer operation.

- Two 32-bit capture channels per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event can also generate an interrupt.

- Four 32-bit match registers that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- Up to two match registers can be used to generate timed DMA requests.

### 7.20.2 Motor control PWM

The motor control PWM is a specialized PWM supporting 3-phase motors and other combinations. Feedback inputs are provided to automatically sense rotor position and use that information to ramp speed up or down. An abort input causes the PWM to release all motor drive outputs immediately. At the same time, the motor control PWM is highly configurable for other generalized timing, counting, capture, and compare applications.

### 7.20.3 Quadrature Encoder Interface (QEI)

A quadrature encoder, also known as a 2-channel incremental encoder, converts angular displacement into two pulse signals. By monitoring both the number of pulses and the relative phase of the two signals, the user code can track the position, direction of rotation, and velocity. In addition, a third channel, or index signal, can be used to reset the position counter. The quadrature encoder interface decodes the digital pulses from a quadrature encoder wheel to integrate position over time and determine direction of rotation. In addition, the QEI can capture the velocity of the encoder wheel.

#### 7.20.3.1 Features

- Tracks encoder position.

- Increments/decrements depending on direction.

- Programmable for 2× or 4× position counting.

- Velocity capture using built-in timer.

- Velocity compare function with "less than" interrupt.

#### 32-bit ARM Cortex-M4/M0 microcontroller

### 7.23.7 System PLL1

The PLL1 accepts an input clock frequency from an external oscillator in the range of 1 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz. This range is possible through an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The output divider can be set to divide by 2, 4, 8, or 16 to produce the output clock. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset. After reset, software can enable the PLL. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

### 7.23.8 Reset Generation Unit (RGU)

The RGU allows generation of independent reset signals for individual blocks and peripherals on the LPC435x/3x/2x/1x.

### 7.23.9 Power Management Controller (PMC)

The PMC controls the power to the cores, peripherals, and memories.

The LPC435x/3x/2x/1x support the following power modes in order from highest to lowest power consumption:

- 1. Active mode

- 2. Sleep mode

- 3. Power-down modes:

- a. Deep-sleep mode

- b. Power-down mode

- c. Deep power-down mode

Active mode and sleep mode apply to the state of the core. In a dual-core system, either core can be in active or sleep mode independently of the other core.

If the core is in Active mode, it is fully operational and can access peripherals and memories as configured by software. If the core is in Sleep mode, it receives no clocks, but peripherals and memories remain running.

Either core can enter sleep mode from active mode independently of the other core and while the other core remains in active mode or is in sleep mode.

Power-down modes apply to the entire system. In the Power-down modes, both cores and all peripherals except for peripherals in the always-on power domain are shut down. Memories can remain powered for retaining memory contents as defined by the individual power-down mode.

Either core in active mode can put the part into one of the three power down modes if the core is enabled to do so. If both cores are enabled for putting the system into power-down, then the system enters power-down only once both cores have received a WFI or WFE instruction.

### 32-bit ARM Cortex-M4/M0 microcontroller

Wake-up from sleep mode is caused by an interrupt or event in the core's NVIC. The interrupt is captured in the NVIC and an event is captured in the Event router. Both cores can wake up from sleep mode independently of each other.

Wake-up from the Power-down modes, Deep-sleep, Power-down, and Deep power-down, is caused by an event on the WAKEUP pins or an event from the RTC or alarm timer.

When waking up from Deep power-down mode, the part resets and attempts to boot.

## 7.23.10 Power control

The LPC435x/3x/2x/1x feature several independent power domains to control power to the core and the peripherals (see <u>Figure 9</u>). The RTC and its associated peripherals (the alarm timer, the CREG block, the OTP controller, the back-up registers, and the event router) are located in the RTC power-domain. The main regulator or a battery supply can power the RTC. A power selector switch ensures that the RTC block is always powered on.

## **NXP Semiconductors**

# LPC435x/3x/2x/1x

120

32-bit ARM Cortex-M4/M0 microcontroller

Deep-sleep mode

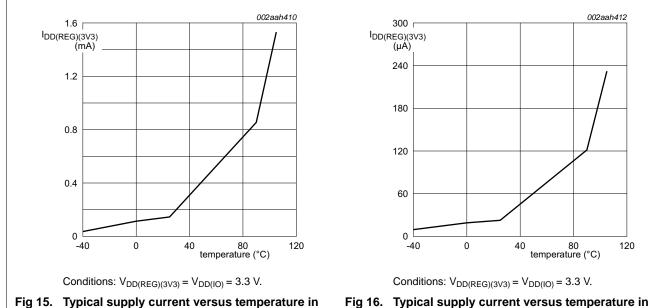

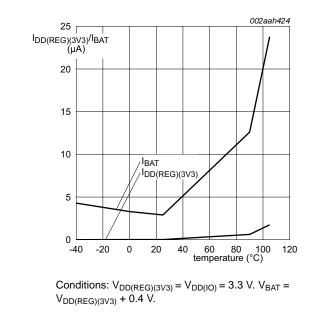

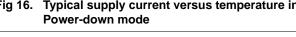

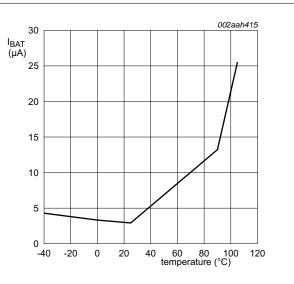

Fig 17. Typical supply current versus temperature in Deep power-down mode

Conditions:  $V_{BAT}$  = 3.6 V.  $V_{DD(REG)(3V3)}$  not present.

32-bit ARM Cortex-M4/M0 microcontroller

## 11.2 Wake-up times

# Table 17. Dynamic characteristic: Wake-up from Deep-sleep, Power-down, and Deep power-down modes

$T_{amb} = -40 \ ^{\circ}C \ to +105 \ ^{\circ}C$

| Symbol            | Parameter    | Conditions                             |     | Min                   | Typ <u>[1]</u>        | Max | Unit |

|-------------------|--------------|----------------------------------------|-----|-----------------------|-----------------------|-----|------|

| t <sub>wake</sub> | wake-up time | from Sleep mode                        | [2] | $3\times T_{cy(clk)}$ | $5\times T_{cy(clk)}$ | -   | ns   |

|                   |              | from Deep-sleep and<br>Power-down mode |     | 12                    | 51                    | -   | μS   |

|                   |              | from Deep power-down mode              |     | -                     | 200                   | -   | μs   |

|                   |              | after reset                            |     | -                     | 200                   | -   | μs   |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2]  $T_{cy(clk)} = 1/CCLK$  with CCLK = CPU clock frequency.

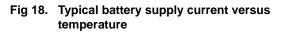

## **11.3** External clock for oscillator in slave mode

**Remark:** The input voltage on the XTAL1/2 pins must be  $\leq 1.2$  V (see <u>Table 11</u>). For connecting the oscillator to the XTAL pins, also see <u>Section 13.2</u> and <u>Section 13.4</u>.

#### Table 18. Dynamic characteristic: external clock

$T_{amb} = -40 \text{ °C to } +105 \text{ °C}; V_{DD(IO)} \text{ over specified ranges.}$

| Symbol               | Parameter            | Conditions |   | Min                     | Max                     | Unit |

|----------------------|----------------------|------------|---|-------------------------|-------------------------|------|

| f <sub>osc</sub>     | oscillator frequency |            |   | 1                       | 25                      | MHz  |