Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                 |

|----------------------------|-------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                          |

| Core Processor             | ARM® Cortex®-M4/M0                                                                              |

| Core Size                  | 32-Bit Dual-Core                                                                                |

| Speed                      | 204MHz                                                                                          |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                                         |

| Number of I/O              | 49                                                                                              |

| Program Memory Size        | 768KB (768K x 8)                                                                                |

| Program Memory Type        | FLASH                                                                                           |

| EEPROM Size                | 16K x 8                                                                                         |

| RAM Size                   | 136K x 8                                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                     |

| Data Converters            | A/D 4x10b; D/A 1x10b                                                                            |

| Oscillator Type            | Internal                                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                              |

| Mounting Type              | Surface Mount                                                                                   |

| Package / Case             | 100-TFBGA                                                                                       |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4325jet100e                          |

|                            |                                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M4/M0 microcontroller

## 4.1 Ordering options

Table 2.Ordering options

|               | <u> </u>    |              |              |            |     |          |                          |                                        |                   |     |              |                              |      |

|---------------|-------------|--------------|--------------|------------|-----|----------|--------------------------|----------------------------------------|-------------------|-----|--------------|------------------------------|------|

| Type number   | Flash total | Flash bank A | Flash bank B | Total SRAM | ГСD | Ethernet | USB0 (Host, Device, OTG) | USB1 (Host, Device)/<br>ULPI interface | Motor control PWM | QEI | ADC channels | Temperature range <u>[1]</u> | GPIO |

| LPC4357FET256 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | yes | yes      | yes                      | yes/yes                                | yes               | yes | 8            | F                            | 164  |

| LPC4357JET256 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | yes | yes      | yes                      | yes/yes                                | yes               | yes | 8            | J                            | 164  |

| LPC4357JBD208 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | yes | yes      | yes                      | yes/yes                                | yes               | yes | 8            | J                            | 142  |

| LPC4353FET256 | 512 kB      | 256 kB       | 256 kB       | 136 kB     | yes | yes      | yes                      | yes/yes                                | yes               | yes | 8            | F                            | 164  |

| LPC4353JET256 | 512 kB      | 256 kB       | 256 kB       | 136 kB     | yes | yes      | yes                      | yes/yes                                | yes               | yes | 8            | J                            | 164  |

| LPC4353JBD208 | 512 kB      | 256 kB       | 256 kB       | 136 kB     | yes | yes      | yes                      | yes/yes                                | yes               | yes | 8            | J                            | 142  |

| LPC4337FET256 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | yes      | yes                      | yes/yes                                | yes               | yes | 8            | F                            | 164  |

| LPC4337JET256 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | yes      | yes                      | yes/yes                                | yes               | yes | 8            | J                            | 164  |

| LPC4337JBD144 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | yes      | yes                      | yes/yes                                | yes               | no  | 8            | J                            | 83   |

| LPC4337JET100 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | yes      | yes                      | yes/no                                 | no                | no  | 4            | J                            | 49   |

| LPC4333FET256 | 512 kB      | 256 kB       | 256 kB       | 136 kB     | no  | yes      | yes                      | yes/yes                                | yes               | yes | 8            | F                            | 164  |

| LPC4333JET256 | 512 kB      | 256 kB       | 256 kB       | 136 kB     | no  | yes      | yes                      | yes/yes                                | yes               | yes | 8            | J                            | 164  |

| LPC4333JBD144 | 512 kB      | 256 kB       | 256 kB       | 136 kB     | no  | yes      | yes                      | yes/yes                                | yes               | no  | 8            | J                            | 83   |

| LPC4333JET100 | 512 kB      | 256 kB       | 256 kB       | 136 kB     | no  | yes      | yes                      | yes/no                                 | no                | no  | 4            | J                            | 49   |

| LPC4327JBD144 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | no       | yes                      | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4327JET100 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | no       | yes                      | no/no                                  | no                | no  | 4            | J                            | 49   |

| LPC4325JBD144 | 768 kB      | 384 kB       | 384 kB       | 136 kB     | no  | no       | yes                      | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4325JET100 | 768 kB      | 384 kB       | 384 kB       | 136 kB     | no  | no       | yes                      | no/no                                  | no                | no  | 4            | J                            | 49   |

| LPC4323JBD144 | 512 kB      | 256 kB       | 256 kB       | 104 kB     | no  | no       | yes                      | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4323JET100 | 512 kB      | 256 kB       | 256 kB       | 104 kB     | no  | no       | yes                      | no/no                                  | no                | no  | 4            | J                            | 49   |

| LPC4322JBD144 | 512 kB      | 512 kB       | 0 kB         | 104 kB     | no  | no       | yes                      | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4322JET100 | 512 kB      | 512 kB       | 0 kB         | 104 kB     | no  | no       | yes                      | no/no                                  | no                | no  | 4            | J                            | 49   |

| LPC4317JBD144 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | no       | no                       | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4317JET100 | 1 MB        | 512 kB       | 512 kB       | 136 kB     | no  | no       | no                       | no/no                                  | no                | no  | 4            | J                            | 49   |

| LPC4315JBD144 | 768 kB      | 384 kB       | 384 kB       | 136 kB     | no  | no       | no                       | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4315JET100 | 768 kB      | 384 kB       | 384 kB       | 136 kB     | no  | no       | no                       | no/no                                  | no                | no  | 4            | J                            | 49   |

| LPC4313JBD144 | 512 kB      | 256 kB       | 256 kB       | 104 kB     | no  | no       | no                       | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4313JET100 | 512 kB      | 256 kB       | 256 kB       | 104 kB     | no  | no       | no                       | no/no                                  | no                | no  | 4            | J                            | 49   |

| LPC4312JBD144 | 512 kB      | 512 kB       | 0 kB         | 104 kB     | no  | no       | no                       | no/no                                  | yes               | no  | 8            | J                            | 83   |

| LPC4312JET100 | 512 kB      | 512 kB       | 0 kB         | 104 kB     | no  | no       | no                       | no/no                                  | no                | no  | 4            | J                            | 49   |

[1]  $J = -40 \degree C$  to +105  $\degree C$ ;  $F = -40 \degree C$  to +85  $\degree C$ .

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state                                  | Type | Description                                                                                                                                                                                        |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|----------|---------|----------|---------|---------|-----|----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|---|------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|------------------------|

| P1_5     | R5      | J4       | 65      | 48      | [2] | N;                                           | I/O  | GPIO1[8] — General purpose digital input/output pin.                                                                                                                                               |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     | PU                                           | 0    | CTOUT_10 — SCT output 10. Match output 3 of timer 3.                                                                                                                                               |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | -    | R — Function reserved.                                                                                                                                                                             |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | 0    | <b>EMC_CS0</b> — LOW active Chip Select 0 signal.                                                                                                                                                  |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | I    | <b>USB0_PWR_FAULT</b> — Port power fault signal indicating overcurrent condition; this signal monitors over-current on the USB bus (external circuitry required to detect over-current condition). |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | I/O  | SSP1_SSEL — Slave Select for SSP1.                                                                                                                                                                 |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | I/O  | SGPIO15 — General purpose digital input/output pin.                                                                                                                                                |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         | 0   | <b>SD_POW</b> — SD/MMC power monitor output. |      |                                                                                                                                                                                                    |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| P1_6     |         |          |         |         | [2] |                                              | I/O  | GPIO1[9] — General purpose digital input/output pin.                                                                                                                                               |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     | PU                                           | I    | CTIN_5 — SCT input 5. Capture input 2 of timer 2.                                                                                                                                                  |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | -    | R — Function reserved.                                                                                                                                                                             |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | 0    | <b>EMC_WE</b> — LOW active Write Enable signal.                                                                                                                                                    |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | -    | R — Function reserved.                                                                                                                                                                             |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | 0    | <b>EMC_BLS0</b> — LOW active Byte Lane select signal 0.                                                                                                                                            |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | I/O  | SGPI014 — General purpose digital input/output pin.                                                                                                                                                |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | I/O  | <b>SD_CMD</b> — SD/MMC command signal.                                                                                                                                                             |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

| P1_7     | T5      | G4       | 69      | 50      | [2] | N;                                           | I/O  | <b>GPIO1[0]</b> — General purpose digital input/output pin.                                                                                                                                        |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     | PU                                           | I    | <b>U1_DSR</b> — Data Set Ready input for UART1.                                                                                                                                                    |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | 0    | <b>CTOUT_13</b> — SCT output 13. Match output 3 of timer 3.                                                                                                                                        |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | I/O  | <b>EMC_D0</b> — External memory data line 0.                                                                                                                                                       |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | 0    | <b>USB0_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active HIGH).                                                    |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              |      |                                                                                                                                                                                                    |  |  |  |  |  |  | Add a pull-down resistor to disable the power switch at reset.<br>This signal has opposite polarity compared to the<br>USB_PPWR used on other NXP LPC parts. |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              |      |                                                                                                                                                                                                    |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | - | R — Function reserved. |

|          |         |          |         |         |     |                                              |      |                                                                                                                                                                                                    |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  | - | R — Function reserved. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

|          |         |          |         |         |     |                                              | -    | R — Function reserved.                                                                                                                                                                             |  |  |  |  |  |  |                                                                                                                                                              |  |  |  |  |  |  |  |   |                        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |                        |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                                                        |

|----------|---------|----------|---------|---------|-----|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2_2     | M15     | F5       | 121     | 84      | [2] | N;          | I/O  | SGPIO6 — General purpose digital input/output pin.                                                                                                                                                 |

|          |         |          |         |         |     | PU          | I/O  | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                                         |

|          |         |          |         |         |     |             |      | EMC_A11 — External memory address line 11.                                                                                                                                                         |

|          |         |          |         |         |     |             | 0    | <b>USB0_IND1</b> — USB0 port indicator LED control output 1.                                                                                                                                       |

|          |         |          |         |         |     |             | I/O  | GPIO5[2] — General purpose digital input/output pin.                                                                                                                                               |

|          |         |          |         |         |     |             | I    | CTIN_6 — SCT input 6. Capture input 1 of timer 3.                                                                                                                                                  |

|          |         |          |         |         |     |             | I    | T3_CAP2 — Capture input 2 of timer 3.                                                                                                                                                              |

|          |         |          |         |         |     |             | 0    | EMC_CS1 — LOW active Chip Select 1 signal.                                                                                                                                                         |

| P2_3     | J12     | D8       | 127     | 87      | [3] | N;          | I/O  | SGPI012 — General purpose digital input/output pin.                                                                                                                                                |

|          |         |          |         |         |     | PU          | I/O  | <b>I2C1_SDA</b> — I <sup>2</sup> C1 data input/output (this pin does not use a specialized I2C pad).                                                                                               |

|          |         |          |         |         |     |             | 0    | <b>U3_TXD</b> — Transmitter output for USART3. See <u>Table 4</u> for ISP mode.                                                                                                                    |

|          |         |          |         |         |     |             | I    | <b>CTIN_1</b> — SCT input 1. Capture input 1 of timer 0. Capture input 1 of timer 2.                                                                                                               |

|          |         |          |         |         |     |             | I/O  | GPIO5[3] — General purpose digital input/output pin.                                                                                                                                               |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                                                                             |

|          |         |          |         |         |     |             | 0    | T3_MAT0 — Match output 0 of timer 3.                                                                                                                                                               |

|          |         |          |         |         |     |             | 0    | <b>USB0_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active HIGH).                                                    |

|          |         |          |         |         |     |             |      | Add a pull-down resistor to disable the power switch at reset.<br><u>This signal has opposite polarity compared to the</u><br>USB_PPWR used on other NXP LPC parts.                                |

| P2_4     | K11     | D9       | 128     | 88      | [3] | N;          | I/O  | SGPI013 — General purpose digital input/output pin.                                                                                                                                                |

|          |         |          |         |         |     | PU          | I/O  | <b>I2C1_SCL</b> — I <sup>2</sup> C1 clock input/output (this pin does not use a specialized I2C pad).                                                                                              |

|          |         |          |         |         |     |             | I    | <b>U3_RXD</b> — Receiver input for USART3. See <u>Table 4</u> for ISP mode.                                                                                                                        |

|          |         |          |         |         |     |             | I    | CTIN_0 — SCT input 0. Capture input 0 of timer 0, 1, 2, 3.                                                                                                                                         |

|          |         |          |         |         |     |             | I/O  | GPIO5[4] — General purpose digital input/output pin.                                                                                                                                               |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                                                                                                                             |

|          |         |          |         |         |     |             | 0    | T3_MAT1 — Match output 1 of timer 3.                                                                                                                                                               |

|          |         |          |         |         |     |             | I    | <b>USB0_PWR_FAULT</b> — Port power fault signal indicating overcurrent condition; this signal monitors over-current on the USB bus (external circuitry required to detect over-current condition). |

Table 3.

Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name    | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state            | Type | Description                                                                                                                                                               |                                                                                                                                                                                |                        |

|-------------|---------|----------|---------|---------|-----|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| P3_2        | F11     | G6       | 166     | 116     | [2] | OL;<br>PU              | I/O  | <b>I2S0_TX_SDA</b> — I2S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification.          |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | I/O  | <b>I2S0_RX_SDA</b> — I2S Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification.           |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | 0    | CAN0_TD — CAN transmitter output.                                                                                                                                         |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | 0    | <b>USB1_IND0</b> — USB1 Port indicator LED control output 0.                                                                                                              |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | I/O  | GPIO5[9] — General purpose digital input/output pin.                                                                                                                      |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | -    | R — Function reserved.                                                                                                                                                    |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | 0    | LCD_VD14 — LCD data.                                                                                                                                                      |                                                                                                                                                                                |                        |

|             |         |          |         |         | -   | R — Function reserved. |      |                                                                                                                                                                           |                                                                                                                                                                                |                        |

| P3_3 B14 A7 |         |          | 169     | 118     | [4] | N;                     | -    | R — Function reserved.                                                                                                                                                    |                                                                                                                                                                                |                        |

|             |         |          |         |         |     | PU                     | I/O  | SPI_SCK — Serial clock for SPI.                                                                                                                                           |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | I/O  | SSP0_SCK — Serial clock for SSP0.                                                                                                                                         |                                                                                                                                                                                |                        |

|             |         |          |         |         |     | -                      | 0    | SPIFI_SCK — Serial clock for SPIFI.                                                                                                                                       |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | 0    | CGU_OUT1 — CGU spare clock output 1.                                                                                                                                      |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        |      |                                                                                                                                                                           | -                                                                                                                                                                              | R — Function reserved. |

|             |         |          |         |         |     |                        | 0    | I2S0_TX_MCLK — I2S transmit master clock.                                                                                                                                 |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | I/O  | <b>I2S1_TX_SCK</b> — Transmit Clock. It is driven by the master<br>and received by the slave. Corresponds to the signal SCK in<br>the I <sup>2</sup> S-bus specification. |                                                                                                                                                                                |                        |

| P3_4        | A15     | B8       | 171     | 119     | [2] | N;                     | I/O  | GPIO1[14] — General purpose digital input/output pin.                                                                                                                     |                                                                                                                                                                                |                        |

|             |         |          |         |         |     | PU                     | -    | R — Function reserved.                                                                                                                                                    |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | -    | R — Function reserved.                                                                                                                                                    |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | I/O  | SPIFI_SIO3 — I/O lane 3 for SPIFI.                                                                                                                                        |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | 0    | U1_TXD — Transmitter output for UART 1.                                                                                                                                   |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        |      | I/O                                                                                                                                                                       | <b>I2S0_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> S-bus specification. |                        |

|             |         |          |         |         |     |                        | I/O  | <b>I2S1_RX_SDA</b> — I2S1 Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification.          |                                                                                                                                                                                |                        |

|             |         |          |         |         |     |                        | 0    | LCD_VD13 — LCD data.                                                                                                                                                      |                                                                                                                                                                                |                        |

Table 3.

Pin description ...continued

LPC435X\_3X\_2X\_1X

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                                         |

|----------|---------|----------|---------|---------|-----|-------------|------|-------------------------------------------------------------------------------------|

| PC_6     | H6      | -        | 22      | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I/O  | USB1_ULPI_D2 — ULPI link bidirectional data line 2.                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | ENET_RXD2 — Ethernet receive data 2 (MII interface).                                |

|          |         |          |         |         |     |             | I/O  | GPIO6[5] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | T3_CAP3 — Capture input 3 of timer 3.                                               |

|          |         |          |         |         |     |             | I/O  | <b>SD_DAT2</b> — SD/MMC data bus line 2.                                            |

| PC_7     | G5      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I/O  | USB1_ULPI_D1 — ULPI link bidirectional data line 1.                                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | ENET_RXD3 — Ethernet receive data 3 (MII interface).                                |

|          |         |          |         |         |     |             | I/O  | GPIO6[6] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | 0    | T3_MAT0 — Match output 0 of timer 3.                                                |

|          |         |          |         |         |     |             | I/O  | SD_DAT3 — SD/MMC data bus line 3.                                                   |

| PC_8     | N4      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I/O  | <b>USB1_ULPI_D0</b> — ULPI link bidirectional data line 0.                          |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | <b>ENET_RX_DV</b> — Ethernet Receive Data Valid (RMII/MII interface).               |

|          |         |          |         |         |     |             | I/O  | GPIO6[7] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | 0    | T3_MAT1 — Match output 1 of timer 3.                                                |

|          |         |          |         |         |     |             | I    | <b>SD_CD</b> — SD/MMC card detect input.                                            |

| PC_9     | K2      | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     | PU          | I    | <b>USB1_ULPI_NXT</b> — ULPI link NXT signal. Data flow control signal from the PHY. |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | I    | ENET_RX_ER — Ethernet receive error (MII interface).                                |

|          |         |          |         |         |     |             | I/O  | GPIO6[8] — General purpose digital input/output pin.                                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                              |

|          |         |          |         |         |     |             | 0    | T3_MAT2 — Match output 2 of timer 3.                                                |

|          |         |          |         |         |     |             | 0    | <b>SD_POW</b> — SD/MMC power monitor output.                                        |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                  |

|----------|---------|----------|---------|---------|-----|-------------|------|--------------------------------------------------------------|

| PD_15    | T15     | -        | 101     | -       | [2] | N;          | -    | R — Function reserved.                                       |

|          |         |          |         |         |     | PU          | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | I/O  | EMC_A17 — External memory address line 17.                   |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | I/O  | <b>GPIO6[29]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     |             | I    | <b>SD_WP</b> — SD/MMC card write protect input.              |

|          |         |          |         |         |     |             | 0    | CTOUT_8 — SCT output 8. Match output 0 of timer 2.           |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

| PD_16    | R14     | -        | 104     | -       | [2] | N;          | -    | R — Function reserved.                                       |

|          |         |          |         |         |     | PU          | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | I/O  | <b>EMC_A16</b> — External memory address line 16.            |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | I/O  | <b>GPIO6[30]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     |             | 0    | <b>SD_VOLT2</b> — SD/MMC bus voltage select output 2.        |

|          |         |          |         |         |     |             | 0    | <b>CTOUT_12</b> — SCT output 12. Match output 3 of timer 3.  |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

| PE_0     | P14     | -        | 106     | -       | [2] | N;<br>PU    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     | PU          | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | I/O  | <b>EMC_A18</b> — External memory address line 18.            |

|          |         |          |         |         |     |             | I/O  | <b>GPIO7[0]</b> — General purpose digital input/output pin.  |

|          |         |          |         |         |     |             | 0    | CAN1_TD — CAN1 transmitter output.                           |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

| PE_1     | N14     | -        | 112     | -       | [2] | N;          | -    | R — Function reserved.                                       |

|          |         |          |         |         |     | PU          | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | I/O  | EMC_A19 — External memory address line 19.                   |

|          |         |          |         |         |     |             | I/O  | <b>GPIO7[1]</b> — General purpose digital input/output pin.  |

|          |         |          |         |         |     |             | I    | CAN1_RD — CAN1 receiver input.                               |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                       |

Table 3.

Pin description ...continued

| Table 3. | Pin d                     | escrip  | tion     | continu | ed      | otioncontinued |                                         |                                                       |                                                                                                                                                        |  |  |  |  |  |

|----------|---------------------------|---------|----------|---------|---------|----------------|-----------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin name |                           | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |                | Reset state                             | Type                                                  | Description                                                                                                                                            |  |  |  |  |  |

| PF_9     |                           | D6      | -        | 203     | -       | [5]            | N;                                      | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                | PU                                      | I/O                                                   | <b>U0_DIR</b> — RS-485/EIA-485 output enable/direction control for USART0.                                                                             |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | 0                                                     | CTOUT_1 — SCT output 1. Match output 3 of timer 3.                                                                                                     |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | I/O                                                   | GPI07[23] — General purpose digital input/output pin.                                                                                                  |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | I/O                                                   | SGPI03 — General purpose digital input/output pin.                                                                                                     |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | AI                                                    | <b>ADC1_2</b> — ADC1 and ADC0, input channel 2. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |  |  |  |  |  |

| PF_10    | _10 A3 - 205 - <u>[5]</u> |         |          |         |         | [5]            | N;                                      | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         | PU      | 0              | U0_TXD — Transmitter output for USART0. |                                                       |                                                                                                                                                        |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | I/O                                                   | GPI07[24] — General purpose digital input/output pin.                                                                                                  |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | I                                                     | <b>SD_WP</b> — SD/MMC card write protect input.                                                                                                        |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | AI                                                    | <b>ADC0_5</b> — ADC0 and ADC1, input channel 5. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |  |  |  |  |  |

| PF_11    |                           | A2      | -        | 207     | -       | [5]            | N;                                      | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                | PU                                      | I                                                     | U0_RXD — Receiver input for USART0.                                                                                                                    |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | -                                                     | R — Function reserved.                                                                                                                                 |  |  |  |  |  |

|          |                           |         |          |         |         |                | I/O                                     | GPI07[25] — General purpose digital input/output pin. |                                                                                                                                                        |  |  |  |  |  |

|          |                           |         |          |         |         |                | -                                       | R — Function reserved.                                |                                                                                                                                                        |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | 0                                                     | <b>SD_VOLT2</b> — SD/MMC bus voltage select output 2.                                                                                                  |  |  |  |  |  |

|          |                           |         |          |         |         | -              | R — Function reserved.                  |                                                       |                                                                                                                                                        |  |  |  |  |  |

|          |                           |         |          |         |         |                |                                         | AI                                                    | <b>ADC1_5</b> — ADC1 and ADC0, input channel 5. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |  |  |  |  |  |

|          |                           | -       | _        | -       |         |                | -                                       | -                                                     |                                                                                                                                                        |  |  |  |  |  |

Table 3.

Pin description ...continued

#### 32-bit ARM Cortex-M4/M0 microcontroller

**Remark:** Any interrupt can wake up the ARM Cortex-M4 from sleep mode if enabled in the NVIC.

## 7.9 Global Input Multiplexer Array (GIMA)

The GIMA allows to route signals to event-driven peripheral targets like the SCTimer/PWM, timers, event router, or the ADCs.

### 7.9.1 Features

- Single selection of a source.

- Signal inversion.

- Can capture a pulse if the input event source is faster than the target clock.

- Synchronization of input event and target clock.

- Single-cycle pulse generation for target.

### 7.10 On-chip static RAM

The LPC435x/3x/2x/1x support up to 136 kB SRAM with separate bus master access for higher throughput and individual power control for low power operation.

## 7.11 On-chip flash memory

The LPC435x/3x/2x/1x contain up to 1 MB of dual-bank flash program memory. With dual-bank flash memory, the user code can write or erase one flash bank while reading the other flash bank without interruption. A two-port flash accelerator maximizes the flash performance.

In-System Programming (ISP) and In-Application Programming (IAP) routines for programming the flash memory are provided in the Boot ROM.

## 7.12 EEPROM

The LPC435x/3x/2x/1x contain 16 kB of on-chip byte-erasable and byte-programmable EEPROM memory.

The EEPROM memory is divided into 128 pages. The user can access pages 1 through 127. Page 128 is protected.

## 7.13 Boot ROM

The internal ROM memory is used to store the boot code of the LPC435x/3x/2x/1x. After a reset, the ARM processor will start its code execution from this memory.

The boot ROM memory includes the following features:

- The ROM memory size is 64 kB.

- Supports booting from external static memory such as NOR flash, SPI flash, quad SPI flash, USB0, and USB1.

- Includes API for OTP programming.

- Includes a flexible USB device stack that supports Human Interface Device (HID), Mass Storage Class (MSC), and Device Firmware Upgrade (DFU) drivers.

LPC435X 3X 2X 1X

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Function | LBGA256                                  | TFBGA100                                          | LQFP208                                           | LQFP144                                           |

|----------|------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| OE       | EMC_OE                                   | EMC_OE                                            | EMC_OE                                            | EMC_OE                                            |

| WE       | EMC_WE                                   | EMC_WE                                            | EMC_WE                                            | EMC_WE                                            |

| CKEOUT   | EMC_<br>CKEOUT[3:0]                      | EMC_<br>CKEOUT[1:0]                               | EMC_<br>CKEOUT[1:0]                               | EMC_<br>CKEOUT[1:0]                               |

| CLK      | EMC_CLK[3:0];<br>EMC_CLK01,<br>EMC_CLK23 | EMC_CLK0,<br>EMC_CLK3;<br>EMC_CLK01,<br>EMC_CLK23 | EMC_CLK0,<br>EMC_CLK3;<br>EMC_CLK01,<br>EMC_CLK23 | EMC_CLK0,<br>EMC_CLK3;<br>EMC_CLK01,<br>EMC_CLK23 |

| DQMOUT   | EMC_<br>DQMOUT[3:0]                      | -                                                 | EMC_<br>DQMOUT[1:0]                               | EMC_<br>DQMOUT[1:0]                               |

| DYCS     | EMC_<br>DYCS[3:0]                        | EMC_DYCS[1:0]                                     | EMC_DYCS[2:0]                                     | EMC_DYCS[1:0]                                     |

| CAS      | EMC_CAS                                  | EMC_CAS                                           | EMC_CAS                                           | EMC_CAS                                           |

| RAS      | EMC_RAS                                  | EMC_RAS                                           | EMC_RAS                                           | EMC_RAS                                           |

## Table 6. EMC pinout for different packages

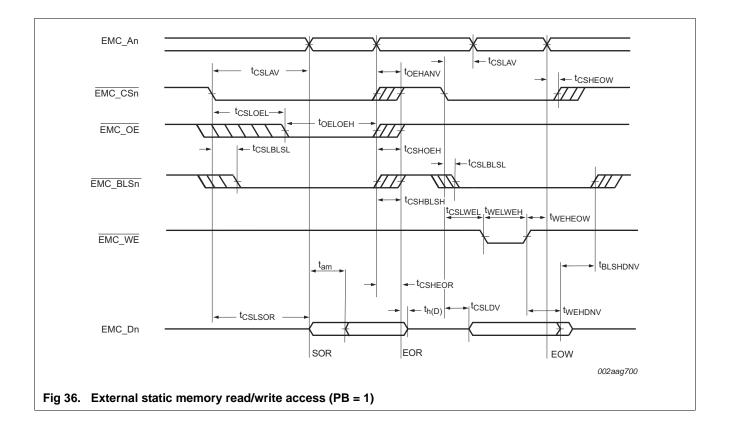

#### 7.18.4.1 Features

- Dynamic memory interface support including single data rate SDRAM.

- Asynchronous static memory device support including RAM, ROM, and NOR flash, with or without asynchronous page mode.

- Low transaction latency.

- Read and write buffers to reduce latency and to improve performance.

- 8/16/32 data and 24 address lines wide static memory support.

- 16 bit and 32 bit wide chip select SDRAM memory support.

- Static memory features include:

- Asynchronous page mode read

- Programmable Wait States

- Bus turnaround delay

- Output enable and write enable delays

- Extended wait

- Four chip selects for synchronous memory and four chip selects for static memory devices.

- Power-saving modes dynamically control EMC\_CKEOUT and EMC\_CLK signals to SDRAMs.

- Dynamic memory self-refresh mode controlled by software.

- Controller supports 2048 (A0 to A10), 4096 (A0 to A11), and 8192 (A0 to A12) row address synchronous memory parts. Those are typically 512 MB, 256 MB, and 128 MB parts, with 4, 8, 16, or 32 data bits per device.

- Separate reset domains allow the for auto-refresh through a chip reset if desired.

- SDRAM clock can run at full or half the Cortex-M4 core frequency.

Note: Synchronous static memory devices (synchronous burst mode) are not supported.

| All information provided in this document is subject to legal disclaimers. |

|----------------------------------------------------------------------------|

|                                                                            |

LPC435X 3X 2X 1X

© NXP Semiconductors N.V. 2016. All rights reserved.

#### 32-bit ARM Cortex-M4/M0 microcontroller

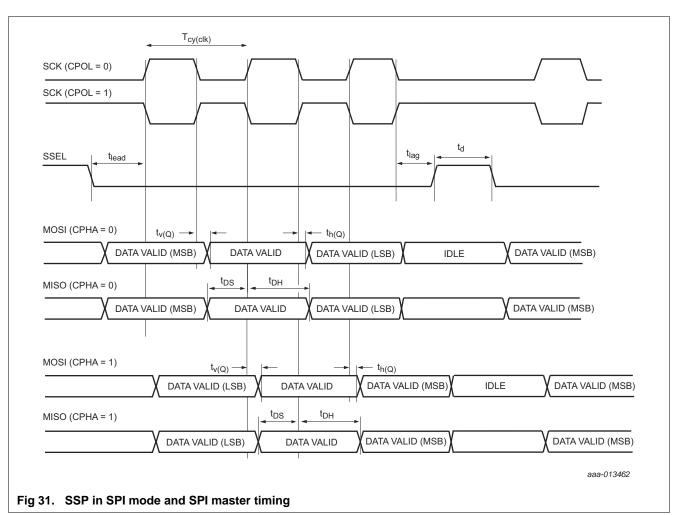

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses

- Synchronous serial communication

- Master or slave operation

- 8-frame FIFOs for both transmit and receive

- 4-bit to 16-bit frame

- DMA transfers supported by GPDMA

#### 7.19.5 I<sup>2</sup>C-bus interface

**Remark:** The LPC435x/3x/2x/1x each contain two I<sup>2</sup>C-bus interfaces.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock line (SCL) and a Serial Data line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (for example an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

#### 7.19.5.1 Features

- I<sup>2</sup>C0 is a standard I<sup>2</sup>C compliant bus interface with open-drain pins. I<sup>2</sup>C0 also supports Fast mode plus with bit rates up to 1 Mbit/s.