Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                          |

|----------------------------|-------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M0                                                                              |

| Core Size                  | 32-Bit Dual-Core                                                                                |

| Speed                      | 204MHz                                                                                          |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 83                                                                                              |

| Program Memory Size        | 1MB (1M × 8)                                                                                    |

| Program Memory Type        | FLASH                                                                                           |

| EEPROM Size                | 16K x 8                                                                                         |

| RAM Size                   | 136К х 8                                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                     |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                            |

| Oscillator Type            | Internal                                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                              |

| Mounting Type              | Surface Mount                                                                                   |

| Package / Case             | 144-LQFP                                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4327jbd144e                          |

|                            |                                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M4/M0 microcontroller

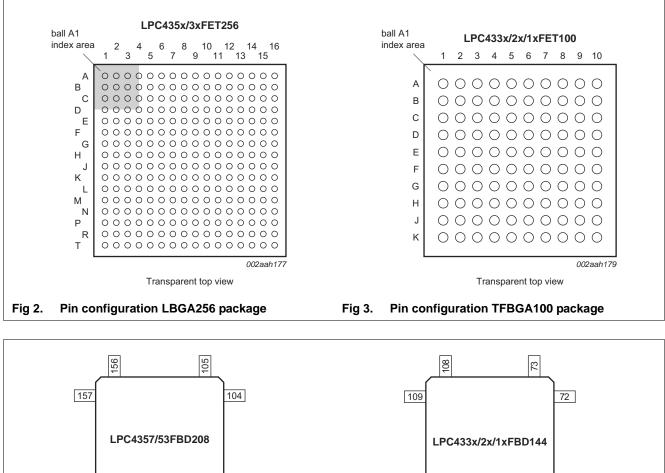

#### **Pinning information** 6.

## 6.1 Pinning

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                               |

|----------|---------|----------|---------|---------|-----|--------------------|------|-----------------------------------------------------------|

| P1_12    | R9      | K7       | 78      | 56      | [2] | N;                 | I/O  | GPI01[5] — General purpose digital input/output pin.      |

|          |         |          |         |         |     | PU                 | I    | U1_DCD — Data Carrier Detect input for UART1.             |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

|          |         |          |         |         |     |                    | I/O  | EMC_D5 — External memory data line 5.                     |

|          |         |          |         |         |     |                    | I    | T0_CAP1 — Capture input 1 of timer 0.                     |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

|          |         |          |         |         |     |                    | I/O  | SGPIO8 — General purpose digital input/output pin.        |

|          |         |          |         |         |     |                    | I/O  | SD_DAT3 — SD/MMC data bus line 3.                         |

| P1_13    | R10     | H8       | 83      | 60      | [2] | N;                 | I/O  | GPIO1[6] — General purpose digital input/output pin.      |

|          |         |          |         |         |     | PU                 | 0    | U1_TXD — Transmitter output for UART1.                    |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

|          |         |          |         |         |     |                    | I/O  | EMC_D6 — External memory data line 6.                     |

|          |         |          |         |         |     |                    | I    | T0_CAP0 — Capture input 0 of timer 0.                     |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

|          |         |          |         |         |     |                    | I/O  | SGPIO9 — General purpose digital input/output pin.        |

|          |         |          |         |         |     |                    | I    | <b>SD_CD</b> — SD/MMC card detect input.                  |

| P1_14    | R11     | J8       | 85      | 61      | [2] | N;                 | I/O  | GPIO1[7] — General purpose digital input/output pin.      |

|          |         |          |         |         |     | PU                 | I    | U1_RXD — Receiver input for UART1.                        |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

|          |         |          |         |         |     |                    | I/O  | EMC_D7 — External memory data line 7.                     |

|          |         |          |         |         |     |                    | 0    | T0_MAT2 — Match output 2 of timer 0.                      |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

|          |         |          |         |         |     |                    | I/O  | SGPIO10 — General purpose digital input/output pin.       |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

| P1_15    | T12     | K8       | 87      | 62      | [2] | N;                 | I/O  | GPIO0[2] — General purpose digital input/output pin.      |

|          |         |          |         |         |     | PU                 | 0    | U2_TXD — Transmitter output for USART2.                   |

|          |         |          |         |         |     |                    | I/O  | SGPIO2 — General purpose digital input/output pin.        |

|          |         |          |         |         |     |                    | I    | ENET_RXD0 — Ethernet receive data 0 (RMII/MII interface). |

|          |         |          |         |         |     |                    | 0    | T0_MAT1 — Match output 1 of timer 0.                      |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

|          |         |          |         |         |     |                    | I/O  | EMC_D8 — External memory data line 8.                     |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                    |

Table 3.

Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                   |

|----------|---------|----------|---------|---------|-----|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6_0     | M12     | H7       | 105     | 73      | [2] | N;                 | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     | PU                 | 0    | I2S0_RX_MCLK — I2S receive master clock.                                                                                                                      |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     |                    | I/O  | <b>I2S0_RX_SCK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the $l^2S$ -bus specification.     |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

| P6_1     | R15     | G5       | 107     | 74      | [2] | N;                 | I/O  | GPIO3[0] — General purpose digital input/output pin.                                                                                                          |

|          |         |          |         |         |     | PU                 | 0    | EMC_DYCS1 — SDRAM chip select 1.                                                                                                                              |

|          |         |          |         |         |     |                    | I/O  | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                    |

|          |         |          |         |         |     |                    | I/O  | <b>I2S0_RX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification.   |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     |                    | I    | T2_CAP0 — Capture input 2 of timer 2.                                                                                                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

| P6_2     | L13     | J9       | 111     | 78      | [2] | N;                 | I/O  | GPIO3[1] — General purpose digital input/output pin.                                                                                                          |

|          |         |          |         |         |     | PU                 | 0    | EMC_CKEOUT1 — SDRAM clock enable 1.                                                                                                                           |

|          |         |          |         |         |     |                    | I/O  | <b>U0_DIR</b> — RS-485/EIA-485 output enable/direction control for USART0.                                                                                    |

|          |         |          |         |         |     |                    | I/O  | <b>I2S0_RX_SDA</b> — I2S Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $PS$ -bus specification. |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

|          |         |          |         |         |     |                    | I    | T2_CAP1 — Capture input 1 of timer 2.                                                                                                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

| 1        |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                        |

Table 3.

Pin description ...continued

32-bit ARM Cortex-M4/M0 microcontroller

| Table 3. | Pin de | Pin descriptioncontinued |          |         |         |     |             |                                                           |                                                                                    |

|----------|--------|--------------------------|----------|---------|---------|-----|-------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|

| Pin name |        | LBGA256                  | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type                                                      | Description                                                                        |

| PB_1     |        | A14                      | -        | 175     | -       | [2] | N;          | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     | PU          | I                                                         | <b>USB1_ULPI_DIR</b> — ULPI link DIR signal. Controls the ULP data line direction. |

|          |        |                          |          |         |         |     |             | 0                                                         | LCD_VD22 — LCD data.                                                               |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | I/O                                                       | GPIO5[21] — General purpose digital input/output pin.                              |

|          |        |                          |          |         |         |     |             | 0                                                         | CTOUT_6 — SCT output 6. Match output 2 of timer 1.                                 |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

| PB_2     |        | B12                      | -        | 177     | -       | [2] | N;          | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     | PU          | I/O                                                       | USB1_ULPI_D7 — ULPI link bidirectional data line 7.                                |

|          |        |                          |          |         |         |     |             | 0                                                         | LCD_VD21 — LCD data.                                                               |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | I/O                                                       | GPIO5[22] — General purpose digital input/output pin.                              |

|          |        |                          |          |         |         |     | 0           | <b>CTOUT_7</b> — SCT output 7. Match output 3 of timer 1. |                                                                                    |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

| PB_3     |        | A13                      | -        | 178     | -       | [2] | N;          | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     | PU          | I/O                                                       | <b>USB1_ULPI_D6</b> — ULPI link bidirectional data line 6.                         |

|          |        |                          |          |         |         |     |             | 0                                                         | LCD_VD20 — LCD data.                                                               |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | I/O                                                       | GPIO5[23] — General purpose digital input/output pin.                              |

|          |        |                          |          |         |         |     |             | 0                                                         | CTOUT_8 — SCT output 8. Match output 0 of timer 2.                                 |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

| PB_4     |        | B11                      | -        | 180     | -       | [2] | N;          | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     | PU          | I/O                                                       | USB1_ULPI_D5 — ULPI link bidirectional data line 5.                                |

|          |        |                          |          |         |         |     |             | 0                                                         | LCD_VD15 — LCD data.                                                               |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | I/O                                                       | GPIO5[24] — General purpose digital input/output pin.                              |

|          |        |                          |          |         |         |     |             | I                                                         | CTIN_5 — SCT input 5. Capture input 2 of timer 2.                                  |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

|          |        |                          |          |         |         |     |             | -                                                         | R — Function reserved.                                                             |

Table 3.

Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |            | Reset state<br>[1] | Type | Description                                                                                                                                                      |

|----------|---------|----------|---------|---------|------------|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |         | Ë        |         | Ľ       | [2]        |                    | Ł    | P. Evention accorded                                                                                                                                             |

| PB_5     | A12     | -        | 181     | -       | <u>[2]</u> | N;<br>PU           | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | I/O  | USB1_ULPI_D4 — ULPI link bidirectional data line 4.                                                                                                              |

|          |         |          |         |         |            |                    | 0    | LCD_VD14 — LCD data.                                                                                                                                             |

|          |         |          |         |         |            |                    | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | I/O  | <b>GPI05[25]</b> — General purpose digital input/output pin.                                                                                                     |

|          |         |          |         |         |            |                    |      | CTIN_7 — SCT input 7.                                                                                                                                            |

|          |         |          |         |         |            |                    | 0    | LCD_PWR — LCD panel power enable.                                                                                                                                |

|          |         |          |         |         |            |                    | -    | R — Function reserved.                                                                                                                                           |

| PB_6     | A6      | -        | -       | -       | [5]        | N;<br>PU           | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            | PU                 | I/O  | <b>USB1_ULPI_D3</b> — ULPI link bidirectional data line 3.                                                                                                       |

|          |         |          |         |         |            |                    | 0    | LCD_VD13 — LCD data.                                                                                                                                             |

|          |         |          |         |         |            |                    | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | I/O  | GPIO5[26] — General purpose digital input/output pin.                                                                                                            |

|          |         |          |         |         |            |                    | I    | CTIN_6 — SCT input 6. Capture input 1 of timer 3.                                                                                                                |

|          |         |          |         |         |            |                    | 0    | LCD_VD19 — LCD data.                                                                                                                                             |

|          |         |          |         |         |            |                    | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | AI   | <b>ADC0_6</b> — ADC0 and ADC1, input channel 6. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.           |

| PC_0     | D4      | -        | 7       | -       | [5]        | N;                 | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            | PU                 | I    | <b>USB1_ULPI_CLK</b> — ULPI link CLK signal. 60 MHz clock generated by the PHY.                                                                                  |

|          |         |          |         |         |            |                    | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | I/O  | ENET_RX_CLK — Ethernet Receive Clock (MII interface).                                                                                                            |

|          |         |          |         |         |            |                    | 0    | LCD_DCLK — LCD panel clock.                                                                                                                                      |

|          |         |          |         |         |            |                    | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | I/O  | SD_CLK — SD/MMC card clock.                                                                                                                                      |

|          |         |          |         |         |            |                    | AI   | <b>ADC1_1</b> — ADC1 and ADC0, input channel 1. Configure the pin as input (USB_ULPI_CLK) and use the ADC function select register in the SCU to select the ADC. |

| PC_1     | E4      | -        | 9       | -       | [2]        | N;                 | I/O  | USB1_ULPI_D7 — ULPI link bidirectional data line 7.                                                                                                              |

|          |         |          |         |         |            | PU                 | -    | R — Function reserved.                                                                                                                                           |

|          |         |          |         |         |            |                    | I    | <b>U1_RI</b> — Ring Indicator input for UART 1.                                                                                                                  |

|          |         |          |         |         |            |                    | 0    | ENET_MDC — Ethernet MIIM clock.                                                                                                                                  |

|          |         |          |         |         |            |                    | I/O  | <b>GPIO6[0]</b> — General purpose digital input/output pin.                                                                                                      |

|          |         |          |         |         |            |                    | -    | <b>R</b> — Function reserved.                                                                                                                                    |

|          |         |          |         |         |            |                    | 1    | T3_CAP0 — Capture input 0 of timer 3.                                                                                                                            |

|          |         |          |         |         |            |                    | O    | SD_VOLT0 — SD/MMC bus voltage select output 0.                                                                                                                   |

|          |         |          |         |         |            |                    | Ŭ    |                                                                                                                                                                  |

#### Table 3. Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name              | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |             | Reset state<br>[1] | Type | Description                                                                                                                                                                                                                                                                       |

|-----------------------|---------|----------|---------|---------|-------------|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAKEUP0               | A9      | A4       | 187     | 130     | [11]        | I; IA              | 1    | External wake-up input; can raise an interrupt and can cause wake-up from any of the low power modes. A pulse with a duration of at least 45 ns wakes up the part.                                                                                                                |

|                       |         |          |         |         |             |                    |      | Input 0 of the event monitor.No internal pull-up is enabled when this pin is configured as input.                                                                                                                                                                                 |

| WAKEUP1               | A10     | -        | -       | -       | [11]        | I; IA              | I    | External wake-up input; can raise an interrupt and can cause<br>wake-up from any of the low power modes. A pulse with a<br>duration of at least 45 ns wakes up the part.<br>Input 1 of the event monitor. No internal pull-up is enabled<br>when this pin is configured as input. |

| WAKEUP2               | C9      | -        | -       | -       | [11]        | I; IA              | 1    | External wake-up input; can raise an interrupt and can cause<br>wake-up from any of the low power modes. A pulse with a<br>duration of at least 45 ns wakes up the part.<br>Input 2 of the event monitor. This pin does not have an<br>internal pull-up.                          |

| WAKEUP3               | D8      | -        | -       | -       | <u>[11]</u> | I; IA              | I    | External wake-up input; can raise an interrupt and can cause<br>wake-up from any of the low power modes. A pulse with a<br>duration of at least 45 ns wakes up the part. This pin does<br>not have an internal pull-up.                                                           |

| ADC pins              |         |          |         |         |             |                    |      |                                                                                                                                                                                                                                                                                   |

| ADC0_0/<br>ADC1_0/DAC | E3      | A2       | 8       | 6       | [8]         | I; IA              | I    | ADC input channel 0. Shared between 10-bit ADC0/1 and DAC.                                                                                                                                                                                                                        |

| ADC0_1/<br>ADC1_1     | C3      | A1       | 4       | 2       | <u>[8]</u>  | I; IA              | I    | ADC input channel 1. Shared between 10-bit ADC0/1.                                                                                                                                                                                                                                |

| ADC0_2/<br>ADC1_2     | A4      | B3       | 206     | 143     | [8]         | I; IA              | I    | ADC input channel 2. Shared between 10-bit ADC0/1.                                                                                                                                                                                                                                |

| ADC0_3/<br>ADC1_3     | B5      | A3       | 200     | 139     | <u>[8]</u>  | I; IA              | I    | ADC input channel 3. Shared between 10-bit ADC0/1.                                                                                                                                                                                                                                |

| ADC0_4/<br>ADC1_4     | C6      | -        | 199     | 138     | [8]         | I; IA              | I    | ADC input channel 4. Shared between 10-bit ADC0/1.                                                                                                                                                                                                                                |

| ADC0_5/<br>ADC1_5     | B3      | -        | 208     | 144     | [8]         | I; IA              | I    | ADC input channel 5. Shared between 10-bit ADC0/1.                                                                                                                                                                                                                                |

| ADC0_6/<br>ADC1_6     | A5      | -        | 204     | 142     | <u>[8]</u>  | I; IA              | I    | ADC input channel 6. Shared between 10-bit ADC0/1.                                                                                                                                                                                                                                |

| ADC0_7/<br>ADC1_7     | C5      | -        | 197     | 136     | [8]         | I; IA              | I    | ADC input channel 7. Shared between 10-bit ADC0/1.                                                                                                                                                                                                                                |

| RTC                   |         |          |         |         |             |                    |      |                                                                                                                                                                                                                                                                                   |

| RTC_ALARM             | A11     | C3       | 186     | 129     | [11]        | -                  | 0    | RTC controlled output.                                                                                                                                                                                                                                                            |

| RTCX1                 | A8      | A5       | 182     | 125     | [8]         | -                  | I    | Input to the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                                                                                                       |

| RTCX2                 | B8      | B5       | 183     | 126     | <u>[8]</u>  | -                  | 0    | Output from the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                                                                                                    |

| SAMPLE                | B9      | -        | -       | -       | [11]        | 0                  | 0    | Event monitor sample output.                                                                                                                                                                                                                                                      |

| Crystal oscillat      | or pins | 6        |         |         | .11         |                    |      |                                                                                                                                                                                                                                                                                   |

Table 3.

Pin description ...continued

32-bit ARM Cortex-M4/M0 microcontroller

## 7. Functional description

### 7.1 Architectural overview

The ARM Cortex-M4 includes three AHB-Lite buses: the system bus, the I-CODE bus, and the D-code bus. The I-CODE and D-code core buses allow for concurrent code and data accesses from different slave ports.

The LPC435x/3x/2x/1x use a multi-layer AHB matrix to connect the ARM Cortex-M4 buses and other bus masters to peripherals in a flexible manner that optimizes performance by allowing peripherals that are on different slaves ports of the matrix to be accessed simultaneously by different bus masters.

An ARM Cortex-M0 co-processor is included in the LPC435x/3x/2x/1x, capable of off-loading the main ARM Cortex-M4 application processor. Most peripheral interrupts are connected to both processors. The processors communicate with each other via an interprocessor communication protocol.

## 7.2 ARM Cortex-M4 processor

The ARM Cortex-M4 CPU incorporates a 3-stage pipeline, uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals, and includes an internal prefetch unit that supports speculative branching. The ARM Cortex-M4 supports single-cycle digital signal processing and SIMD instructions. A hardware floating-point processor is integrated in the core. The processor includes an NVIC with up to 53 interrupts.

## 7.3 ARM Cortex-M0 co-processor

The ARM Cortex-M0 is a general purpose, 32-bit microprocessor, which offers high performance and very low power consumption. The ARM Cortex-M0 co-processor uses a 3-stage pipeline von Neumann architecture and a small but powerful instruction set providing high-end processing hardware. In LPC43xx, the Cortex-M0 coprocessor hardware multiply is implemented as a 32-cycle iterative multiplier. The co-processor incorporates an NVIC with 32 interrupts.

## 7.4 Interprocessor communication

The ARM Cortex-M4 and ARM Cortex-M0 interprocessor communication is based on using shared SRAM as mailbox and one processor raising an interrupt on the other processor's NVIC, for example after it has delivered a new message in the mailbox. The receiving processor can reply by raising an interrupt on the sending processor's NVIC to acknowledge the message.

### 32-bit ARM Cortex-M4/M0 microcontroller

| Boot mode | Pins |      |      |      | Description                                                                                                                                                                                  |

|-----------|------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | P2_9 | P2_8 | P1_2 | P1_1 |                                                                                                                                                                                              |

| USB1      | LOW  | HIGH | HIGH | LOW  | Boot from USB1.                                                                                                                                                                              |

| SPI (SSP) | LOW  | HIGH | HIGH | HIGH | Boot from SPI flash connected to the SSP0<br>interface on P3_3 (function SSP0_SCK), P3_6<br>(function SSP0_SSEL), P3_7 (function<br>SSP0_MISO), and P3_8 (function SSP0_MOSI) <sup>[1]</sup> |

| USART3    | HIGH | LOW  | LOW  | LOW  | Enter ISP mode using USART3 pins P2_3 and P2_4.                                                                                                                                              |

#### Table 5. Boot mode when OPT BOOT\_SRC bits are zero

[1] The boot loader programs the appropriate pin function at reset to boot using either SSP0 or SPIFI. **Remark:** Pin functions for SPIFI and SSP0 boot are different.

## 7.14 Memory mapping

The memory map shown in Figure 7 and Figure 8 is global to both the Cortex-M4 and the Cortex-M0 processors and all SRAM, flash, and EEPROM memory is shared between both processors. Each processor uses its own ARM private bus memory map for the NVIC and other system functions.

#### 32-bit ARM Cortex-M4/M0 microcontroller

• Each slice has a 32-bit pattern match filter.

### 7.18 AHB peripherals

### 7.18.1 General Purpose DMA

The DMA controller allows peripheral-to memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory transactions. Each DMA stream provides unidirectional serial DMA transfers for a single source and destination. For example, a bidirectional port requires one stream for transmit and one for receives. The source and destination areas can each be either a memory region or a peripheral for master 1, but only memory for master 0.

#### 7.18.1.1 Features

- Eight DMA channels. Each channel can support a unidirectional transfer.

- 16 DMA request lines.

- Single DMA and burst DMA request signals. Each peripheral connected to the DMA Controller can assert either a burst DMA request or a single DMA request. The DMA burst size is set by programming the DMA Controller.

- Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and peripheral-to-peripheral transfers are supported.

- Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

- Hardware DMA channel priority.

- AHB slave DMA programming interface. The DMA Controller is programmed by writing to the DMA control registers over the AHB slave interface.

- Two AHB bus masters for transferring data. These interfaces transfer data when a DMA request goes active. Master 1 can access memories and peripherals, master 0 can access memories only.

- 32-bit AHB master bus width.

- Incrementing or non-incrementing addressing for source and destination.

- Programmable DMA burst size. The DMA burst size can be programmed to more efficiently transfer data.

- Internal four-word FIFO per channel.

- Supports 8, 16, and 32-bit wide transactions.

- Big-endian and little-endian support. The DMA Controller defaults to little-endian mode on reset.

- An interrupt to the processor can be generated on a DMA completion or when a DMA error has occurred.

- Raw interrupt status. The DMA error and DMA count raw interrupt status can be read prior to masking.

## 7.18.2 SPI Flash Interface (SPIFI)

The SPI Flash Interface allows low-cost serial flash memories to be connected to the ARM Cortex-M4 processor with little performance penalty compared to parallel flash devices with higher pin count.

#### 32-bit ARM Cortex-M4/M0 microcontroller

After a few commands configure the interface at startup, the entire flash content is accessible as normal memory using byte, halfword, and word accesses by the processor and/or DMA channels. Simple sequences of commands handle erasing and programming.

Many serial flash devices use a half-duplex command-driven SPI protocol for device setup and initialization and then move to a half-duplex, command-driven 4-bit protocol for normal operation. Different serial flash vendors and devices accept or require different commands and command formats. SPIFI provides sufficient flexibility to be compatible with common flash devices and includes extensions to help insure compatibility with future devices.

#### 7.18.2.1 Features

- Interfaces to serial flash memory in the main memory map.

- Supports classic and 4-bit bidirectional serial protocols.

- Half-duplex protocol compatible with various vendors and devices.

- Quad SPI Flash Interface (SPIFI) with 1-, 2-, or 4-bit data at rates of up to 52 MB per second.

- Supports DMA access.

### 7.18.3 SD/MMC card interface

The SD/MMC card interface supports the following modes to control:

- Secure Digital memory (SD version 3.0)

- Secure Digital I/O (SDIO version 2.0)

- Consumer Electronics Advanced Transport Architecture (CE-ATA version 1.1)

- MultiMedia Cards (MMC version 4.4)

### 7.18.4 External Memory Controller (EMC)

**Remark:** The EMC is available on all LPC435x/3x/2x/1x parts. The following memory bus widths are supported:

- LBGA256 packages: 32 bit

- TFBGA100 packages: 16 bit

- LQFP208 packages: 16 bit

- LQFP144 packages: 16 bit

The LPC435x/3x/2x/1x EMC is a Memory Controller peripheral offering support for asynchronous static memory devices such as RAM, ROM, and NOR flash. In addition, it can be used as an interface with off-chip memory-mapped devices and peripherals.

| Function | LBGA256      | TFBGA100    | LQFP208      | LQFP144      |

|----------|--------------|-------------|--------------|--------------|

| A        | EMC_A[23:0]  | EMC_A[13:0] | EMC_A[23:0]  | EMC_A[15:0]  |

| D        | EMC_D[31:0]  | EMC_D[7:0]  | EMC_D[15:0]  | EMC_D[15:0]  |

| BLS      | EMC_BLS[3:0] | EMC_BLS0    | EMC_BLS[1:0] | EMC_BLS[1:0] |

| CS       | EMC_CS[3:0]  | EMC_CS0     | EMC_CS[3:0]  | EMC_CS[1:0]  |

Table 6. EMC pinout for different packages

### 32-bit ARM Cortex-M4/M0 microcontroller

• Alarm interrupt can be generated for a specific date/time.

#### 7.22.1.2 Event monitor/recorder

The event monitor/recorder allows recording and creating a time stamp of events related to the WAKEUP pins. Sensors report changes to the state of the WAKEUP pins, and the event monitor/recorder stores records of such events. The event recorder can be powered by the backup battery.

The event monitor/recorder can monitor the integrity of the device and record any tampering events.

#### Features

- Supports three digital event inputs in the VBAT power domain.

- An event is defined as a level change at the digital event inputs.

- For each event channel, two timestamps mark the first and the last occurrence of an event. Each channel also has a dedicated counter tracking the total number of events. Timestamp values are taken from the RTC.

- Runs in VBAT power domain, independent of system power supply. The event/recorder/monitor can therefore operate in Deep power-down mode.

- Low power consumption.

- Interrupt available if system is running.

- A qualified event can be used as a wake-up trigger.

- State of event interrupts accessible by software through GPIO.

#### 7.22.2 Alarm timer

The alarm timer is a 16-bit timer and counts down at 1 kHz from a preset value generating alarms in intervals of up to 1 min. The counter triggers a status bit when it reaches 0x00 and asserts an interrupt if enabled.

The alarm timer is part of the RTC power domain and can be battery powered.

### 7.23 System control

#### 7.23.1 Configuration registers (CREG)

The following settings are controlled in the configuration register block:

- BOD trip settings

- Oscillator output

- DMA-to-peripheral muxing

- Ethernet mode

- Memory mapping

- Timer/USART inputs

- Enabling the USB controllers

In addition, the CREG block contains the part identification and part configuration information.

### 32-bit ARM Cortex-M4/M0 microcontroller

## 9. Thermal characteristics

The average chip junction temperature,  $T_{j}\,(^{\circ}C),$  can be calculated using the following equation:

$$T_j = T_{amb} + (P_D \times R_{th(j-a)}) \tag{1}$$

- T<sub>amb</sub> = ambient temperature (°C),

- R<sub>th(j-a)</sub> = the package junction-to-ambient thermal resistance (°C/W)

- P<sub>D</sub> = sum of internal and I/O power dissipation

The internal power dissipation is the product of  $I_{DD}$  and  $V_{DD}$ . The I/O power dissipation of the I/O pins is often small and many times can be negligible. However it can be significant in some applications.

#### Table 8. Thermal characteristics

| Symbol              | Parameter        | Conditions | Min | Тур | Мах | Unit |

|---------------------|------------------|------------|-----|-----|-----|------|

| T <sub>j(max)</sub> | maximum junction | -          | -   | -   | 125 | °C   |

|                     | temperature      |            |     |     |     |      |

#### Table 9. Thermal resistance (LQFP packages)

| Symbol               | Parameter                                   | Conditions                                     | Thermal resista<br>±15 % | ance in °C/W |

|----------------------|---------------------------------------------|------------------------------------------------|--------------------------|--------------|

|                      |                                             |                                                | LQFP144                  | LQFP208      |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | JEDEC (4.5 in $\times$ 4 in); still air        | 38                       | 31           |

|                      |                                             | Single-layer (4.5 in $\times$ 3 in); still air | 50                       | 39           |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    | -                                              | 11                       | 10           |

#### Table 10. Thermal resistance value (BGA packages)

| Symbol               | Parameter                                   | Conditions                            | Thermal resistance in °C/W ±15 % |          |  |  |

|----------------------|---------------------------------------------|---------------------------------------|----------------------------------|----------|--|--|

|                      |                                             |                                       | LBGA256                          | TFBGA100 |  |  |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | JEDEC (4.5 in × 4 in);<br>still air   | 29                               | 46       |  |  |

|                      |                                             | 8-layer (4.5 in × 3 in);<br>still air | 24                               | 37       |  |  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |                                       | 14                               | 11       |  |  |

32-bit ARM Cortex-M4/M0 microcontroller

## 10. Static characteristics

### Table 11. Static characteristics

$T_{amb} = -40$  °C to +105 °C, unless otherwise specified.

| Symbol                    | Parameter                        | Conditions                                                                                                     |            | Min | Typ <u>[1]</u> | Max | Unit |

|---------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|------------|-----|----------------|-----|------|

| Supply pins               |                                  |                                                                                                                |            |     |                |     |      |

| V <sub>DD(IO)</sub>       | input/output supply voltage      |                                                                                                                | [17]       | 2.4 | -              | 3.6 | V    |

| V <sub>DD(REG)(3V3)</sub> | regulator supply voltage (3.3 V) |                                                                                                                | [2]        | 2.4 | -              | 3.6 | V    |

| V <sub>DDA(3V3)</sub>     | analog supply voltage            | on pin VDDA                                                                                                    |            | 2.4 | -              | 3.6 | V    |

|                           | (3.3 V)                          | on pins<br>USB0_VDDA3V3_<br>DRIVER and<br>USB0_VDDA3V3                                                         |            | 3.0 | 3.3            | 3.6 | V    |

| V <sub>BAT</sub>          | battery supply voltage           |                                                                                                                | [2]        | 2.4 | -              | 3.6 | V    |

| V <sub>prog(pf)</sub>     | polyfuse programming voltage     | on pin VPP (for OTP)                                                                                           | [3]        | 2.7 | -              | 3.6 | V    |

| I <sub>prog(pf)</sub>     | polyfuse programming<br>current  | on pin VPP; OTP<br>programming time ≤<br>1.6 ms                                                                |            | -   | -              | 30  | mA   |

| IDD(REG)(3V3)             | regulator supply current (3.3 V) | Active mode; ARM<br>Cortex-M0 core in reset;<br>code                                                           |            |     |                |     |      |

|                           |                                  | while(1){}                                                                                                     |            |     |                |     |      |

|                           |                                  | executed from RAM; all peripherals disabled; PLL1 enabled                                                      |            |     |                |     |      |

|                           |                                  | CCLK = 12 MHz                                                                                                  | [4]        | -   | 10             | -   | mA   |

|                           |                                  | CCLK = 60 MHz                                                                                                  | [4]        |     | 28             | -   | mA   |

|                           |                                  | CCLK = 120 MHz                                                                                                 | [4]        | -   | 51             | -   | mA   |

|                           |                                  | CCLK = 180 MHz                                                                                                 | [4]        | -   | 74             | -   | mA   |

|                           |                                  | CCLK = 204 MHz                                                                                                 | [4]        | -   | 83             | -   | mA   |

| I <sub>DD(REG)(3V3)</sub> | regulator supply current (3.3 V) | after WFE/WFI instruction<br>executed from RAM; all<br>peripherals disabled;<br>ARM Cortex-M0 core in<br>reset |            |     |                |     |      |

|                           |                                  | sleep mode                                                                                                     | [4][5]     | -   | 8.8            | -   | mA   |

|                           |                                  | deep-sleep mode                                                                                                | [4]        | -   | 145            | -   | μA   |

|                           |                                  | power-down mode                                                                                                | [4]        | -   | 23             | -   | μA   |

|                           |                                  | deep power-down<br>mode                                                                                        | [4][6]     | -   | 0.05           | -   | μA   |

|                           |                                  | deep power-down<br>mode; VBAT floating                                                                         | <u>[4]</u> | -   | 3.0            | -   | μA   |

| I <sub>BAT</sub>          | battery supply current           | V <sub>BAT</sub> = 3.0 V;<br>V <sub>DD(REG)(3V3)</sub> = 3.3 V                                                 | <u>[7]</u> | -   |                | 0.1 | nA   |

### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol           | Parameter                                  | Conditions                                                                                     | Min                  | Typ[1]                       | Max | Unit                    |        |

|------------------|--------------------------------------------|------------------------------------------------------------------------------------------------|----------------------|------------------------------|-----|-------------------------|--------|

| Vo               | output voltage                             | output active                                                                                  |                      | 0                            | -   | V <sub>DD(IO)</sub>     | V      |

| V <sub>IH</sub>  | HIGH-level input voltage                   |                                                                                                |                      | $0.7 \times V_{DD(IO)}$      | -   | 5.5                     | V      |

| V <sub>IL</sub>  | LOW-level input voltage                    |                                                                                                |                      | -0.5                         | -   | $0.3 \times V_{DD(IO)}$ | V      |

| V <sub>hys</sub> | hysteresis voltage                         |                                                                                                |                      | $0.1 \times V_{DD(IO)}$      | -   | -                       | V      |

| V <sub>OH</sub>  | HIGH-level output voltage                  | I <sub>OH</sub> = -6 mA                                                                        |                      | V <sub>DD(IO)</sub> -<br>0.4 | -   | -                       | V      |

| V <sub>OL</sub>  | LOW-level output voltage                   | I <sub>OL</sub> = 6 mA                                                                         |                      | -                            | -   | 0.4                     | V      |

| I <sub>OH</sub>  | HIGH-level output current                  | $V_{OH} = V_{DD(IO)} - 0.4 \text{ V}$                                                          |                      | -6                           | -   | -                       | mA     |

| I <sub>OL</sub>  | LOW-level output current                   | V <sub>OL</sub> = 0.4 V                                                                        |                      | 6                            | -   | -                       | mA     |

| I <sub>OHS</sub> | HIGH-level short-circuit<br>output current | drive HIGH; connected to ground                                                                | <u>[11]</u>          | -                            | -   | 86.5                    | mA     |

| I <sub>OLS</sub> | LOW-level short-circuit<br>output current  | drive LOW; connected to $V_{DD(IO)}$                                                           | <u>[11]</u>          | -                            | -   | 76.5                    | mA     |

| I <sub>pd</sub>  | pull-down current                          | V <sub>1</sub> = 5 V                                                                           | [13]<br>[14]<br>[15] | -                            | 93  | -                       | μA     |

| I <sub>pu</sub>  | pull-up current                            | V <sub>1</sub> = 0 V                                                                           | [13]<br>[14]<br>[15] | -                            | -62 | -                       | μA     |

|                  |                                            | $V_{DD(IO)} < V_I \le 5 V$                                                                     |                      | -                            | 10  | -                       | μA     |

| R <sub>s</sub>   | series resistance                          | on I/O pins with analog<br>function; analog function<br>enabled                                |                      |                              | 200 |                         | Ω      |

| I/O pins - hi    | gh drive strength                          |                                                                                                |                      |                              |     |                         |        |

| CI               | input capacitance                          |                                                                                                |                      | -                            | -   | 5.2                     | pF     |

| ILL              | LOW-level leakage current                  | V <sub>I</sub> = 0 V; on-chip pull-up<br>resistor disabled                                     |                      | -                            | 3   | -                       | nA     |

| I <sub>OZ</sub>  | OFF-state output<br>current                | $V_O = 0 V$ to $V_{DD(IO)}$ ;<br>on-chip pull-up/down<br>resistors disabled;<br>absolute value |                      | -                            | 3   | -                       | nA     |

| VI               | input voltage                              | pin configured to provide<br>a digital function;                                               |                      |                              |     |                         |        |

|                  |                                            | $V_{DD(IO)} \ge 2.4 \text{ V}$ $V_{DD(IO)} = 0 \text{ V}$                                      |                      | 0                            | -   | 5.5<br>3.6              | V<br>V |

| Vo               | output voltage                             | output active                                                                                  |                      | 0                            | -   | V <sub>DD(IO)</sub>     | V      |

| VIH              | HIGH-level input<br>voltage                |                                                                                                |                      | $0.7 \times V_{DD(IO)}$      | -   | 5.5                     | V      |

| V <sub>IL</sub>  | LOW-level input voltage                    |                                                                                                |                      | -0.5                         | -   | $0.3 \times V_{DD(IO)}$ | V      |

#### Table 11. Static characteristics ... continued T 10 °C to : 105 °C uplace otherwise and oifind

#### 32-bit ARM Cortex-M4/M0 microcontroller

- [2] Simulated using 10 cm of 50  $\Omega$  PCB trace with 5 pF receiver input. Rise and fall times measured between 80 % and 20 % of the full output signal level.

- [3] The slew rate is configured in the system control block in the SFSP registers using the EHS bit. See the LPC43xx user manual.

- [4]  $C_L = 20$  pF. Rise and fall times measured between 90 % and 10 % of the full input signal level.

- [5] The drive modes are configured in the system control block in the SFSP registers using the EHD bit. See the LPC43xx user manual.

## 11.9 I<sup>2</sup>C-bus

#### Table 24. Dynamic characteristic: I<sup>2</sup>C-bus pins

$T_{amb} = -40 \text{ °C to } +105 \text{ °C}; 2.4 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}.$ [1]

| Symbol              | Parameter                    |              | Conditions                                      | Min                       | Max | Unit |

|---------------------|------------------------------|--------------|-------------------------------------------------|---------------------------|-----|------|

| f <sub>SCL</sub>    | SCL clock frequency          |              | Standard-mode                                   | 0                         | 100 | kHz  |

|                     |                              |              | Fast-mode                                       | 0                         | 400 | kHz  |

|                     |                              |              | Fast-mode Plus                                  | 0                         | 1   | MHz  |

| t <sub>f</sub>      | fall time                    | [3][4][5][6] | of both SDA and<br>SCL signals<br>Standard-mode | -                         | 300 | ns   |

|                     |                              |              | Fast-mode                                       | 20 + 0.1 × C <sub>b</sub> | 300 | ns   |

|                     |                              |              | Fast-mode Plus                                  | -                         | 120 | ns   |

| t <sub>LOW</sub>    | LOW period of the SCL clock  |              | Standard-mode                                   | 4.7                       | -   | μs   |

|                     |                              |              | Fast-mode                                       | 1.3                       | -   | μs   |

|                     |                              |              | Fast-mode Plus                                  | 0.5                       | -   | μS   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock |              | Standard-mode                                   | 4.0                       | -   | μS   |

|                     |                              |              | Fast-mode                                       | 0.6                       | -   | μs   |

|                     |                              |              | Fast-mode Plus                                  | 0.26                      | -   | μs   |

| t <sub>HD;DAT</sub> | data hold time               | [2][3][7]    | Standard-mode                                   | 0                         | -   | μs   |

|                     |                              |              | Fast-mode                                       | 0                         | -   | μs   |

|                     |                              |              | Fast-mode Plus                                  | 0                         | -   | μs   |

| t <sub>SU;DAT</sub> | data set-up time             | [8][9]       | Standard-mode                                   | 250                       | -   | ns   |

|                     |                              |              | Fast-mode                                       | 100                       | -   | ns   |

|                     |                              |              | Fast-mode Plus                                  | 50                        | -   | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified. See the I<sup>2</sup>C-bus specification UM10204 for details.

[2] tHD;DAT is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

[3] A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>IH</sub>(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

[4] C<sub>b</sub> = total capacitance of one bus line in pF. If mixed with Hs-mode devices, faster fall times are allowed.

- [5] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [6] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [7] The maximum t<sub>HD;DAT</sub> could be 3.45 μs and 0.9 μs for Standard-mode and Fast-mode but must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time. This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [8] tSU;DAT is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

LPC435X 3X 2X 1X

© NXP Semiconductors N.V. 2016. All rights reserved.

### 32-bit ARM Cortex-M4/M0 microcontroller

#### Table 27. Dynamic characteristics: SSP pins in SPI mode

$T_{amb} = -40$  °C to +105 °C; 2.4 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V;  $C_L = 20$  pF; sampled at 10 % and 90 % of the signal level; EHS = 1 for all pins. Simulated values.

| Symbol               | Parameter                     | Conditions                                                  |     | Min                             | Тур                             | Max                | Unit |

|----------------------|-------------------------------|-------------------------------------------------------------|-----|---------------------------------|---------------------------------|--------------------|------|

| t <sub>d</sub>       | delay time                    | continuous transfer mode                                    |     | -                               | $0.5 	imes T_{cy(clk)}$         | -                  | ns   |

|                      |                               | SPI mode; CPOL = 0;<br>CPHA = 0                             |     |                                 |                                 |                    |      |

|                      |                               | SPI mode; CPOL = 0;<br>CPHA = 1                             |     | -                               | n/a                             | -                  | ns   |

|                      |                               | SPI mode; CPOL = 1;<br>CPHA = 0                             |     | -                               | $0.5 \times T_{\text{cy(clk)}}$ | -                  | ns   |

|                      |                               | SPI mode; CPOL = 1;<br>CPHA = 1                             |     | -                               | n/a                             | -                  | ns   |

|                      |                               | synchronous serial<br>frame mode                            |     | -                               | T <sub>cy(clk)</sub>            | -                  | ns   |

|                      |                               | microwire frame format                                      |     | -                               | n/a                             | -                  | ns   |

| SSP slav             | 'e                            |                                                             |     |                                 |                                 |                    |      |

| PCLK                 | Peripheral clock<br>frequency |                                                             |     | -                               | -                               | 204                | MHz  |