Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                         |

| Core Processor             | ARM® Cortex®-M4/M0                                                                                             |

| Core Size                  | 32-Bit Dual-Core                                                                                               |

| Speed                      | 204MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, QEI, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, Motor Control PWM, POR, PWM, WDT                           |

| Number of I/O              | 164                                                                                                            |

| Program Memory Size        | 512KB (512K x 8)                                                                                               |

| Program Memory Type        | FLASH                                                                                                          |

| EEPROM Size                | 16K × 8                                                                                                        |

| RAM Size                   | 136K x 8                                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                                    |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                           |

| Oscillator Type            | Internal                                                                                                       |

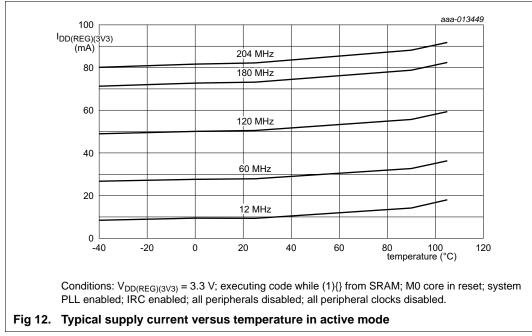

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                             |

| Mounting Type              | Surface Mount                                                                                                  |

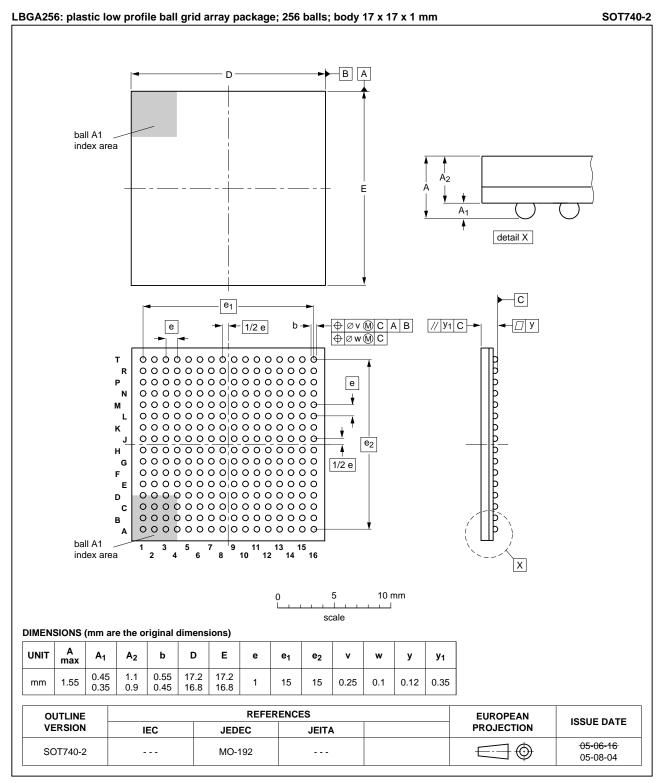

| Package / Case             | 256-LBGA                                                                                                       |

| Supplier Device Package    | 256-LBGA (17x17)                                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4353jet256-551                                      |

|                            |                                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

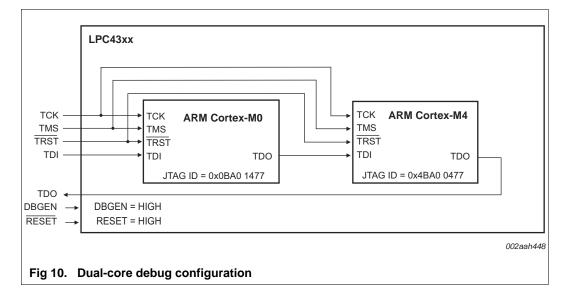

- Cortex-M0 Processor core

- ARM Cortex-M0 co-processor (version r0p0) capable of off-loading the main ARM Cortex-M4 application processor.

- ◆ Running at frequencies of up to 204 MHz.

- ♦ JTAG

- Built-in NVIC.

- On-chip memory

- ♦ Up to 1 MB on-chip dual bank flash memory with flash accelerator.

- ◆ 16 kB on-chip EEPROM data memory.

- ◆ 136 kB SRAM for code and data use.

- Multiple SRAM blocks with separate bus access. Two SRAM blocks can be powered down individually.

- ♦ 64 kB ROM containing boot code and on-chip software drivers.

- 64 bit+ 256 bit of One-Time Programmable (OTP) memory for general-purpose use.

- Configurable digital peripherals

- ◆ Serial GPIO (SGPIO) interface.

- ◆ State Configurable Timer (SCTimer/PWM) subsystem on AHB.

- Global Input Multiplexer Array (GIMA) allows to cross-connect multiple inputs and outputs to event driven peripherals like the timers, SCTimer/PWM, and ADC0/1.

- Serial interfaces

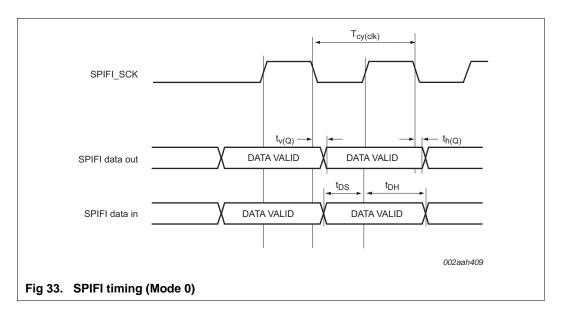

- ◆ Quad SPI Flash Interface (SPIFI) with four lanes and up to 52 MB per second.

- 10/100T Ethernet MAC with RMII and MII interfaces and DMA support for high throughput at low CPU load. Support for IEEE 1588 time stamping/advanced time stamping (IEEE 1588-2008 v2).

- One High-speed USB 2.0 Host/Device/OTG interface with DMA support and on-chip high-speed PHY.

- One High-speed USB 2.0 Host/Device interface with DMA support, on-chip full-speed PHY and ULPI interface to external high-speed PHY.

- ♦ USB interface electrical test software included in ROM USB stack.

- One 550 UART with DMA support and full modem interface.

- Three 550 USARTs with DMA and synchronous mode support and a smart card interface conforming to ISO7816 specification. One USART with IrDA interface.

- Up to two C\_CAN 2.0B controllers with one channel each.

- Two SSP controllers with FIFO and multi-protocol support. Both SSPs with DMA support.

- One SPI controller.

- One Fast-mode Plus I<sup>2</sup>C-bus interface with monitor mode and with open-drain I/O pins conforming to the full I<sup>2</sup>C-bus specification. Supports data rates of up to 1 Mbit/s.

- ♦ One standard I<sup>2</sup>C-bus interface with monitor mode and with standard I/O pins.

- ◆ Two I<sup>2</sup>S interfaces, each with DMA support and with one input and one output.

- Digital peripherals

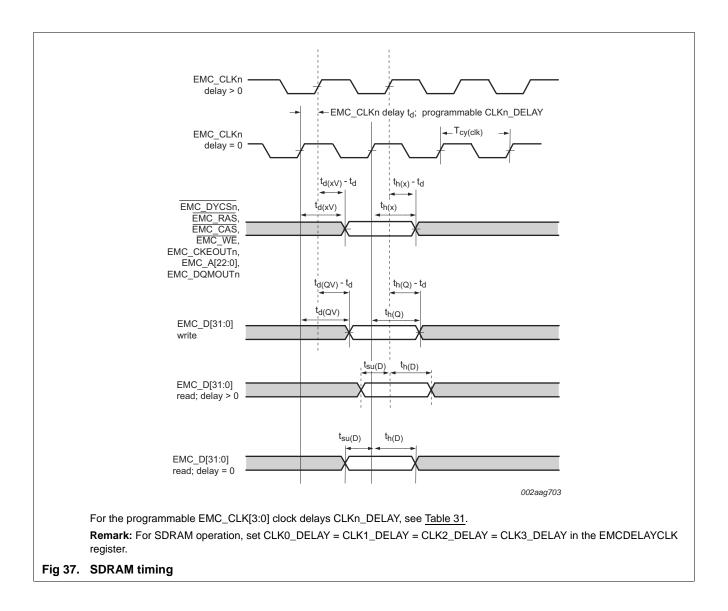

- External Memory Controller (EMC) supporting external SRAM, ROM, NOR flash, and SDRAM devices.

- ♦ LCD controller with DMA support and a programmable display resolution of up to 1024 H × 768 V. Supports monochrome and color STN panels and TFT color panels; supports 1/2/4/8 bpp Color Look-Up Table (CLUT) and 16/24-bit direct pixel mapping. Available on parts LPC4357/53 only.

- ◆ Secure Digital Input Output (SD/MMC) card interface.

- Eight-channel General-Purpose DMA controller can access all memories on the AHB and all DMA-capable AHB slaves.

- Up to 164 General-Purpose Input/Output (GPIO) pins with configurable pull-up/pull-down resistors.

- GPIO registers are located on the AHB for fast access. GPIO ports have DMA support.

- Up to eight GPIO pins can be selected from all GPIO pins as edge and level sensitive interrupt sources.

- Two GPIO group interrupt modules enable an interrupt based on a programmable pattern of input states of a group of GPIO pins.

- ◆ Four general-purpose timer/counters with capture and match capabilities.

- One motor control Pulse Width Modulator (PWM) for three-phase motor control.

- One Quadrature Encoder Interface (QEI).

- Repetitive Interrupt timer (RI timer).

- Windowed watchdog timer (WWDT).

- Ultra-low power Real-Time Clock (RTC) on separate power domain with 256 bytes of battery powered backup registers.

- ♦ Alarm timer; can be battery powered.

- Analog peripherals

- One 10-bit DAC with DMA support and a data conversion rate of 400 kSamples/s.

- Two 10-bit ADCs with DMA support and a data conversion rate of 400 kSamples/s. Up to eight input channels per ADC.

- Unique ID for each device.

- Clock generation unit

- Crystal oscillator with an operating range of 1 MHz to 25 MHz.

- ◆ 12 MHz internal RC oscillator trimmed to 3 % accuracy over temperature and voltage (1.5 % accuracy for T<sub>amb</sub> = 0 °C to 85 °C).

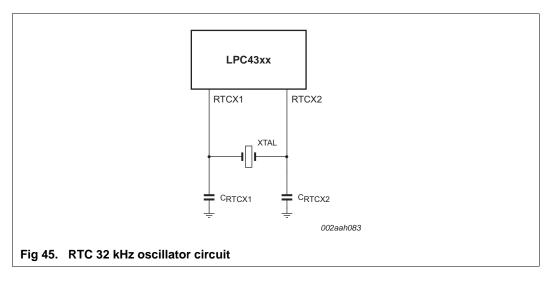

- ◆ Ultra-low power Real-Time Clock (RTC) crystal oscillator.

- Three PLLs allow CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. The second PLL can be used with the High-speed USB, the third PLL can be used as audio PLL.

- Clock output.

- Power

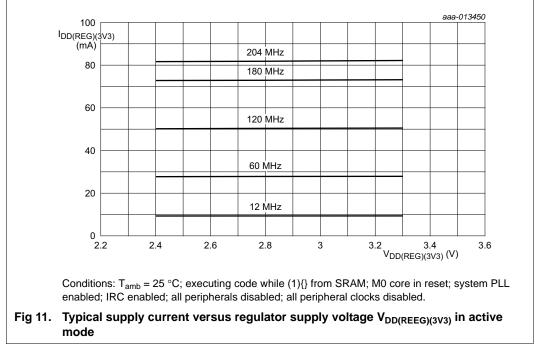

- Single 3.3 V (2.4 V to 3.6 V) power supply with on-chip DC-to-DC converter for the core supply and the RTC power domain.

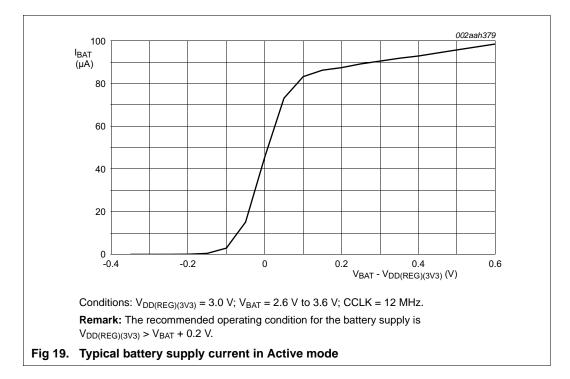

- RTC power domain can be powered separately by a 3 V battery supply.

- Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

- Processor wake-up from Sleep mode via wake-up interrupts from various peripherals.

# 32-bit ARM Cortex-M4/M0 microcontroller

| No.         No. <th>Table 3. Pi</th> <th colspan="6">in description continued</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 3. Pi | in description continued |          |         |         |     |             |      |                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------|----------|---------|---------|-----|-------------|------|-------------------------------------------------------------|

| P1_8       R7       H5       71       51       [2]       N;       [V]       GPI01[1] — General purpose digital input/output pin.         0       U1_DTR — Data Terminal Ready output for UART1.       O       CTOUT.12 — SCT output 12. Match output 3 of timer 3.         10       EMC_D1 — External memory data line 1.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function res                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin name    | LBGA256                  | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                 |

| P1_9       T7       J5       73       52       [2]       N;<br>P1_9       VO       EMC_D1 - External memory data line 1.<br>- R - Function reserved.<br>- R -                                                                                                                                                                                                                                                                                                                                                                                                                   | P1_8        | R7                       | H5       | 71      | 51      | [2] | N;          | I/O  | GPIO1[1] — General purpose digital input/output pin.        |

| P1_9       T7       J5       73       52       I2       N;<br>H       V0       EMC_D1 — External memory data line 1.       -       R - Function reserved.         P1_9       T7       J5       73       52       I2       N;<br>H       V0       GPI01[2] — General purpose digital input/output pin.       0       U1_RTS — Request to Send output for UART1.       0       U1_RTS — Request to Send output for UART1.       0       U1_RTS — Request to Send output for UART1.       0       CTOUT_11 — SCT output 11. Match output 3 of timer 2.       V/0       EMC_D2 — External memory data line 2.       -       R — Function reserved.       -       R — Function reserved. <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>PU</td> <td>0</td> <td>U1_DTR — Data Terminal Ready output for UART1.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                          |          |         |         |     | PU          | 0    | U1_DTR — Data Terminal Ready output for UART1.              |

| P1_9       T7       J5       73       52       Z       N;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                          |          |         |         |     |             | 0    |                                                             |

| P1_9       T7       J5       73       52       Z       N:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                          |          |         |         |     |             | I/O  | EMC_D1 — External memory data line 1.                       |

| P1_9       T7       J5       73       52       P1       N;<br>PU       VO       GPI01[2] General purpose digital input/output pin.         0       U1_RTS Request to Send output for UART1.       0       U1_RTS Request to Send output for UART1.         0       CTOUT_11 SCT output 11. Match output 3 of timer 2.       N;<br>VO       EMC_02 External memory data line 2.         -       R Function reserved.       R Function reserved.         -       R Function reserved.         VO       SD_DAT0 SD/MMC data bus line 0.         VO       EMC_03 External memory data line 3.         -       R Function reserved.         VO       SD_DAT1 SD/MMC data bus line 1.         VO       SD_DAT1 SD/MMC data bus line 1.         VO       SD_DAT1 SD/MMC data bus line 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| P1_9T7J5T352Z1N;<br>PUV0GPI01[2] General purpose digital input/output pin.0U1_RTS Request to Send output for UART1.0U1_RTS Request to Send output for UART1.0CTOUT_11 SCT output 11. Match output 3 of timer 2.VOEMC_D2 External memory data line 2R Function reservedR Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| P1_9       T7       J5       T3       52       I2       N;<br>PU       V/0       GPI01[2] - General purpose digital input/output pin.         0       U1_RTS - Request to Send output for UART1.       O       CTOUT_11 - SCT output 11. Match output 3 of timer 2.         V/0       EMC_D2 - External memory data line 2.       R - Function reserved.       R - Function reserved.         -       R - Function reserved.       R - Function reserved.         -       R - Function reserved.       R - Function reserved.         P1_10       R8       H6       75       53       I2       N;<br>PV       V/0       GPI01[3] - General purpose digital input/output pin.         P1_10       R8       H6       75       53       I2       N;<br>PV       V/0       GPI01[3] - General purpose digital input/output pin.         P1_11       P1       T9       J7       77       55       I2       N;<br>PV       V/0       GPI01[4] - General purpose digital input/output pin.         P1_11       T9       J7       T7       55       I2       N;<br>PV       V/0       GPI01[4] - General purpose digital input/output pin.         P1_11       T9       J7       T7       55       I2       N;<br>PV       V/0       GPI01[4] - General purpose digital input/output pin.       IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| PUOU1_RTS - Request to Send output for UART1.<br>OCTOUT_11 - SCT output 11. Match output 3 of timer 2.<br>I/OEMC_D2 - External memory data line 2.<br>-<br>R - Function reserved.<br>-<br>R - Functio                                                                                                                                                 |             |                          |          |         |         |     |             | 0    | <b>SD_VOLT0</b> — SD/MMC bus voltage select output 0.       |

| P1_10       R8       H6       75       53       Image: Signal Amount of the served of the serv                                              | P1_9        | Τ7                       | J5       | 73      | 52      | [2] |             | I/O  | GPIO1[2] — General purpose digital input/output pin.        |

| P1_10R8H67553[2]N;<br>P1_10I/OEMC_D2 — External memory data line 2.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.<br>I/OR — Function reserved.<br>-<br>R — Function reserved.<br>I/OR — Function reserved.<br>I/OP1_10R8H67553[2]N;<br>PUI/OGPI01[3] — General purpose digital input/output pin.<br>I<br>I U1_RI — Ring Indicator input for UART1.<br>OCTOUT_14 — SCT output 14. Match output 2 of timer 3.<br>I/OI/OEMC_D3 — External memory data line 3.<br>-<br>R — Function reserved.<br>-<br>R — Function reserve                                                                                                                                                                                                                                                                                                                                                                                              |             |                          |          |         |         |     | PU          | 0    | <b>U1_RTS</b> — Request to Send output for UART1.           |

| P1_10       R8       H6       75       53       Image: Constraint of the served                                               |             |                          |          |         |         |     |             | 0    | CTOUT_11 — SCT output 11. Match output 3 of timer 2.        |

| P1_10       R       HG       V       R       Function reserved.         P1_10       R8       H6       75       53       S3       V       GPI01[3] - General purpose digital input/output pin.         P1_10       R8       H6       75       53       S3       V       GPI01[3] - General purpose digital input/output pin.         P1_10       R8       H6       75       53       V       GPI01[3] - General purpose digital input/output pin.         VI       GPI01[3] - General purpose digital input/output pin.       V       GCTOUT_14 - SCT output 14. Match output 2 of timer 3.         V/O       EMC_D3 - External memory data line 3.       R - Function reserved.       R - Function reserved.         -       R - Function reserved.       R - Function reserved.       R - Function reserved.         -       R - Function reserved.       R - Function reserved.       R - Function reserved.         P1_11       T9       J7       77       55       V       N;       V       GPI01[4] - General purpose digital input/output pin.         P1_11       T9       J7       77       55       V       N;       V       GPI01[4] - General purpose digital input/output pin.         I       U1_CTS - Clear to Send input for UART1.       O       CTOUT_15 - SCT output 15. Match ou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                          |          |         |         |     |             | I/O  | EMC_D2 — External memory data line 2.                       |

| P1_10R8H67553[2]N;<br>FUV(OGPI01[3] — General purpose digital input/output pin.P1_10R8H67553[2]N;<br>FUV(OGPI01[3] — General purpose digital input/output pin.P1_10R8H67553[2]N;<br>FUV(OGPI01[3] — General purpose digital input/output pin.P1_10R8H67553[2]N;<br>FUV(OGPI01[4] — Ring Indicator input for UART1.<br>OOCTOUT_14 — SCT output 14. Match output 2 of timer 3.<br>I/OEMC_D3 — External memory data line 3.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.P1_11T9J77755[2]N;<br>PUV(OGPI01[4] — General purpose digital input/output pin.<br>I<br>U1_CTS — Clear to Send input for UART1.<br>OP1_11T9J77755[2]N;<br>PUV(OGPI01[4] — General purpose digital input/output pin.<br>I<br>U1_CTS — Clear to Send input for UART1.<br>OP1_11T9J77755[2]N;<br>PUV(OGPI01[4] — General purpose digital input/output pin.<br>I<br>U1_CTS — Clear to Send input for UART1.<br>OOCTOUT_15 — SCT output 15. Match output 3 of timer 3.<br>I/OI/OEMC_D4 — External memory data line 4.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| P1_10R8H67553I2N;<br>PUI/O <b>SD_DAT0</b> — SD/MMC data bus line 0.P1_10R8H67553I2N;<br>PUIU1_RI — Ring Indicator input for UART1.<br>OCTOUT_14 — SCT output 14. Match output 2 of timer 3.<br>I/OI/OEMC_D3 — External memory data line 3.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.P1_11T9J77755I2N;<br>PUI/OGPI01[4] — General purpose digital input/output pin.<br>I<br>U1_CTS — Clear to Send input for UART1.<br>OP1_11T9J77755I2N;<br>PUI/OGPI01[4] — General purpose digital input/output pin.<br>I<br>U1_CTS — Clear to Send input for UART1.<br>OCTOUT_15 — SCT output 15. Match output 3 of timer 3.<br>I/OI/OEMC_D4 — External memory data line 4.<br>-<br>R — Function reserved.<br>-<br>R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| P1_10R8H67553I2N;<br>PUI/OGPI01[3] — General purpose digital input/output pin.IU1_RI — Ring Indicator input for UART1.OCTOUT_14 — SCT output 14. Match output 2 of timer 3.I/OEMC_D3 — External memory data line 3R — Function reservedR — Function reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| PU       I       U1_RI - Ring Indicator input for UART1.         O       CTOUT_14 - SCT output 14. Match output 2 of timer 3.         I/O       EMC_D3 - External memory data line 3.         -       R - Function reserved.         I/O       SD_DAT1 - SD/MMC data bus line 1.         P1_11       T9       J7       77       55       I/I       V/O       GPI01[4] - General purpose digital input/output pin.         I       U1_CTS - Clear to Send input for UART1.       O       CTOUT_15 - SCT output 15. Match output 3 of timer 3.         V/O       EMC_D4 - External memory data line 4.       R - Function reserved.       R - Function reserved.         R - Function reserved.       R - Function reserved.       R - Function reserved.       R - Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                          |          |         |         |     |             | I/O  | <b>SD_DAT0</b> — SD/MMC data bus line 0.                    |

| $P1\_11$ $T9$ $T9$ $T9$ $T9$ $T9$ $T9$ $T9$ $T9$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P1_10       | R8                       | H6       | 75      | 53      | [2] |             | I/O  | <b>GPIO1[3]</b> — General purpose digital input/output pin. |

| P1_11       T9       J7       77       55       Image: P5       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                          |          |         |         |     | PU          | I    | U1_RI — Ring Indicator input for UART1.                     |

| P1_11       T9       J7       77       55       Image: Space of the system of th                                              |             |                          |          |         |         |     |             | 0    | CTOUT_14 — SCT output 14. Match output 2 of timer 3.        |

| P1_11       T9       J7       77       55       Image: Signature in the im                                              |             |                          |          |         |         |     |             | I/O  | EMC_D3 — External memory data line 3.                       |

| P1_11       T9       J7       77       55       I       N;<br>PU       I/O       GPI01[4] — General purpose digital input/output pin.         I       U1_CTS — Clear to Send input for UART1.       O       CTOUT_15 — SCT output 15. Match output 3 of timer 3.         I/O       EMC_D4 — External memory data line 4.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| P1_11       T9       J7       77       55       Image: P2 provided and p                                              |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| P1_11       T9       J7       77       55       I       N;<br>PU       I/O       GPI01[4] — General purpose digital input/output pin.         I       U1_CTS — Clear to Send input for UART1.       O       CTOUT_15 — SCT output 15. Match output 3 of timer 3.         I/O       EMC_D4 — External memory data line 4.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.         -       R — Function reserved.       -       R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| PU<br>PU<br>PU<br>PU<br>PU<br>PU<br>PU<br>PU<br>PU<br>PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                          |          |         |         |     |             | I/O  | <b>SD_DAT1</b> — SD/MMC data bus line 1.                    |

| Image: Comparison of the comparison | P1_11       | Т9                       | J7       | 77      | 55      | [2] |             | I/O  | <b>GPIO1[4]</b> — General purpose digital input/output pin. |

| <ul> <li>I/O EMC_D4 — External memory data line 4.</li> <li>R — Function reserved.</li> <li>R — Function reserved.</li> <li>R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                          |          |         |         |     | PU          | I    | <b>U1_CTS</b> — Clear to Send input for UART1.              |

| <ul> <li>- R — Function reserved.</li> <li>- R — Function reserved.</li> <li>- R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                          |          |         |         |     |             | 0    | <b>CTOUT_15</b> — SCT output 15. Match output 3 of timer 3. |

| <ul> <li>- R — Function reserved.</li> <li>- R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |                          |          |         |         |     |             | I/O  | <b>EMC_D4</b> — External memory data line 4.                |

| - <b>R</b> — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

| I/O <b>SD_DAT2</b> — SD/MMC data bus line 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                          |          |         |         |     |             | -    | R — Function reserved.                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                          |          |         |         |     |             | I/O  | SD_DAT2 — SD/MMC data bus line 2.                           |

Table 3. Pin description ...continued

Product data sheet

## 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                    |

|----------|---------|----------|---------|---------|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |         | Ë        |         |         | [0] |                    |      |                                                                                                                                                                |

| P4_0     | D5      | -        | 1       | 1       | [2] | N;<br>PU           | I/O  | <b>GPIO2[0]</b> — General purpose digital input/output pin.                                                                                                    |

|          |         |          |         |         |     |                    | 0    | MCOA0 — Motor control PWM channel 0, output A.                                                                                                                 |

|          |         |          |         |         |     |                    | I    | <b>NMI</b> — External interrupt input to NMI.                                                                                                                  |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | 0    | LCD_VD13 — LCD data.                                                                                                                                           |

|          |         |          |         |         |     |                    | I/O  | <b>U3_UCLK</b> — Serial clock input/output for USART3 in synchronous mode.                                                                                     |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

| P4_1     | A1      | -        | 3       | 3       | [5] | N;                 | I/O  | <b>GPIO2[1]</b> — General purpose digital input/output pin.                                                                                                    |

|          |         |          |         |         |     | PU                 | 0    | <b>CTOUT_1</b> — SCT output 1. Match output 3 of timer 3.                                                                                                      |

|          |         |          |         |         |     |                    | 0    | LCD_VD0 — LCD data.                                                                                                                                            |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | 0    | LCD_VD19 — LCD data.                                                                                                                                           |

|          |         |          |         |         |     |                    | 0    | <b>U3_TXD</b> — Transmitter output for USART3.                                                                                                                 |

|          |         |          |         |         |     |                    | I    | <b>ENET_COL</b> — Ethernet Collision detect (MII interface).                                                                                                   |

|          |         |          |         |         |     |                    | AI   | <b>ADC0_1</b> — ADC0 and ADC1, input channel 1. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.         |

| P4_2     | D3      | -        | 12      | 8       | [2] | N;                 | I/O  | GPIO2[2] — General purpose digital input/output pin.                                                                                                           |

|          |         |          |         |         |     | PU                 | 0    | CTOUT_0 — SCT output 0. Match output 0 of timer 0.                                                                                                             |

|          |         |          |         |         |     |                    | 0    | LCD_VD3 — LCD data.                                                                                                                                            |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | 0    | LCD_VD12 — LCD data.                                                                                                                                           |

|          |         |          |         |         |     |                    | I    | U3_RXD — Receiver input for USART3.                                                                                                                            |

|          |         |          |         |         |     |                    | I/O  | SGPIO8 — General purpose digital input/output pin.                                                                                                             |

| P4_3     | C2      | -        | 10      | 7       | [5] | N;                 | I/O  | GPIO2[3] — General purpose digital input/output pin.                                                                                                           |

|          |         |          |         |         |     | PU                 | 0    | CTOUT_3 — SCT output 3. Match output 3 of timer 0.                                                                                                             |

|          |         |          |         |         |     |                    | 0    | LCD_VD2 — LCD data.                                                                                                                                            |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                         |

|          |         |          |         |         |     |                    | 0    | LCD_VD21 — LCD data.                                                                                                                                           |

|          |         |          |         |         |     |                    | I/O  | U3_BAUD — Baud pin for USART3.                                                                                                                                 |

|          |         |          |         |         |     |                    | I/O  | SGPI09 — General purpose digital input/output pin.                                                                                                             |

|          |         |          |         |         |     |                    | AI   | <b>ADC0_0</b> — DAC, ADC0 and ADC1, input channel 0.<br>Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

Table 3.

Pin description ...continued

LPC435X\_3X\_2X\_1X

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                  |

|----------|---------|----------|---------|---------|-----|--------------------|------|--------------------------------------------------------------|

| P8_2     | K4      | -        | 36      | -       | [3] | N;                 | I/O  | GPIO4[2] — General purpose digital input/output pin.         |

|          |         |          |         |         |     | PU                 | 0    | <b>USB0_IND0</b> — USB0 port indicator LED control output 0. |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | I    | MCI0 — Motor control PWM channel 0, input.                   |

|          |         |          |         |         |     |                    | I/O  | SGPIO10 — General purpose digital input/output pin.          |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | 0    | T0_MAT2 — Match output 2 of timer 0.                         |

| P8_3     | J3      | -        | 37      | -       | [2] | N;                 | I/O  | GPIO4[3] — General purpose digital input/output pin.         |

|          |         |          |         |         |     | PU                 | I/O  | USB1_ULPI_D2 — ULPI link bidirectional data line 2.          |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | 0    | LCD_VD12 — LCD data.                                         |

|          |         |          |         |         |     |                    | 0    | LCD_VD19 — LCD data.                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | 0    | T0_MAT3 — Match output 3 of timer 0.                         |

| P8_4     | J2      | -        | 39      | -       | [2] | N;                 | I/O  | GPIO4[4] — General purpose digital input/output pin.         |

|          |         |          |         |         |     | PU                 | I/O  | USB1_ULPI_D1 — ULPI link bidirectional data line 1.          |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | 0    | LCD_VD7 — LCD data.                                          |

|          |         |          |         |         |     |                    | 0    | LCD_VD16 — LCD data.                                         |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

| 1        |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

| 1        |         |          |         |         |     |                    | I    | T0_CAP0 — Capture input 0 of timer 0.                        |

| P8_5     | J1      | -        | 40      | -       | [2] | N;                 | I/O  | GPIO4[5] — General purpose digital input/output pin.         |

|          |         |          |         |         |     | PU                 | I/O  | USB1_ULPI_D0 — ULPI link bidirectional data line 0.          |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                       |

|          |         |          |         |         |     |                    | 0    | LCD_VD6 — LCD data.                                          |

|          |         |          |         |         |     |                    | 0    | LCD_VD8 — LCD data.                                          |