Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                                                       |

| Core Processor             | ARM® Cortex®-M4/M0                                                                                             |

| Core Size                  | 32-Bit Dual-Core                                                                                               |

| Speed                      | 204MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, QEI, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, Motor Control PWM, POR, PWM, WDT                           |

| Number of I/O              | 164                                                                                                            |

| Program Memory Size        | 1MB (1M x 8)                                                                                                   |

| Program Memory Type        | FLASH                                                                                                          |

| EEPROM Size                | 16K x 8                                                                                                        |

| RAM Size                   | 136K x 8                                                                                                       |

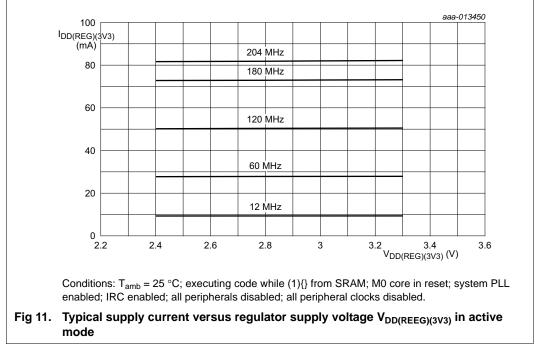

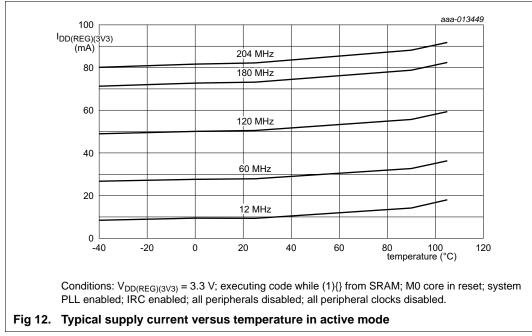

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                                    |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                           |

| Oscillator Type            | Internal                                                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                              |

| Mounting Type              | Surface Mount                                                                                                  |

| Package / Case             | 256-LBGA                                                                                                       |

| Supplier Device Package    | 256-LBGA (17x17)                                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4357fet256-551                                      |

|                            |                                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 32-bit ARM Cortex-M4/M0 microcontroller

| Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                                                 |

|----------|---------|----------|---------|---------|-----|-------------|------|---------------------------------------------------------------------------------------------|

| P1_1     | R2      | K2       | 58      | 42      | [2] | N;<br>PU    | I/O  | <b>GPIO0[8]</b> — General purpose digital input/output pin. Boot pin (see <u>Table 5</u> ). |

|          |         |          |         |         |     |             | 0    | <b>CTOUT_7</b> — SCT output 7. Match output 3 of timer 1.                                   |

|          |         |          |         |         |     |             | I/O  | <b>EMC_A6</b> — External memory address line 6.                                             |

|          |         |          |         |         |     |             | I/O  | <b>SGPI08</b> — General purpose digital input/output pin.                                   |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                      |

|          |         |          |         |         |     |             | I/O  | <b>SSP0_MISO</b> — Master In Slave Out for SSP0.                                            |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                      |

|          |         |          |         |         |     |             | I/O  | EMC_D13 — External memory data line 13.                                                     |

| P1_2     | R3      | K1       | 60      | 43      | [2] | N;<br>PU    | I/O  | <b>GPIO0[9]</b> — General purpose digital input/output pin. Boot pin (see <u>Table 5</u> ). |

|          |         |          |         |         |     |             | 0    | CTOUT_6 — SCT output 6. Match output 2 of timer 1.                                          |

|          |         |          |         |         |     |             | I/O  | EMC_A7 — External memory address line 7.                                                    |

|          |         |          |         |         |     |             | I/O  | SGPI09 — General purpose digital input/output pin.                                          |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                      |

|          |         |          |         |         |     |             | I/O  | <b>SSP0_MOSI</b> — Master Out Slave in for SSP0.                                            |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                      |

|          |         |          |         |         |     |             | I/O  | <b>EMC_D14</b> — External memory data line 14.                                              |

| P1_3     | P5      | J1       | 61      | 44      | [2] | N;          | I/O  | <b>GPIO0[10]</b> — General purpose digital input/output pin.                                |

|          |         |          |         |         |     | PU          | 0    | <b>CTOUT_8</b> — SCT output 8. Match output 0 of timer 2.                                   |

|          |         |          |         |         |     |             | I/O  | <b>SGPIO10</b> — General purpose digital input/output pin.                                  |

|          |         |          |         |         |     |             | 0    | <b>EMC_OE</b> — LOW active Output Enable signal.                                            |

|          |         |          |         |         |     |             | 0    | <b>USB0_IND1</b> — USB0 port indicator LED control output 1.                                |

|          |         |          |         |         |     |             | I/O  | SSP1_MISO — Master In Slave Out for SSP1.                                                   |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                                                      |

|          |         |          |         |         |     |             | 0    | <b>SD_RST</b> — SD/MMC reset signal for MMC4.4 card.                                        |

| P1_4     | Т3      | J2       | 64      | 47      | [2] | N;          | I/O  | <b>GPIO0[11]</b> — General purpose digital input/output pin.                                |

|          |         |          |         |         |     | PU          | 0    | <b>CTOUT_9</b> — SCT output 9. Match output 3 of timer 3.                                   |

|          |         |          |         |         |     |             | I/O  | <b>SGPI011</b> — General purpose digital input/output pin.                                  |

|          |         |          |         |         |     |             | 0    | <b>EMC_BLS0</b> — LOW active Byte Lane select signal 0.                                     |

|          |         |          |         |         |     |             | 0    | <b>USB0_IND0</b> — USB0 port indicator LED control output 0.                                |

|          |         |          |         |         |     |             | I/O  | SSP1_MOSI — Master Out Slave in for SSP1.                                                   |

|          |         |          |         |         |     |             | I/O  | EMC_D15 — External memory data line 15.                                                     |

|          |         |          |         |         |     |             | 0    | <b>SD_VOLT1</b> — SD/MMC bus voltage select output 1.                                       |

#### Table 3. Pin description ...continued

| Table 3. | Pin a | escrip  | otion    | continu | ed      |     |             |      |                                                                                      |

|----------|-------|---------|----------|---------|---------|-----|-------------|------|--------------------------------------------------------------------------------------|

| Pin name |       | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                                                          |

| PD_7     |       | T6      | -        | 72      | -       | [2] | N;          | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     | PU          | I    | CTIN_5 — SCT input 5. Capture input 2 of timer 2.                                    |

|          |       |         |          |         |         |     |             | I/O  | EMC_D21 — External memory data line 21.                                              |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | I/O  | GPIO6[21] — General purpose digital input/output pin.                                |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | I/O  | SGPI011 — General purpose digital input/output pin.                                  |

| PD_8     |       | P8      | -        | 74      | -       | [2] | N;          | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     | PU          | I    | CTIN_6 — SCT input 6. Capture input 1 of timer 3.                                    |

|          |       |         |          |         |         |     |             | I/O  | EMC_D22 — External memory data line 22.                                              |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | I/O  | GPIO6[22] — General purpose digital input/output pin.                                |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | I/O  | SGPI012 — General purpose digital input/output pin.                                  |

| PD_9     |       | T11     | -        | 84      | -       | [2] | N;          | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     | PU          | 0    | <b>CTOUT_13</b> — SCT output 13. Match output 3 of timer 3.                          |

|          |       |         |          |         |         |     |             | I/O  | EMC_D23 — External memory data line 23.                                              |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | I/O  | <b>GPIO6[23]</b> — General purpose digital input/output pin.                         |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | I/O  | SGPI013 — General purpose digital input/output pin.                                  |

| PD_10    |       | P11     | -        | 86      | -       | [2] | N;          | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     | PU          | I    | <b>CTIN_1</b> — SCT input 1. Capture input 1 of timer 0. Capture input 1 of timer 2. |

|          |       |         |          |         |         |     |             | 0    | EMC_BLS3 — LOW active Byte Lane select signal 3.                                     |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | I/O  | GPIO6[24] — General purpose digital input/output pin.                                |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

|          |       |         |          |         |         |     |             | -    | R — Function reserved.                                                               |

Table 3.

Pin description ...continued

| PE_14       C15       -       -       -       R       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R       -       R </th <th>Pin name</th> <th>LBGA256</th> <th>TFBGA100</th> <th>LQFP208</th> <th>LQFP144</th> <th></th> <th>Reset state</th> <th>Type</th> <th>Description</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin name | LBGA256 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state | Type | Description                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------|---------|---------|-----|-------------|------|-----------------------------------------------------------|

| PE_15     E13     -     -     R     -     R     -     Function reserved.       PE_15     E13     -     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     -     R     - <td>PE_14</td> <td>C15</td> <td>-</td> <td>-</td> <td>-</td> <td>[2]</td> <td>N;</td> <td>-</td> <td>R — Function reserved.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PE_14    | C15     | -        | -       | -       | [2] | N;          | -    | R — Function reserved.                                    |

| PE_15     E13     -     -     Image: Ima                   |          |         |          |         |         |     | PU          | -    | R — Function reserved.                                    |

| PE_15     E13     -     -     Image: Ima                   |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PE_15     E13     -     R     -     R - Function reserved.       PE_15     E13     -     R     -     R - Function reserved.       0     CTOUT_0 - SCT output 0. Match output 0 of timer 0.     V/0     I2C1_SCL - I2C1 clock input/output (this pin does not use a specialized 12C pad).       0     EMC_CKEOUT3 - SDRAM clock enable 3.     V/0     GPI07[15] - General purpose digital input/output pin.       -     R - Function reserved.     -     R - Function reserved.       PF_0     D12     -     159     -     I2       PF_0     D12     -     159     -     I2       PF_1     E11     -     159     -     I2       PF_1     E11     -     R     -     R - Function reserved.       -     R - Function reserved.     -     R - Function reserved.       -     R - Function reserved.     -     R - Function reserved.       -     R - Function reserved.     -     R - Function reserved.       -     R - Function reserved.     -     R - Function reserved.       -     R - Function reserved.     -     R - Function reserved.       -     R - Function reserved.     -     R - Function reserved.       -     R - Function reserved.     -     R - Function reserved. <tr< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0</td><td>EMC_DYCS3 — SDRAM chip select 3.</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |         |          |         |         |     |             | 0    | EMC_DYCS3 — SDRAM chip select 3.                          |

| PE_15     E13     -     -     R - Function reserved.       PE_15     E13     -     -     R - Function reserved.       0     CTOUT_0 - SCT output 0. Match output 0 of timer 0.       VO     VO     ISC1_SCL - I <sup>2</sup> C1 clock input/output (this pin does not use a specialized I2C pad).       0     EMC_CKEOUT3 - SDRAM clock enable 3.       VO     POT0[15] - General purpose digital input/output pin.       -     R - Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |         |          |         |         |     |             | I/O  | GPI07[14] — General purpose digital input/output pin.     |

| PE_15       E13       -       -       R - Function reserved.         PE_15       E13       -       -       R       -       R - Function reserved.         0       CTOUT_0 - SCT output 0. Match output 0 of timer 0.       VO       VO       ISC1_SCL - I2C1 clock input/output (this pin does not use a specialized I2C pad).         0       EMC_CKEOUT3 - SDRAM clock enable 3.       VO       GPI07[15] General purpose digital input/output pin.         R - Function reserved.       -       R - Function reserved.       -         PF_0       D12       -       159       2       VI       SSP0_SCK - Serial clock for SSP0.         PF_0       D12       -       159       2       VI       SPC_LKIN - General purpose clock input to the CGU.         -       R - Function reserved.       -       R - Function reserved.       -         PF_0       D12       -       159       YI       YI       SPC_LKIN - General purpose clock input to the CGU.         -       R - Function reserved.       -       R - Function reserved.       -       R - Function reserved.         PF_0       D12       -       159       YI       YI       YI       SPC_LKIN - General purpose clock input to the CGU.         -       R - Function reserved.       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PE_15     E13     -     -     I     I     N;<br>PU     PU     -     R - Function reserved.       0     CTOUT_0 - SCT output 0. Match output 0 of timer 0.     I/O     I2C1_SCL - I <sup>2</sup> C1 clock input/output (this pin does not use a<br>specialized I2C pad).       0     EMC_CKEOUT3 - SDRAM clock enable 3.       I/O     GPI07[15] - General purpose digital input/output pin.       -     R - Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PL     E     Image: Sector of the sec |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PF_0       D12       -       159       -       Image: Construction of the construction of                                           | PE_15    | E13     | -        | -       | -       | [2] |             | -    | R — Function reserved.                                    |

| PF_0       D12       -       159       -       [2]       O;       I/O       GPI07[15] — General purpose digital input/output pin.       -       R — Function reserved.         PF_0       D12       -       159       -       [2]       O;       I/O       SSP0_SCK — Serial clock for SSP0.       I       GPIC/LKIN — General purpose clock input to the CGU.       -       R — Function reserved.         PF_1       Final Provide the                                                                                                                                                                                                                                                                |          |         |          |         |         |     | PU          | 0    | CTOUT_0 — SCT output 0. Match output 0 of timer 0.        |

| PF_0     D12     -     159     -     C     PU     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W     W    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |         |          |         |         |     |             | I/O  |                                                           |

| PF_0       D12       -       159       -       Image: Constraint of the constrant of the constraint of the constraint of the constrain                                          |          |         |          |         |         |     |             | 0    | EMC_CKEOUT3 — SDRAM clock enable 3.                       |

| PF_0     D12     -     159     -     Image: Constraint of the constrand of t                            |          |         |          |         |         |     |             | I/O  | GPI07[15] — General purpose digital input/output pin.     |

| PF_0       D12       -       IS9       -       IS9       O;<br>PU       I/O       SSP0_SCK - Serial clock for SSP0.         PF_0       D12       -       IS9       -       IS9       O;<br>PU       I/O       SSP0_SCK - Serial clock for SSP0.         I       GP_CLKIN - General purpose clock input to the CGU.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PF_0D12-159-ISPUI/OSSP0_SCK — Serial clock for SSP0.IGP_CLKIN — General purpose clock input to the CGUR — Function reservedR — Function reserved <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>-</td><td>R — Function reserved.</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PU       I       GP_CLKIN — General purpose clock input to the CGU.       .         I       GP_CLKIN — General purpose clock input to the CGU.       .         I       GP_CLKIN — General purpose clock input to the CGU.       .         I       GP_CLKIN — General purpose clock input to the CGU.       .         I       GP_CLKIN — General purpose clock input to the CGU.       .         I       R — Function reserved.       .         I       III I       .       .         III I       .       .       .         III I       . <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>-</td><td>R — Function reserved.</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PF_1       E11       -       -       -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.       -       R - Function reserved.         0       I2S1_TX_MCLK - I2S1 transmit master clock.       -       R - Function reserved.       -         VO       ISSP0_SSEL - Slave Select for SSP0.       -       R - Function reserved.       -         VO       GPI07[16] - General purpose digital input/output pin.       -       R - Function reserved.       -         VO       SGPI00 - General purpose digital input/output pin.       -       R - Function reserved.       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PF_0     | D12     | -        | 159     | -       | [2] |             | I/O  | SSP0_SCK — Serial clock for SSP0.                         |

| PF_1       E11       -       -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.         -       R - Function reserved.       -       R - Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         |          |         |         |     | PU          | I    | <b>GP_CLKIN</b> — General purpose clock input to the CGU. |

| PF_1       E11       -       -       R - Function reserved.       -       R - Function reserved.         PF_1       E11       -       -       -       R - Function reserved.         PF_1       E11       -       -       -       R - Function reserved.         VO       I2S1_TX_MCLK - I2S1 transmit master clock.         PF_1       E11       -       -       R - Function reserved.         VO       SSP0_SSEL - Slave Select for SSP0.       -       R - Function reserved.         VO       GPI07[16] - General purpose digital input/output pin.       -       R - Function reserved.         VO       SGPI00 - General purpose digital input/output pin.       -       R - Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PF_1     E11     -     -     R — Function reserved.       -     R — Function reserved.     -       0     I2S1_TX_MCLK — I2S1 transmit master clock.       -     R — Function reserved.       0     I2S1_TX_MCLK — I2S1 transmit master clock.       -     R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PF_1     E11     -     -     R — Function reserved.       0     I2S1_TX_MCLK — I2S1 transmit master clock.       PF_1     E11     -     -     R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PF_1       E11       -       -       Image: Constraint of the constrain                                 |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PF_1       E11       -       -       R       -       R — Function reserved.         -       R       -       Function reserved.       -       R         -       R       -       Function reserved.       -         -       N;       -       R       -       Function reserved.         -       N;       SGPI00       -       General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| PU       -       R — Function reserved.         I/O       SSP0_SSEL — Slave Select for SSP0.         -       R — Function reserved.         I/O       GPI07[16] — General purpose digital input/output pin.         -       R — Function reserved.         I/O       SGPI00 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |         |          |         |         |     |             | 0    | I2S1_TX_MCLK — I2S1 transmit master clock.                |

| I/O       SSP0_SSEL — Slave Select for SSP0.         -       R — Function reserved.         I/O       GPI07[16] — General purpose digital input/output pin.         -       R — Function reserved.         I/O       SGPI00 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PF_1     | E11     | -        | -       | -       | [2] |             | -    | R — Function reserved.                                    |

| <ul> <li>- R — Function reserved.</li> <li>I/O GPI07[16] — General purpose digital input/output pin.</li> <li>- R — Function reserved.</li> <li>I/O SGPI00 — General purpose digital input/output pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |         |          |         |         |     | PU          | -    | R — Function reserved.                                    |

| <ul> <li>I/O GPI07[16] — General purpose digital input/output pin.</li> <li>R — Function reserved.</li> <li>I/O SGPI00 — General purpose digital input/output pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |         |          |         |         |     |             | I/O  | SSP0_SSEL — Slave Select for SSP0.                        |

| -     R — Function reserved.       I/O     SGPI00 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| I/O <b>SGPI00</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |         |          |         |         |     |             | I/O  | GPIO7[16] — General purpose digital input/output pin.     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

| - R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |         |          |         |         |     |             | I/O  | SGPI00 — General purpose digital input/output pin.        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |         |          |         |         |     |             | -    | R — Function reserved.                                    |

Table 3.

Pin description ...continued

| Pin name                | LBGA256                                                                                     | TFBGA100         | LQFP208                                                 | LQFP144                                               |            | Reset state | Type | Description                                                                                                                                   |

|-------------------------|---------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------|-------------------------------------------------------|------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1                   | D1                                                                                          | B1               | 18                                                      | 12                                                    | <u>[8]</u> | -           | I    | Input to the oscillator circuit and internal clock generator circuits.                                                                        |

| XTAL2                   | E1                                                                                          | C1               | 19                                                      | 13                                                    | [8]        | -           | 0    | Output from the oscillator amplifier.                                                                                                         |

| Power and gro           | und pir                                                                                     | IS               |                                                         |                                                       |            |             |      |                                                                                                                                               |

| USB0_VDDA<br>3V3_DRIVER | F3                                                                                          | D1               | 24                                                      | 16                                                    |            | -           | -    | Separate analog 3.3 V power supply for driver.                                                                                                |

| USB0<br>_VDDA3V3        | G3                                                                                          | D2               | 25                                                      | 17                                                    |            | -           | -    | USB 3.3 V separate power supply voltage.                                                                                                      |

| USB0_VSSA<br>_TERM      | H3                                                                                          | D3               | 27                                                      | 19                                                    |            | -           | -    | Dedicated analog ground for clean reference for termination resistors.                                                                        |

| USB0_VSSA<br>_REF       | G1                                                                                          | F2               | 31                                                      | 23                                                    |            | -           | -    | Dedicated clean analog ground for generation of reference currents and voltages.                                                              |

| VDDA                    | B4                                                                                          | B2               | 198                                                     | 137                                                   |            | -           | -    | Analog power supply and ADC reference voltage.                                                                                                |

| VBAT                    | B10                                                                                         | C5               | 184                                                     | 127                                                   |            | -           | -    | RTC power supply: 3.3 V on this pin supplies power to the RTC.                                                                                |

| VDDREG                  | F10,<br>F9,<br>L8,<br>L7                                                                    | E4,<br>E5,<br>F4 | 135,<br>188,<br>195,<br>82,<br>33                       | 94,<br>131,<br>59,<br>25                              |            |             | -    | Main regulator power supply. Tie the VDDREG and VDDIO pins to a common power supply to ensure the same ramp-up time for both supply voltages. |

| VPP                     | E8                                                                                          | -                | -                                                       | -                                                     | [12]       | -           | -    | OTP programming voltage.                                                                                                                      |

| VDDIO                   | D7,<br>E12,<br>F7,<br>F8,<br>G10,<br>H10,<br>J6,<br>J7,<br>K7,<br>L9,<br>L10,<br>N7,<br>N13 | F10,<br>K5       | 6,<br>52,<br>57,<br>102,<br>110,<br>155,<br>160,<br>202 | 5,<br>36,<br>41,<br>71,<br>77,<br>107,<br>111,<br>141 | [12]       | -           | -    | I/O power supply. Tie the VDDREG and VDDIO pins to a common power supply to ensure the same ramp-up time for both supply voltages.            |

Table 3.

Pin description ...continued

### 32-bit ARM Cortex-M4/M0 microcontroller

In the two-counter case, the following operational elements are global to the SCTimer/PWM, but the last three can use match conditions from either counter:

- Clock selection

- Inputs

- Events

- Outputs

- Interrupts

### 7.17.1.1 Features

- Two 16-bit counters or one 32-bit counter.

- · Counters clocked by bus clock or selected input.

- Up counters or up-down counters.

- State variable allows sequencing across multiple counter cycles.

- The following conditions define an event: a counter match condition, an input (or output) condition, a combination of a match and/or and input/output condition in a specified state.

- Events control outputs, interrupts, and DMA requests.

- Match register 0 can be used as an automatic limit.

- In bi-directional mode, events can be enabled based on the count direction.

- Match events can be held until another qualifying event occurs.

- Selected events can limit, halt, start, or stop a counter.

- Supports:

- 8 inputs

- 16 outputs

- 16 match/capture registers

- 16 events

- 32 states

- Match register 0 to 5 support a fractional component for the dither engine

### 7.17.2 Serial GPIO (SGPIO)

The Serial GPIOs offer standard GPIO functionality enhanced with features to accelerate serial stream processing.

### 7.17.2.1 Features

- Each SGPIO input/output slice can be used to perform a serial to parallel or parallel to serial data conversion.

- 16 SGPIO input/output slices each with a 32-bit FIFO that can shift the input value from a pin or an output value to a pin with every cycle of a shift clock.

- Each slice is double-buffered.

- Interrupt is generated on a full FIFO, shift clock, or pattern match.

- Slices can be concatenated to increase buffer size.

### 32-bit ARM Cortex-M4/M0 microcontroller

- Supports both full-duplex and half-duplex operation

- Supports CSMA/CD Protocol for half-duplex operation.

- Supports IEEE 802.3x flow control for full-duplex operation.

- Optional forwarding of received pause control frames to the user application in full-duplex operation.

- Back-pressure support for half-duplex operation.

- Automatic transmission of zero-quanta pause frame on deassertion of flow control input in full-duplex operation.

- Supports IEEE1588 time stamping and IEEE 1588 advanced time stamping (IEEE 1588-2008 v2).

## 7.19 Digital serial peripherals

### 7.19.1 UART1

**Remark:** The LPC435x/3x/2x/1x contain one UART with standard transmit and receive data lines.

UART1 also provides a full modem control handshake interface and support for RS-485/9-bit mode allowing both software address detection and automatic address detection using 9-bit mode.