# E·XFL

### Intel - EPF81500ARC240-4 Datasheet

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 162                                                         |

| Number of Logic Elements/Cells | 1296                                                        |

| Total RAM Bits                 | -                                                           |

| Number of I/O                  | 181                                                         |

| Number of Gates                | 16000                                                       |

| Voltage - Supply               | 4.75V ~ 5.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 240-BFQFP Exposed Pad                                       |

| Supplier Device Package        | 240-RQFP (32x32)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf81500arc240-4 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Each LAB provides four control signals that can be used in all eight LEs. Two of these signals can be used as clocks, and the other two for clear/preset control. The LAB control signals can be driven directly from a dedicated input pin, an I/O pin, or any internal signal via the LAB local interconnect. The dedicated inputs are typically used for global clock, clear, or preset signals because they provide synchronous control with very low skew across the device. FLEX 8000 devices support up to four individual global clock, clear, or preset control signals. If logic is required on a control signal, it can be generated in one or more LEs in any LAB and driven into the local interconnect of the target LAB.

### Logic Element

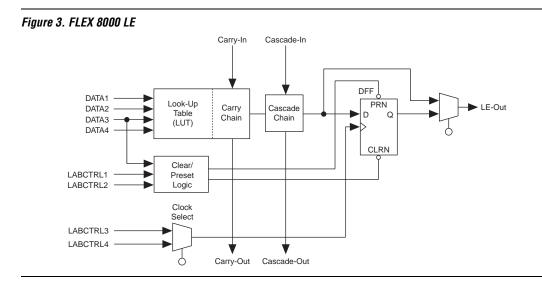

The logic element (LE) is the smallest unit of logic in the FLEX 8000 architecture, with a compact size that provides efficient logic utilization. Each LE contains a 4-input LUT, a programmable flipflop, a carry chain, and cascade chain. Figure 3 shows a block diagram of an LE.

The LUT is a function generator that can quickly compute any function of four variables. The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by dedicated input pins, general-purpose I/O pins, or any internal logic. For purely combinatorial functions, the flipflop is bypassed and the output of the LUT goes directly to the output of the LE.

The FLEX 8000 architecture provides two dedicated high-speed data paths—carry chains and cascade chains—that connect adjacent LEs without using local interconnect paths. The carry chain supports highspeed counters and adders; the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in an LAB and all LABs in the same row. Heavy use of carry and cascade chains can reduce routing flexibility. Therefore, the use of carry and cascade chains should be limited to speed-critical portions of a design.

### Carry Chain

The carry chain provides a very fast (less than 1 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit moves forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 8000 architecture to implement high-speed counters and adders of arbitrary width. The MAX+PLUS II Compiler can create carry chains automatically during design processing; designers can also insert carry chain logic manually during design entry.

Figure 4 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register is typically bypassed for simple adders, but can be used for an accumulator function. Another portion of the LUT and the carry chain logic generate the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to another LE, where it can be used as a general-purpose signal. In addition to mathematical functions, carry chain logic supports very fast counters and comparators.

### Asynchronous Clear

A register is cleared by one of the two LABCTRL signals. When the CLRn port receives a low signal, the register is set to zero.

### **Asynchronous Preset**

An asynchronous preset is implemented as either an asynchronous load or an asynchronous clear. If DATA3 is tied to VCC, asserting LABCTRL1 asynchronously loads a 1 into the register. Alternatively, the MAX+PLUS II software can provide preset control by using the clear and inverting the input and output of the register. Inversion control is available for the inputs to both LEs and IOEs. Therefore, if a register is preset by only one of the two LABCTRL signals, the DATA3 input is not needed and can be used for one of the LE operating modes.

### Asynchronous Clear & Preset

When implementing asynchronous clear and preset, LABCTRL1 controls the preset and LABCTRL2 controls the clear. The DATA3 input is tied to VCC; therefore, asserting LABCTRL1 asynchronously loads a 1 into the register, effectively presetting the register. Asserting LABCTRL2 clears the register.

### Asynchronous Load with Clear

When implementing an asynchronous load with the clear, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear. LABCTRL2 implements the clear by controlling the register clear.

### Asynchronous Load with Preset

When implementing an asynchronous load in conjunction with a preset, the MAX+PLUS II software provides preset control by using the clear and inverting the input and output of the register. Asserting LABCTRL2 clears the register, while asserting LABCTRL1 loads the register. The MAX+PLUS II software inverts the signal that drives the DATA3 signal to account for the inversion of the register's output.

### Asynchronous Load without Clear or Preset

When implementing an asynchronous load without the clear or preset, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear.

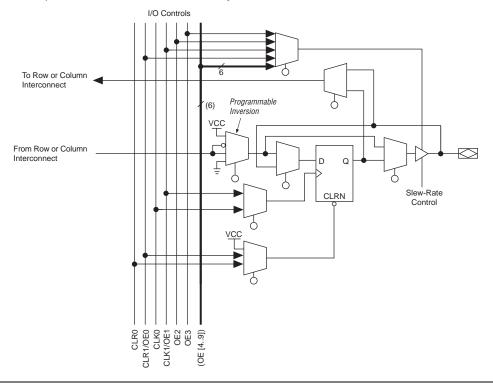

### Figure 10. FLEX 8000 IOE

Numbers in parentheses are for EPF81500A devices only.

### Row-to-IOE Connections

Figure 11 illustrates the connection between row interconnect channels and IOEs. An input signal from an IOE can drive two separate row channels. When an IOE is used as an output, the signal is driven by an *n*-to-1 multiplexer that selects the row channels. The size of the multiplexer varies with the number of columns in a device. EPF81500A devices use a 27-to-1 multiplexer; EPF81188A, EPF8820A, EPF8636A, and EPF8452A devices use a 21-to-1 multiplexer; and EPF8282A and EPF8282AV devices use a 13-to-1 multiplexer. Eight IOEs are connected to each side of the row channels.

### MultiVolt I/O Interface

The FLEX 8000 device architecture supports the MultiVolt I/O interface feature, which allows EPF81500A, EPF81188A, EPF8820A, and EPF8636A devices to interface with systems with differing supply voltages. These devices in all packages—except for EPF8636A devices in 84-pin PLCC packages—can be set for 3.3-V or 5.0-V I/O pin operation. These devices have one set of V<sub>CC</sub> pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The VCCINT pins must always be connected to a 5.0-V power supply. With a 5.0-V V<sub>CCINT</sub> level, input voltages are at TTL levels and are therefore compatible with 3.3-V and 5.0-V inputs.

The VCCIO pins can be connected to either a 3.3-V or 5.0-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 5.0-V power supply, the output levels are compatible with 5.0-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is at 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with V<sub>CCIO</sub> levels lower than 4.75 V incur a nominally greater timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ . See Table 8 on page 26.

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

The EPF8282A, EPF8282AV, EPF8636A, EPF8820A, and EPF81500A devices provide JTAG BST circuitry. FLEX 8000 devices with JTAG circuitry support the JTAG instructions shown in Table 6.

| Table 6. EPF8282A, | Table 6. EPF8282A, EPF8282AV, EPF8636A, EPF8820A & EPF81500A JTAG Instructions                                                                                                                 |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG Instruction   | Description                                                                                                                                                                                    |  |  |  |

| SAMPLE/PRELOAD     | Allows a snapshot of the signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins.           |  |  |  |

| EXTEST             | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                         |  |  |  |

| BYPASS             | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through the selected device to adjacent devices during normal device operation. |  |  |  |

| Table 1          | 2. FLEX 8000 5.0-V Device Ca | pacitance Note (8)                  |     |     |      |

|------------------|------------------------------|-------------------------------------|-----|-----|------|

| Symbol           | Parameter                    | Conditions                          | Min | Max | Unit |

| C <sub>IN</sub>  | Input capacitance            | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |

| C <sub>OUT</sub> | Output capacitance           | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |

### Notes to tables:

(1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 7.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) The maximum  $V_{CC}$  rise time is 100 ms.

- (4) Numbers in parentheses are for industrial-temperature-range devices.

- (5) Typical values are for  $T_A = 25^\circ \text{ C}$  and  $V_{CC} = 5.0 \text{ V}$ .

- (6) These values are specified in Table 10 on page 28.

- (7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current; the I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current.

- (8) Capacitance is sample-tested only.

Tables 13 through 16 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for 3.3-V FLEX 8000 devices.

| Table 1          | Table 13. FLEX 8000 3.3-V Device Absolute Maximum Ratings       Note (1) |                              |      |     |      |  |

|------------------|--------------------------------------------------------------------------|------------------------------|------|-----|------|--|

| Symbol           | Parameter                                                                | Conditions                   | Min  | Max | Unit |  |

| V <sub>CC</sub>  | Supply voltage                                                           | With respect to ground (2)   | -2.0 | 5.3 | V    |  |

| VI               | DC input voltage                                                         |                              | -2.0 | 5.3 | V    |  |

| I <sub>OUT</sub> | DC output current, per pin                                               |                              | -25  | 25  | mA   |  |

| T <sub>STG</sub> | Storage temperature                                                      | No bias                      | -65  | 150 | °C   |  |

| T <sub>AMB</sub> | Ambient temperature                                                      | Under bias                   | -65  | 135 | °C   |  |

| TJ               | Junction temperature                                                     | Plastic packages, under bias |      | 135 | °C   |  |

| Table 1         | Table 14. FLEX 8000 3.3-V Device Recommended Operating Conditions |                    |      |                       |      |  |  |

|-----------------|-------------------------------------------------------------------|--------------------|------|-----------------------|------|--|--|

| Symbol          | Parameter                                                         | Conditions         | Min  | Max                   | Unit |  |  |

| V <sub>CC</sub> | Supply voltage                                                    | (3)                | 3.0  | 3.6                   | V    |  |  |

| VI              | Input voltage                                                     |                    | -0.3 | V <sub>CC</sub> + 0.3 | V    |  |  |

| Vo              | Output voltage                                                    |                    | 0    | V <sub>CC</sub>       | V    |  |  |

| Τ <sub>Α</sub>  | Operating temperature                                             | For commercial use | 0    | 70                    | °C   |  |  |

| t <sub>R</sub>  | Input rise time                                                   |                    |      | 40                    | ns   |  |  |

| t <sub>F</sub>  | Input fall time                                                   |                    |      | 40                    | ns   |  |  |

### FLEX 8000 Programmable Logic Device Family Data Sheet

| Table 1          | Table 15. FLEX 8000 3.3-V Device DC Operating Conditions       Note (4) |                                                  |                |     |                       |      |  |

|------------------|-------------------------------------------------------------------------|--------------------------------------------------|----------------|-----|-----------------------|------|--|

| Symbol           | Parameter                                                               | Conditions                                       | Min            | Тур | Max                   | Unit |  |

| V <sub>IH</sub>  | High-level input voltage                                                |                                                  | 2.0            |     | V <sub>CC</sub> + 0.3 | V    |  |

| V <sub>IL</sub>  | Low-level input voltage                                                 |                                                  | -0.3           |     | 0.8                   | V    |  |

| V <sub>OH</sub>  | High-level output voltage                                               | I <sub>OH</sub> = -0.1 mA DC <i>(</i> 5 <i>)</i> | $V_{CC} - 0.2$ |     |                       | V    |  |

| V <sub>OL</sub>  | Low-level output voltage                                                | I <sub>OL</sub> = 4 mA DC <i>(</i> 5 <i>)</i>    |                |     | 0.45                  | V    |  |

| I <sub>I</sub>   | Input leakage current                                                   | $V_{I} = V_{CC}$ or ground                       | -10            |     | 10                    | μA   |  |

| I <sub>OZ</sub>  | Tri-state output off-state current                                      | $V_{O} = V_{CC}$ or ground                       | -40            |     | 40                    | μA   |  |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby)                                | V <sub>I</sub> = ground, no load (6)             |                | 0.3 | 10                    | mA   |  |

| Table 1          | 6. FLEX 8000 3.3-V Device Cap | acitance Note (7)                   |     |     |      |

|------------------|-------------------------------|-------------------------------------|-----|-----|------|

| Symbol           | Parameter                     | Conditions                          | Min | Max | Unit |

| C <sub>IN</sub>  | Input capacitance             | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |

| C <sub>OUT</sub> | Output capacitance            | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |

### Notes to tables:

(1) See the Operating Requirements for Altera Devices Data Sheet.

(2) Minimum DC input voltage is -0.3 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.3 V for input currents less than 100 mA and periods shorter than 20 ns.

(3) The maximum  $V_{CC}$  rise time is 100 ms.  $\overline{V}_{CC}$  must rise monotonically.

(4) These values are specified in Table 14 on page 29.

(5) The I<sub>OH</sub> parameter refers to high-level TTL output current; the I<sub>OL</sub> parameter refers to low-level TTL output current.

(6) Typical values are for  $T_A = 25^\circ \text{ C}$  and  $V_{CC} = 3.3 \text{ V}$ .

(7) Capacitance is sample-tested only.

Figure 16 shows the typical output drive characteristics of 5.0-V FLEX 8000 devices. The output driver is compliant with *PCI Local Bus Specification, Revision* 2.2.

| Table 17. F         | Table 17. FLEX 8000 Internal Timing Parameters       Note (1)                                        |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol              | Parameter                                                                                            |  |  |  |  |

| t <sub>IOD</sub>    | IOE register data delay                                                                              |  |  |  |  |

| t <sub>IOC</sub>    | IOE register control signal delay                                                                    |  |  |  |  |

| t <sub>IOE</sub>    | Output enable delay                                                                                  |  |  |  |  |

| t <sub>IOCO</sub>   | IOE register clock-to-output delay                                                                   |  |  |  |  |

| t <sub>IOCOMB</sub> | IOE combinatorial delay                                                                              |  |  |  |  |

| t <sub>IOSU</sub>   | IOE register setup time before clock; IOE register recovery time after asynchronous clear            |  |  |  |  |

| t <sub>IOH</sub>    | IOE register hold time after clock                                                                   |  |  |  |  |

| t <sub>IOCLR</sub>  | IOE register clear delay                                                                             |  |  |  |  |

| t <sub>IN</sub>     | Input pad and buffer delay                                                                           |  |  |  |  |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, $V_{CCIO} = 5.0 \text{ V C1} = 35 \text{ pF}$ (2) |  |  |  |  |

| t <sub>OD2</sub>    | Output buffer and pad delay, slow slew rate = off, $V_{CCIO}$ = 3.3 V C1 = 35 pF (2)                 |  |  |  |  |

| t <sub>OD3</sub>    | Output buffer and pad delay, slow slew rate = on, C1 = 35 pF (3)                                     |  |  |  |  |

| t <sub>XZ</sub>     | Output buffer disable delay, C1 = 5 pF                                                               |  |  |  |  |

| t <sub>ZX1</sub>    | Output buffer enable delay, slow slew rate = off, $V_{CCIO}$ = 5.0 V, C1 = 35 pF (2)                 |  |  |  |  |

| t <sub>ZX2</sub>    | Output buffer enable delay, slow slew rate = off, $V_{CCIO}$ = 3.3 V, C1 = 35 pF (2)                 |  |  |  |  |

| t <sub>ZX3</sub>    | Output buffer enable delay, slow slew rate = on, C1 = 35 pF $(3)$                                    |  |  |  |  |

| Symbol             | Parameter                                                                                                |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| t <sub>LUT</sub>   | LUT delay for data-in                                                                                    |  |  |  |  |  |  |

| t <sub>CLUT</sub>  | LUT delay for carry-in                                                                                   |  |  |  |  |  |  |

| t <sub>RLUT</sub>  | LUT delay for LE register feedback                                                                       |  |  |  |  |  |  |

| t <sub>GATE</sub>  | Cascade gate delay                                                                                       |  |  |  |  |  |  |

| t <sub>CASC</sub>  | Cascade chain routing delay                                                                              |  |  |  |  |  |  |

| t <sub>CICO</sub>  | Carry-in to carry-out delay                                                                              |  |  |  |  |  |  |

| t <sub>CGEN</sub>  | Data-in to carry-out delay                                                                               |  |  |  |  |  |  |

| t <sub>CGENR</sub> | LE register feedback to carry-out delay                                                                  |  |  |  |  |  |  |

| t <sub>C</sub>     | LE register control signal delay                                                                         |  |  |  |  |  |  |

| t <sub>CH</sub>    | LE register clock high time                                                                              |  |  |  |  |  |  |

| t <sub>CL</sub>    | LE register clock low time                                                                               |  |  |  |  |  |  |

| t <sub>CO</sub>    | LE register clock-to-output delay                                                                        |  |  |  |  |  |  |

| t <sub>COMB</sub>  | Combinatorial delay                                                                                      |  |  |  |  |  |  |

| t <sub>SU</sub>    | LE register setup time before clock; LE register recovery time after asynchronous preset, clear, or load |  |  |  |  |  |  |

| t <sub>H</sub>     | LE register hold time after clock                                                                        |  |  |  |  |  |  |

| t <sub>PRE</sub>   | LE register preset delay                                                                                 |  |  |  |  |  |  |

| t <sub>CLR</sub>   | LE register clear delay                                                                                  |  |  |  |  |  |  |

Altera Corporation

| Symbol                | Parameter                                   |  |  |  |  |

|-----------------------|---------------------------------------------|--|--|--|--|

| t <sub>LABCASC</sub>  | Cascade delay between LEs in different LABs |  |  |  |  |

| t <sub>LABCARRY</sub> | Carry delay between LEs in different LABs   |  |  |  |  |

| t <sub>LOCAL</sub>    | LAB local interconnect delay                |  |  |  |  |

| t <sub>ROW</sub>      | Row interconnect routing delay (4)          |  |  |  |  |

| t <sub>COL</sub>      | Column interconnect routing delay           |  |  |  |  |

| t <sub>DIN_C</sub>    | Dedicated input to LE control delay         |  |  |  |  |

| t <sub>DIN_D</sub>    | Dedicated input to LE data delay (4)        |  |  |  |  |

| t <sub>DIN IO</sub>   | Dedicated input to IOE control delay        |  |  |  |  |

### Table 20. FLEX 8000 External Reference Timing Characteristics Note (5)

| Symbol           | Parameter                                                                                |

|------------------|------------------------------------------------------------------------------------------|

| t <sub>DRR</sub> | Register-to-register delay via 4 LEs, 3 row interconnects, and 4 local interconnects (6) |

| t <sub>ODH</sub> | Output data hold time after clock (7)                                                    |

Notes to tables:

- Internal timing parameters cannot be measured explicitly. They are worst-case delays based on testable and external parameters specified by Altera. Internal timing parameters should be used for estimating device performance. Post-compilation timing simulation or timing analysis is required to determine actual worst-case performance.

- (2) These values are specified in Table 10 on page 28 or Table 14 on page 29.

- (3) For the  $t_{OD3}$  and  $t_{ZX3}$  parameters,  $V_{CCIO} = 3.3$  V or 5.0 V.

- (4) The  $t_{ROW}$  and  $t_{DIN_D}$  delays are worst-case values for typical applications. Post-compilation timing simulation or timing analysis is required to determine actual worst-case performance.

- (5) External reference timing characteristics are factory-tested, worst-case values specified by Altera. A representative subset of signal paths is tested to approximate typical device applications.

- (6) For more information on test conditions, see Application Note 76 (Understanding FLEX 8000 Timing).

- (7) This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This parameter applies to global and non-global clocking, and for LE and I/O element registers.

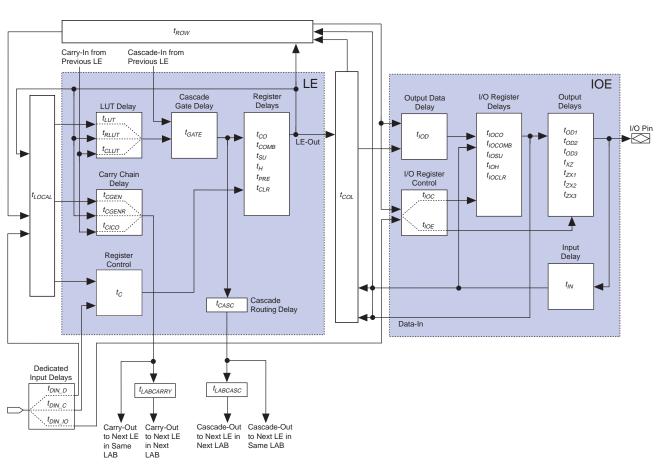

The FLEX 8000 timing model shows the delays for various paths and functions in the circuit. See Figure 19. This model contains three distinct parts: the LE; the IOE; and the interconnect, including the row and column FastTrack Interconnect, LAB local interconnect, and carry and cascade interconnect paths. Each parameter shown in Figure 19 is expressed as a worst-case value in Tables 22 through 49. Hand-calculations that use the FLEX 8000 timing model and these timing parameters can be used to estimate FLEX 8000 device performance. Timing simulation or timing analysis after compilation is required to determine the final worst-case performance. Table 21 summarizes the interconnect paths shown in Figure 19.

For more information on timing parameters, go to *Application Note 76* (*Understanding FLEX 8000 Timing*).

Altera Corporation

# Figure 19. FLEX 8000 Timing Model

| Symbol                |     |     | Speed | Grade |     |     | Unit |

|-----------------------|-----|-----|-------|-------|-----|-----|------|

|                       | A   | -2  | A     | -3    | Α   | -4  |      |

|                       | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>LABCASC</sub>  |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LABCARRY</sub> |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LOCAL</sub>    |     | 0.5 |       | 0.6   |     | 0.8 | ns   |

| t <sub>ROW</sub>      |     | 4.2 |       | 4.2   |     | 4.2 | ns   |

| t <sub>COL</sub>      |     | 2.5 |       | 2.5   |     | 2.5 | ns   |

| t <sub>DIN_C</sub>    |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

| t <sub>DIN_D</sub>    |     | 7.2 |       | 7.2   |     | 7.2 | ns   |

| t <sub>DIN IO</sub>   |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

| Symbol             | Speed Grade |     |     |     |     |     |    |  |  |

|--------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                    | A-2         |     | A-3 |     | A-4 |     |    |  |  |

|                    | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>LUT</sub>   |             | 2.0 |     | 2.3 |     | 3.0 | ns |  |  |

| t <sub>CLUT</sub>  |             | 0.0 |     | 0.2 |     | 0.1 | ns |  |  |

| t <sub>RLUT</sub>  |             | 0.9 |     | 1.6 |     | 1.6 | ns |  |  |

| t <sub>GATE</sub>  |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |  |

| t <sub>CASC</sub>  |             | 0.6 |     | 0.7 |     | 0.9 | ns |  |  |

| t <sub>CICO</sub>  |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>CGEN</sub>  |             | 0.4 |     | 0.9 |     | 0.8 | ns |  |  |

| t <sub>CGENR</sub> |             | 0.9 |     | 1.4 |     | 1.5 | ns |  |  |

| t <sub>C</sub>     |             | 1.6 |     | 1.8 |     | 2.4 | ns |  |  |

| t <sub>CH</sub>    | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |  |

| t <sub>CL</sub>    | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |  |

| t <sub>CO</sub>    |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>COMB</sub>  |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>SU</sub>    | 0.8         |     | 1.0 |     | 1.1 |     | ns |  |  |

| t <sub>H</sub>     | 0.9         |     | 1.1 |     | 1.4 |     | ns |  |  |

| t <sub>PRE</sub>   |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |  |

| t <sub>CLR</sub>   |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |  |

### Table 33. EPF8452A External Timing Parameters

| Symbol           |     | Speed Grade |     |      |     |      |    |  |  |  |

|------------------|-----|-------------|-----|------|-----|------|----|--|--|--|

|                  | A   | -2          | A   | -3   | A   | -4   |    |  |  |  |

|                  | Min | Max         | Min | Max  | Min | Мах  |    |  |  |  |

| t <sub>DRR</sub> |     | 16.0        |     | 20.0 |     | 25.0 | ns |  |  |  |

| t <sub>oDH</sub> | 1.0 |             | 1.0 |      | 1.0 |      | ns |  |  |  |

| Symbol             | Speed Grade |     |     |     |     |     |    |  |  |

|--------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                    | A           | -2  | A-3 |     | A-4 |     |    |  |  |

|                    | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>LUT</sub>   |             | 2.0 |     | 2.5 |     | 3.2 | ns |  |  |

| t <sub>CLUT</sub>  |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |  |

| t <sub>RLUT</sub>  |             | 0.9 |     | 1.1 |     | 1.5 | ns |  |  |

| t <sub>GATE</sub>  |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |  |

| t <sub>CASC</sub>  |             | 0.6 |     | 0.7 |     | 0.9 | ns |  |  |

| t <sub>CICO</sub>  |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>CGEN</sub>  |             | 0.4 |     | 0.5 |     | 0.7 | ns |  |  |

| t <sub>CGENR</sub> |             | 0.9 |     | 1.1 |     | 1.5 | ns |  |  |

| t <sub>C</sub>     |             | 1.6 |     | 2.0 |     | 2.5 | ns |  |  |

| t <sub>CH</sub>    | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |  |

| t <sub>CL</sub>    | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |  |

| t <sub>CO</sub>    |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>COMB</sub>  |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>SU</sub>    | 0.8         |     | 1.1 |     | 1.2 |     | ns |  |  |

| t <sub>H</sub>     | 0.9         |     | 1.1 |     | 1.5 |     | ns |  |  |

| t <sub>PRE</sub>   |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |  |

| t <sub>CLR</sub>   |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |  |

| Table 41. EPF8820A External Timing Parameters |     |             |     |      |     |      |    |  |  |  |

|-----------------------------------------------|-----|-------------|-----|------|-----|------|----|--|--|--|

| Symbol                                        |     | Speed Grade |     |      |     |      |    |  |  |  |

|                                               | A-2 |             | A-3 |      | A-4 |      |    |  |  |  |

|                                               | Min | Max         | Min | Max  | Min | Max  |    |  |  |  |

| t <sub>DRR</sub>                              |     | 16.0        |     | 20.0 |     | 25.0 | ns |  |  |  |

| t <sub>ODH</sub>                              | 1.0 |             | 1.0 |      | 1.0 |      | ns |  |  |  |

| Symbol              | Speed Grade |     |     |     |     |     |    |  |  |

|---------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                     | A-2         |     | A-3 |     | A-4 |     | 1  |  |  |

|                     | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>IOD</sub>    |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |  |

| t <sub>IOC</sub>    |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| t <sub>IOE</sub>    |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| t <sub>IOCO</sub>   |             | 1.0 |     | 1.0 |     | 1.0 | ns |  |  |

| t <sub>IOCOMB</sub> |             | 0.3 |     | 0.2 |     | 0.1 | ns |  |  |

| t <sub>IOSU</sub>   | 1.4         |     | 1.6 |     | 1.8 |     | ns |  |  |

| t <sub>IOH</sub>    | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |  |

| t <sub>IOCLR</sub>  |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |  |

| t <sub>IN</sub>     |             | 1.5 |     | 1.6 |     | 1.7 | ns |  |  |

| t <sub>OD1</sub>    |             | 1.1 |     | 1.4 |     | 1.7 | ns |  |  |

| t <sub>OD2</sub>    |             | 1.6 |     | 1.9 |     | 2.2 | ns |  |  |

| t <sub>OD3</sub>    |             | 4.6 |     | 4.9 |     | 5.2 | ns |  |  |

| t <sub>XZ</sub>     |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| t <sub>ZX1</sub>    |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| t <sub>ZX2</sub>    |             | 1.9 |     | 2.1 |     | 2.3 | ns |  |  |

| t <sub>ZX3</sub>    |             | 4.9 |     | 5.1 |     | 5.3 | ns |  |  |

| Symbol                |     |     | Speed | Grade |     |     | Unit |

|-----------------------|-----|-----|-------|-------|-----|-----|------|

|                       | A-2 |     | A-3   |       | A-4 |     |      |

|                       | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>LABCASC</sub>  |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LABCARRY</sub> |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LOCAL</sub>    |     | 0.5 |       | 0.6   |     | 0.8 | ns   |

| t <sub>ROW</sub>      |     | 6.2 |       | 6.2   |     | 6.2 | ns   |

| t <sub>COL</sub>      |     | 3.0 |       | 3.0   |     | 3.0 | ns   |

| t <sub>DIN_C</sub>    |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

| t <sub>DIN_D</sub>    |     | 8.2 |       | 8.2   |     | 8.7 | ns   |

| t <sub>DIN_IO</sub>   |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

ſ

1

| Symbol             | Speed Grade |     |     |     |     |     |    |  |  |

|--------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                    | A           | -2  | A-3 |     | A-4 |     | 1  |  |  |

|                    | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>LUT</sub>   |             | 2.0 |     | 2.5 |     | 3.2 | ns |  |  |

| t <sub>CLUT</sub>  |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |  |

| t <sub>RLUT</sub>  |             | 0.9 |     | 1.1 |     | 1.5 | ns |  |  |

| t <sub>GATE</sub>  |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |  |

| t <sub>CASC</sub>  |             | 0.6 |     | 0.7 |     | 0.9 | ns |  |  |

| t <sub>CICO</sub>  |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>CGEN</sub>  |             | 0.4 |     | 0.5 |     | 0.7 | ns |  |  |

| t <sub>CGENR</sub> |             | 0.9 |     | 1.1 |     | 1.5 | ns |  |  |

| t <sub>C</sub>     |             | 1.6 |     | 2.0 |     | 2.5 | ns |  |  |

| t <sub>CH</sub>    | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |  |

| t <sub>CL</sub>    | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |  |

| t <sub>CO</sub>    |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>COMB</sub>  |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |  |

| t <sub>SU</sub>    | 0.8         |     | 1.1 |     | 1.2 |     | ns |  |  |

| t <sub>H</sub>     | 0.9         |     | 1.1 |     | 1.5 |     | ns |  |  |

| t <sub>PRE</sub>   |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |  |

| t <sub>CLR</sub>   |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |  |

| Symbol           |     | Speed Grade |     |      |     |      |    |  |  |

|------------------|-----|-------------|-----|------|-----|------|----|--|--|

|                  | A   | -2          | A   | -3   | A   | -4   |    |  |  |

|                  | Min | Max         | Min | Max  | Min | Max  |    |  |  |

| t <sub>DRR</sub> |     | 16.1        |     | 20.1 |     | 25.1 | ns |  |  |

| t <sub>oDH</sub> | 1.0 |             | 1.0 |      | 1.0 |      | ns |  |  |

## Power Consumption

The supply power (P) for FLEX 8000 devices can be calculated with the following equation:

$P = P_{INT} + P_{IO} = [(I_{CCSTANDBY} + I_{CCACTIVE}) \times V_{CC}] + P_{IO}$

Typical I<sub>CCSTANDBY</sub> values are shown as I<sub>CC0</sub> in Table 11 on page 28 and Table 15 on page 30. The P<sub>IO</sub> value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note* 74 (*Evaluating Power for Altera Devices*). The I<sub>CCACTIVE</sub> value depends on the switching frequency and the application logic. This value can be calculated based on the amount of current that each LE typically consumes.

The following equation shows the general formula for calculating  $I_{\mbox{\scriptsize CCACTIVE}}$ :

$$I_{CCACTIVE} = K \times f_{MAX} \times N \times tog_{LC} \times \frac{\mu A}{MHz \times LE}$$

The parameters in this equation are shown below:

| f <sub>MAX</sub>  | = | Maximum operating frequency in MHz                       |

|-------------------|---|----------------------------------------------------------|

| Ν                 | = | Total number of logic cells used in the device           |

| tog <sub>LC</sub> | = | Average percentage of logic cells toggling at each clock |

| Κ                 | = | Constant, shown in Table 50                              |

|                   |   |                                                          |

| Table 50. Values for Constant K |    |  |  |  |

|---------------------------------|----|--|--|--|

| Device                          | к  |  |  |  |

| 5.0-V FLEX 8000 devices         | 75 |  |  |  |

| 3.3-V FLEX 8000 devices         | 60 |  |  |  |

This calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  value should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

Figure 20 shows the relationship between  $\rm I_{\rm CC}$  and operating frequency for several LE utilization values.

### **Operating Modes**

The FLEX 8000 architecture uses SRAM elements that require configuration data to be loaded whenever the device powers up and begins operation. The process of physically loading the SRAM programming data into the device is called *configuration*. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. The configuration and initialization processes together are called *command mode*; normal device operation is called *user mode*.

SRAM elements allow FLEX 8000 devices to be reconfigured in-circuit with new programming data that is loaded into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different programming data, reinitializing the device, and resuming user-mode operation. The entire reconfiguration process requires less than 100 ms and can be used to dynamically reconfigure an entire system. In-field upgrades can be performed by distributing new configuration files.

### **Configuration Schemes**

The configuration data for a FLEX 8000 device can be loaded with one of six configuration schemes, chosen on the basis of the target application. Both active and passive schemes are available. In the active configuration schemes, the FLEX 8000 device functions as the controller, directing the loading operation, controlling external configuration devices, and completing the loading process. The clock source for all active configuration schemes is an oscillator on the FLEX 8000 device that operates between 2 MHz and 6 MHz. In the passive configuration schemes, an external controller guides the FLEX 8000 device. Table 51 shows the data source for each of the six configuration schemes.

| Table 51. Data Source for Configura | Table 51. Data Source for Configuration |                               |  |  |  |  |  |  |  |  |

|-------------------------------------|-----------------------------------------|-------------------------------|--|--|--|--|--|--|--|--|

| Configuration Scheme                | Acronym                                 | Data Source                   |  |  |  |  |  |  |  |  |

| Active serial                       | AS                                      | Altera configuration device   |  |  |  |  |  |  |  |  |

| Active parallel up                  | APU                                     | Parallel configuration device |  |  |  |  |  |  |  |  |

| Active parallel down                | APD                                     | Parallel configuration device |  |  |  |  |  |  |  |  |

| Passive serial                      | PS                                      | Serial data path              |  |  |  |  |  |  |  |  |

| Passive parallel synchronous        | PPS                                     | Intelligent host              |  |  |  |  |  |  |  |  |

| Passive parallel asynchronous       | PPA                                     | Intelligent host              |  |  |  |  |  |  |  |  |

| Table 52. FLEX 8000 84-, 100-, 144- & 160-Pin Package Pin-Outs (Part 2 of 3) |                            |                                        |                                          |                             |                                            |                                                                                           |                                                         |

|------------------------------------------------------------------------------|----------------------------|----------------------------------------|------------------------------------------|-----------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Pin Name                                                                     | 84-Pin<br>PLCC<br>EPF8282A | 84-Pin<br>PLCC<br>EPF8452A<br>EPF8636A | 100-Pin<br>TQFP<br>EPF8282A<br>EPF8282AV | 100-Pin<br>TQFP<br>EPF8452A | 144-Pin<br>TQFP<br>EPF8820A                | 160-Pin<br>PGA<br>EPF8452A                                                                | 160-Pin<br>PQFP<br>EPF8820A<br>(1)                      |

| ADD0                                                                         | 78                         | 76                                     | 78                                       | 77                          | 106                                        | N3                                                                                        | 6                                                       |

| data7                                                                        | 3                          | 2                                      | 90                                       | 89                          | 131                                        | P8                                                                                        | 140                                                     |

| DATA6                                                                        | 4                          | 4                                      | 91                                       | 91                          | 132                                        | P10                                                                                       | 139                                                     |

| DATA5                                                                        | 6                          | 6                                      | 92                                       | 95                          | 133                                        | R12                                                                                       | 138                                                     |

| DATA4                                                                        | 7                          | 7                                      | 95                                       | 96                          | 134                                        | R13                                                                                       | 136                                                     |

| DATA3                                                                        | 8                          | 8                                      | 97                                       | 97                          | 135                                        | P13                                                                                       | 135                                                     |

| DATA2                                                                        | 9                          | 9                                      | 99                                       | 98                          | 137                                        | R14                                                                                       | 133                                                     |

| DATA1                                                                        | 13                         | 13                                     | 4                                        | 4                           | 138                                        | N15                                                                                       | 132                                                     |

| DATA0                                                                        | 14                         | 14                                     | 5                                        | 5                           | 140                                        | K13                                                                                       | 129                                                     |

| SDOUT (3)                                                                    | 79                         | 78                                     | 79                                       | 79                          | 23                                         | P4                                                                                        | 97                                                      |

| TDI (4)                                                                      | 55                         | 45 (5)                                 | 54                                       | -                           | 96                                         | -                                                                                         | 17                                                      |

| TDO (4)                                                                      | 27                         | 27 (5)                                 | 18                                       | -                           | 18                                         | -                                                                                         | 102                                                     |

| TCK (4), (6)                                                                 | 72                         | 44 (5)                                 | 72                                       | -                           | 88                                         | _                                                                                         | 27                                                      |

| TMS (4)                                                                      | 20                         | 43 (5)                                 | 11                                       | -                           | 86                                         | -                                                                                         | 29                                                      |

| TRST (7)                                                                     | 52                         | 52 (8)                                 | 50                                       | -                           | 71                                         | -                                                                                         | 45                                                      |

| Dedicated<br>Inputs (10)                                                     | 12, 31, 54,<br>73          | 12, 31, 54,<br>73                      | 3, 23, 53, 73                            | 3, 24, 53,<br>74            | 9, 26, 82,<br>99                           | C3, D14,<br>N2, R15                                                                       | 14, 33, 94,<br>113                                      |

| VCCINT                                                                       | 17, 38, 59,<br>80          | 17, 38, 59,<br>80                      | 6, 20, 37, 56,<br>70, 87                 | 9, 32, 49,<br>59, 82        | 8, 28, 70,<br>90, 111                      | B2, C4, D3,<br>D8, D12,<br>G3, G12,<br>H4, H13,<br>J3, J12,<br>M4, M7,<br>M9, M13,<br>N12 | 3, 24, 46,<br>92, 114,<br>160                           |

| VCCIO                                                                        | -                          | -                                      | -                                        | -                           | 16, 40, 60,<br>69, 91,<br>112, 122,<br>141 | -                                                                                         | 23, 47, 57,<br>69, 79,<br>104, 127,<br>137, 149,<br>159 |

Г

| Pin Name                | 160-Pin<br>PQFP<br>EPF8452A | 160-Pin<br>PQFP<br>EPF8636A | 192-Pin PGA<br>EPF8636A<br>EPF8820A | 208-Pin<br>PQFP<br>EPF8636A (1) | 208-Pin<br>PQFP<br>EPF8820A (1) | 208-Pin<br>PQFP<br>EPF81188A <i>(1)</i> |

|-------------------------|-----------------------------|-----------------------------|-------------------------------------|---------------------------------|---------------------------------|-----------------------------------------|

| nSP (2)                 | 120                         | 1                           | R15                                 | 207                             | 207                             | 5                                       |

| MSEL0 (2)               | 117                         | 3                           | T15                                 | 4                               | 4                               | 3<br>21                                 |

| MSELU (2)<br>MSEL1 (2)  | 84                          | 38                          | T3                                  | 49                              | 49                              | 33                                      |

| nSTATUS (2)             | 37                          | 83                          | B3                                  | 108                             | 108                             | 124                                     |

| . ,                     | 40                          | 81                          | C3                                  | 103                             | 103                             | 107                                     |

| nCONFIG (2)<br>DCLK (2) | 1                           | 120                         | C15                                 | 158                             | 158                             | 154                                     |

|                         | 4                           |                             |                                     |                                 |                                 | 134                                     |

| CONF_DONE (2)           | 4                           | 118                         | B15                                 | 153                             | 153                             | 138                                     |

| nWS                     | 30                          | 89                          | C5                                  | 114                             | 114                             | 118                                     |

| nRS                     | 71                          | 50                          | B5                                  | 66                              | 116                             | 121                                     |

| RDCLK                   | 73                          | 48                          | C11                                 | 64                              | 137                             | 137                                     |

| nCS                     | 29                          | 91                          | B13                                 | 116                             | 145                             | 142                                     |

| CS                      | 27                          | 93                          | A16                                 | 118                             | 148                             | 144                                     |

| RDYnBUSY                | 125                         | 155                         | A8                                  | 201                             | 127                             | 128                                     |

| CLKUSR                  | 76                          | 44                          | A10                                 | 59                              | 134                             | 134                                     |

| ADD17                   | 78                          | 43                          | R5                                  | 57                              | 43                              | 46                                      |

| ADD16                   | 91                          | 33                          | U3                                  | 43                              | 42                              | 45                                      |

| ADD15                   | 92                          | 31                          | T5                                  | 41                              | 41                              | 44                                      |

| ADD14                   | 94                          | 29                          | U4                                  | 39                              | 40                              | 39                                      |

| ADD13                   | 95                          | 27                          | R6                                  | 37                              | 39                              | 37                                      |

| ADD12                   | 96                          | 24                          | Т6                                  | 31                              | 35                              | 36                                      |

| ADD11                   | 97                          | 23                          | R7                                  | 30                              | 33                              | 31                                      |

| ADD10                   | 98                          | 22                          | T7                                  | 29                              | 31                              | 30                                      |

| ADD9                    | 99                          | 21                          | Т8                                  | 28                              | 29                              | 29                                      |

| ADD8                    | 101                         | 20                          | U9                                  | 24                              | 25                              | 26                                      |

| ADD7                    | 102                         | 19                          | U10                                 | 23                              | 23                              | 25                                      |

| ADD6                    | 103                         | 18                          | U11                                 | 22                              | 21                              | 24                                      |

| ADD5                    | 104                         | 17                          | U12                                 | 21                              | 19                              | 18                                      |

| ADD4                    | 105                         | 13                          | R12                                 | 14                              | 14                              | 17                                      |

| ADD3                    | 106                         | 11                          | U14                                 | 12                              | 13                              | 16                                      |

| ADD2                    | 109                         | 9                           | U15                                 | 10                              | 11                              | 10                                      |

| ADD1                    | 110                         | 7                           | R13                                 | 8                               | 10                              | 9                                       |

| ADD0                    | 123                         | 157                         | U16                                 | 203                             | 9                               | 8                                       |

| DATA7                   | 144                         | 137                         | H17                                 | 178                             | 178                             | 177                                     |

| DATA6                   | 150                         | 132                         | G17                                 | 172                             | 176                             | 175                                     |

| DATA5                   | 152                         | 129                         | F17                                 | 169                             | 174                             | 172                                     |

Altera Corporation

| Pin Name                     | 160-Pin<br>PQFP<br>EPF8452A                                  | 160-Pin<br>PQFP<br>EPF8636A                                                | 192-Pin PGA<br>EPF8636A<br>EPF8820A                                                               | 208-Pin<br>PQFP<br>EPF8636A (1)                                                                                                                                                                                 | 208-Pin<br>PQFP<br>EPF8820A (1)                    | 208-Pin<br>PQFP<br>EPF81188A (1)                             |

|------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------|

| DATA4                        | 154                                                          | 127                                                                        | E17                                                                                               | 165                                                                                                                                                                                                             | 172                                                | 170                                                          |

| DATA3                        | 157                                                          | 124                                                                        | G15                                                                                               | 162                                                                                                                                                                                                             | 171                                                | 168                                                          |

| DATA2                        | 159                                                          | 122                                                                        | F15                                                                                               | 160                                                                                                                                                                                                             | 167                                                | 166                                                          |

| DATA1                        | 11                                                           | 115                                                                        | E16                                                                                               | 149                                                                                                                                                                                                             | 165                                                | 163                                                          |

| DATA0                        | 12                                                           | 113                                                                        | C16                                                                                               | 147                                                                                                                                                                                                             | 162                                                | 161                                                          |

| SDOUT (3)                    | 128                                                          | 152                                                                        | C7 (11)                                                                                           | 198                                                                                                                                                                                                             | 124                                                | 119                                                          |

| TDI <i>(4)</i>               | _                                                            | 55                                                                         | R11                                                                                               | 72                                                                                                                                                                                                              | 20                                                 | -                                                            |

| TDO <i>(4)</i>               | _                                                            | 95                                                                         | B9                                                                                                | 120                                                                                                                                                                                                             | 129                                                | -                                                            |

| TCK (4), (6)                 | _                                                            | 57                                                                         | U8                                                                                                | 74                                                                                                                                                                                                              | 30                                                 | -                                                            |

| TMS (4)                      | _                                                            | 59                                                                         | U7                                                                                                | 76                                                                                                                                                                                                              | 32                                                 | -                                                            |

| trst (7)                     | _                                                            | 40                                                                         | R3                                                                                                | 54                                                                                                                                                                                                              | 54                                                 | -                                                            |

| Dedicated<br>Inputs (10)     | 5, 36, 85, 116                                               | 6, 35, 87, 116                                                             | A5, U5, U13,<br>A13                                                                               | 7, 45, 112,<br>150                                                                                                                                                                                              | 17, 36, 121,<br>140                                | 13, 41, 116,<br>146                                          |

| VCCINT<br>(5.0 V)            | 21, 41, 53, 67,<br>80, 81, 100, 121,<br>133, 147, 160        | 4, 5, 26, 85,<br>106                                                       | C8, C9, C10,<br>R8, R9, R10,<br>R14                                                               | 5, 6, 33, 110,<br>137                                                                                                                                                                                           | 5, 6, 27, 48,<br>119, 141                          | 4, 20, 35, 48,<br>50, 102, 114,<br>131, 147                  |

| VCCIO<br>(5.0 V or<br>3.3 V) | _                                                            | 25, 41, 60, 70,<br>80, 107, 121,<br>140, 149, 160                          | D3, D4, D9,<br>D14, D15, G4,<br>G14, L4, L14,<br>P4, P9, P14                                      | 32, 55, 78, 91,<br>102, 138, 159,<br>182, 193, 206                                                                                                                                                              | 26, 55, 69, 87,<br>102, 131, 159,<br>173, 191, 206 | 3, 19, 34, 49,<br>69, 87, 106,<br>123, 140, 156,<br>174, 192 |

| GND                          | 13, 14, 28, 46,<br>60, 75, 93, 107,<br>108, 126, 140,<br>155 | 15, 16, 36, 37,<br>45, 51, 75, 84,<br>86, 96, 97,<br>117, 126, 131,<br>154 | C4, D7, D8,<br>D10, D11, H4,<br>H14, K4, K14,<br>P7, P8, P10,<br>P11                              | 19, 20, 46, 47,<br>60, 67, 96,<br>109, 111, 124,<br>125, 151, 164,<br>171, 200                                                                                                                                  |                                                    | 42, 43, 60, 78,<br>96, 105, 115,<br>122, 132, 139,           |

| No Connect<br>(N.C.)         | 2, 3, 38, 39, 70,<br>82, 83, 118, 119,<br>148                | 2, 39, 82, 119                                                             | C6, C12, C13,<br>C14, E3, E15,<br>F3, J3, J4,<br>J14, J15, N3,<br>N15, P3, P15,<br>R4 <i>(12)</i> | $\begin{array}{c} 1, 2, 3, 16, 17, \\ 18, 25, 26, 27, \\ 34, 35, 36, 50, \\ 51, 52, 53, \\ 104, 105, 106, \\ 107, 121, 122, \\ 123, 130, 131, \\ 132, 139, 140, \\ 141, 154, 155, \\ 156, 157, 208 \end{array}$ | 154, 155, 156,                                     | 1, 2, 51, 52, 53,<br>54, 103, 104,<br>157, 158, 207,<br>208  |

| Total User<br>I/O Pins (9)   | 116                                                          | 114                                                                        | 132, 148 (13)                                                                                     | 132                                                                                                                                                                                                             | 148                                                | 144                                                          |