Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 42                                                        |

| Number of Logic Elements/Cells | 336                                                       |

| Total RAM Bits                 | -                                                         |

| Number of I/O                  | 68                                                        |

| Number of Gates                | 4000                                                      |

| Voltage - Supply               | 4.75V ~ 5.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                           |

| Package / Case                 | 84-LCC (J-Lead)                                           |

| Supplier Device Package        | 84-PLCC (29.31x29.31)                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf8452alc84-4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 1 shows a block diagram of the FLEX 8000 architecture. Each group of eight LEs is combined into an LAB; LABs are arranged into rows and columns. The I/O pins are supported by I/O elements (IOEs) located at the ends of rows and columns. Each IOE contains a bidirectional I/O buffer and a flipflop that can be used as either an input or output register.

Figure 1. FLEX 8000 Device Block Diagram

Signal interconnections within FLEX 8000 devices and between device pins are provided by the FastTrack Interconnect, a series of fast, continuous channels that run the entire length and width of the device. IOEs are located at the end of each row (horizontal) and column (vertical) FastTrack Interconnect path.

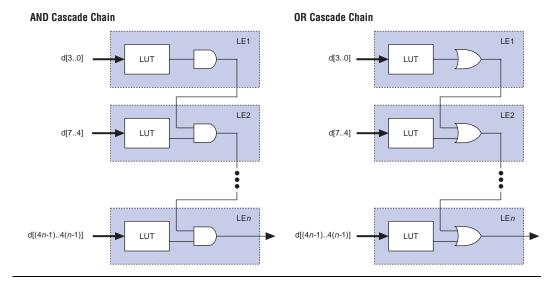

The FLEX 8000 architecture provides two dedicated high-speed data paths—carry chains and cascade chains—that connect adjacent LEs without using local interconnect paths. The carry chain supports high-speed counters and adders; the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in an LAB and all LABs in the same row. Heavy use of carry and cascade chains can reduce routing flexibility. Therefore, the use of carry and cascade chains should be limited to speed-critical portions of a design.

#### Carry Chain

The carry chain provides a very fast (less than 1 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit moves forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 8000 architecture to implement high-speed counters and adders of arbitrary width. The MAX+PLUS II Compiler can create carry chains automatically during design processing; designers can also insert carry chain logic manually during design entry.

Figure 4 shows how an n-bit full adder can be implemented in n+1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register is typically bypassed for simple adders, but can be used for an accumulator function. Another portion of the LUT and the carry chain logic generate the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to another LE, where it can be used as a general-purpose signal. In addition to mathematical functions, carry chain logic supports very fast counters and comparators.

The MAX+PLUS II Compiler can create cascade chains automatically during design processing; designers can also insert cascade chain logic manually during design entry. Cascade chains longer than eight LEs are automatically implemented by linking LABs together. The last LE of an LAB cascades to the first LE of the next LAB.

Figure 5 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. These examples show functions of 4n variables implemented with n LEs. For a device with an A-2 speed grade, the LE delay is 2.4 ns; the cascade chain delay is 0.6 ns. With the cascade chain, 4.2 ns is needed to decode a 16-bit address.

Figure 5. FLEX 8000 Cascade Chain Operation

#### LE Operating Modes

The FLEX 8000 LE can operate in one of four modes, each of which uses LE resources differently. See Figure 6. In each mode, seven of the ten available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. The three remaining inputs to the LE provide clock, clear, and preset control for the register. The MAX+PLUS II software automatically chooses the appropriate mode for each application. Design performance can also be enhanced by designing for the operating mode that supports the desired application.

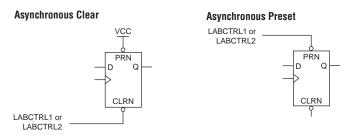

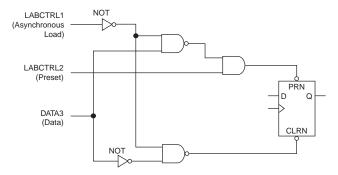

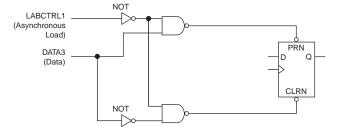

Figure 7. FLEX 8000 LE Asynchronous Clear & Preset Modes

# Asynchronous Clear & Preset LABCTRL1 PRN

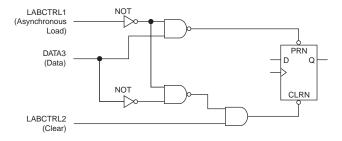

#### **Asynchronous Load with Clear**

#### **Asynchronous Load with Preset**

#### **Asynchronous Load without Clear or Preset**

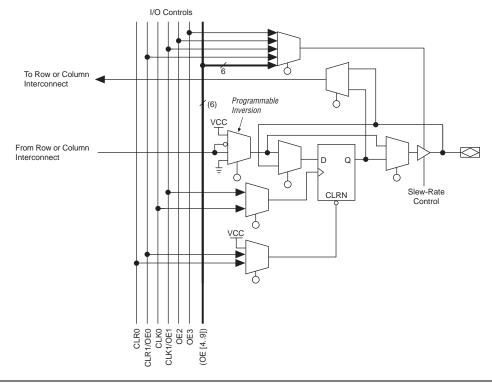

#### Figure 10. FLEX 8000 IOE

Numbers in parentheses are for EPF81500A devices only.

#### Row-to-IOE Connections

Figure 11 illustrates the connection between row interconnect channels and IOEs. An input signal from an IOE can drive two separate row channels. When an IOE is used as an output, the signal is driven by an *n*-to-1 multiplexer that selects the row channels. The size of the multiplexer varies with the number of columns in a device. EPF81500A devices use a 27-to-1 multiplexer; EPF81188A, EPF8820A, EPF8636A, and EPF8452A devices use a 21-to-1 multiplexer; and EPF8282A and EPF8282AV devices use a 13-to-1 multiplexer. Eight IOEs are connected to each side of the row channels.

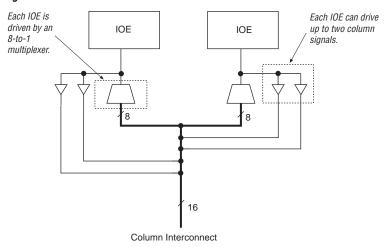

Figure 12. FLEX 8000 Column-to-IOE Connections

In addition to general-purpose I/O pins, FLEX 8000 devices have four dedicated input pins. These dedicated inputs provide low-skew, device-wide signal distribution, and are typically used for global clock, clear, and preset control signals. The signals from the dedicated inputs are available as control signals for all LABs and I/O elements in the device. The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device.

Signals enter the FLEX 8000 device either from the I/O pins that provide general-purpose input capability or from the four dedicated inputs. The IOEs are located at the ends of the row and column interconnect channels.

I/O pins can be used as input, output, or bidirectional pins. Each I/O pin has a register that can be used either as an input register for external data that requires fast setup times, or as an output register for data that requires fast clock-to-output performance. The MAX+PLUS II Compiler uses the programmable inversion option to invert signals automatically from the row and column interconnect when appropriate.

The clock, clear, and output enable controls for the IOEs are provided by a network of I/O control signals. These signals can be supplied by either the dedicated input pins or by internal logic. The IOE control-signal paths are designed to minimize the skew across the device. All control-signal sources are buffered onto high-speed drivers that drive the signals around the periphery of the device. This "peripheral bus" can be configured to provide up to four output enable signals (10 in EPF81500A devices), and up to two clock or clear signals. Figure 13 on page 22 shows how two output enable signals are shared with one clock and one clear signal.

The instruction register length for FLEX 8000 devices is three bits. Table 7 shows the boundary-scan register length for FLEX 8000 devices.

| Table 7. FLEX 8000 Boundary-Scan Register Length |     |  |  |

|--------------------------------------------------|-----|--|--|

| Device Boundary-Scan Register Length             |     |  |  |

| EPF8282A, EPF8282AV                              | 273 |  |  |

| EPF8636A                                         | 417 |  |  |

| EPF8820A                                         | 465 |  |  |

| EPF81500A                                        | 645 |  |  |

FLEX 8000 devices that support JTAG include weak pull-ups on the JTAG pins. Figure 14 shows the timing requirements for the JTAG signals.

TDI

TCK

t<sub>JCP</sub>

t<sub>JCL</sub>

t<sub>JPSU</sub>

t<sub>JPSU</sub>

t<sub>JPNZ</sub>

TDO

Signal to Be Captured

Signal to Be Driven

Figure 14. EPF8282A, EPF8282AV, EPF8636A, EPF8820A & EPF81500A JTAG Waveforms

Table 8 shows the timing parameters and values for EPF8282A, EPF8282AV, EPF8636A, EPF8820A, and EPF81500A devices.

| Table 8. JTAG Timing Parameters & Values |                                                |                                                            |     |      |

|------------------------------------------|------------------------------------------------|------------------------------------------------------------|-----|------|

| Symbol                                   | Parameter                                      | EPF8282A<br>EPF8282AV<br>EPF8636A<br>EPF8820A<br>EPF81500A |     | Unit |

|                                          |                                                | Min                                                        | Max |      |

| t <sub>JCP</sub>                         | TCK clock period                               | 100                                                        |     | ns   |

| t <sub>JCH</sub>                         | TCK clock high time                            | 50                                                         |     | ns   |

| t <sub>JCL</sub>                         | TCK clock low time                             | 50                                                         |     | ns   |

| t <sub>JPSU</sub>                        | JTAG port setup time                           | 20                                                         |     | ns   |

| t <sub>JPH</sub>                         | JTAG port hold time                            | 45                                                         |     | ns   |

| t <sub>JPCO</sub>                        | JTAG port clock to output                      |                                                            | 25  | ns   |

| t <sub>JPZX</sub>                        | JTAG port high-impedance to valid output       |                                                            | 25  | ns   |

| t <sub>JPXZ</sub>                        | JTAG port valid output to high-impedance       |                                                            | 25  | ns   |

| t <sub>JSSU</sub>                        | Capture register setup time                    | 20                                                         |     | ns   |

| t <sub>JSH</sub>                         | Capture register hold time                     | 45                                                         |     | ns   |

| t <sub>JSCO</sub>                        | Update register clock to output                |                                                            | 35  | ns   |

| t <sub>JSZX</sub>                        | Update register high-impedance to valid output |                                                            | 35  | ns   |

| t <sub>JSXZ</sub>                        | Update register valid output to high-impedance |                                                            | 35  | ns   |

For detailed information on JTAG operation in FLEX 8000 devices, refer to *Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices*).

### **Generic Testing**

Each FLEX 8000 device is functionally tested and specified by Altera. Complete testing of each configurable SRAM bit and all logic functionality ensures 100% configuration yield. AC test measurements for FLEX 8000 devices are made under conditions equivalent to those shown in Figure 15. Designers can use multiple test patterns to configure devices during all stages of the production flow.

| Symbol             | Parameter                                           | Conditions         | Min         | Max                      | Unit |

|--------------------|-----------------------------------------------------|--------------------|-------------|--------------------------|------|

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 5.0-V operation  | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | V    |

|                    | Supply voltage for output buffers, 3.3-V operation  | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)              | V    |

| V <sub>I</sub>     | Input voltage                                       |                    | -0.5        | V <sub>CCINT</sub> + 0.5 | V    |

| Vo                 | Output voltage                                      |                    | 0           | V <sub>CCIO</sub>        | V    |

| T <sub>A</sub>     | Operating temperature                               | For commercial use | 0           | 70                       | °C   |

|                    |                                                     | For industrial use | -40         | 85                       | °C   |

| t <sub>R</sub>     | Input rise time                                     |                    |             | 40                       | ns   |

| t <sub>F</sub>     | Input fall time                                     |                    |             | 40                       | ns   |

| Table 1          | Table 11. FLEX 8000 5.0-V Device DC Operating ConditionsNotes (5), (6) |                                                                   |                         |     |                          |      |

|------------------|------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|-----|--------------------------|------|

| Symbol           | Parameter                                                              | Conditions                                                        | Min                     | Тур | Max                      | Unit |

| $V_{IH}$         | High-level input voltage                                               |                                                                   | 2.0                     |     | V <sub>CCINT</sub> + 0.5 | V    |

| V <sub>IL</sub>  | Low-level input voltage                                                |                                                                   | -0.5                    |     | 0.8                      | V    |

| V <sub>OH</sub>  | 5.0-V high-level TTL output voltage                                    | $I_{OH} = -4 \text{ mA DC } (7)$<br>$V_{CCIO} = 4.75 \text{ V}$   | 2.4                     |     |                          | V    |

|                  | 3.3-V high-level TTL output voltage                                    | $I_{OH} = -4 \text{ mA DC } (7)$<br>$V_{CCIO} = 3.00 \text{ V}$   | 2.4                     |     |                          | V    |

|                  | 3.3-V high-level CMOS output voltage                                   | $I_{OH} = -0.1 \text{ mA DC } (7)$<br>$V_{CCIO} = 3.00 \text{ V}$ | V <sub>CCIO</sub> – 0.2 |     |                          | V    |

| V <sub>OL</sub>  | 5.0-V low-level TTL output voltage                                     | I <sub>OL</sub> = 12 mA DC (7)<br>V <sub>CCIO</sub> = 4.75 V      |                         |     | 0.45                     | V    |

|                  | 3.3-V low-level TTL output voltage                                     | I <sub>OL</sub> = 12 mA DC (7)<br>V <sub>CCIO</sub> = 3.00 V      |                         |     | 0.45                     | V    |

|                  | 3.3-V low-level CMOS output voltage                                    | I <sub>OL</sub> = 0.1 mA DC (7)<br>V <sub>CCIO</sub> = 3.00 V     |                         |     | 0.2                      | V    |

| I <sub>I</sub>   | Input leakage current                                                  | $V_I = V_{CC}$ or ground                                          | -10                     |     | 10                       | μΑ   |

| I <sub>OZ</sub>  | Tri-state output off-state current                                     | $V_O = V_{CC}$ or ground                                          | -40                     |     | 40                       | μA   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby)                               | V <sub>I</sub> = ground, no load                                  |                         | 0.5 | 10                       | mA   |

| Table 1          | Table 12. FLEX 8000 5.0-V Device Capacitance Note (8) |                                     |  |      |    |

|------------------|-------------------------------------------------------|-------------------------------------|--|------|----|

| Symbol           | Parameter                                             | Conditions Min Max                  |  | Unit |    |

| C <sub>IN</sub>  | Input capacitance                                     | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |  | 10   | pF |

| C <sub>OUT</sub> | Output capacitance                                    | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |  | 10   | pF |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 7.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) The maximum V<sub>CC</sub> rise time is 100 ms.

- (4) Numbers in parentheses are for industrial-temperature-range devices.

- (5) Typical values are for  $T_A = 25^{\circ} \text{ C}$  and  $V_{CC} = 5.0 \text{ V}$ .

- (6) These values are specified in Table 10 on page 28.

- (7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current; the I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current.

- (8) Capacitance is sample-tested only.

Tables 13 through 16 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for 3.3-V FLEX 8000 devices.

| Table 1          | Table 13. FLEX 8000 3.3-V Device Absolute Maximum Ratings   Note (1) |                              |      |     |      |  |

|------------------|----------------------------------------------------------------------|------------------------------|------|-----|------|--|

| Symbol           | Parameter                                                            | Conditions                   | Min  | Max | Unit |  |

| V <sub>CC</sub>  | Supply voltage                                                       | With respect to ground (2)   | -2.0 | 5.3 | V    |  |

| V <sub>I</sub>   | DC input voltage                                                     |                              | -2.0 | 5.3 | V    |  |

| I <sub>OUT</sub> | DC output current, per pin                                           |                              | -25  | 25  | mA   |  |

| T <sub>STG</sub> | Storage temperature                                                  | No bias                      | -65  | 150 | ° C  |  |

| $T_{AMB}$        | Ambient temperature                                                  | Under bias                   | -65  | 135 | ° C  |  |

| $T_{J}$          | Junction temperature                                                 | Plastic packages, under bias |      | 135 | ° C  |  |

| Table 1         | Table 14. FLEX 8000 3.3-V Device Recommended Operating Conditions |                    |      |                       |      |  |

|-----------------|-------------------------------------------------------------------|--------------------|------|-----------------------|------|--|

| Symbol          | Parameter                                                         | Conditions         | Min  | Max                   | Unit |  |

| V <sub>CC</sub> | Supply voltage                                                    | (3)                | 3.0  | 3.6                   | V    |  |

| VI              | Input voltage                                                     |                    | -0.3 | V <sub>CC</sub> + 0.3 | V    |  |

| Vo              | Output voltage                                                    |                    | 0    | V <sub>CC</sub>       | V    |  |

| T <sub>A</sub>  | Operating temperature                                             | For commercial use | 0    | 70                    | ° C  |  |

| t <sub>R</sub>  | Input rise time                                                   |                    |      | 40                    | ns   |  |

| t <sub>F</sub>  | Input fall time                                                   |                    |      | 40                    | ns   |  |

| Table 1          | Table 15. FLEX 8000 3.3-V Device DC Operating Conditions       Note (4) |                                      |                       |     |                       |    |

|------------------|-------------------------------------------------------------------------|--------------------------------------|-----------------------|-----|-----------------------|----|

| Symbol           | ol Parameter Conditions Min Typ Max Ur                                  |                                      |                       |     |                       |    |

| V <sub>IH</sub>  | High-level input voltage                                                |                                      | 2.0                   |     | V <sub>CC</sub> + 0.3 | V  |

| $V_{IL}$         | Low-level input voltage                                                 |                                      | -0.3                  |     | 0.8                   | V  |

| $V_{OH}$         | High-level output voltage                                               | $I_{OH} = -0.1 \text{ mA DC } (5)$   | V <sub>CC</sub> - 0.2 |     |                       | V  |

| $V_{OL}$         | Low-level output voltage                                                | I <sub>OL</sub> = 4 mA DC (5)        |                       |     | 0.45                  | V  |

| I <sub>I</sub>   | Input leakage current                                                   | $V_I = V_{CC}$ or ground             | -10                   |     | 10                    | μΑ |

| $I_{OZ}$         | Tri-state output off-state current                                      | $V_O = V_{CC}$ or ground             | -40                   |     | 40                    | μΑ |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby)                                | V <sub>I</sub> = ground, no load (6) |                       | 0.3 | 10                    | mA |

| Table 1          | Table 16. FLEX 8000 3.3-V Device Capacitance Note (7) |                                     |  |      |    |

|------------------|-------------------------------------------------------|-------------------------------------|--|------|----|

| Symbol           | Parameter                                             | Conditions Min Max                  |  | Unit |    |

| C <sub>IN</sub>  | Input capacitance                                     | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |  | 10   | pF |

| C <sub>OUT</sub> | Output capacitance                                    | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |  | 10   | pF |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is –0.3 V. During transitions, the inputs may undershoot to –2.0 V or overshoot to 5.3 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) The maximum  $V_{CC}$  rise time is 100 ms.  $V_{CC}$  must rise monotonically.

- (4) These values are specified in Table 14 on page 29.

- (5) The I<sub>OH</sub> parameter refers to high-level TTL output current; the I<sub>OL</sub> parameter refers to low-level TTL output current.

- (6) Typical values are for  $T_A = 25^{\circ}$  C and  $V_{CC} = 3.3$  V.

- (7) Capacitance is sample-tested only.

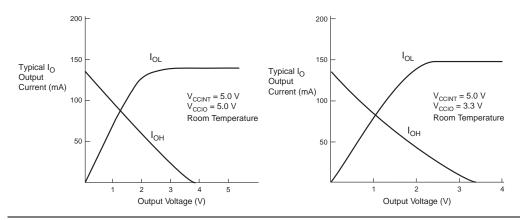

Figure 16 shows the typical output drive characteristics of 5.0-V FLEX 8000 devices. The output driver is compliant with *PCI Local Bus Specification, Revision 2.2*.

Figure 16. Output Drive Characteristics of 5.0-V FLEX 8000 Devices (Except EPF8282A)

Figure 17 shows the typical output drive characteristics of 5.0-V EPF8282A devices. The output driver is compliant with *PCI Local Bus Specification, Revision* 2.2.

Figure 17. Output Drive Characteristics of EPF8282A Devices with 5.0-V V<sub>CCIO</sub>

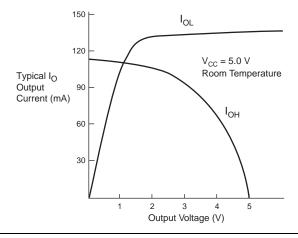

Figure 18 shows the typical output drive characteristics of EPF8282AV devices.

| Table 19. FLEX 8000 Interconnect Timing Parameters Note (1) |                                             |  |

|-------------------------------------------------------------|---------------------------------------------|--|

| Symbol                                                      | Parameter                                   |  |

| t <sub>LABCASC</sub>                                        | Cascade delay between LEs in different LABs |  |

| t <sub>LABCARRY</sub>                                       | Carry delay between LEs in different LABs   |  |

| t <sub>LOCAL</sub>                                          | LAB local interconnect delay                |  |

| t <sub>ROW</sub>                                            | Row interconnect routing delay (4)          |  |

| $t_{COL}$                                                   | Column interconnect routing delay           |  |

| t <sub>DIN_C</sub>                                          | Dedicated input to LE control delay         |  |

| t <sub>DIN_D</sub>                                          | Dedicated input to LE data delay (4)        |  |

| t <sub>DIN_IO</sub>                                         | Dedicated input to IOE control delay        |  |

| Table 20. FLEX 8000 External Reference Timing Characteristics         Note (5)                            |           |  |

|-----------------------------------------------------------------------------------------------------------|-----------|--|

| Symbol                                                                                                    | Parameter |  |

| t <sub>DRR</sub> Register-to-register delay via 4 LEs, 3 row interconnects, and 4 local interconnects (6) |           |  |

| todh Output data hold time after clock (7)                                                                |           |  |

#### Notes to tables:

- (1) Internal timing parameters cannot be measured explicitly. They are worst-case delays based on testable and external parameters specified by Altera. Internal timing parameters should be used for estimating device performance. Post-compilation timing simulation or timing analysis is required to determine actual worst-case performance.

- (2) These values are specified in Table 10 on page 28 or Table 14 on page 29.

- (3) For the  $t_{OD3}$  and  $t_{ZX3}$  parameters,  $V_{CCIO} = 3.3 \text{ V or } 5.0 \text{ V}$ .

- (4) The  $t_{ROW}$  and  $t_{DIN\_D}$  delays are worst-case values for typical applications. Post-compilation timing simulation or timing analysis is required to determine actual worst-case performance.

- (5) External reference timing characteristics are factory-tested, worst-case values specified by Altera. A representative subset of signal paths is tested to approximate typical device applications.

- (6) For more information on test conditions, see *Application Note 76* (*Understanding FLEX 8000 Timing*).

- (7) This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This parameter applies to global and non-global clocking, and for LE and I/O element registers.

The FLEX 8000 timing model shows the delays for various paths and functions in the circuit. See Figure 19. This model contains three distinct parts: the LE; the IOE; and the interconnect, including the row and column FastTrack Interconnect, LAB local interconnect, and carry and cascade interconnect paths. Each parameter shown in Figure 19 is expressed as a worst-case value in Tables 22 through 49. Hand-calculations that use the FLEX 8000 timing model and these timing parameters can be used to estimate FLEX 8000 device performance. Timing simulation or timing analysis after compilation is required to determine the final worst-case performance. Table 21 summarizes the interconnect paths shown in Figure 19.

For more information on timing parameters, go to *Application Note 76* (*Understanding FLEX 8000 Timing*).

Table 21. FLEX 8000 Timing Model Interconnect Paths Source Destination **Total Delay** LE-Out LE in same LAB  $t_{LOCAL}$ LE-Out LE in same row, different LAB  $t_{ROW} + t_{LOCAL}$  $t_{COL} + t_{ROW} + t_{LOCAL}$ LE-Out LE in different row LE-Out IOE on column  $t_{COL}$ LE-Out IOE on row  $t_{ROW}$ IOE on row LE in same row  $t_{ROW} + t_{LOCAL}$ IOE on column Any LE  $t_{COL} + t_{ROW} + t_{LOCAL}$

Tables 22 through  $49\ \mathrm{show}$  the FLEX 8000 internal and external timing parameters.

| Symbol              | Speed Grade |     |     |     |     |     |    |  |  |

|---------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                     | A-2         |     | A   | -3  | A   | 1   |    |  |  |

|                     | Min         | Max | Min | Max | Min | Max |    |  |  |

| $t_{IOD}$           |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |  |

| t <sub>IOC</sub>    |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| t <sub>IOE</sub>    |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| t <sub>IOCO</sub>   |             | 1.0 |     | 1.0 |     | 1.0 | ns |  |  |

| t <sub>IOCOMB</sub> |             | 0.3 |     | 0.2 |     | 0.1 | ns |  |  |

| t <sub>IOSU</sub>   | 1.4         |     | 1.6 |     | 1.8 |     | ns |  |  |

| t <sub>IOH</sub>    | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |  |

| t <sub>IOCLR</sub>  |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |  |

| t <sub>IN</sub>     |             | 1.5 |     | 1.6 |     | 1.7 | ns |  |  |

| t <sub>OD1</sub>    |             | 1.1 |     | 1.4 |     | 1.7 | ns |  |  |

| t <sub>OD2</sub>    |             | -   |     | _   |     | -   | ns |  |  |

| t <sub>OD3</sub>    |             | 4.6 |     | 4.9 |     | 5.2 | ns |  |  |

| $t_{XZ}$            |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| $t_{ZX1}$           |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| $t_{ZX2}$           |             | -   |     | -   |     | -   | ns |  |  |

| $t_{ZX3}$           |             | 4.9 |     | 5.1 |     | 5.3 | ns |  |  |

| Table 34. EPF8636A I/O Element Timing Parameters |             |     |     |     |     |     |    |  |  |

|--------------------------------------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

| Symbol                                           | Speed Grade |     |     |     |     |     |    |  |  |

|                                                  | A-2         |     | A-3 |     | A-4 |     |    |  |  |

|                                                  | Min         | Max | Min | Max | Min | Max |    |  |  |

| $t_{IOD}$                                        |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |  |

| $t_{IOC}$                                        |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| t <sub>IOE</sub>                                 |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| t <sub>IOCO</sub>                                |             | 1.0 |     | 1.0 |     | 1.0 | ns |  |  |

| t <sub>IOCOMB</sub>                              |             | 0.3 |     | 0.2 |     | 0.1 | ns |  |  |

| t <sub>IOSU</sub>                                | 1.4         |     | 1.6 |     | 1.8 |     | ns |  |  |

| t <sub>IOH</sub>                                 | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |  |

| t <sub>IOCLR</sub>                               |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |  |

| t <sub>IN</sub>                                  |             | 1.5 |     | 1.6 |     | 1.7 | ns |  |  |

| t <sub>OD1</sub>                                 |             | 1.1 |     | 1.4 |     | 1.7 | ns |  |  |

| t <sub>OD2</sub>                                 |             | 1.6 |     | 1.9 |     | 2.2 | ns |  |  |

| t <sub>OD3</sub>                                 |             | 4.6 |     | 4.9 |     | 5.2 | ns |  |  |

| $t_{XZ}$                                         |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| $t_{ZX1}$                                        |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| $t_{ZX2}$                                        |             | 1.9 |     | 2.1 |     | 2.3 | ns |  |  |

| $t_{ZX3}$                                        |             | 4.9 |     | 5.1 |     | 5.3 | ns |  |  |

| Symbol                |     | Speed Grade |     |     |     |     |    |  |  |  |

|-----------------------|-----|-------------|-----|-----|-----|-----|----|--|--|--|

|                       | A-2 |             | A-3 |     | A-4 |     |    |  |  |  |

|                       | Min | Max         | Min | Max | Min | Max |    |  |  |  |

| t <sub>LABCASC</sub>  |     | 0.3         |     | 0.4 |     | 0.4 | ns |  |  |  |

| t <sub>LABCARRY</sub> |     | 0.3         |     | 0.4 |     | 0.4 | ns |  |  |  |

| t <sub>LOCAL</sub>    |     | 0.5         |     | 0.5 |     | 0.7 | ns |  |  |  |

| t <sub>ROW</sub>      |     | 5.0         |     | 5.0 |     | 5.0 | ns |  |  |  |

| $t_{COL}$             |     | 3.0         |     | 3.0 |     | 3.0 | ns |  |  |  |

| t <sub>DIN_C</sub>    |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |  |

| t <sub>DIN_D</sub>    |     | 7.0         |     | 7.0 |     | 7.5 | ns |  |  |  |

| t <sub>DIN IO</sub>   |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |  |

| Symbol             | Speed Grade |     |     |     |     |     |    |  |

|--------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                    | A-2         |     | A-3 |     | A-4 |     |    |  |

|                    | Min         | Max | Min | Max | Min | Max |    |  |

| $t_{IOD}$          |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |

| $t_{IOC}$          |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |

| $t_{IOE}$          |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |

| t <sub>IOCO</sub>  |             | 1.0 |     | 1.0 |     | 1.0 | ns |  |

| $t_{IOCOMB}$       |             | 0.3 |     | 0.2 |     | 0.1 | ns |  |

| t <sub>IOSU</sub>  | 1.4         |     | 1.6 |     | 1.8 |     | ns |  |

| t <sub>IOH</sub>   | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>IOCLR</sub> |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |

| t <sub>IN</sub>    |             | 1.5 |     | 1.6 |     | 1.7 | ns |  |

| t <sub>OD1</sub>   |             | 1.1 |     | 1.4 |     | 1.7 | ns |  |

| t <sub>OD2</sub>   |             | 1.6 |     | 1.9 |     | 2.2 | ns |  |

| t <sub>OD3</sub>   |             | 4.6 |     | 4.9 |     | 5.2 | ns |  |

| $t_{XZ}$           |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |

| $t_{ZX1}$          |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |

| $t_{ZX2}$          |             | 1.9 |     | 2.1 |     | 2.3 | ns |  |

| $t_{ZX3}$          |             | 4.9 |     | 5.1 |     | 5.3 | ns |  |

| Symbol                |     | Speed Grade |     |     |     |     |    |  |  |  |

|-----------------------|-----|-------------|-----|-----|-----|-----|----|--|--|--|

|                       | A-2 |             | A-3 |     | A-4 |     |    |  |  |  |

|                       | Min | Max         | Min | Max | Min | Max | 1  |  |  |  |

| t <sub>LABCASC</sub>  |     | 0.3         |     | 0.3 |     | 0.4 | ns |  |  |  |

| t <sub>LABCARRY</sub> |     | 0.3         |     | 0.3 |     | 0.4 | ns |  |  |  |

| t <sub>LOCAL</sub>    |     | 0.5         |     | 0.6 |     | 0.8 | ns |  |  |  |

| t <sub>ROW</sub>      |     | 5.0         |     | 5.0 |     | 5.0 | ns |  |  |  |

| $t_{COL}$             |     | 3.0         |     | 3.0 |     | 3.0 | ns |  |  |  |

| t <sub>DIN_C</sub>    |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |  |

| t <sub>DIN_D</sub>    |     | 7.0         |     | 7.0 |     | 7.5 | ns |  |  |  |

| t <sub>DIN IO</sub>   |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |  |

| Symbol              | Speed Grade |     |     |     |     |     |    |  |  |

|---------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                     | A-2         |     | A-3 |     | A-4 |     |    |  |  |

|                     | Min         | Max | Min | Max | Min | Max |    |  |  |

| $t_{IOD}$           |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |  |

| t <sub>IOC</sub>    |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| $t_{IOE}$           |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |  |

| t <sub>IOCO</sub>   |             | 1.0 |     | 1.0 |     | 1.0 | ns |  |  |

| t <sub>IOCOMB</sub> |             | 0.3 |     | 0.2 |     | 0.1 | ns |  |  |

| t <sub>IOSU</sub>   | 1.4         |     | 1.6 |     | 1.8 |     | ns |  |  |

| t <sub>IOH</sub>    | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |  |

| t <sub>IOCLR</sub>  |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |  |

| t <sub>IN</sub>     |             | 1.5 |     | 1.6 |     | 1.7 | ns |  |  |

| t <sub>OD1</sub>    |             | 1.1 |     | 1.4 |     | 1.7 | ns |  |  |

| t <sub>OD2</sub>    |             | 1.6 |     | 1.9 |     | 2.2 | ns |  |  |

| t <sub>OD3</sub>    |             | 4.6 |     | 4.9 |     | 5.2 | ns |  |  |

| $t_{XZ}$            |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| $t_{ZX1}$           |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |  |

| $t_{ZX2}$           |             | 1.9 |     | 2.1 |     | 2.3 | ns |  |  |

| $t_{ZX3}$           |             | 4.9 |     | 5.1 |     | 5.3 | ns |  |  |

| Symbol                |     | Speed Grade |     |     |     |     |    |  |  |  |

|-----------------------|-----|-------------|-----|-----|-----|-----|----|--|--|--|

|                       | A   | A-2         |     | A-3 |     | -4  |    |  |  |  |

|                       | Min | Max         | Min | Max | Min | Max |    |  |  |  |

| t <sub>LABCASC</sub>  |     | 0.3         |     | 0.3 |     | 0.4 | ns |  |  |  |

| t <sub>LABCARRY</sub> |     | 0.3         |     | 0.3 |     | 0.4 | ns |  |  |  |

| t <sub>LOCAL</sub>    |     | 0.5         |     | 0.6 |     | 0.8 | ns |  |  |  |

| $t_{ROW}$             |     | 6.2         |     | 6.2 |     | 6.2 | ns |  |  |  |

| t <sub>COL</sub>      |     | 3.0         |     | 3.0 |     | 3.0 | ns |  |  |  |

| t <sub>DIN_C</sub>    |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |  |

| t <sub>DIN_D</sub>    |     | 8.2         |     | 8.2 |     | 8.7 | ns |  |  |  |

| t <sub>DIN IO</sub>   |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |  |

### Device Pin-Outs

Tables 52 through 54 show the pin names and numbers for the dedicated pins in each FLEX 8000 device package.

| Pin Name       | 84-Pin<br>PLCC<br>EPF8282A | 84-Pin<br>PLCC<br>EPF8452A<br>EPF8636A | 100-Pin<br>TQFP<br>EPF8282A<br>EPF8282AV | 100-Pin<br>TQFP<br>EPF8452A | 144-Pin<br>TQFP<br>EPF8820A | 160-Pin<br>PGA<br>EPF8452A | 160-Pin<br>PQFP<br>EPF8820A<br>(1) |

|----------------|----------------------------|----------------------------------------|------------------------------------------|-----------------------------|-----------------------------|----------------------------|------------------------------------|

| nSP <i>(2)</i> | 75                         | 75                                     | 75                                       | 76                          | 110                         | R1                         | 1                                  |

| MSELO (2)      | 74                         | 74                                     | 74                                       | 75                          | 109                         | P2                         | 2                                  |

| MSEL1 (2)      | 53                         | 53                                     | 51                                       | 51                          | 72                          | A1                         | 44                                 |

| nSTATUS (2)    | 32                         | 32                                     | 24                                       | 25                          | 37                          | C13                        | 82                                 |

| nCONFIG (2)    | 33                         | 33                                     | 25                                       | 26                          | 38                          | A15                        | 81                                 |

| DCLK (2)       | 10                         | 10                                     | 100                                      | 100                         | 143                         | P14                        | 125                                |

| CONF_DONE (2)  | 11                         | 11                                     | 1                                        | 1                           | 144                         | N13                        | 124                                |

| nWS            | 30                         | 30                                     | 22                                       | 23                          | 33                          | F13                        | 87                                 |

| nRS            | 48                         | 48                                     | 42                                       | 45                          | 31                          | C6                         | 89                                 |

| RDCLK          | 49                         | 49                                     | 45                                       | 46                          | 12                          | B5                         | 110                                |

| nCS            | 29                         | 29                                     | 21                                       | 22                          | 4                           | D15                        | 118                                |

| CS             | 28                         | 28                                     | 19                                       | 21                          | 3                           | E15                        | 121                                |

| RDYnBUSY       | 77                         | 77                                     | 77                                       | 78                          | 20                          | P3                         | 100                                |

| CLKUSR         | 50                         | 50                                     | 47                                       | 47                          | 13                          | C5                         | 107                                |

| ADD17          | 51                         | 51                                     | 49                                       | 48                          | 75                          | B4                         | 40                                 |

| ADD16          | 36                         | 55                                     | 28                                       | 54                          | 76                          | E2                         | 39                                 |

| ADD15          | 56                         | 56                                     | 55                                       | 55                          | 77                          | D1                         | 38                                 |

| ADD14          | 57                         | 57                                     | 57                                       | 57                          | 78                          | E1                         | 37                                 |

| ADD13          | 58                         | 58                                     | 58                                       | 58                          | 79                          | F3                         | 36                                 |

| ADD12          | 60                         | 60                                     | 59                                       | 60                          | 83                          | F2                         | 32                                 |

| ADD11          | 61                         | 61                                     | 60                                       | 61                          | 85                          | F1                         | 30                                 |

| ADD10          | 62                         | 62                                     | 61                                       | 62                          | 87                          | G2                         | 28                                 |

| ADD9           | 63                         | 63                                     | 62                                       | 64                          | 89                          | G1                         | 26                                 |

| ADD8           | 64                         | 64                                     | 64                                       | 65                          | 92                          | H1                         | 22                                 |

| ADD7           | 65                         | 65                                     | 65                                       | 66                          | 94                          | H2                         | 20                                 |

| ADD6           | 66                         | 66                                     | 66                                       | 67                          | 95                          | J1                         | 18                                 |

| ADD5           | 67                         | 67                                     | 67                                       | 68                          | 97                          | J2                         | 16                                 |

| ADD4           | 69                         | 69                                     | 68                                       | 70                          | 102                         | K2                         | 11                                 |

| ADD3           | 70                         | 70                                     | 69                                       | 71                          | 103                         | K1                         | 10                                 |

| ADD2           | 71                         | 71                                     | 71                                       | 72                          | 104                         | K3                         | 8                                  |

| ADD1           | 76                         | 72                                     | 76                                       | 73                          | 105                         | M1                         | 7                                  |

| Pin Name      | 160-Pin<br>PQFP<br>EPF8452A | 160-Pin<br>PQFP<br>EPF8636A | 192-Pin PGA<br>EPF8636A<br>EPF8820A | 208-Pin<br>PQFP<br>EPF8636A (1) | 208-Pin<br>PQFP<br>EPF8820A (1) | 208-Pin<br>PQFP<br>EPF81188A (1) |

|---------------|-----------------------------|-----------------------------|-------------------------------------|---------------------------------|---------------------------------|----------------------------------|

| nSP (2)       | 120                         | 1                           | R15                                 | 207                             | 207                             | 5                                |

| MSELO (2)     | 117                         | 3                           | T15                                 | 4                               | 4                               | 21                               |

| MSEL1 (2)     | 84                          | 38                          | Т3                                  | 49                              | 49                              | 33                               |

| nSTATUS (2)   | 37                          | 83                          | B3                                  | 108                             | 108                             | 124                              |

| nCONFIG (2)   | 40                          | 81                          | C3                                  | 103                             | 103                             | 107                              |

| DCLK (2)      | 1                           | 120                         | C15                                 | 158                             | 158                             | 154                              |

| CONF_DONE (2) | 4                           | 118                         | B15                                 | 153                             | 153                             | 138                              |

| nWS           | 30                          | 89                          | C5                                  | 114                             | 114                             | 118                              |

| nRS           | 71                          | 50                          | B5                                  | 66                              | 116                             | 121                              |

| RDCLK         | 73                          | 48                          | C11                                 | 64                              | 137                             | 137                              |

| nCS           | 29                          | 91                          | B13                                 | 116                             | 145                             | 142                              |

| CS            | 27                          | 93                          | A16                                 | 118                             | 148                             | 144                              |

| RDYnBUSY      | 125                         | 155                         | A8                                  | 201                             | 127                             | 128                              |

| CLKUSR        | 76                          | 44                          | A10                                 | 59                              | 134                             | 134                              |

| ADD17         | 78                          | 43                          | R5                                  | 57                              | 43                              | 46                               |

| ADD16         | 91                          | 33                          | U3                                  | 43                              | 42                              | 45                               |

| ADD15         | 92                          | 31                          | T5                                  | 41                              | 41                              | 44                               |

| ADD14         | 94                          | 29                          | U4                                  | 39                              | 40                              | 39                               |

| ADD13         | 95                          | 27                          | R6                                  | 37                              | 39                              | 37                               |

| ADD12         | 96                          | 24                          | T6                                  | 31                              | 35                              | 36                               |

| ADD11         | 97                          | 23                          | R7                                  | 30                              | 33                              | 31                               |

| ADD10         | 98                          | 22                          | T7                                  | 29                              | 31                              | 30                               |

| ADD9          | 99                          | 21                          | Т8                                  | 28                              | 29                              | 29                               |

| ADD8          | 101                         | 20                          | U9                                  | 24                              | 25                              | 26                               |

| ADD7          | 102                         | 19                          | U10                                 | 23                              | 23                              | 25                               |

| ADD6          | 103                         | 18                          | U11                                 | 22                              | 21                              | 24                               |

| ADD5          | 104                         | 17                          | U12                                 | 21                              | 19                              | 18                               |

| ADD4          | 105                         | 13                          | R12                                 | 14                              | 14                              | 17                               |

| ADD3          | 106                         | 11                          | U14                                 | 12                              | 13                              | 16                               |

| ADD2          | 109                         | 9                           | U15                                 | 10                              | 11                              | 10                               |

| ADD1          | 110                         | 7                           | R13                                 | 8                               | 10                              | 9                                |

| ADD0          | 123                         | 157                         | U16                                 | 203                             | 9                               | 8                                |

| DATA7         | 144                         | 137                         | H17                                 | 178                             | 178                             | 177                              |

| DATA6         | 150                         | 132                         | G17                                 | 172                             | 176                             | 175                              |

| DATA5         | 152                         | 129                         | F17                                 | 169                             | 174                             | 172                              |

#### Notes to tables:

- (1) Perform a complete thermal analysis before committing a design to this device package. See *Application Note 74* (Evaluating Power for Altera Devices) for more information.

- (2) This pin is a dedicated pin and is not available as a user I/O pin.

- (3) SDOUT will drive out during configuration. After configuration, it may be used as a user I/O pin. By default, the MAX+PLUS II software will not use SDOUT as a user I/O pin; the user can override the MAX+PLUS II software and use SDOUT as a user I/O pin.

- (4) If the device is not configured to use the JTAG BST circuitry, this pin is available as a user I/O pin.

- (5) JTAG pins are available for EPF8636A devices only. These pins are dedicated user I/O pins.

- (6) If this pin is used as an input in user mode, ensure that it does not toggle before or during configuration.

- (7) TRST is a dedicated input pin for JTAG use. This pin must be grounded if JTAG BST is not used.

- (8) Pin 52 is a V<sub>CC</sub> pin on EPF8452A devices only.

- (9) The user I/O pin count includes dedicated input pins and all I/O pins.

- (10) Unused dedicated inputs should be tied to ground on the board.

- (11) SDOUT does not exist in the EPF8636GC192 device.

- (12) These pins are no connect (N.C.) pins for EPF8636A devices only. They are user I/O pins in EPF8820A devices.

- (13) EPF8636A devices have 132 user I/O pins; EPF8820A devices have 148 user I/O pins.

- (14) For EPF81500A devices, these pins are dedicated JTAG pins and are not available as user I/O pins. If JTAG BST is not used, TDI, TCK, TMS, and TRST should be tied to GND.

## Revision History

The information contained in the *FLEX 8000 Programmable Logic Device Family Data Sheet* version 11.1 supersedes information published in previous versions. The *FLEX 8000 Programmable Logic Device Family Data Sheet* version 11.1 contains the following change: minor textual updates.