Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 84                                                         |

| Number of Logic Elements/Cells | 672                                                        |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 112                                                        |

| Number of Gates                | 8000                                                       |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 70°C (TA)                                            |

| Package / Case                 | 144-LQFP                                                   |

| Supplier Device Package        | 144-TQFP (20x20)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf8820atc144-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 1 shows a block diagram of the FLEX 8000 architecture. Each group of eight LEs is combined into an LAB; LABs are arranged into rows and columns. The I/O pins are supported by I/O elements (IOEs) located at the ends of rows and columns. Each IOE contains a bidirectional I/O buffer and a flipflop that can be used as either an input or output register.

Figure 1. FLEX 8000 Device Block Diagram

Signal interconnections within FLEX 8000 devices and between device pins are provided by the FastTrack Interconnect, a series of fast, continuous channels that run the entire length and width of the device. IOEs are located at the end of each row (horizontal) and column (vertical) FastTrack Interconnect path.

# **Logic Array Block**

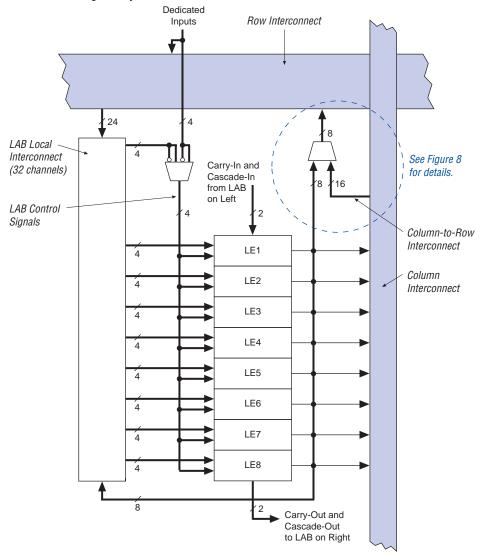

A logic array block (LAB) consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure of the FLEX 8000 architecture. This structure enables FLEX 8000 devices to provide efficient routing, high device utilization, and high performance. Figure 2 shows a block diagram of the FLEX 8000 LAB.

Figure 2. FLEX 8000 Logic Array Block

Each LAB provides four control signals that can be used in all eight LEs. Two of these signals can be used as clocks, and the other two for clear/preset control. The LAB control signals can be driven directly from a dedicated input pin, an I/O pin, or any internal signal via the LAB local interconnect. The dedicated inputs are typically used for global clock, clear, or preset signals because they provide synchronous control with very low skew across the device. FLEX 8000 devices support up to four individual global clock, clear, or preset control signals. If logic is required on a control signal, it can be generated in one or more LEs in any LAB and driven into the local interconnect of the target LAB.

# Logic Element

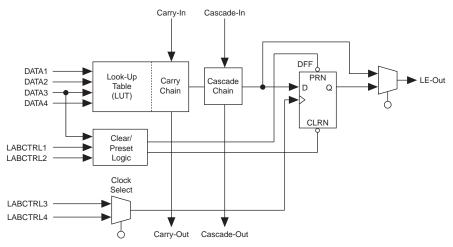

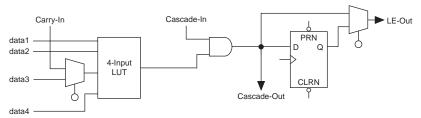

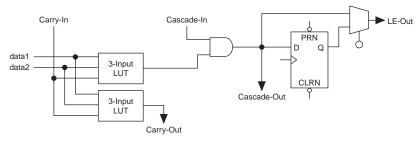

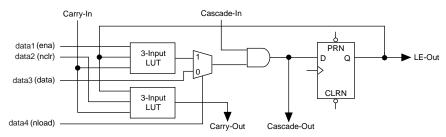

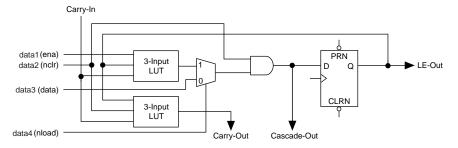

The logic element (LE) is the smallest unit of logic in the FLEX 8000 architecture, with a compact size that provides efficient logic utilization. Each LE contains a 4-input LUT, a programmable flipflop, a carry chain, and cascade chain. Figure 3 shows a block diagram of an LE.

Figure 3. FLEX 8000 LE

The LUT is a function generator that can quickly compute any function of four variables. The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by dedicated input pins, general-purpose I/O pins, or any internal logic. For purely combinatorial functions, the flipflop is bypassed and the output of the LUT goes directly to the output of the LE.

Figure 6. FLEX 8000 LE Operating Modes

#### **Normal Mode**

#### **Arithmetic Mode**

#### **Up/Down Counter Mode**

#### **Clearable Counter Mode**

#### Asynchronous Clear

A register is cleared by one of the two LABCTRL signals. When the CLRn port receives a low signal, the register is set to zero.

#### **Asynchronous Preset**

An asynchronous preset is implemented as either an asynchronous load or an asynchronous clear. If DATA3 is tied to VCC, asserting LABCTRL1 asynchronously loads a 1 into the register. Alternatively, the MAX+PLUS II software can provide preset control by using the clear and inverting the input and output of the register. Inversion control is available for the inputs to both LEs and IOEs. Therefore, if a register is preset by only one of the two LABCTRL signals, the DATA3 input is not needed and can be used for one of the LE operating modes.

#### Asynchronous Clear & Preset

When implementing asynchronous clear and preset, LABCTRL1 controls the preset and LABCTRL2 controls the clear. The DATA3 input is tied to VCC; therefore, asserting LABCTRL1 asynchronously loads a 1 into the register, effectively presetting the register. Asserting LABCTRL2 clears the register.

## Asynchronous Load with Clear

When implementing an asynchronous load with the clear, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear. LABCTRL2 implements the clear by controlling the register clear.

#### Asynchronous Load with Preset

When implementing an asynchronous load in conjunction with a preset, the MAX+PLUS II software provides preset control by using the clear and inverting the input and output of the register. Asserting LABCTRL2 clears the register, while asserting LABCTRL1 loads the register. The MAX+PLUS II software inverts the signal that drives the DATA3 signal to account for the inversion of the register's output.

#### Asynchronous Load without Clear or Preset

When implementing an asynchronous load without the clear or preset, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear.

#### FastTrack Interconnect

In the FLEX 8000 architecture, connections between LEs and device I/O pins are provided by the FastTrack Interconnect, a series of continuous horizontal (row) and vertical (column) routing channels that traverse the entire FLEX 8000 device. This device-wide routing structure provides predictable performance even in complex designs. In contrast, the segmented routing structure in FPGAs requires switch matrices to connect a variable number of routing paths, which increases the delays between logic resources and reduces performance.

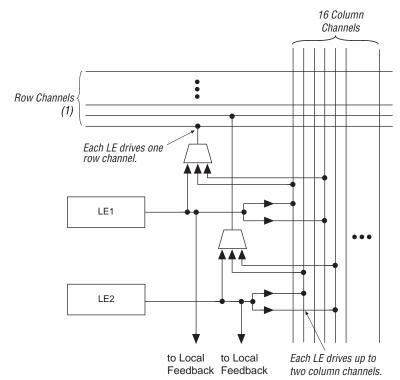

The LABs within FLEX 8000 devices are arranged into a matrix of columns and rows. Each row of LABs has a dedicated row interconnect that routes signals both into and out of the LABs in the row. The row interconnect can then drive I/O pins or feed other LABs in the device. Figure 8 shows how an LE drives the row and column interconnect.

Figure 8. FLEX 8000 LAB Connections to Row & Column Interconnect

Note:

(1) See Table 4 for the number of row channels.

Each LE in an LAB can drive up to two separate column interconnect channels. Therefore, all 16 available column channels can be driven by the LAB. The column channels run vertically across the entire device, and share access to LABs in the same column but in different rows. The MAX+PLUS II Compiler chooses which LEs must be connected to a column channel. A row interconnect channel can be fed by the output of the LE or by two column channels. These three signals feed a multiplexer that connects to a specific row channel. Each LE is connected to one 3-to-1 multiplexer. In an LAB, the multiplexers provide all 16 column channels with access to 8 row channels.

Each column of LABs has a dedicated column interconnect that routes signals out of the LABs into the column. The column interconnect can then drive I/O pins or feed into the row interconnect to route the signals to other LABs in the device. A signal from the column interconnect, which can be either the output of an LE or an input from an I/O pin, must transfer to the row interconnect before it can enter an LAB. Table 4 summarizes the FastTrack Interconnect resources available in each FLEX 8000 device.

| Table 4. FLEX 8000 FastTrack Interconnect Resources |      |                  |         |                     |  |  |  |  |  |

|-----------------------------------------------------|------|------------------|---------|---------------------|--|--|--|--|--|

| Device                                              | Rows | Channels per Row | Columns | Channels per Column |  |  |  |  |  |

| EPF8282A<br>EPF8282AV                               | 2    | 168              | 13      | 16                  |  |  |  |  |  |

| EPF8452A                                            | 2    | 168              | 21      | 16                  |  |  |  |  |  |

| EPF8636A                                            | 3    | 168              | 21      | 16                  |  |  |  |  |  |

| EPF8820A                                            | 4    | 168              | 21      | 16                  |  |  |  |  |  |

| EPF81188A                                           | 6    | 168              | 21      | 16                  |  |  |  |  |  |

| EPF81500A                                           | 6    | 216              | 27      | 16                  |  |  |  |  |  |

Figure 9 shows the interconnection of four adjacent LABs, with row, column, and local interconnects, as well as the associated cascade and carry chains.

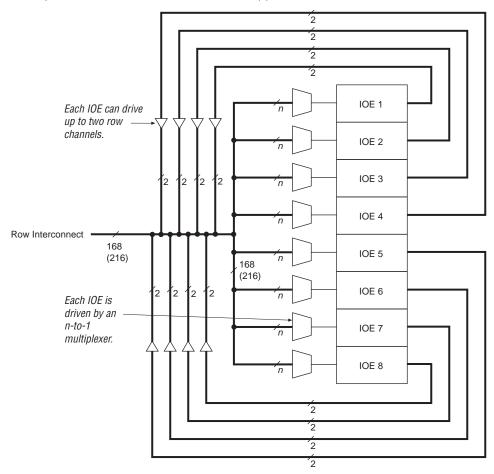

Figure 11. FLEX 8000 Row-to-IOE Connections

Numbers in parentheses are for EPF81500A devices. See Note (1).

#### Note:

- (1) n = 13 for EPF8282A and EPF8282AV devices.

- *n* = 21 for EPF8452A, EPF8636A, EPF8820A, and EPF81188A devices.

- n = 27 for EPF81500A devices.

#### Column-to-IOE Connections

Two IOEs are located at the top and bottom of the column channels (see Figure 12). When an IOE is used as an input, it can drive up to two separate column channels. The output signal to an IOE can choose from 8 of the 16 column channels through an 8-to-1 multiplexer.

Table 5 lists the source of the peripheral control signal for each FLEX 8000 device by row.

| Peripheral<br>Control Signal | EPF8282A<br>EPF8282AV | EPF8452A | EPF8636A | EPF8820A | EPF81188A | EPF81500A |

|------------------------------|-----------------------|----------|----------|----------|-----------|-----------|

| CLK0                         | Row A                 | Row A    | Row A    | Row A    | Row E     | Row E     |

| CLK1/OE1                     | Row B                 | Row B    | Row C    | Row C    | Row B     | Row B     |

| CLR0                         | Row A                 | Row A    | Row B    | Row B    | Row F     | Row F     |

| CLR1/OE0                     | Row B                 | Row B    | Row C    | Row D    | Row C     | Row C     |

| OE2                          | Row A                 | Row A    | Row A    | Row A    | Row D     | Row A     |

| OE3                          | Row B                 | Row B    | Row B    | Row B    | Row A     | Row A     |

| OE4                          | _                     | _        | -        | _        | -         | Row B     |

| OE5                          | _                     | _        | -        | _        | -         | Row C     |

| OE6                          | -                     | -        | -        | -        | -         | Row D     |

| OE7                          | -                     | -        | -        | -        | -         | Row D     |

| OE8                          | -                     | -        | -        | -        | -         | Row E     |

| OE9                          | _                     | _        | _        | _        | -         | Row F     |

# Output Configuration

This section discusses slew-rate control and MultiVolt I/O interface operation for FLEX 8000 devices.

#### **Slew-Rate Control**

The output buffer in each IOE has an adjustable output slew rate that can be configured for low-noise or high-speed performance. A slow slew rate reduces system noise by slowing signal transitions, adding a maximum delay of 3.5 ns. The slow slew-rate setting affects only the falling edge of a signal. The fast slew rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew rate on a pin-by-pin basis during design entry or assign a default slew rate to all pins on a global basis.

For more information on high-speed system design, go to *Application Note 75 (High-Speed Board Designs)*.

| Cumbal              | Parameter                                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------|

| Symbol              | Faiailietei                                                                                           |

| t <sub>IOD</sub>    | IOE register data delay                                                                               |

| t <sub>IOC</sub>    | IOE register control signal delay                                                                     |

| t <sub>IOE</sub>    | Output enable delay                                                                                   |

| t <sub>IOCO</sub>   | IOE register clock-to-output delay                                                                    |

| t <sub>IOCOMB</sub> | IOE combinatorial delay                                                                               |

| t <sub>IOSU</sub>   | IOE register setup time before clock; IOE register recovery time after asynchronous clear             |

| t <sub>IOH</sub>    | IOE register hold time after clock                                                                    |

| t <sub>IOCLR</sub>  | IOE register clear delay                                                                              |

| t <sub>IN</sub>     | Input pad and buffer delay                                                                            |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, $V_{CCIO} = 5.0 \text{ V C1} = 35 \text{ pF}$ (2)  |

| t <sub>OD2</sub>    | Output buffer and pad delay, slow slew rate = off, $V_{CCIO} = 3.3 \text{ V C1} = 35 \text{ pF } (2)$ |

| t <sub>OD3</sub>    | Output buffer and pad delay, slow slew rate = on, C1 = 35 pF (3)                                      |

| $t_{XZ}$            | Output buffer disable delay, C1 = 5 pF                                                                |

| $t_{ZX1}$           | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 5.0 V, C1 = 35 pF (2)           |

| $t_{ZX2}$           | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 3.3 V, C1 = 35 pF (2)           |

| $t_{ZX3}$           | Output buffer enable delay, slow slew rate = on, C1 = 35 pF (3)                                       |

| Table 18. F        | Table 18. FLEX 8000 LE Timing Parameters Note (1)                                                        |  |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                                |  |  |  |  |  |  |  |

| $t_{LUT}$          | LUT delay for data-in                                                                                    |  |  |  |  |  |  |  |

| t <sub>CLUT</sub>  | LUT delay for carry-in                                                                                   |  |  |  |  |  |  |  |

| t <sub>RLUT</sub>  | LUT delay for LE register feedback                                                                       |  |  |  |  |  |  |  |

| t <sub>GATE</sub>  | Cascade gate delay                                                                                       |  |  |  |  |  |  |  |

| t <sub>CASC</sub>  | Cascade chain routing delay                                                                              |  |  |  |  |  |  |  |

| t <sub>CICO</sub>  | Carry-in to carry-out delay                                                                              |  |  |  |  |  |  |  |

| t <sub>CGEN</sub>  | Data-in to carry-out delay                                                                               |  |  |  |  |  |  |  |

| t <sub>CGENR</sub> | LE register feedback to carry-out delay                                                                  |  |  |  |  |  |  |  |

| $t_{C}$            | LE register control signal delay                                                                         |  |  |  |  |  |  |  |

| t <sub>CH</sub>    | LE register clock high time                                                                              |  |  |  |  |  |  |  |

| t <sub>CL</sub>    | LE register clock low time                                                                               |  |  |  |  |  |  |  |

| $t_{CO}$           | LE register clock-to-output delay                                                                        |  |  |  |  |  |  |  |

| t <sub>COMB</sub>  | Combinatorial delay                                                                                      |  |  |  |  |  |  |  |

| t <sub>SU</sub>    | LE register setup time before clock; LE register recovery time after asynchronous preset, clear, or load |  |  |  |  |  |  |  |

| $t_H$              | LE register hold time after clock                                                                        |  |  |  |  |  |  |  |

| t <sub>PRE</sub>   | LE register preset delay                                                                                 |  |  |  |  |  |  |  |

| t <sub>CLR</sub>   | LE register clear delay                                                                                  |  |  |  |  |  |  |  |

| Symbol                |     |     | Speed | Grade |     |     | Unit |

|-----------------------|-----|-----|-------|-------|-----|-----|------|

|                       | A-2 |     | А     | A-3   |     | A-4 |      |

|                       | Min | Max | Min   | Max   | Min | Max | 1    |

| t <sub>LABCASC</sub>  |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LABCARRY</sub> |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LOCAL</sub>    |     | 0.5 |       | 0.6   |     | 0.8 | ns   |

| t <sub>ROW</sub>      |     | 4.2 |       | 4.2   |     | 4.2 | ns   |

| $t_{COL}$             |     | 2.5 |       | 2.5   |     | 2.5 | ns   |

| t <sub>DIN_C</sub>    |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

| t <sub>DIN_D</sub>    |     | 7.2 |       | 7.2   |     | 7.2 | ns   |

| t <sub>DIN_IO</sub>   |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

| Table 28. EPF8282AV Logic Element Timing Parameters |     |      |     |     |    |  |  |  |  |

|-----------------------------------------------------|-----|------|-----|-----|----|--|--|--|--|

| Symbol                                              |     | Unit |     |     |    |  |  |  |  |

|                                                     | A-3 |      | A   | -4  | •  |  |  |  |  |

|                                                     | Min | Max  | Min | Max | •  |  |  |  |  |

| $t_{LUT}$                                           |     | 3.2  |     | 7.3 | ns |  |  |  |  |

| t <sub>CLUT</sub>                                   |     | 0.0  |     | 1.4 | ns |  |  |  |  |

| t <sub>RLUT</sub>                                   |     | 1.5  |     | 5.1 | ns |  |  |  |  |

| t <sub>GATE</sub>                                   |     | 0.0  |     | 0.0 | ns |  |  |  |  |

| t <sub>CASC</sub>                                   |     | 0.9  |     | 2.8 | ns |  |  |  |  |

| t <sub>CICO</sub>                                   |     | 0.6  |     | 1.5 | ns |  |  |  |  |

| t <sub>CGEN</sub>                                   |     | 0.7  |     | 2.2 | ns |  |  |  |  |

| t <sub>CGENR</sub>                                  |     | 1.5  |     | 3.7 | ns |  |  |  |  |

| $t_{\rm C}$                                         |     | 2.5  |     | 4.7 | ns |  |  |  |  |

| t <sub>CH</sub>                                     | 4.0 |      | 6.0 |     | ns |  |  |  |  |

| $t_{CL}$                                            | 4.0 |      | 6.0 |     | ns |  |  |  |  |

| $t_{CO}$                                            |     | 0.6  |     | 0.9 | ns |  |  |  |  |

| t <sub>COMB</sub>                                   |     | 0.6  |     | 0.9 | ns |  |  |  |  |

| t <sub>SU</sub>                                     | 1.2 |      | 2.4 |     | ns |  |  |  |  |

| $t_H$                                               | 1.5 |      | 4.6 |     | ns |  |  |  |  |

| t <sub>PRE</sub>                                    |     | 0.8  |     | 1.3 | ns |  |  |  |  |

| t <sub>CLR</sub>                                    |     | 0.8  |     | 1.3 | ns |  |  |  |  |

| Table 29. EPF8282AV External Timing Parameters |     |             |     |      |    |  |  |  |  |

|------------------------------------------------|-----|-------------|-----|------|----|--|--|--|--|

| Symbol                                         |     | Speed Grade |     |      |    |  |  |  |  |

|                                                | A-3 |             | А   |      |    |  |  |  |  |

|                                                | Min | Max         | Min | Max  |    |  |  |  |  |

| t <sub>DRR</sub>                               |     | 24.8        |     | 50.1 | ns |  |  |  |  |

| t <sub>ODH</sub>                               | 1.0 |             | 1.0 |      | ns |  |  |  |  |

| Table 34. EPF8636A I/O Element Timing Parameters |             |     |     |     |     |            |    |  |

|--------------------------------------------------|-------------|-----|-----|-----|-----|------------|----|--|

| Symbol                                           | Speed Grade |     |     |     |     |            |    |  |

|                                                  | A-2         |     | A   | A-3 |     | <b>1-4</b> |    |  |

|                                                  | Min         | Max | Min | Max | Min | Max        |    |  |

| $t_{IOD}$                                        |             | 0.7 |     | 0.8 |     | 0.9        | ns |  |

| t <sub>IOC</sub>                                 |             | 1.7 |     | 1.8 |     | 1.9        | ns |  |

| t <sub>IOE</sub>                                 |             | 1.7 |     | 1.8 |     | 1.9        | ns |  |

| t <sub>IOCO</sub>                                |             | 1.0 |     | 1.0 |     | 1.0        | ns |  |

| t <sub>IOCOMB</sub>                              |             | 0.3 |     | 0.2 |     | 0.1        | ns |  |

| t <sub>IOSU</sub>                                | 1.4         |     | 1.6 |     | 1.8 |            | ns |  |

| t <sub>IOH</sub>                                 | 0.0         |     | 0.0 |     | 0.0 |            | ns |  |

| t <sub>IOCLR</sub>                               |             | 1.2 |     | 1.2 |     | 1.2        | ns |  |

| t <sub>IN</sub>                                  |             | 1.5 |     | 1.6 |     | 1.7        | ns |  |

| t <sub>OD1</sub>                                 |             | 1.1 |     | 1.4 |     | 1.7        | ns |  |

| t <sub>OD2</sub>                                 |             | 1.6 |     | 1.9 |     | 2.2        | ns |  |

| t <sub>OD3</sub>                                 |             | 4.6 |     | 4.9 |     | 5.2        | ns |  |

| $t_{XZ}$                                         |             | 1.4 |     | 1.6 |     | 1.8        | ns |  |

| $t_{ZX1}$                                        |             | 1.4 |     | 1.6 |     | 1.8        | ns |  |

| $t_{ZX2}$                                        |             | 1.9 |     | 2.1 |     | 2.3        | ns |  |

| $t_{ZX3}$                                        |             | 4.9 |     | 5.1 |     | 5.3        | ns |  |

| Symbol                |     | Speed Grade |     |     |     |     |    |  |  |

|-----------------------|-----|-------------|-----|-----|-----|-----|----|--|--|

|                       | A-2 |             | A-3 |     | A-4 |     | 1  |  |  |

|                       | Min | Max         | Min | Max | Min | Max | 1  |  |  |

| t <sub>LABCASC</sub>  |     | 0.3         |     | 0.4 |     | 0.4 | ns |  |  |

| t <sub>LABCARRY</sub> |     | 0.3         |     | 0.4 |     | 0.4 | ns |  |  |

| t <sub>LOCAL</sub>    |     | 0.5         |     | 0.5 |     | 0.7 | ns |  |  |

| t <sub>ROW</sub>      |     | 5.0         |     | 5.0 |     | 5.0 | ns |  |  |

| $t_{COL}$             |     | 3.0         |     | 3.0 |     | 3.0 | ns |  |  |

| t <sub>DIN_C</sub>    |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |

| t <sub>DIN_D</sub>    |     | 7.0         |     | 7.0 |     | 7.5 | ns |  |  |

| t <sub>DIN IO</sub>   |     | 5.0         |     | 5.0 |     | 5.5 | ns |  |  |

| Symbol              | Speed Grade |     |     |     |     |     |    |  |

|---------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                     | A-2         |     | A-3 |     | A-4 |     |    |  |

|                     | Min         | Max | Min | Max | Min | Max |    |  |

| $t_{IOD}$           |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |

| t <sub>IOC</sub>    |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |

| t <sub>IOE</sub>    |             | 1.7 |     | 1.8 |     | 1.9 | ns |  |

| t <sub>IOCO</sub>   |             | 1.0 |     | 1.0 |     | 1.0 | ns |  |

| t <sub>IOCOMB</sub> |             | 0.3 |     | 0.2 |     | 0.1 | ns |  |

| t <sub>IOSU</sub>   | 1.4         |     | 1.6 |     | 1.8 |     | ns |  |

| t <sub>IOH</sub>    | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>IOCLR</sub>  |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |

| t <sub>IN</sub>     |             | 1.5 |     | 1.6 |     | 1.7 | ns |  |

| t <sub>OD1</sub>    |             | 1.1 |     | 1.4 |     | 1.7 | ns |  |

| t <sub>OD2</sub>    |             | 1.6 |     | 1.9 |     | 2.2 | ns |  |

| t <sub>OD3</sub>    |             | 4.6 |     | 4.9 |     | 5.2 | ns |  |

| $t_{XZ}$            |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |

| $t_{ZX1}$           |             | 1.4 |     | 1.6 |     | 1.8 | ns |  |

| $t_{ZX2}$           |             | 1.9 |     | 2.1 |     | 2.3 | ns |  |

| $t_{ZX3}$           |             | 4.9 |     | 5.1 |     | 5.3 | ns |  |

| Symbol                |     |     | Speed | Grade |     |     | Unit |

|-----------------------|-----|-----|-------|-------|-----|-----|------|

|                       | A-2 |     | A-3   |       | A-4 |     |      |

|                       | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>LABCASC</sub>  |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LABCARRY</sub> |     | 0.3 |       | 0.3   |     | 0.4 | ns   |

| t <sub>LOCAL</sub>    |     | 0.5 |       | 0.6   |     | 0.8 | ns   |

| t <sub>ROW</sub>      |     | 5.0 |       | 5.0   |     | 5.0 | ns   |

| t <sub>COL</sub>      |     | 3.0 |       | 3.0   |     | 3.0 | ns   |

| t <sub>DIN_C</sub>    |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

| t <sub>DIN_D</sub>    |     | 7.0 |       | 7.0   |     | 7.5 | ns   |

| t <sub>DIN_IO</sub>   |     | 5.0 |       | 5.0   |     | 5.5 | ns   |

| Table 40. EPF8820A LE Timing Parameters |             |     |     |     |     |     |    |  |

|-----------------------------------------|-------------|-----|-----|-----|-----|-----|----|--|

| Symbol                                  | Speed Grade |     |     |     |     |     |    |  |

|                                         | A-2         |     | A-3 |     | A-4 |     |    |  |

|                                         | Min         | Max | Min | Max | Min | Max |    |  |

| $t_{LUT}$                               |             | 2.0 |     | 2.5 |     | 3.2 | ns |  |

| t <sub>CLUT</sub>                       |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>RLUT</sub>                       |             | 0.9 |     | 1.1 |     | 1.5 | ns |  |

| $t_{GATE}$                              |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>CASC</sub>                       |             | 0.6 |     | 0.7 |     | 0.9 | ns |  |

| t <sub>CICO</sub>                       |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |

| t <sub>CGEN</sub>                       |             | 0.4 |     | 0.5 |     | 0.7 | ns |  |

| t <sub>CGENR</sub>                      |             | 0.9 |     | 1.1 |     | 1.5 | ns |  |

| $t_C$                                   |             | 1.6 |     | 2.0 |     | 2.5 | ns |  |

| t <sub>CH</sub>                         | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |

| t <sub>CL</sub>                         | 4.0         |     | 4.0 |     | 4.0 |     | ns |  |

| $t_{CO}$                                |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |

| t <sub>COMB</sub>                       |             | 0.4 |     | 0.5 |     | 0.6 | ns |  |

| t <sub>SU</sub>                         | 0.8         |     | 1.1 |     | 1.2 |     | ns |  |

| t <sub>H</sub>                          | 0.9         |     | 1.1 |     | 1.5 |     | ns |  |

| t <sub>PRE</sub>                        |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |

| t <sub>CLR</sub>                        |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |

| Table 41. EPF8820A External Timing Parameters |             |      |     |      |     |      |    |  |

|-----------------------------------------------|-------------|------|-----|------|-----|------|----|--|

| Symbol                                        | Speed Grade |      |     |      |     |      |    |  |

|                                               | А           | -2   | A-3 |      | A-4 |      | -  |  |

|                                               | Min         | Max  | Min | Max  | Min | Max  |    |  |

| t <sub>DRR</sub>                              |             | 16.0 |     | 20.0 |     | 25.0 | ns |  |

| t <sub>ODH</sub>                              | 1.0         |      | 1.0 |      | 1.0 |      | ns |  |

# **Operating Modes**

The FLEX 8000 architecture uses SRAM elements that require configuration data to be loaded whenever the device powers up and begins operation. The process of physically loading the SRAM programming data into the device is called *configuration*. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. The configuration and initialization processes together are called *command mode*; normal device operation is called *user mode*.

SRAM elements allow FLEX 8000 devices to be reconfigured in-circuit with new programming data that is loaded into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different programming data, reinitializing the device, and resuming user-mode operation. The entire reconfiguration process requires less than 100 ms and can be used to dynamically reconfigure an entire system. In-field upgrades can be performed by distributing new configuration files.

# **Configuration Schemes**

The configuration data for a FLEX 8000 device can be loaded with one of six configuration schemes, chosen on the basis of the target application. Both active and passive schemes are available. In the active configuration schemes, the FLEX 8000 device functions as the controller, directing the loading operation, controlling external configuration devices, and completing the loading process. The clock source for all active configuration schemes is an oscillator on the FLEX 8000 device that operates between 2 MHz and 6 MHz. In the passive configuration schemes, an external controller guides the FLEX 8000 device. Table 51 shows the data source for each of the six configuration schemes.

| Table 51. Data Source for Configuration |         |                               |  |  |  |  |  |

|-----------------------------------------|---------|-------------------------------|--|--|--|--|--|

| Configuration Scheme                    | Acronym | Data Source                   |  |  |  |  |  |

| Active serial                           | AS      | Altera configuration device   |  |  |  |  |  |

| Active parallel up                      | APU     | Parallel configuration device |  |  |  |  |  |

| Active parallel down                    | APD     | Parallel configuration device |  |  |  |  |  |

| Passive serial                          | PS      | Serial data path              |  |  |  |  |  |

| Passive parallel synchronous            | PPS     | Intelligent host              |  |  |  |  |  |

| Passive parallel asynchronous           | PPA     | Intelligent host              |  |  |  |  |  |

| Pin Name     | 84-Pin            | 84-Pin                       | 100-Pin                       | 100-Pin              | 144-Pin                                    | 160-Pin                                                                                   | 160-Pin                                                 |

|--------------|-------------------|------------------------------|-------------------------------|----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------|

|              | PLCC<br>EPF8282A  | PLCC<br>EPF8452A<br>EPF8636A | TQFP<br>EPF8282A<br>EPF8282AV | TQFP<br>EPF8452A     | TQFP<br>EPF8820A                           | PGA<br>EPF8452A                                                                           | PQFP<br>EPF8820A<br>(1)                                 |

| ADD0         | 78                | 76                           | 78                            | 77                   | 106                                        | N3                                                                                        | 6                                                       |

| DATA7        | 3                 | 2                            | 90                            | 89                   | 131                                        | P8                                                                                        | 140                                                     |

| DATA6        | 4                 | 4                            | 91                            | 91                   | 132                                        | P10                                                                                       | 139                                                     |

| DATA5        | 6                 | 6                            | 92                            | 95                   | 133                                        | R12                                                                                       | 138                                                     |

| DATA4        | 7                 | 7                            | 95                            | 96                   | 134                                        | R13                                                                                       | 136                                                     |

| DATA3        | 8                 | 8                            | 97                            | 97                   | 135                                        | P13                                                                                       | 135                                                     |

| DATA2        | 9                 | 9                            | 99                            | 98                   | 137                                        | R14                                                                                       | 133                                                     |

| DATA1        | 13                | 13                           | 4                             | 4                    | 138                                        | N15                                                                                       | 132                                                     |

| DATA0        | 14                | 14                           | 5                             | 5                    | 140                                        | K13                                                                                       | 129                                                     |

| SDOUT (3)    | 79                | 78                           | 79                            | 79                   | 23                                         | P4                                                                                        | 97                                                      |

| TDI (4)      | 55                | 45 (5)                       | 54                            | _                    | 96                                         | _                                                                                         | 17                                                      |

| TDO (4)      | 27                | 27 (5)                       | 18                            | _                    | 18                                         | _                                                                                         | 102                                                     |

| TCK (4), (6) | 72                | 44 (5)                       | 72                            | _                    | 88                                         | _                                                                                         | 27                                                      |

| TMS (4)      | 20                | 43 (5)                       | 11                            | _                    | 86                                         | _                                                                                         | 29                                                      |

| TRST (7)     | 52                | 52 (8)                       | 50                            | _                    | 71                                         | _                                                                                         | 45                                                      |

| Dedicated    | 12, 31, 54,       | 12, 31, 54,                  | 3, 23, 53, 73                 | 3, 24, 53,           | 9, 26, 82,                                 | C3, D14,                                                                                  | 14, 33, 94,                                             |

| Inputs (10)  | 73                | 73                           |                               | 74                   | 99                                         | N2, R15                                                                                   | 113                                                     |

| VCCINT       | 17, 38, 59,<br>80 | 17, 38, 59,<br>80            | 6, 20, 37, 56,<br>70, 87      | 9, 32, 49,<br>59, 82 | 8, 28, 70,<br>90, 111                      | B2, C4, D3,<br>D8, D12,<br>G3, G12,<br>H4, H13,<br>J3, J12,<br>M4, M7,<br>M9, M13,<br>N12 | 3, 24, 46,<br>92, 114,<br>160                           |

| VCCIO        | -                 | _                            | _                             | _                    | 16, 40, 60,<br>69, 91,<br>112, 122,<br>141 | _                                                                                         | 23, 47, 57,<br>69, 79,<br>104, 127,<br>137, 149,<br>159 |

| Pin Name                     | 160-Pin<br>PQFP<br>EPF8452A                                  | 160-Pin<br>PQFP<br>EPF8636A                                                | 192-Pin PGA<br>EPF8636A<br>EPF8820A                                                        | 208-Pin<br>PQFP<br>EPF8636A (1)                                                                                                                                                  | 208-Pin<br>PQFP<br>EPF8820A (1)                                                     | 208-Pin<br>PQFP<br>EPF81188A (1)                                                                         |

|------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| DATA4                        | 154                                                          | 127                                                                        | E17                                                                                        | 165                                                                                                                                                                              | 172                                                                                 | 170                                                                                                      |

| DATA3                        | 157                                                          | 124                                                                        | G15                                                                                        | 162                                                                                                                                                                              | 171                                                                                 | 168                                                                                                      |

| DATA2                        | 159                                                          | 122                                                                        | F15                                                                                        | 160                                                                                                                                                                              | 167                                                                                 | 166                                                                                                      |

| DATA1                        | 11                                                           | 115                                                                        | E16                                                                                        | 149                                                                                                                                                                              | 165                                                                                 | 163                                                                                                      |

| DATA0                        | 12                                                           | 113                                                                        | C16                                                                                        | 147                                                                                                                                                                              | 162                                                                                 | 161                                                                                                      |

| SDOUT (3)                    | 128                                                          | 152                                                                        | C7 (11)                                                                                    | 198                                                                                                                                                                              | 124                                                                                 | 119                                                                                                      |

| TDI (4)                      | _                                                            | 55                                                                         | R11                                                                                        | 72                                                                                                                                                                               | 20                                                                                  | _                                                                                                        |

| TDO (4)                      | _                                                            | 95                                                                         | B9                                                                                         | 120                                                                                                                                                                              | 129                                                                                 | _                                                                                                        |

| TCK (4), (6)                 | _                                                            | 57                                                                         | U8                                                                                         | 74                                                                                                                                                                               | 30                                                                                  | _                                                                                                        |

| TMS (4)                      | _                                                            | 59                                                                         | U7                                                                                         | 76                                                                                                                                                                               | 32                                                                                  | _                                                                                                        |

| TRST (7)                     | -                                                            | 40                                                                         | R3                                                                                         | 54                                                                                                                                                                               | 54                                                                                  | _                                                                                                        |

| Dedicated<br>Inputs (10)     | 5, 36, 85, 116                                               | 6, 35, 87, 116                                                             | A5, U5, U13,<br>A13                                                                        | 7, 45, 112,<br>150                                                                                                                                                               | 17, 36, 121,<br>140                                                                 | 13, 41, 116,<br>146                                                                                      |

| VCCINT (5.0 V)               | 21, 41, 53, 67,<br>80, 81, 100, 121,<br>133, 147, 160        | 4, 5, 26, 85,<br>106                                                       | C8, C9, C10,<br>R8, R9, R10,<br>R14                                                        | 5, 6, 33, 110,<br>137                                                                                                                                                            | 5, 6, 27, 48,<br>119, 141                                                           | 4, 20, 35, 48,<br>50, 102, 114,<br>131, 147                                                              |

| VCCIO<br>(5.0 V or<br>3.3 V) | _                                                            | 25, 41, 60, 70,<br>80, 107, 121,<br>140, 149, 160                          | D3, D4, D9,<br>D14, D15, G4,<br>G14, L4, L14,<br>P4, P9, P14                               | 32, 55, 78, 91,<br>102, 138, 159,<br>182, 193, 206                                                                                                                               | 26, 55, 69, 87,<br>102, 131, 159,<br>173, 191, 206                                  | 3, 19, 34, 49,<br>69, 87, 106,<br>123, 140, 156,<br>174, 192                                             |

| GND                          | 13, 14, 28, 46,<br>60, 75, 93, 107,<br>108, 126, 140,<br>155 | 15, 16, 36, 37,<br>45, 51, 75, 84,<br>86, 96, 97,<br>117, 126, 131,<br>154 | C4, D7, D8,<br>D10, D11, H4,<br>H14, K4, K14,<br>P7, P8, P10,<br>P11                       | 19, 20, 46, 47,<br>60, 67, 96,<br>109, 111, 124,<br>125, 151, 164,<br>171, 200                                                                                                   | 15, 16, 37, 38,<br>60, 78, 96,<br>109, 110, 120,<br>130, 142, 152,<br>164, 182, 200 | 11, 12, 27, 28,<br>42, 43, 60, 78,<br>96, 105, 115,<br>122, 132, 139,<br>148, 155, 159,<br>165, 183, 201 |

| No Connect<br>(N.C.)         | 2, 3, 38, 39, 70,<br>82, 83, 118, 119,<br>148                | 2, 39, 82, 119                                                             | C6, C12, C13,<br>C14, E3, E15,<br>F3, J3, J4,<br>J14, J15, N3,<br>N15, P3, P15,<br>R4 (12) | 1, 2, 3, 16, 17,<br>18, 25, 26, 27,<br>34, 35, 36, 50,<br>51, 52, 53,<br>104, 105, 106,<br>107, 121, 122,<br>123, 130, 131,<br>132, 139, 140,<br>141, 154, 155,<br>156, 157, 208 | 1, 2, 3, 50, 51,<br>52, 53, 104,<br>105, 106, 107,<br>154, 155, 156,<br>157, 208    | 1, 2, 51, 52, 53,<br>54, 103, 104,<br>157, 158, 207,<br>208                                              |

| Total User<br>I/O Pins (9)   | 116                                                          | 114                                                                        | 132, 148 (13)                                                                              | 132                                                                                                                                                                              | 148                                                                                 | 144                                                                                                      |

| Pin Name         | 225-Pin<br>BGA<br>EPF8820A | 232-Pin<br>PGA<br>EPF81188A | 240-Pin<br>PQFP | 240-Pin<br>PQFP | 280-Pin<br>PGA<br>EPF81500A | 304-Pin<br>RQFP |

|------------------|----------------------------|-----------------------------|-----------------|-----------------|-----------------------------|-----------------|

|                  |                            |                             | EPF81188A       | EPF81500A       |                             | EPF81500A       |

| DATA4            | A5                         | C7                          | 198             | 194             | W16                         | 248             |

| DATA3            | B5                         | D7                          | 196             | 193             | W17                         | 246             |

| DATA2            | E6                         | B5                          | 194             | 190             | V16                         | 243             |

| DATA1            | D5                         | А3                          | 191             | 189             | U16                         | 241             |

| DATA0            | C4                         | A2                          | 189             | 187             | V17                         | 239             |

| SDOUT (3)        | K1                         | N2                          | 135             | 136             | F19                         | 169             |

| TDI              | F15 (4)                    | _                           | _               | 63 (14)         | B1 (14)                     | 80 (14)         |

| TDO              | J2 (4)                     | _                           | _               | 117             | C17                         | 149             |

| TCK (6)          | J14 (4)                    | _                           | _               | 116 <i>(14)</i> | A19 (14)                    | 148 (14)        |

| TMS              | J12 (4)                    | _                           | _               | 64 (14)         | C2 (14)                     | 81 (14)         |

| TRST (7)         | P14                        | _                           | _               | 115 <i>(14)</i> | A18 (14)                    | 145 (14)        |

| Dedicated Inputs | F4, L1, K12,               | C1, C17, R1,                | 10, 51, 130,    | 8, 49, 131,     | F1, F16, P3,                | 12, 64, 164,    |

| (10)             | E15                        | R17                         | 171             | 172             | P19                         | 217             |

| VCCINT           | F5, F10, E1,               | E4, H4, L4,                 | 20, 42, 64, 66, | 18, 40, 60, 62, | B17, D3, D15,               | 24, 54, 77,     |

| (5.0 V)          | L2, K4, M12,               | P12, L14,                   | 114, 128, 150,  | 91, 114, 129,   | E8, E10, E12,               | 144, 79, 115,   |

|                  | P15, H13,                  | H14, E14,                   | 172, 236        |                 | E14, R7, R9,                | 162, 191, 218,  |

|                  | H14, B15,                  | R14, U1                     |                 | 236             | R11, R13,                   | 266, 301        |

|                  | C13                        |                             |                 |                 | R14, T14                    |                 |

| VCCIO            | H3, H2, P6,                | N10, M13,                   | 19, 41, 65, 81, | 17, 39, 61, 78, | D14, E7, E9,                | 22, 53, 78, 99, |

| (5.0 V or 3.3 V) | R6, P10, N10,              | M5, K13, K5,                | 99, 116, 140,   | 94, 108, 130,   | E11, E13, R6,               |                 |

|                  | R14, N13,                  | H13, H5, F5,                | 162, 186, 202,  |                 | R8, R10, R12,               |                 |

|                  | H15, H12,                  | E10, E8, N8,                | 220, 235        | 205, 221, 235   | T13, T15                    | 262, 282, 300   |

|                  | D12, A14,                  | F13                         |                 |                 |                             |                 |

|                  | B10, A10, B6,              |                             |                 |                 |                             |                 |

|                  | C6, A2, C3,                |                             |                 |                 |                             |                 |

| Ì                | M4, R2                     |                             |                 |                 |                             |                 |

#### Notes to tables:

- (1) Perform a complete thermal analysis before committing a design to this device package. See *Application Note 74* (Evaluating Power for Altera Devices) for more information.

- (2) This pin is a dedicated pin and is not available as a user I/O pin.

- (3) SDOUT will drive out during configuration. After configuration, it may be used as a user I/O pin. By default, the MAX+PLUS II software will not use SDOUT as a user I/O pin; the user can override the MAX+PLUS II software and use SDOUT as a user I/O pin.

- (4) If the device is not configured to use the JTAG BST circuitry, this pin is available as a user I/O pin.

- (5) JTAG pins are available for EPF8636A devices only. These pins are dedicated user I/O pins.

- (6) If this pin is used as an input in user mode, ensure that it does not toggle before or during configuration.

- (7) TRST is a dedicated input pin for JTAG use. This pin must be grounded if JTAG BST is not used.

- (8) Pin 52 is a V<sub>CC</sub> pin on EPF8452A devices only.

- (9) The user I/O pin count includes dedicated input pins and all I/O pins.

- (10) Unused dedicated inputs should be tied to ground on the board.

- (11) SDOUT does not exist in the EPF8636GC192 device.

- (12) These pins are no connect (N.C.) pins for EPF8636A devices only. They are user I/O pins in EPF8820A devices.

- (13) EPF8636A devices have 132 user I/O pins; EPF8820A devices have 148 user I/O pins.

- (14) For EPF81500A devices, these pins are dedicated JTAG pins and are not available as user I/O pins. If JTAG BST is not used, TDI, TCK, TMS, and TRST should be tied to GND.

# Revision History

The information contained in the *FLEX 8000 Programmable Logic Device Family Data Sheet* version 11.1 supersedes information published in previous versions. The *FLEX 8000 Programmable Logic Device Family Data Sheet* version 11.1 contains the following change: minor textual updates.