#### Welcome to E-XFL.COM

## Understanding Embedded - PLDs (Programmable Logic Devices)

Embedded - PLDs, or Programmable Logic Devices, are a type of digital electronic component used to build reconfigurable digital circuits. Unlike fixed-function logic devices, PLDs can be programmed to perform specific functions by the user. This flexibility allows designers to customize the logic to meet the exact needs of their applications, making PLDs a crucial component in modern embedded systems.

# Applications of Embedded - PLDs (Programmable Logic Devices)

The versatility of PLDs makes them suitable for a wide range of applications. In consumer electronics, PLDs are used to enhance the functionality and performance of

#### Details

| Details                 |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Active                                                                     |

| Programmable Type       | EPLD                                                                       |

| Number of Macrocells    | 10                                                                         |

| Voltage - Input         | 5V                                                                         |

| Speed                   | 15 ns                                                                      |

| Mounting Type           | Through Hole                                                               |

| Package / Case          | 24-CDIP (0.300", 7.62mm) Window                                            |

| Supplier Device Package | 24-CDIP                                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/atv750b-15dm-883 |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Features

- Advanced, High-speed Programmable Logic Device Superset of 22V10

- Improved Performance 7.5 ns  $t_{\text{PD}},$  95 MHz External Operation

- Enhanced Logic Flexibility

- Backward Compatible with ATV750(L) Software and Hardware

- New Flip-flop Features

- D- or T-type

- Product Term or Direct Input Pin Clocking

- High-speed Erasable Programmable Logic Devices

- 7.5 ns Maximum Pin-to-pin Delay

| Device   | I <sub>CC</sub> , Standby |

|----------|---------------------------|

| ATV750B  | 125 mA                    |

| ATV750BL | 15 mA                     |

- Highest Density Programmable Logic Available in a 24-pin Package

- Increased Logic Flexibility

- 42 Array Inputs, 20 Sum Terms and 20 Flip-flops

- Enhanced Output Logic Flexibility

- All 20 Flip-flops Feed Back Internally

- 10 Flip-flops are Also Available as Outputs

- Full Military, Commercial and Industrial Temperature Ranges

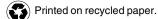

# Logic Diagram

## Description

The ATV750B(L) is twice as powerful as most other 24-pin programmable logic devices. Increased product terms, sum terms, flip-flops and output logic configurations translate into more usable gates. High-speed logic and uniform, predictable delays guarantee fast in-system performance.

| Pin Configurations |                        | DIP/S                 | oic                  |                      |                                              |

|--------------------|------------------------|-----------------------|----------------------|----------------------|----------------------------------------------|

| Pin Name           | Function               | CLK/IN □ 1<br>IN □ 2  | 24 □ VCC<br>23 □ I/O |                      |                                              |

| CLK                | Clock                  | IN □ 3<br>IN □ 4      | 22 □ I/O<br>21 □ I/O | IN □ 5               | 0 ~ ~ ~25 1/0                                |

| IN                 | Logic Inputs           | IN □ 5<br>IN □ 6      | 20 🗆 I/O<br>19 🗖 I/O | IN                   | 24 □ 1/0<br>23 □ 1/0                         |

| I/O                | Bi-directional Buffers | IN 🗆 7<br>IN 🗖 8      | 18 □ I/O<br>17 □ I/O | * □ 8<br>IN □ 9      | 22 □ *<br>21 □ I/O                           |

| *                  | No Internal Connection | IN ☐ 9<br>IN ☐ 10     | 16 □ I/O<br>15 □ I/O | IN ☐ 10<br>IN ☐ 11 , | 20 □ 1/0<br>± 10 00 0 m <sup>1</sup> 9 □ 1/0 |

| V <sub>cc</sub>    | +5V Supply             | IN [] 11<br>GND [] 12 | 14 □ I/O<br>13 □ IN  |                      | ; ≠ ≠ ÷ ÷ i                                  |

|                    |                        |                       |                      |                      |                                              |

High-speed UV Erasable Programmable Logic Device

# ATV750B ATV750BL

Commercial and industrial versions are obsolete. Please use ATF750C.

Military versions continue to be available, but please do not use for new designs. For new military applications, recommend multiple ATF22V10s.

Each of the ATV750B(L) 22 logic pins can be used as an input. Ten of these can be used as inputs, outputs or bi-directional I/O pins. Each flip-flop is individually configurable as either D-or T-type. Each flip-flop output is fed back into the array independently. This allows burying of all the sum terms and flip-flops.

There are 171 total product terms available. A variable format is used to assign between four to eight product terms per sum term. There are two sum terms per output, providing added flexibility. Much more logic can be replaced by this device than by any other 24-pin PLD. With 20 sum terms and flip-flops, complex state machines are easily implemented with logic to spare.

Product terms provide individual clocks and asynchronous resets for each flip-flop. Each flipflop may also be individually configured to have direct input pin controlled clocking. Each output has its own enable product term. One product term provides a common synchronous preset for all flip-flops. Register preload functions are provided to simplify testing. All registers automatically reset upon power-up.

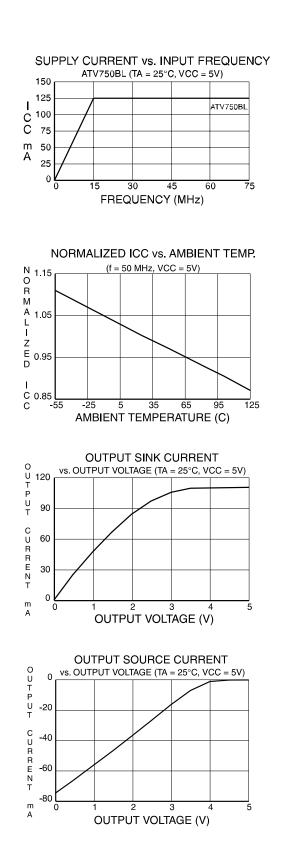

The ATV750BL is a low-power device with speeds as fast as 15 ns. The ATV750BL provides the optimum low-power PLD solution, with full CMOS output levels. This device significantly reduces total system power, thereby allowing battery-powered operation.

### Absolute Maximum Ratings\*

| Temperature Under Bias55°C to +125°C                                                               |

|----------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                  |

| Voltage on Any Pin with<br>Respect to Ground2.0V to +7.0V <sup>(1)</sup>                           |

| Voltage on Input Pins<br>with Respect to Ground<br>During Programming2.0V to +14.0V <sup>(1)</sup> |

| Programming Voltage with<br>Respect to Ground2.0V to +14.0V <sup>(1)</sup>                         |

| Integrated UV Erase Dose7258 W-sec/cm <sup>2</sup>                                                 |

- \*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Note: 1. Minimum voltage is -0.6V DC which may undershoot to -2.0V for pulses of less than 20 ns.Maximum output pin voltage is  $V_{CC}$  + 0.75V DC which may overshoot to +7.0V for pulses of less than 20 ns.

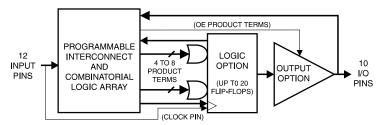

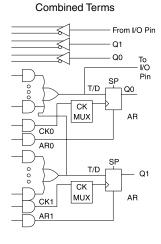

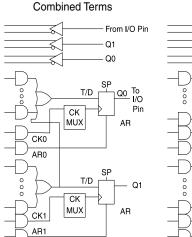

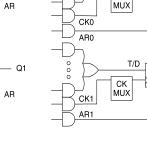

# **Logic Options**

#### **Combinatorial Output**

#### **Registered Output**

C T/D SP Q0 1/0 Pin

СК

Separate Terms

Pin

01

AR

AR

SP

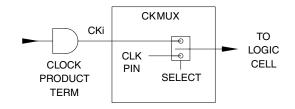

### **Clock Mux**

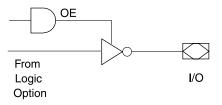

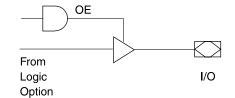

## **Output Options**

# DC and AC Operating Conditions<sup>(1)</sup>

|                              | Commercial<br>-7, -10, -15 | Commercial<br>-25       | Industrial                | Military                |

|------------------------------|----------------------------|-------------------------|---------------------------|-------------------------|

| Operating Temperature        | 0°C - 70°C<br>(Ambient)    | 0°C - 70°C<br>(Ambient) | -40°C - 85°C<br>(Ambient) | -55°C - 125°C<br>(Case) |

| V <sub>CC</sub> Power Supply | $5V \pm 5\%$               | $5V\pm10\%$             | 5V ± 10%                  | $5V\pm10\%$             |

Note: 1. See ordering information for valid speed and temperature combination.

### **DC** Characteristics

| Symbol                         | Parameter                       | Condition                                                                      | Condition                            |            |                       | Тур | Max                    | Units |

|--------------------------------|---------------------------------|--------------------------------------------------------------------------------|--------------------------------------|------------|-----------------------|-----|------------------------|-------|

| ILI                            | Input Load Current              | $V_{IN} = -0.1V$ to $V_{CC} + 1V$                                              |                                      |            |                       |     | 10                     | μA    |

| I <sub>LO</sub>                | Output Leakage<br>Current       | $V_{OUT} = -0.1 V$ to V                                                        | $V_{OUT} = -0.1V$ to $V_{CC} + 0.1V$ |            |                       |     | 10                     | μΑ    |

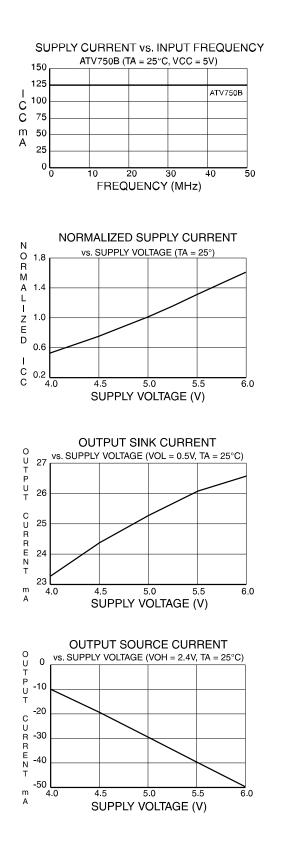

|                                |                                 |                                                                                |                                      | Com.       |                       | 125 | 180                    | mA    |

|                                |                                 |                                                                                | B-7, -10                             | Ind., Mil. |                       | 125 | 190                    | mA    |

|                                |                                 |                                                                                |                                      | Com.       |                       | 125 | 180                    | mA    |

|                                |                                 |                                                                                | B-15, -25                            | Ind., Mil. |                       | 125 | 190                    | mA    |

|                                | Power Supply                    | $V_{CC} = MAX,$<br>$V_{IN} = MAX,$                                             |                                      | Com.       |                       | 15  | 30                     | mA    |

| I <sub>cc</sub>                | Current, Standby                | Outputs Open                                                                   | BL-15                                | Ind., Mil. |                       | 15  | 30                     | mA    |

| I <sub>OS</sub> <sup>(1)</sup> | Output Short<br>Circuit Current | V <sub>OUT</sub> = 0.5V                                                        |                                      | 1          |                       |     | -120                   | mA    |

| V <sub>IL</sub>                | Input Low Voltage               | $4.5 \le V_{CC} \le 5.5 V$                                                     |                                      |            | -0.6                  |     | 0.8                    | V     |

| V <sub>IH</sub>                | Input High Voltage              |                                                                                |                                      |            | 2.0                   |     | V <sub>CC</sub> + 0.75 | V     |

|                                |                                 |                                                                                | I <sub>OL</sub> = 16 mA              | Com., Ind. |                       |     | 0.5                    | V     |

|                                | Output Low                      | $V_{IN} = V_{IH} \text{ or } V_{IL},$                                          | I <sub>OL</sub> = 12 mA              | Mil.       |                       |     | 0.5                    | V     |

| V <sub>OL</sub>                | Voltage                         | $V_{\rm IN} = V_{\rm IH}  \text{Or}  V_{\rm IL},$<br>$V_{\rm CC} = \text{MIN}$ | I <sub>OL</sub> = 24 mA              | Com.       |                       |     | 0.8                    | V     |

|                                | Output High                     | $V_{IN} = V_{IH} \text{ or } V_{IL},$                                          | I <sub>OH</sub> = -100 μA            |            | V <sub>CC</sub> - 0.3 |     |                        | V     |

| V <sub>OH</sub>                | Voltage                         | $V_{\rm IN} = V_{\rm IH} \text{ Or } V_{\rm IL},$<br>$V_{\rm CC} = \text{MIN}$ | I <sub>OH</sub> = -4.0 mA            |            | 2.4                   |     |                        | V     |

Note: 1. Not more than one output at a time should be shorted. Duration of short circuit test should not exceed 30 sec.

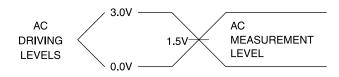

### **Input Test Waveforms and Measurement Levels**

$t_{\rm R}, t_{\rm F} < 3 \text{ ns} (10\% \text{ to } 90\%)$

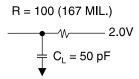

## **Output Test Load**

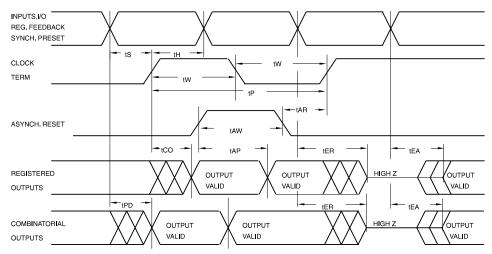

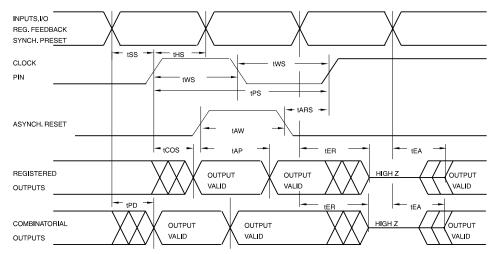

# AC Waveforms, Product Term Clock<sup>(1)</sup>

Note: 1. Timing measurement reference is 1.5V. Input AC driving levels are 0.0V and 3.0V, unless otherwise specified.

# AC Characteristics, Product Term Clock<sup>(1)</sup>

|                  |                                                         | -7  |     | -10 |     | B/BL-15 |       | B/BL-25 |     |       |

|------------------|---------------------------------------------------------|-----|-----|-----|-----|---------|-------|---------|-----|-------|

| Symbol           | Parameter                                               | Min | Max | Min | Max | Min     | Max   | Min     | Max | Units |

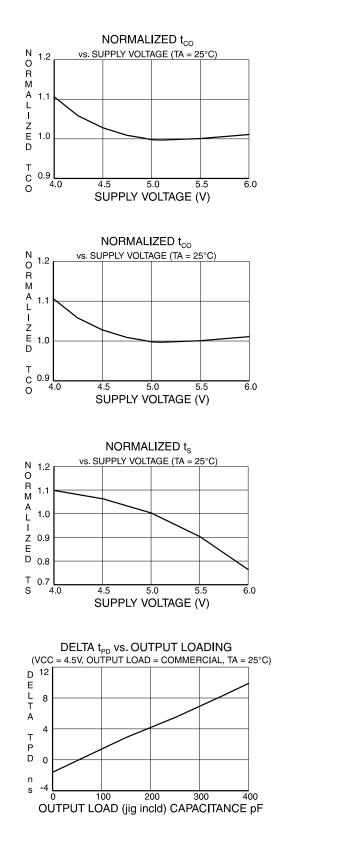

| t <sub>PD</sub>  | Input or Feedback to<br>Non-Registered Output           |     | 7.5 |     | 10  |         | 15    |         | 25  | ns    |

| t <sub>EA</sub>  | Input to Output Enable                                  |     | 7.5 |     | 10  |         | 15    |         | 25  | ns    |

| t <sub>ER</sub>  | Input to Output Disable                                 |     | 7.5 |     | 10  |         | 15    |         | 25  | ns    |

| t <sub>CO</sub>  | Clock to Output                                         | 3   | 7.5 | 4   | 10  | 5       | 12    | 6       | 20  | ns    |

| t <sub>CF</sub>  | Clock to Feedback                                       | 1   | 5   | 4   | 7.5 | 5       | 9     | 5       | 10  | ns    |

| t <sub>S</sub>   | Input Setup Time                                        | 3   |     | 4   |     | 8/12    |       | 14      |     | ns    |

| t <sub>SF</sub>  | Feedback Setup Time                                     | 3   |     | 4   |     | 7       |       | 7       |     | ns    |

| t <sub>H</sub>   | Hold Time                                               | 1   |     | 2   |     | 5/7     |       | 5/7     |     | ns    |

| t <sub>P</sub>   | Clock Period                                            | 7   |     | 11  |     | 14      |       | 17      |     | ns    |

| t <sub>w</sub>   | Clock Width                                             | 3.5 |     | 5.5 |     | 7       |       | 8.5     |     | ns    |

| f <sub>MAX</sub> | External Feedback 1/(t <sub>S</sub> +t <sub>CO</sub> )  |     | 95  |     | 71  |         | 50/41 |         | 29  | MHz   |

|                  | Internal Feedback 1/(t <sub>SF</sub> +t <sub>CF</sub> ) |     | 125 |     | 86  |         | 62    |         | 58  | MHz   |

|                  | No Feedback 1/(t <sub>P</sub> )                         |     | 142 |     | 90  |         | 71    |         | 58  | MHz   |

| t <sub>AW</sub>  | Asynchronous Reset Width                                | 5   |     | 10  |     | 15      |       | 20      |     | ns    |

| t <sub>AR</sub>  | Asynchronous Reset<br>Recovery Time                     | 3   |     | 10  |     | 15      |       | 20      |     | ns    |

| t <sub>AP</sub>  | Asynchronous Reset to<br>Registered Output Reset        |     | 8   |     | 12  |         | 15    |         | 25  | ns    |

| t <sub>SP</sub>  | Setup Time, Synchronous Preset                          | 4   |     | 7   |     | 8       |       | 15      |     | ns    |

Note: 1. See ordering information for valid part numbers.

# AC Waveforms, Input Pin Clock<sup>(1)</sup>

Note: 1. Timing measurement reference is 1.5V. Input AC driving levels are 0.0V and 3.0V, unless otherwise specified.

### **AC Characteristics, Input Pin Clock**

|                   |                                                           |     | -7  | -   | 10  |        | BL<br>5 |      | /BL<br>25 |       |

|-------------------|-----------------------------------------------------------|-----|-----|-----|-----|--------|---------|------|-----------|-------|

| Symbol            | Parameter                                                 | Min | Max | Min | Max | Min    | Мах     | Min  | Мах       | Units |

| t <sub>PD</sub>   | Input or Feedback to<br>Non-Registered Output             |     | 7.5 |     | 10  |        | 15      |      | 25        | ns    |

| t <sub>EA</sub>   | Input to Output Enable                                    |     | 7.5 |     | 10  |        | 15      |      | 25        | ns    |

| t <sub>ER</sub>   | Input to Output Disable                                   |     | 7.5 |     | 10  |        | 15      |      | 25        | ns    |

| t <sub>cos</sub>  | Clock to Output                                           | 0   | 6.5 | 0   | 7   | 0      | 10      | 0    | 12        | ns    |

| t <sub>CFS</sub>  | Clock to Feedback                                         | 0   | 3.5 | 0   | 5   | 0      | 5.5     | 0    | 7         | ns    |

| t <sub>SS</sub>   | Input Setup Time                                          | 4   |     | 6.5 |     | 8/12.5 |         | 9/15 |           | ns    |

| t <sub>SFS</sub>  | Feedback Setup Time                                       | 4   |     | 5   |     | 7      |         | 9    |           | ns    |

| t <sub>HS</sub>   | Hold Time                                                 | 0   |     | 0   |     | 0      |         | 0    |           | ns    |

| t <sub>PS</sub>   | Clock Period                                              | 7   |     | 10  |     | 12     |         | 16   |           | ns    |

| t <sub>ws</sub>   | Clock Width                                               | 3.5 |     | 5   |     | 6      |         | 8    |           | ns    |

| f <sub>MAXS</sub> | External Feedback 1/(t <sub>SS</sub> +t <sub>COS</sub> )  |     | 95  |     | 74  |        | 55/44   |      | 48/37     | MHz   |

|                   | Internal Feedback 1/(t <sub>SFS</sub> +t <sub>CFS</sub> ) |     | 133 |     | 100 |        | 80      |      | 62        | MHz   |

|                   | No Feedback 1/(t <sub>PS</sub> )                          |     | 142 |     | 100 |        | 83      |      | 62        | MHz   |

| t <sub>AW</sub>   | Asynchronous Reset Width                                  | 5   |     | 10  |     | 15     |         | 20   |           | ns    |

| t <sub>ARS</sub>  | Asynchronous Reset<br>Recovery Time                       | 5   |     | 10  |     | 15     |         | 25   |           | ns    |

| t <sub>AP</sub>   | Asynchronous Reset to<br>Registered Output Reset          |     | 8   |     | 10  |        | 15      |      | 25        | ns    |

| t <sub>SPS</sub>  | Setup Time, Synchronous Preset                            | 5   |     | 5/9 |     | 11     |         | 15   |           | ns    |

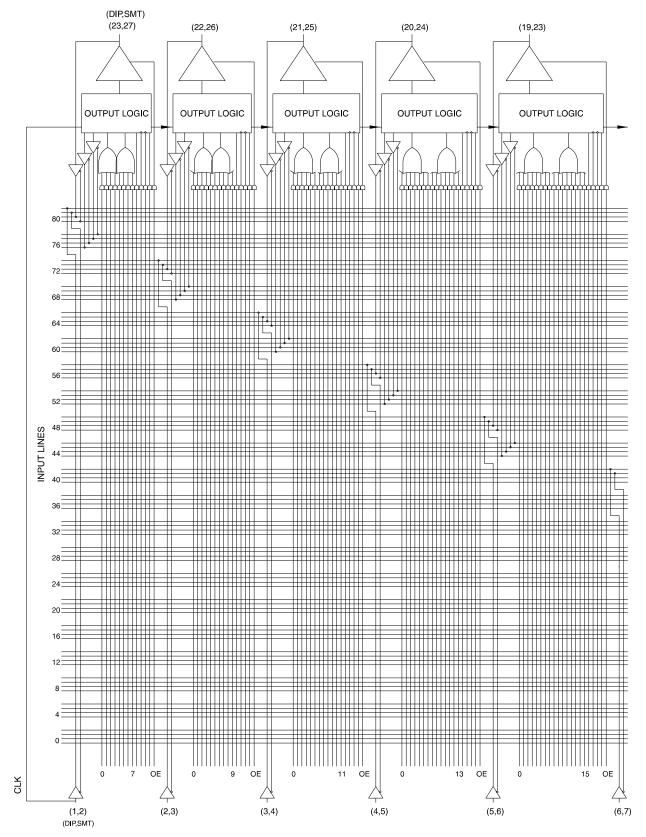

### Functional Logic Diagram ATV750B, Upper Half

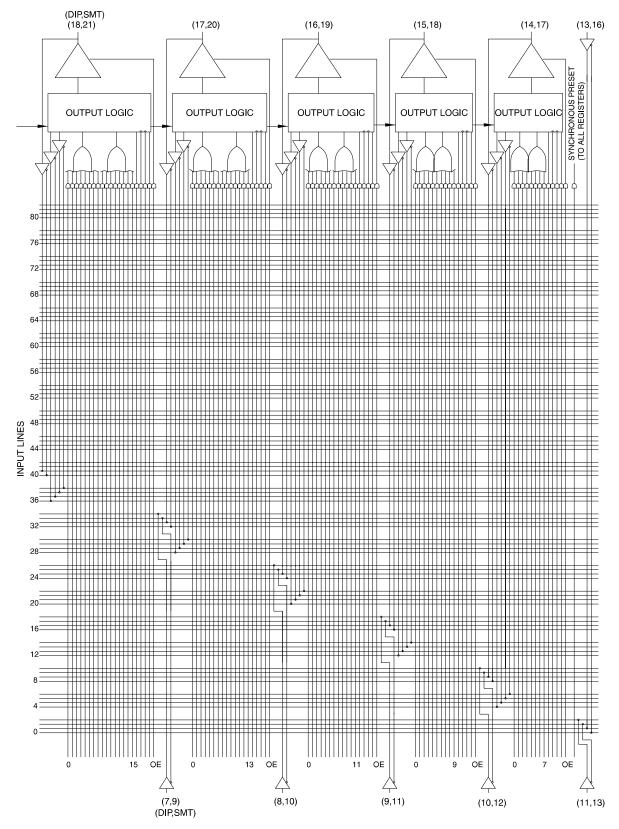

### Functional Logic Diagram ATV750B, Lower Half

8 ATV750B(L)

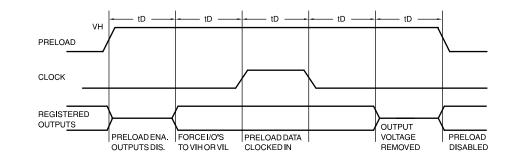

## Preload of Registered Outputs

The ATV750B(L) registers are provided with circuitry to allow loading of each register asynchronously with either a high or a low. This feature will simplify testing since any state can be forced into the registers to control test sequencing. A V<sub>IH</sub> level on the I/O pin will force the register high; a V<sub>IL</sub> will force it low, independent of the output polarity. The PRELOAD state is entered by placing a 10.25V to 10.75V signal on pin 8 on DIPs, and lead 10 on SMDs. When the clock term is pulsed high, the data on the I/O pins is placed into the register chosen by the Select Pin.

| Level Forced on Registered<br>Output Pin during<br>PRELOAD Cycle | Select Pin<br>State | Register #0 State after<br>Cycle | Register #1 State after<br>Cycle |

|------------------------------------------------------------------|---------------------|----------------------------------|----------------------------------|

| V <sub>IH</sub>                                                  | Low                 | High                             | Х                                |

| V <sub>IL</sub>                                                  | Low                 | Low                              | Х                                |

| V <sub>IH</sub>                                                  | High                | Х                                | High                             |

| V <sub>IL</sub>                                                  | High                | Х                                | Low                              |

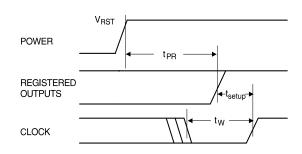

#### **Power-up Reset**

The registers in the ATV750B(L) is designed to reset during power-up. At a point delayed slightly from  $V_{CC}$  crossing  $V_{RST}$ , all registers will be reset to the low state. The output state will depend on the polarity of the output buffer.

This feature is critical for state machine initialization. However, due to the asynchronous nature of reset and the uncertainty of how  $V_{CC}$  actually rises in the system, the following conditions are required:

- 1. The  $V_{CC}$  rise must be monotonic,

- 2. After reset occurs, all input and feedback setup times must be met before driving the clock terms or pin high, and

- 3. The clock pin, or signals from which clock terms are derived, must remain stable during  $t_{\mbox{\scriptsize PR}}.$

| Parameter        | Description            | Тур | Мах  | Units |

|------------------|------------------------|-----|------|-------|

| t <sub>PR</sub>  | Power-up Reset Time    | 600 | 1000 | ns    |

| V <sub>RST</sub> | Power-up Reset Voltage | 3.8 | 4.5  | V     |

### **Pin Capacitance**

$f = 1 \text{ MHz}, T = 25^{\circ}C^{(1)}$

|                  | Тур | Max | Units | Conditions     |

|------------------|-----|-----|-------|----------------|

| C <sub>IN</sub>  | 5   | 8   | pF    | $V_{IN} = 0V$  |

| C <sub>OUT</sub> | 6   | 8   | pF    | $V_{OUT} = 0V$ |

#### Using the ATV750B(L) Many Advanced Features

The ATV750B(L) advanced flexibility packs more usable gates into 24-pins than any other logic device. The ATV750B(L) starts with the popular 22V10 architecture, and add several enhanced features:

- Selectable D- and T-type Registers Each ATV750B flip-flop can be individually configured as either D- or T-type. Using the T-type configuration, JK and SR flip-flops are also easily created. These options allow more efficient product term usage.

- Selectable Asynchronous Clocks Each of the ATV750B(L) flip-flops may be clocked by its own clock product term or directly from Pin 1 (SMD Lead 2). This removes the constraint that all registers must use the same clock. Buried state machines, counters and registers can all coexist in one device while running on separate clocks. Individual flip-flop clock source selection further allows mixing higher performance pin clocking and flexible product term clocking within one design.

- A Full Bank of Ten More Registers The ATV750B provides two flip-flops per output logic cell for a total of 20. Each register has its own sum term, its own reset term and its own clock term.

- Independent I/O Pin and Feedback Paths Each I/O pin on the ATV750B has a dedicated input path. Each of the 20 registers has its own feedback terms into the array as well. This feature, combined with individual product terms for each I/O's output enable, facilitates true bi-directional I/O design.

| Programming<br>Software<br>Support        | As with all other Atmel PLDs, several third-party development software products support the ATV750B(L). Several third-party programmers support the ATV750B as well. Additionally, the ATV750B may be programmed to perform the ATV750(L)'s functional subset (no T-type flip-<br>flops or pin clocking) using the ATV750(L) JEDEC file. In this case, the ATV750B becomes a<br>direct replacement or speed upgrade for the ATV750(L). The ATV750(L) programming algo-<br>rithm is different from the ATV750B algorithm. Choose the appropriate device in your<br>programmer menu to ensure proper programming. Please refer to the <i>Programmable Logic</i><br><i>Development Tools</i> section for a complete PLD software and programmer listing. |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synchronous<br>Preset and<br>Asynchronous | One synchronous preset line is provided for all 20 registers in the ATV750B. The appropriate input signals to cause the internal clocks to go to a high state must be received during a syn-<br>chronous preset. Appropriate setup and hold times must be met, as shown in the switching waveform diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reset                                     | An individual asynchronous reset line is provided for each of the 20 flip-flops. Both master and slave halves of the flip-flops are reset when the input signals received force the internal resets high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Security Fuse<br>Usage                    | A single fuse is provided to prevent unauthorized copying of the ATV750B fuse patterns. Once the security fuse is programmed, all fuses will appear programmed during verify.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                           | The security fuse should be programmed last, as its effect is immediate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### Erasure Characteristics

The entire memory array of an ATV750B is erased after exposure to ultraviolet light at a wavelength of 2537 Å. Complete erasure is assured after a minimum of 20 minutes exposure using 12,000  $\mu$ W/cm<sup>2</sup> intensity lamps spaced one inch away from the chip. Minimum erase time for lamps at other intensity ratings can be calculated from the minimum integrated erasure dose of 15 W-sec/cm<sup>2</sup>. To prevent unintentional erasure, an opaque label is recommended to cover the clear window on any UV-erasable PLD which will be subjected to continuous fluorescent indoor lighting or sunlight.

### Atmel CMOS PLDs

The ATV750B utilizes an advanced 0.65-micron CMOS EPROM technology. This technology's state-of-art features are the optimum combination for PLDs:

- CMOS technology provides high-speed, low-power, and high noise immunity.

- EPROM technology is the most cos-effective method for producing PLDs surpassing bipolar fusible link technology in low cost, while providing the necessary reprogrammability.

- EPROM reprogrammability, which is 100% tested before shipment, provides inherently better programmability and reliability than one-time fusible PLDs.

# **Ordering Information**

| t <sub>PD</sub><br>(ns) | t <sub>cos</sub><br>(ns) | Ext.<br>f <sub>MAXS</sub><br>(MHz) | Ordering Code                                                                             | Package            | Operation Range                                               |

|-------------------------|--------------------------|------------------------------------|-------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------|

| 7.5                     | 6.5                      | 95                                 | ATV750B-7JC <sup>(1)</sup><br>ATV750B-7PC <sup>(1)</sup>                                  | 28J<br>24P3        | Commercial<br>(0°C to 70°C)                                   |

| 10                      | 7                        | 74                                 | ATV750B-10JC <sup>(1)</sup><br>ATV750B-10PC <sup>(1)</sup><br>ATV750B-10SC <sup>(1)</sup> | 28J<br>24P3<br>24S | Commercial<br>(0°C to 70°C)                                   |

|                         |                          |                                    | ATV750B-10JI <sup>(1)</sup><br>ATV750B-10PI <sup>(1)</sup><br>ATV750B-10SI <sup>(1)</sup> | 28J<br>24P3<br>24S | Industrial<br>(-40°C to 85°C)                                 |

|                         |                          |                                    | ATV750B-10DM/883 <sup>(2)</sup><br>ATV750B-10LM/883 <sup>(2)</sup>                        | 24DW3<br>28LW      | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

| 15                      | 10                       | 58                                 | ATV750B-15JC <sup>(1)</sup><br>ATV750B-15PC <sup>(1)</sup><br>ATV750B-15SC <sup>(1)</sup> | 28J<br>24P3<br>24S | Commercial<br>(0°C to 70°C)                                   |

|                         |                          |                                    | ATV750B-15JI <sup>(1)</sup><br>ATV750B-15PI <sup>(1)</sup><br>ATV750B-15SI <sup>(1)</sup> | 28J<br>24P3<br>24S | Industrial<br>(-40°C to 85°C)                                 |

|                         |                          |                                    | ATV750B-15DM/883 <sup>(2)</sup><br>ATV750B-15LM/883 <sup>(2)</sup>                        | 24DW3<br>28LW      | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

| 25                      | 15                       | 41                                 | ATV750B-25JC <sup>(1)</sup><br>ATV750B-25PC <sup>(1)</sup><br>ATV750B-25SC <sup>(1)</sup> | 28J<br>24P3<br>24S | Commercial<br>(0°C to 70°C)                                   |

|                         |                          |                                    | ATV750B-25JI <sup>(1)</sup><br>ATV750B-25PI <sup>(1)</sup><br>ATV750B-25SI <sup>(1)</sup> | 28J<br>24P3<br>24S | Industrial<br>(-40°C to 85°C)                                 |

| 10                      | 7                        | 74                                 | 5962-88726 08 LA <sup>(2)</sup><br>5962-88726 08 3X <sup>(2)</sup>                        | 24DW3<br>28LW      | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

| 15                      | 9                        | 58                                 | 5962-88726 09 LA <sup>(2)</sup><br>5962-88726 09 3X <sup>(2)</sup>                        | 24DW3<br>28LW      | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

Notes: 1. Obsolete, please use ATF750C versions.

2. Continue to be available, but please do not use for new designs. For new designs recommend multiple ATF22V10s.

### **Ordering Information (Continued)**

| t <sub>PD</sub><br>(ns) | t <sub>cos</sub><br>(ns) | Ext.<br>f <sub>MAXS</sub><br>(MHz) | Ordering Code                                                                                | Package            | Operation Range                                               |

|-------------------------|--------------------------|------------------------------------|----------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------|

| 15                      | 9                        | 92                                 | ATV750BL-15JC <sup>(1)</sup><br>ATV750BL-15PC <sup>(1)</sup><br>ATV750BL-15SC <sup>(1)</sup> | 28J<br>24P3<br>24S | Commercial<br>(0°C to 70°C)                                   |

|                         |                          |                                    | ATV750BL-15JI <sup>(1)</sup><br>ATV750BL-15PI <sup>(1)</sup><br>ATV750BL-15SI <sup>(1)</sup> | 28J<br>24P3<br>24S | Industrial<br>(-40°C to 85°C)                                 |

|                         |                          |                                    | ATV750BL-15DM/883 <sup>(2)</sup><br>ATV750BL-15LM/883 <sup>(2)</sup>                         | 24DW3<br>28LW      | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

| 25                      | 15                       | 37                                 | ATV750BL-25JC <sup>(1)</sup><br>ATV750BL-25PC <sup>(1)</sup><br>ATV750BL-25SC <sup>(1)</sup> | 28J<br>24P3<br>24S | Commercial<br>(0°C to 70°C)                                   |

|                         |                          |                                    | ATV750BL-25JI19<br>ATV750BL-25PI <sup>(1)</sup><br>ATV750BL-25SI <sup>(1)</sup>              | 28J<br>24P3<br>24S | Industrial<br>(-40°C to 85°C)                                 |

| 15                      | 9                        | 92                                 | 5962-88726 11 LX <sup>(2)</sup><br>5962-88726 11 3X <sup>(2)</sup>                           | 24DW3<br>28LW      | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

Notes: 1. Obsolete, please use ATF750C versions.

2. Continue to be available, but please do not use for new designs. For new designs recommend multiple ATF22V10s.

### Using "C" Product for Industrial

To use commercial product for Industrial temperature ranges, down-grade one speed grade from the "I" to the "C" device (7 ns "C" = 10 ns "I") and de-rate power by 30%.

| Package Type |                                                                      |  |  |  |  |

|--------------|----------------------------------------------------------------------|--|--|--|--|

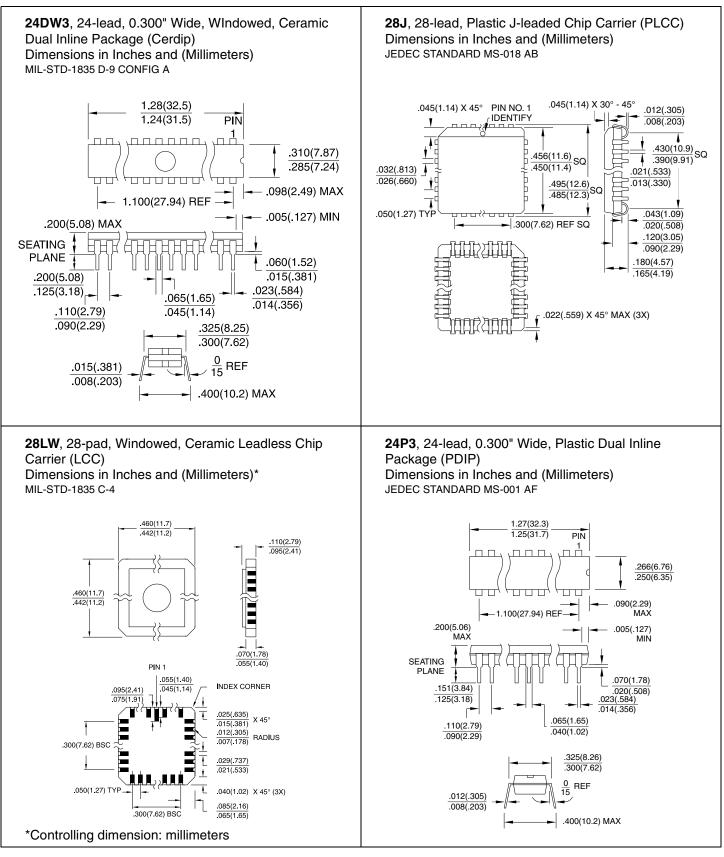

| 24DW3        | 24-lead, 0.300" Wide, Windowed, Ceramic Dual Inline Package (Cerdip) |  |  |  |  |

| 28J          | 28-lead, Plastic J-leaded Chip Carrier OTP (PLCC)                    |  |  |  |  |

| 28LW         | 28-pad, Windowed, Ceramic Leadless Chip Carrier (LCC)                |  |  |  |  |

| 24P3         | 24-lead, 0.300" Wide, Plastic Dual Inline Package OTP (PDIP)         |  |  |  |  |

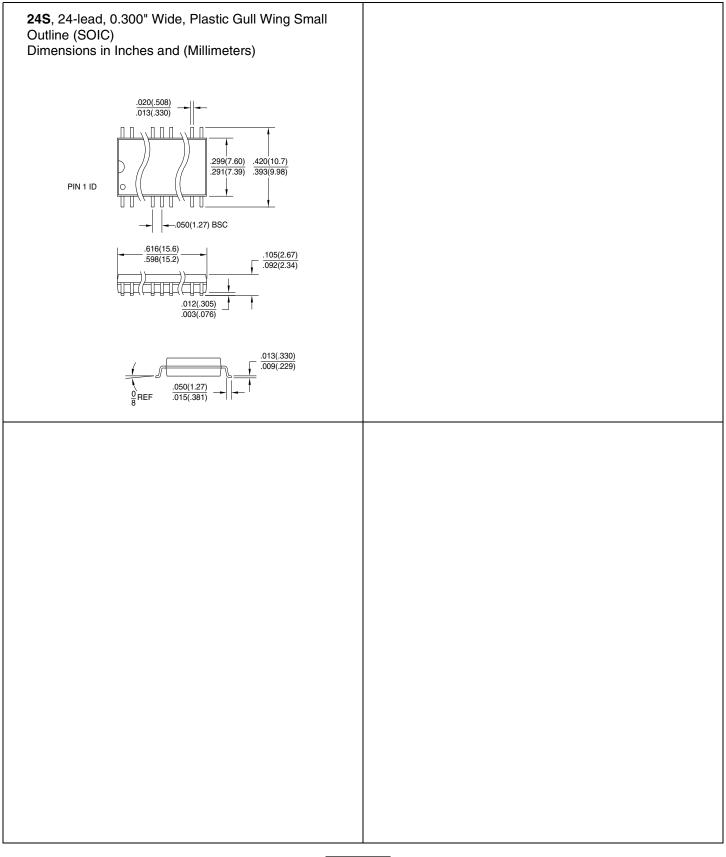

| 24S          | 24-lead, 0.300" Wide, Plastic Gull Wing Small Outline OTP (SOIC)     |  |  |  |  |

### **Packaging Information**

### **Packaging Information**

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Product Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

#### Atmel Heilbronn

Theresienstrasse 2 POB 3535 D-74025 Heilbronn, Germany TEL (49) 71 31 67 25 94 FAX (49) 71 31 67 24 23

#### Atmel Nantes

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 0 2 40 18 18 18 FAX (33) 0 2 40 18 19 60

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

#### Atmel Smart Card ICs

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

> *e-mail* literature@atmel.com

> Web Site http://www.atmel.com

BBS 1-(408) 436-4309

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL<sup>®</sup> is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.