Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | LINbusSCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 48                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f361ar7t3 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **6.4 SYSTEM INTEGRITY MANAGEMENT (SI)**

The System Integrity Management block contains the Low Voltage Detector (LVD) and Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

## 6.4.1 Low Voltage Detector (LVD)

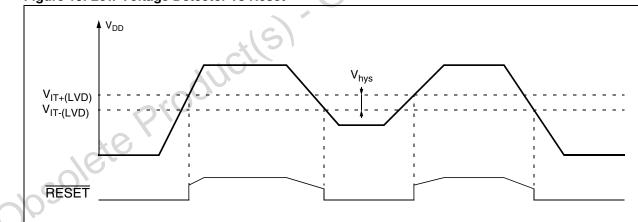

The Low Voltage Detector function (LVD) generates a static reset when the V<sub>DD</sub> supply voltage is below a V<sub>IT-(LVD)</sub> reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The V<sub>IT-(LVD)</sub> reference value for a voltage drop is lower than the V<sub>IT+(LVD)</sub> reference value for poweron in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{DD}$  is below:

- $V_{IT+(LVD)}$  when  $V_{DD}$  is rising

- $-V_{IT-(LVD)}$  when  $V_{DD}$  is falling

The LVD function is illustrated in Figure 15.

Figure 15. Low Voltage Detector vs Reset

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{\text{IT-(LVD)}},$  the MCU can only be in two modes:

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### Notes:

The LVD allows the device to be used without any external RESET circuitry.

The LVD is an optional function which can be selected by option byte.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

**67/**

#### INTERRUPTS (Cont'd)

# 7.3 INTERRUPTS AND LOW POWER MODES

All interrupts allow the processor to exit the WAIT low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the HALT modes (see column "Exit from HALT" in "Interrupt Mapping" table). When several pending interrupts are present while exiting HALT mode, the first one serviced can only be an interrupt with exit from HALT mode capability and it is selected through the same decision process shown in Figure 18.

**Note:** If an interrupt, that is not able to Exit from HALT mode, is pending with the highest priority when exiting HALT mode, this interrupt is serviced after the first one serviced.

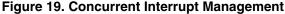

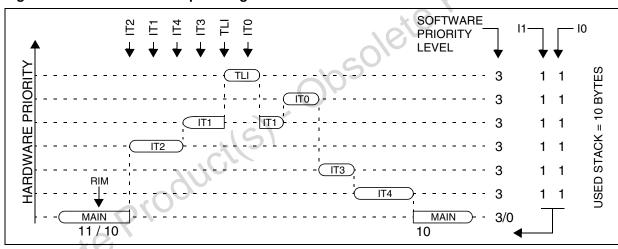

# 7.4 CONCURRENT & NESTED MANAGEMENT

The following Figure 19 and Figure 20 show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in Figure 20. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0, TLI. The software priority is given for each interrupt.

**Warning**: A stack overflow may occur without notifying the software of the failure.

Figure 20. Nested Interrupt Management

# I/O PORTS (Cont'd)

# Table 14. Port Configuration

| Port   | Pin name |                | put                      | Output     |          |  |

|--------|----------|----------------|--------------------------|------------|----------|--|

| Port   | Pin name | OR = 0         | OR = 1                   | OR = 0     | OR = 1   |  |

|        | PA0      |                | pull-up interrupt (ei0)  |            |          |  |

|        | PA1      |                | floating interrupt (ei0) |            |          |  |

|        | PA2      |                | pull-up interrupt (ei0)  |            |          |  |

| Port A | PA3      | floating       | floating interrupt (ei0) | onon drain | puch pu  |  |

| POILA  | PA4      | floating       | pull-up interrupt (ei0)  | open drain | push-pu  |  |

|        | PA5      |                | floating interrupt (ei0) |            |          |  |

|        | PA6      |                | pull-up interrupt (ei0)  |            |          |  |

|        | PA7      |                | floating interrupt (ei0) |            | 15       |  |

|        | PB0      |                | pull-up interrupt (ei1)  |            | <u> </u> |  |

|        | PB1      |                | floating interrupt (ei1) |            |          |  |

| Port B | PB2      | fleation       | pull-up interrupt (ei1)  | open drain |          |  |

| Port B | PB3      | floating       | floating interrupt (ei1) | open drain | push-pu  |  |

|        | PB4      |                | pull-up interrupt (ei1)  | 01         |          |  |

|        | PB5      |                | floating interrupt (ei1) |            |          |  |

|        | PC0      |                | pull-up                  | (0)        |          |  |

|        | PC1      | fleation       | pull-up interrupt (ei2)  | open drain |          |  |

| Port C | PC2      | floating       | floating interrupt (ei2) | open drain | push-pu  |  |

| PontC  | PC3      |                | pull-up                  |            |          |  |

|        | PC4      | pu             | ll-up                    | N/         | A        |  |

|        | PC7:5    | floating       | pull-up                  | open drain | push-pu  |  |

|        | PD0      |                | pull-up interrupt (ei3)  |            |          |  |

|        | PD1      | 15             | floating interrupt (ei3) |            |          |  |

|        | PD3:2    |                | pull-up                  |            |          |  |

| Port D | PD4      | floating       | floating interrupt (ei3) | open drain | push-pu  |  |

|        | PD5      |                | pull-up                  |            |          |  |

|        | PD6      |                | pull-up interrupt (ei3)  |            |          |  |

|        | PD7      |                | floating interrupt (ei3) |            |          |  |

| Port E | PE7:0    | floating (TTL) | pull-up (TTL)            | open drain | push-pu  |  |

| TORE   | PF7:0    | floating (TTL) | pull-up (TTL)            | open drain | push-pu  |  |

# 16-BIT TIMER (Cont'd)

# 10.4.3.3 Input Capture

In this section, the index, *i*, may be 1 or 2 because there are two input capture functions in the 16-bit timer.

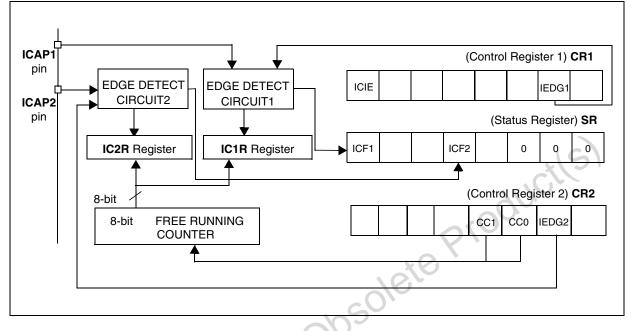

The two 16-bit input capture registers (IC1R and IC2R) are used to latch the value of the free running counter after a transition is detected on the ICAP*i* pin (see Figure 52).

|      | MS Byte        | LS Byte        |

|------|----------------|----------------|

| ICiR | IC <i>i</i> HR | IC <i>i</i> LR |

IC*i*R register is a read-only register.

The active transition is software programmable through the IEDG*i* bit of Control Registers (CR*i*).

Timing resolution is one count of the free running counter:  $(f_{CPU}/CC[1:0])$ .

## Procedure:

To use the input capture function select the following in the CR2 register:

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

- Select the edge of the active transition on the ICAP2 pin with the IEDG2 bit (the ICAP2 pin must be configured as floating input or input with pull-up without interrupt if this configuration is available).

And select the following in the CR1 register:

- Set the ICIE bit to generate an interrupt after an input capture coming from either the ICAP1 pin or the ICAP2 pin

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1pin must be configured as floating input or input with pullup without interrupt if this configuration is available).

When an input capture occurs:

- ICF*i* bit is set.

- The IC*i*R register contains the value of the free running counter on the active transition on the ICAP*i* pin (see Figure 53).

- A timer interrupt is generated if the ICIE bit is set and the I bit is cleared in the CC register. Otherwise, the interrupt remains pending until both conditions become true.

Clearing the Input Capture interrupt request (that is, clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set.

- 2. An access (read or write) to the ICiLR register.

#### Notes:

- 1. After reading the IC*i*HR register, transfer of input capture data is inhibited and ICF*i* will never be set until the IC*i*LR register is also read.

- 2. The IC/R register contains the free running counter value which corresponds to the most recent input capture.

- 3. The two input capture functions can be used together even if the timer also uses the two output compare functions.

- 4. In One Pulse mode and PWM mode only Input Capture 2 can be used.

- 5. The alternate inputs (ICAP1 and ICAP2) are always directly connected to the timer. So any transitions on these pins activates the input capture function. Moreover if one of the ICAP*i* pins is configured as an input and the second one as an output, an interrupt can be generated if the user tog-

gles the output pin and if the ICIE bit is set. This can be avoided if the input capture function *i* is disabled by reading the IC*i*HR (see note 1).

6. The TOF bit can be used with interrupt generation in order to measure events that go beyond the timer range (FFFFh).

**/**

# 8-BIT TIMER (Cont'd)

# Figure 63. Input Capture Block Diagram

# Figure 64. Input Capture Timing Diagram

|   | COUNTER REGISTER 01 X 02 X 03 X                  |  |

|---|--------------------------------------------------|--|

|   | ICAPI PIN                                        |  |

| 1 | ICAPI REGISTER                                   |  |

|   | <b>Note:</b> The rising edge is the active edge. |  |

57

# 8-BIT TIMER (Cont'd) 10.5.8 8-bit Timer Register Map

## **ON-CHIP PERIPHERALS** (cont'd)

## **10.6 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 10.6.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 10.6.2 Main Features

- Full duplex synchronous transfers (on three lines)

- Simplex synchronous transfers (on two lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

Note: In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### **10.6.3 General Description**

Figure 70 on page 110 shows the serial peripheral interface (SPI) block diagram. There are three registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through four pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

# SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.4 Clock Phase and Clock Polarity

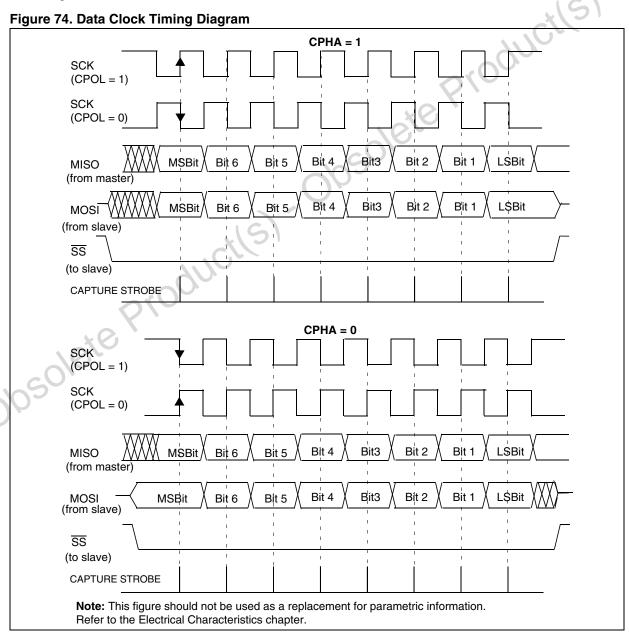

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 74).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge.

Figure 74 shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin and the MOSI pin are directly connected between the master and the slave device.

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

# **/**

#### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Mode)

#### 10.7.9 LIN Mode - Functional Description.

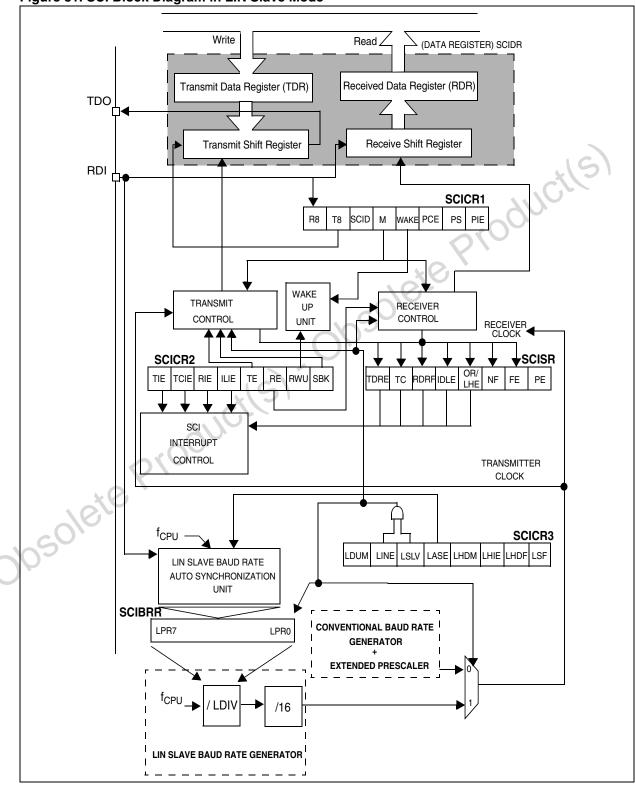

The block diagram of the Serial Control Interface, in LIN slave mode is shown in Figure 5.

It uses six registers:

- 3 control registers: SCICR1, SCICR2 and SCICR3

- 2 status registers: the SCISR register and the LHLR register mapped at the SCIERPR address

- A baud rate register: LPR mapped at the SCI-BRR address and an associated fraction register LPFR mapped at the SCIETPR address

The bits dedicated to LIN are located in the SCICR3. Refer to the register descriptions in Section 0.1.10 for the definitions of each bit.

#### 10.7.9.1 Entering LIN Mode

To use the LINSCI in LIN mode the following configuration must be set in SCICR3 register:

- Clear the M bit to configure 8-bit word length.

- Set the LINE bit.

#### Master

To enter master mode the LSLV bit must be reset In this case, setting the SBK bit will send 13 low bits.

Then the baud rate can programmed using the SCIBRR, SCIERPR and SCIETPR registers.

In LIN master mode, the Conventional and / or Extended Prescaler define the baud rate (as in standard SCI mode)

#### Slave

Set the LSLV bit in the SCICR3 register to enter LIN slave mode. In this case, setting the SBK bit will have no effect.

In LIN Slave mode the LIN baud rate generator is selected instead of the Conventional or Extended Prescaler. The LIN baud rate generator is common to the transmitter and the receiver.

Then the baud rate can be programmed using LPR and LPRF registers.

**Note:** It is mandatory to set the LIN configuration first before programming LPR and LPRF, because the LIN configuration uses a different baud rate generator from the standard one.

#### 10.7.9.2 LIN Transmission

In LIN mode the same procedure as in SCI mode has to be applied for a LIN transmission.

To transmit the LIN Header the proceed as follows:

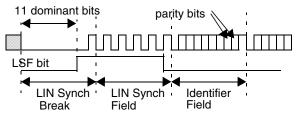

- First set the SBK bit in the SCICR2 register to start transmitting a 13-bit LIN Synch Break

- reset the SBK bit

- Load the LIN Synch Field (0x55) in the SCIDR register to request Synch Field transmission

- Wait until the SCIDR is empty (TDRE bit set in the SCISR register)

- Load the LIN message Identifier in the SCIDR register to request Identifier transmission.

<u>لرک</u>

# LINSCI<sup>™</sup> SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd) Figure 81. SCI Block Diagram in LIN Slave Mode

57

137/225

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.9 Error due to LIN Synch measurement

The LIN Synch Field is measured over eight bit times.

This measurement is performed using a counter clocked by the CPU clock. The edge detections are performed using the CPU clock cycle.

This leads to a precision of 2 CPU clock cycles for the measurement which lasts 16\*8\*LDIV clock cycles.

Consequently, this error (D<sub>MEAS</sub>) is equal to:

2 / (128\*LDIV<sub>MIN</sub>).

$LDIV_{MIN}$  corresponds to the minimum LIN prescaler content, leading to the maximum baud rate, taking into account the maximum deviation of +/-15%.

#### 10.7.9.10 Error due to Baud Rate Quantization

The baud rate can be adjusted in steps of 1 / (16 \* LDIV). The worst case occurs when the "real" baud rate is in the middle of the step.

This leads to a quantization error ( $D_{QUANT}$ ) equal to 1 / (2\*16\*LDIV<sub>MIN</sub>).

#### 10.7.9.11 Impact of Clock Deviation on Maximum Baud Rate

The choice of the nominal baud rate (LDIV<sub>NOM</sub>) will influence both the quantization error ( $D_{QUANT}$ ) and the measurement error ( $D_{MEAS}$ ). The worst case occurs for LDIV<sub>MIN</sub>.

Consequently, at a given CPU frequency, the maximum possible nominal baud rate (LPR<sub>MIN</sub>) should be chosen with respect to the maximum tolerated deviation given by the equation:

D<sub>TRA</sub> + 2 / (128\*LDIV<sub>MIN</sub>) + 1 / (2\*16\*LDIV<sub>MIN</sub>)

$+ D_{REC} + D_{TCL} < 3.75\%$

#### Example:

A nominal baud rate of 20Kbits/s at  $T_{CPU}$  = 125ns (8 MHz) leads to LDIV<sub>NOM</sub> = 25d.

LDIV<sub>MIN</sub> = 25 - 0.15\*25 = 21.25

D<sub>MEAS</sub> = 2 / (128\*LDIV<sub>MIN</sub>) \* 100 = 0.00073%

$D_{QUANT} = 1 / (2*16*LDIV_{MIN}) * 100 = 0.0015\%$

#### LIN Slave systems

For LIN Slave systems (the LINE and LSLV bits are set), receivers wake up by LIN Synch Break or LIN Identifier detection (depending on the LHDM bit).

#### Hot Plugging Feature for LIN Slave Nodes

In LIN Slave Mute Mode (the LINE, LSLV and RWU bits are set) it is possible to hot plug to a network during an ongoing communication flow. In this case the SCI monitors the bus on the RDI line until 11 consecutive dominant bits have been detected and discards all the other bits received.

## LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

SCICR2 register is set, the LHDM bit selects the Wake-Up method (replacing the WAKE bit). 0: LIN Synch Break Detection Method 1: LIN Identifier Field Detection Method

Bit 2 = LHIE LIN Header Interrupt Enable

This bit is set and cleared by software. It is only usable in LIN Slave mode.

0: LIN Header Interrupt is inhibited.

1: An SCI interrupt is generated whenever LHDF = 1.

Bit 1 = LHDF LIN Header Detection Flag

This bit is set by hardware when a LIN Header is detected and cleared by a software sequence (an access to the SCISR register followed by a read of the SCICR3 register). It is only usable in LIN Slave mode.

0: No LIN Header detected.

1: LIN Header detected.

**Notes:** The header detection method depends on the LHDM bit:

- If LHDM = 0, a header is detected as a LIN Synch Break.

- If LHDM = 1, a header is detected as a LIN Identifier, meaning that a LIN Synch Break Field + a LIN Synch Field + a LIN Identifier Field have been consecutively received.

#### Bit 0 = LSF LIN Synch Field State

This bit indicates that the LIN Synch Field is being analyzed. It is only used in LIN Slave mode. In Auto Synchronization Mode (LASE bit = 1), when the SCI is in the LIN Synch Field State it waits or counts the falling edges on the RDI line.

It is set by hardware as soon as a LIN Synch Break is detected and cleared by hardware when the LIN Synch Field analysis is finished (see Figure 11). This bit can also be cleared by software to exit LIN Synch State and return to idle mode.

0: The current character is not the LIN Synch Field

1: LIN Synch Field State (LIN Synch Field undergoing analysis)

## LIN DIVIDER REGISTERS

LDIV is coded using the two registers LPR and LP-FR. In LIN Slave mode, the LPR register is accessible at the address of the SCIBRR register and the LPFR register is accessible at the address of the SCIETPR register.

#### LIN PRESCALER REGISTER (LPR) Read/Write

Reset Value: 0000 0000 (00h)

| 70   | 0.   |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| LPR7 | LPR6 | LPR5 | LPR4 | LPR3 | LPR2 | LPR1 | LPR0 |

#### LPR[7:0] LIN Prescaler (mantissa of LDIV)

These 8 bits define the value of the mantissa of the LIN Divider (LDIV):

| LPR[7:0] | Rounded Mantissa (LDIV) |

|----------|-------------------------|

| 00h      | SCI clock disabled      |

| 01h      | 1                       |

|          |                         |

| FEh      | 254                     |

| FFh      | 255                     |

**Caution:** LPR and LPFR registers have different meanings when reading or writing to them. Consequently bit manipulation instructions (BRES or BSET) should never be used to modify the LPR[7:0] bits, or the LPFR[3:0] bits.

57

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd) CONTROL REGISTER 2 (SCICR2)

Λ

#### Read/Write

Reset Value: 0000 0000 (00h)

7

| '   |      |     |      |    |    |     | Ũ   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TDRE = 1 in the SCISR register

Bit 6 = **TCIE** *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC = 1 in the SCISR register

Bit 5 = **RIE** *Receiver interrupt enable.*

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR = 1 or RDRF = 1 in the SCISR register

Bit 4 = ILIE Idle line interrupt enable.

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE = 1 in the SCISR register.

# Bit 3 = **TE** Transmitter enable.

This bit enables the transmitter. It is set and cleared by software.

- 0: Transmitter is disabled

- 1: Transmitter is enabled

# Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

#### Bit 2 = RE Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

#### Bit 1 = RWU Receiver wake-up.

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

0: Receiver in active mode

1: Receiver in mute mode

## Notes:

- Before selecting Mute mode (by setting the RWU bit) the SCI must first receive a data byte, otherwise it cannot function in Mute mode with wakeup by Idle line detection.

- In Address Mark Detection Wake-Up configuration (WAKE bit = 1) the RWU bit cannot be modified by software while the RDRF bit is set.

#### Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

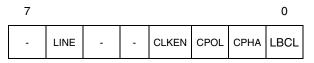

# **CONTROL REGISTER 3 (SCICR3)**

## Read/Write

Reset Value: 0000 0000 (00h)

Bit 7 = Reserved, must be kept cleared.

#### Bit 6 = LINE LIN Mode Enable.

This bit is set and cleared by software. 0: LIN Mode disabled 1: LIN Master mode enabled

The LIN Master mode enables the capability to send LIN Synch Breaks (13 low bits) using the SBK bit in the SCICR2 register

.In transmission, the LIN Synch Break low phase duration is shown as below:

| LINE | М | Number of low bits sent<br>during a LIN Synch Break |

|------|---|-----------------------------------------------------|

| 0    | 0 | 10                                                  |

| 0    | 1 | 11                                                  |

| -    | 0 | 13                                                  |

| I    | 1 | 14                                                  |

|      |   |                                                     |

Bits 5:4 = Reserved, forced by hardware to 0. These bits are not used.

Bit 3 = CLKEN Clock Enable.

This bit allows the user to enable the SCLK pin. 0: SLK pin disabled

1: SLK pin enabled

#### Bit 2 = CPOL Clock Polarity.

This bit allows the user to select the polarity of the clock output on the SCLK pin. It works in conjunction with the CPHA bit to produce the desired clock/data relationship (see Figure 92 and Figure 93).

- 0: Steady low value on SCLK pin outside transmission window.

- 1: Steady high value on SCLK pin outside transmission window.

# Bit 1 = CPHA Clock Phase.

This bit allows the user to select the phase of the clock output on the SCLK pin. It works in conjunction with the CPOL bit to produce the desired clock/data relationship (see Figure 92 and Figure 93)

0: SCLK clock line activated in middle of data bit.

1: SCLK clock line activated at beginning of data bit.

## Bit 0 = LBCL Last bit clock pulse.

This bit allows the user to select whether the clock pulse associated with the last data bit transmitted (MSB) has to be output on the SCLK pin.

- 0: The clock pulse of the last data bit is not output to the SCLK pin.

- 1: The clock pulse of the last data bit is output to the SCLK pin.

**Note:** The last bit is the 8th or 9th data bit transmitted depending on the 8 or 9 bit format selected by the M bit in the SCICR1 register.

# Table 26. SCI clock on SCLK pin

| Data<br>format | M bit | LBCL bit | Number of clock<br>pulses on SCLK |

|----------------|-------|----------|-----------------------------------|

| 8 bit          | t O   | 0        | 7                                 |

| 0 Dit          |       | 1        | 8                                 |

| 9 bit          | 1     | 0        | 8                                 |

| 9 DII          | I     | 1        | 9                                 |

**Note:** These 3 bits (**CPOL**, **CPHA**, **LBCL**) should not be written while the transmitter is enabled.

# **12.10 CONTROL PIN CHARACTERISTICS**

# 12.10.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                  | Parameter                                        | ter Conditions    |                        | Min                 | Тур  | Max                 | Unit |

|-------------------------|--------------------------------------------------|-------------------|------------------------|---------------------|------|---------------------|------|

| V <sub>IL</sub>         | Input low level voltage <sup>1)</sup>            |                   |                        |                     |      | $0.3 \times V_{DD}$ |      |

| V <sub>IH</sub>         | Input high level voltage <sup>1)</sup>           |                   |                        | $0.7 \times V_{DD}$ |      |                     |      |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis <sup>2)</sup> | $V_{DD} = 5V$     |                        |                     | 1.5  |                     | V    |

| V                       | Output low level voltage <sup>3)</sup>           | V - 5V            | I <sub>IO</sub> = +5mA |                     | 0.68 | 0.95                |      |

| V <sub>OL</sub>         | Output low level voltage                         | $V_{DD} = 5V$     | I <sub>IO</sub> = +2mA |                     | 0.28 | 0.45                |      |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor <sup>4)</sup>   | $V_{IN} = V_{SS}$ |                        | 20                  | 40   | 80                  | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration                   | Internal res      | set source             |                     | 30   |                     |      |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time <sup>5)</sup>     |                   |                        | 2.5                 |      |                     | μs   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>6)</sup>           |                   |                        |                     | 200  | 2                   | ns   |

|                         | ed on characterization results, not test         | •                 |                        | 8                   | 100  |                     |      |

#### Notes:

2. Hysteresis voltage between Schmitt trigger switching levels.

3. The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overrightarrow{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(\text{RSTL})in}$  can be ignored.

5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

roducits productions 6. Data guaranteed by design, not tested in production.

# **12.11 TIMER PERIPHERAL CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}, f_{OSC},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

## 12.11.1 8-Bit PWM-ART Autoreload Timer

| Symbol                | Parameter                        | Conditions                         | Min   | Тур | Max                 | Unit             |

|-----------------------|----------------------------------|------------------------------------|-------|-----|---------------------|------------------|

| +                     | PWM resolution time              |                                    | 1     |     |                     | t <sub>CPU</sub> |

| <sup>t</sup> res(PWM) | F WW resolution time             | f <sub>CPU</sub> = 8 MHz           | 125   |     |                     | ns               |

| f <sub>EXT</sub>      | ART external clock frequency     |                                    | 0     |     | f/2                 | MHz              |

| f <sub>PWM</sub>      | PWM repetition rate              |                                    |       |     | f <sub>CPU</sub> /2 |                  |

| Res <sub>PWM</sub>    | PWM resolution                   |                                    |       |     | 8                   | bit              |

| V <sub>OS</sub>       | PWM/DAC output step voltage      | V <sub>DD</sub> = 5V, Res = 8-bits |       | 20  | N,                  | mV               |

| +                     | Timer clock period when internal | f _ 0 MLI-7                        | 1     | -0  | 128                 | t <sub>CPU</sub> |

| <sup>t</sup> COUNTER  | clock is selected                | f <sub>CPU</sub> = 8 MHz           | 0.125 |     | 16                  | μs               |

| 2.11.2 8              | -Bit Timer                       |                                    | 10    |     |                     |                  |

## 12.11.2 8-Bit Timer

| Symbol                 | Parameter                | Conditions               | Min   | Тур | Max                 | Unit             |

|------------------------|--------------------------|--------------------------|-------|-----|---------------------|------------------|

| t <sub>w(ICAP)in</sub> | Input capture pulse time | S                        | 1     |     |                     | +                |

| t <sub>res(PWM)</sub>  | PWM resolution time      | <b>O</b> Y               | 2     |     |                     | t <sub>CPU</sub> |

|                        |                          | f <sub>CPU</sub> = 8 MHz | 250   |     |                     | ns               |

| f <sub>PWM</sub>       | PWM repetition rate      |                          | 0     |     | f <sub>CPU</sub> /4 | MHz              |

| Res <sub>PWM</sub>     | PWM resolution           |                          |       |     | 8                   | bit              |

| <sup>t</sup> COUNTER   | Timer clock period       | f <sub>CPU</sub> = 8 MHz | 2     |     | 8000                | t <sub>CPU</sub> |

|                        |                          |                          | 0.250 |     | 1000                | μs               |

# 12.11.3 16-Bit Timer

| ſ | Symbol                 | Parameter                        | Conditions               | Min   | Тур | Max                 | Unit             |

|---|------------------------|----------------------------------|--------------------------|-------|-----|---------------------|------------------|

|   | t <sub>w(ICAP)in</sub> | Input capture pulse time         |                          | 1     |     |                     | <b>t</b>         |

|   | t CO                   | PWM resolution time              |                          | 2     |     |                     | t <sub>CPU</sub> |

|   | t <sub>res(PWM)</sub>  |                                  | f <sub>CPU</sub> = 8 MHz | 250   |     |                     | ns               |

|   | f <sub>EXT</sub>       | Timer external clock frequency   |                          | 0     |     | f / 1               | MHz              |

| Ī | f <sub>PWM</sub>       | PWM repetition rate              |                          | 0     |     | f <sub>CPU</sub> /4 |                  |

| Ī | Res <sub>PWM</sub>     | PWM resolution                   |                          |       |     | 16                  | bit              |

|   | t <sub>COUNTER</sub>   | Timer clock period when internal | f <sub>CPU</sub> = 8 MHz | 2     |     | 8                   | t <sub>CPU</sub> |

|   |                        | clock is selected                | 1CPU - 0 100 12          | 0.250 |     | 1                   | μs               |

# COMMUNICATIONS INTERFACE CHARACTERISTICS (Cont'd)

# **12.13 10-BIT ADC CHARACTERISTICS**

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol            | Parameter                                                                                 | Conditions                                                                | Min <sup>1)</sup> | Тур        | Max <sup>1)</sup> | Unit               |

|-------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------|------------|-------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                       |                                                                           | 0.4               |            | 4                 | MHz                |

| V <sub>AIN</sub>  | Conversion voltage range <sup>2)</sup>                                                    |                                                                           | V <sub>SSA</sub>  |            | V <sub>DDA</sub>  | V                  |

| R <sub>AIN</sub>  | External input impedance                                                                  |                                                                           |                   |            | see Figure        | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                        |                                                                           |                   |            | 119 and           | рF                 |

| f <sub>AIN</sub>  | Variation frequency of analog input signal                                                |                                                                           |                   |            | Figure<br>120     | Hz                 |

| l <sub>lkg</sub>  | Negative input leakage current on ro-<br>bust analog pins (refer to Table 2 on<br>page 8) | $V_{IN} < V_{SS,} \mid I_{IN} \mid$ < 400µA on adjacent robust analog pin | Ó                 | <b>6</b> 0 | 6                 | μA                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                        |                                                                           | X                 | 6          |                   | pF                 |

| t <sub>CONV</sub> | Conversion time                                                                           | f <sub>ADC</sub> = 4 MHz                                                  | 0                 | 3.5        |                   | μS                 |

|                   |                                                                                           |                                                                           |                   | 14         |                   | 1/f <sub>ADC</sub> |

| I <sub>ADC</sub>  | Analog part                                                                               | Sunk on V <sub>DDA</sub> <sup>2)</sup>                                    |                   |            | 3.6               | mA                 |

|                   | Digital part                                                                              | Sunk on V <sub>DD</sub>                                                   |                   |            | 0.2               | IIIA               |

#### Notes:

1. Data based on characterization results, not tested in production.

2. When  $V_{DDA}$  and  $V_{SSA}$  pins are not available on the pinout, the ADC refers to  $V_{DD}$  and  $V_{SS}$ .

duration is always correct assuming the application is not doing anything between the idle and the break. This can be ensured by temporarily disabling interrupts.

The exact sequence is:

- Disable interrupts

- Reset and Set TE (IDLE request)

- Set and Reset SBK (Break Request)

- Re-enable interrupts

## LIN mode

If the LINE bit in the SCICR3 is set and the M bit in the SCICR1 register is reset, the LINSCI is in LIN master mode. A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 24 bits instead of 13 bits

#### IMPORTANT NOTES (Cont'd)

#### Occurrence

The occurrence of the problem is random and proportional to the baud rate. With a transmit frequency of 19200 baud ( $f_{CPU} = 8$  MHz and SCIBRR = 0xC9), the wrong break duration occurrence is around 1%.

#### Analysis

The LIN protocol specifies a minimum of 13 bits for the break duration, but there is no maximum value. Nevertheless, the maximum length of the header is specified as  $(14+10+10+1) \times 1.4 = 49$  bits. This is composed of:

- the synch break field (14 bits)

- the synch field (10 bits)

- the identifier field (10 bits)

Every LIN frame starts with a break character. Adding an idle character increases the length of each header by 10 bits. When the problem occurs, the header length is increased by 11 bits and becomes ((14+11)+10+10+1) = 45 bits.

To conclude, the problem is not always critical for LIN communication if the software keeps the time between the sync field and the ID smaller than 4 bits, that is, 208µs at 19200 baud. The workaround is the same as for SCI mode but considering the low probability of occurrence (1%), it may be better to keep the break generation sequence as it is.

#### 16.2.2 16-bit and 8-bit Timer PWM Mode

In PWM mode, the first PWM pulse is missed after writing the value FFFCh in the OC1R or OC2R register.

#### **16.3 ROM DEVICES ONLY**

# 16.3.1 16-bit Timer PWM Mode Buffering Feature Change

In all devices, the frequency and period of the PWM signal are controlled by comparing the counter with a 16-bit buffer updated by the OCiHR and OCiLR registers. In ROM devices, contrary to the description in Section 10.5.3.5 on page 101, the output compare function is not inhibited after a write instruction to the OCiHR register. Instead the buffer update at the end of the PWM period is inhibited until OCiLR is written. This improved buffer handling is fully compatible with applications written for Flash devices.

uctis

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

57