Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | LINbusSCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 48                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f361ar9t3 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIN DESCRIPTION (Cont'd)

For external pin connection guidelines, refer to "ELECTRICAL CHARACTERISTICS" on page 178.

# Legend / Abbreviations for Table 2:

Type: I = input, O = output, S = supply

In/Output level:  $C_T$ = CMOS 0.3V<sub>DD</sub>/0.7V<sub>DD</sub> with Schmitt trigger

T<sub>T</sub>= TTL 0.8V / 2V with Schmitt trigger

Output level: HS = 20mA high sink (on N-buffer only)

Port and control configuration:

- Input: float = floating, wpu = weak pull-up, int = interrupt<sup>1)</sup>, ana = analog, RB = robust

- Output: OD = open drain, PP = push-pull

Refer to "I/O PORTS" on page 45 for more details on the software configuration of the I/O ports.

The RESET configuration of each pin is shown in bold which is valid as long as the device is in reset state.

## Table 2. Device Pin Description

|        | Pin n  | 0      |                      |      | Le             | evel   |       |     | Р   | ort |     |      | Main               | 0                                     |                       |

|--------|--------|--------|----------------------|------|----------------|--------|-------|-----|-----|-----|-----|------|--------------------|---------------------------------------|-----------------------|

| P64    | P44    | P32    | Pin Name             | Type | ut             | out    |       | Inp | out |     | Out | tput | function<br>(after | Alternate                             | function              |

| LQFP64 | LQFP44 | LQFP32 |                      | -    | Input          | Output | float | ndm | int | ana | ao  | 99   | reset)             |                                       |                       |

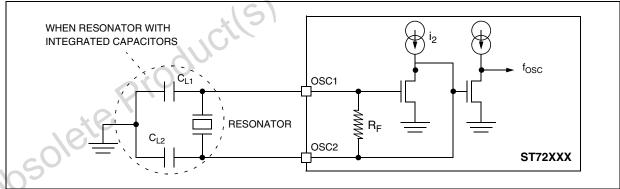

| 1      | 1      | 1      | OSC1 <sup>3)</sup>   | I    |                |        |       | ~   | 0   | 5   |     |      |                    | clock input or l<br>verter input      | Resonator os-         |

| 2      | 2      | 2      | OSC2 <sup>3)</sup>   | I/O  |                |        |       |     |     |     |     |      | Resonate           | or oscillator inv                     | erter output          |

| 3      | -      | -      | PA0 / ARTIC1         | I/O  | $C_T$          | 1      | X     | е   | i0  |     | Х   | Х    | Port A0            | ART Input Ca                          | apture 1              |

| 4      | 3      | 3      | PA1 / PWM0           | I/O  | $C_T$          | 5      | Х     |     | ei0 |     | Х   | Х    | Port A1            | ART PWM O                             | utput 0               |

| 5      | 4      | 4      | PA2 (HS) / PWM1      | I/O  | $C_T$          | HS     | Х     | е   | i0  |     | Х   | Х    | Port A2            | ART PWM O                             | utput 1               |

| 6      | 5      | -      | PA3 / PWM2           | I/O  | $C_T$          |        | Х     |     | ei0 |     | Х   | Х    | Port A3            | ART PWM O                             | utput 2               |

| 7      | 6      | -      | PA4 / PWM3           | I/O  | $C_T$          |        | Х     | е   | i0  |     | Х   | Х    | Port A4            | ART PWM O                             | utput 3               |

| 8      | -      | -      | V <sub>SS_3</sub>    | S    |                |        |       |     |     |     |     |      | Digital G          | ound Voltage                          |                       |

| 9      | -      | -      | V <sub>DD_3</sub>    | S    |                |        |       |     |     |     |     |      | Digital Ma         | ain Supply Vol                        | tage                  |

| 10     | 7      | 5      | PA5 (HS) / ARTCLK    | I/O  | $C_T$          | HS     | Х     |     | ei0 |     | Х   | Х    | Port A5            | ART Externa                           | l Clock               |

| 11     | 8      | )-{    | PA6 (HS) / ARTIC2    | I/O  | $C_T$          | HS     | Х     | е   | i0  |     | Х   | Х    | Port A6            | ART Input Ca                          | apture 2              |

| 12     |        | )•     | PA7 / T8_OCMP2       | I/O  | $C_T$          |        | Х     |     | ei0 |     | Х   | Х    | Port A7            | TIM8 Output                           | Compare 2             |

| 13     | 0      | -      | PB0 /T8_ICAP2        | I/O  | $C_T$          |        | X     | е   | i1  |     | Х   | Х    | Port B0            | TIM8 Input Capture 2                  |                       |

| 14     | 9      | 6      | PB1 /T8_OCMP1        | I/O  | $C_T$          |        | Х     |     | ei1 |     | Х   | Х    | Port B1            | TIM8 Output Compare 1                 |                       |

| 15     | 10     | 7      | PB2 / T8_ICAP1       | I/O  | $C_T$          |        | Х     | е   | i1  |     | Х   | Х    | Port B2            | TIM8 Input Capture 1                  |                       |

| 16     | 11     | 8      | PB3 / MCO            | I/O  | $C_T$          |        | X     |     | ei1 |     | Х   | Х    | Port B3            | Main clock out (f <sub>OSC2</sub> )   |                       |

| 17     | -      | -      | PE0 / AIN12          | I/O  | TT             |        | Х     | Х   |     | RB  | Х   | Х    | Port E0            | ADC Analog Input 12                   |                       |

| 18     | -      | -      | PE1 / AIN13          | I/O  | T <sub>T</sub> |        | Х     | Х   |     | RB  | Х   | Х    | Port E1            | ADC Analog Input 13                   |                       |

| 19     | 12     | 9      | PB4 / AIN0 / ICCCLK  | I/O  | CT             |        | Х     | e   | i1  | RB  | х   | х    | Port B4            | ICC Clock ADC Analog<br>input Input 0 |                       |

| 20     | -      | -      | PE2 / AIN14          | I/O  | $T_T$          |        | Х     | Х   |     | RB  | Х   | Х    | Port E2            | ADC Analog                            | Input 14              |

| 21     | -      | -      | PE3 / AIN15          | I/O  | $T_T$          |        | Х     | Х   |     | RB  | Х   | Х    | Port E3            | ADC Analog                            | Input 15              |

| 22     | 13     | 10     | PB5 / AIN1 / ICCDATA | I/O  | C <sub>T</sub> |        | х     |     | ei1 | RB  | Х   | х    | Port B5            | ICC Data in-<br>put                   | ADC Analog<br>Input 1 |

# 4 FLASH PROGRAM MEMORY

## **4.1 INTRODUCTION**

The ST7 dual voltage High Density Flash

(HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external V<sub>PP</sub> supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) or IAP (In-Application Programming).

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

#### **4.2 MAIN FEATURES**

- 3 Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application Programming) In this mode, all sectors except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

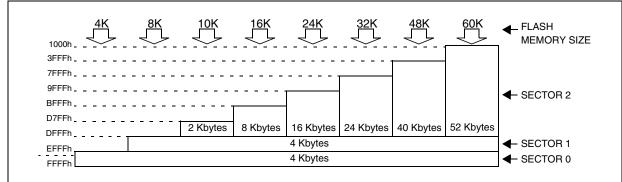

# 4.3 STRUCTURE

The Flash memory is organised in sectors and can be used for both code and data storage.

Depending on the overall Flash memory size in the microcontroller device, there are up to three user sectors (see Table 3). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

The first two sectors have a fixed size of 4 Kbytes (see Figure 6). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

| Table 4 | . Sectors | available | in | Flash | devices |

|---------|-----------|-----------|----|-------|---------|

|         |           |           |    |       | )       |

| Flash Size (bytes) | Available Sectors |  |  |

|--------------------|-------------------|--|--|

| 4K                 | Sector 0          |  |  |

| 8K                 | Sectors 0,1       |  |  |

| > 8K               | Sectors 0,1, 2    |  |  |

## 4.3.1 Read-out Protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In Flash devices, this protection is removed by reprogramming the option. In this case, the entire program memory is first automatically erased and the device can be reprogrammed.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

Figure 6. Memory Map and Sector Address

## POWER SAVING MODES (Cont'd)

#### 8.6.1 Register Description

# AWUFH CONTROL/STATUS REGISTER (AWUCSR)

Read/Write (except bit 2 read only) Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |          |          | 0         |

|---|---|---|---|---|----------|----------|-----------|

| 0 | 0 | 0 | 0 | 0 | AWU<br>F | AWU<br>M | AWU<br>EN |

Bits 7:3 = Reserved.

#### Bit 2 = AWUF Auto Wake-Up Flag

This bit is set by hardware when the AWU module generates an interrupt and cleared by software on reading AWUCSR.

0: No AWU interrupt occurred

1: AWU interrupt occurred

Bit 1 = **AWUM** Auto Wake-Up Measurement This bit enables the AWU RC oscillator and connects its output to the ICAP1 input of the 16-bit timer. This allows the timer to be used to measure the AWU RC oscillator dispersion and then compensate this dispersion by providing the right value in the AWUPR register.

0: Measurement disabled

1: Measurement enabled

Bit 0 = **AWUEN** Auto Wake-Up From Halt Enabled This bit enables the Auto Wake-Up From Halt feature: once HALT mode is entered, the AWUFH wakes up the microcontroller after a time delay defined by the AWU prescaler value. It is set and cleared by software.

Table 11. AWU Register Map and Reset Values

1: AWUFH (Auto Wake-Up From Halt) mode enabled

#### AWUFH PRESCALER REGISTER (AWUPR) Read/Write

Reset Value: 1111 1111 (FFh)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     |     |     | AWU |

| PR7 | PR6 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

Bits 7:0 = **AWUPR[7:0]** Auto Wake-Up Prescaler These 8 bits define the AWUPR Dividing factor (as explained below:

| AWUPR[7:0] | Dividing factor      |

|------------|----------------------|

| 00h        | Forbidden (See note) |

| 01h        | 1                    |

|            |                      |

| FEh        | 254                  |

| FFh        | 255                  |

In AWU mode, the period that the MCU stays in Halt Mode (t<sub>AWU</sub> in Figure 30) is defined by

<sup>t</sup>AWU =

$$64 \times AWUPR \times \frac{1}{f_{AWURC}} + t_{RCSTRT}$$

This prescaler register can be programmed to modify the time that the MCU stays in Halt mode before waking up automatically.

**Note:** If 00h is written to AWUPR, depending on the product, an interrupt is generated immediately after a HALT instruction or the AWUPR remains unchanged.

| Address<br>(Hex.) | Register<br>Label     | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------------|-----------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 002Bh             | AWUCSR<br>Reset Value | 0           | 0           | 0           | 0           | 0           | AWUF<br>0   | AWUM<br>0   | AWUEN<br>0  |

| 002Ch             | AWUPR<br>Reset Value  | AWUPR7<br>1 | AWUPR6<br>1 | AWUPR5<br>1 | AWUPR4<br>1 | AWUPR3<br>1 | AWUPR2<br>1 | AWUPR1<br>1 | AWUPR0<br>1 |

#### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

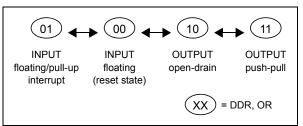

## 9.3 I/O PORT IMPLEMENTATION

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 33 on page 49. Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

## Figure 33. Interrupt I/O Port State Transitions

## 9.4 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

# 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit |   | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|---|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Y | es                   |

## I/O PORTS (Cont'd)

## Table 15. I/O Port Register Map and Reset Values

| 0002h       PAOR       Image: constraint of the second sec        | of all IO port registers         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th>of all IO p</th> <th>t Value</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | of all IO p | t Value |     |     |   |        |    |    |   |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|-----|-----|---|--------|----|----|---|-----|

| 0001h       PADDR       MSB       LSB         0002h       PAOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0001h       PADDR       MSB       LSB         0002h       PAOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00006       |         | 0   | 0   | 0 | 0      | 0  | 0  | 0 | 0   |

| 0002h       PAOR       Image: constraint of the second sec        | 0002h       PAOR       Image: constraint of the second sec        | 00000       | PADR    |     |     |   |        |    |    |   |     |

| 0003h       PBDR       MSB       LSB         0004h       PBDR       MSB       LSB         0005h       PBOR       MSB       LSB         0006h       PCDR       MSB       LSB         0007h       PCDR       MSB       LSB         0008h       PCOR       LSB       LSB         0009h       PDDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         000Ah       PEDR       MSB       LSB         000Ah       PEDR       MSB       LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0003h       PBDR       MSB       LSB         0004h       PBDR       MSB       LSB         0005h       PBOR       MSB       LSB         0006h       PCDR       MSB       LSB         0007h       PCDR       MSB       LSB         0008h       PCOR       LSB       LSB         0009h       PDDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         0000Ah       PEDR       MSB       LSB         000Ah       PEDR       MSB       LSB         000Ah       PEDR       MSB       LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0001h       | PADDR   | MSB |     |   |        |    |    |   | LSB |

| 0004h       PBDDR       MSB       Image: Sector of the s                 | 0004h       PBDDR       MSB       Image: Constraint of the second seco                 | 0002h       | PAOR    |     |     |   |        |    |    |   |     |

| 0005h       PBOR       Image: constraint of the second sec        | 0005h       PBOR       Image: constraint of the second sec        | 0003h       | PBDR    |     |     |   |        |    |    |   | 1   |

| 0006h       PCDR       MSB       LSB         0007h       PCDDR       MSB       LSB         0008h       PCOR       MSB       LSB         0009h       PDDR       MSB       LSB         0000h       PDDR       MSB       LSB         0000h       PDDR       MSB       LSB         0000h       PDOR       MSB       LSB         0000h       PEDR       MSB       LSB         0000h       PEDR       MSB       LSB         0000h       PEDR       MSB       LSB         0000h       PEDR       MSB       LSB         000Fh       PEDR       MSB       LSB         000Fh       PEDR       MSB       LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0006h       PCDR       MSB       LSB         0007h       PCDDR       MSB       LSB         0008h       PCOR       MSB       LSB         0009h       PDDR       MSB       LSB         0000h       PDDR       MSB       LSB         0000h       PDDR       MSB       LSB         0000h       PDOR       MSB       LSB         0000h       PEDR       MSB       LSB         0000h       PEDR       MSB       LSB         0000h       PEDR       MSB       LSB         0000h       PEDR       MSB       LSB         000Fh       PEOR       ISB       ISB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0004h       | PBDDR   | MSB |     |   |        |    |    | 1 | LSB |

| 0007h     PCDDR     MSB     LSB       0008h     PCOR     Image: state st                                           | 0007h     PCDDR     MSB     LSB       0008h     PCOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0005h       | PBOR    |     |     |   |        |    |    | X | 5   |

| 0008h       PCOR       Image: Constraint of the second sec        | 0008h       PCOR       Image: Constraint of the second sec        | 0006h       | PCDR    |     |     |   |        |    |    |   |     |

| 0009h     PDDR       000Ah     PDDR       000Bh     PDOR       000Ch     PEDR       000Dh     PEDDR       000Eh     PEOR       000Fh     PFDR       0010h     PEDDR       0010h     PEDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0009h     PDDR       000Ah     PDDR       000Bh     PDOR       000Ch     PEDR       000Dh     PEDDR       000Eh     PEOR       000Fh     PFDR       0010h     PEDDR       0010h     PEDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0007h       | PCDDR   | MSB |     |   |        |    |    |   | LSB |

| 000Ah     PDDDR     MSB     LSB       000Bh     PDOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000Ah     PDDDR     MSB     LSB       000Bh     PDOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0008h       | PCOR    |     |     |   |        |    | .0 |   |     |

| 000Bh         PDOR         Image: Constraint of the second | 000Bh         PDOR         Image: Constraint of the second | 0009h       | PDDR    |     |     |   |        |    |    |   |     |

| 000Ch         PEDR         MSB         LSB           000Dh         PEDDR         MSB         LSB           000Eh         PEOR         Image: Constraint of the second seco                                                                                                          | 000Ch         PEDR         MSB         LSB           000Dh         PEDDR         MSB         LSB           000Eh         PEOR         Image: Constraint of the second seco                                                                                                          | 000Ah       | PDDDR   | MSB |     |   |        |    |    |   | LSB |

| 000Dh     PEDDR     MSB     LSB       000Eh     PEOR     000Fh     PFDR     0010h       0010h     PEDDR     MSB     15B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 000Dh     PEDDR     MSB     LSB       000Eh     PEOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000Bh       | PDOR    |     |     |   |        | ×0 |    |   |     |

| 000Eh         PEOR         Sec         Sec           000Fh         PFDR         ISB         ISB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 000Eh         PEOR         Sec         Sec           000Fh         PFDR         ISB         ISB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 000Ch       | PEDR    |     |     |   |        | 0  |    |   |     |

| 000Fh PFDR MSB LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 000Fh PFDR MSB LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 000Dh       | PEDDR   | MSB |     |   | $\sim$ |    |    |   | LSB |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 000Eh       | PEOR    |     |     |   | 5      |    |    |   |     |

| 0010h     PFDDR     MSB     LSB       0011h     PFOR     Image: Constraint of the second seco                                           | O010h     PFDDR     MSB     LSB       0011h     PFOR     Image: Constraint of the second seco                                           | 000Fh       | PFDR    |     |     |   | Ŷ      |    |    |   |     |

| 0011h PFOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0011h PFOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0010h       | PFDDR   | MSB |     |   |        |    |    |   | LSB |

| AUCI(SI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Lete Product(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0011h       | PFOR    |     |     |   |        |    |    |   |     |

| 01001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | eteri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |         | odu | ctl | 1 |        |    |    |   |     |