# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | LINbusSCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 48                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f361ar9tc |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

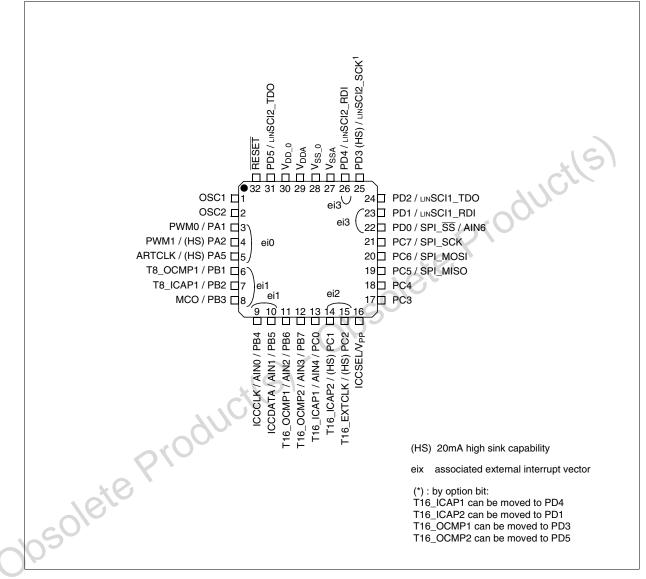

### PIN DESCRIPTION (Cont'd)

# Figure 4. LQFP 32-Pin Package Pinout

For external pin connection guidelines, refer to "ELECTRICAL CHARACTERISTICS" on page 178.

| Address | Block         | Register<br>Label | Register Name                             | Reset<br>Status | Remarks   |

|---------|---------------|-------------------|-------------------------------------------|-----------------|-----------|

| 0048h   |               | SCI1ISR           | SCI1 Status Register                      | C0h             | Read Only |

| 0049h   |               | SCI1DR            | SCI1 Data Register                        | xxh             | R/W       |

| 004Ah   | LINSCI1       | SCI1BRR           | SCI1 Baud Rate Register                   | 00h             | R/W       |

| 004Bh   | (LIN Master/  | SCI1CR1           | SCI1 Control Register 1                   | xxh             | R/W       |

| 004Ch   | Slave)        | SCI1CR2           | SCI1 Control Register 2                   | 00h             | R/W       |

| 004Dh   | Olavej        | SCI1CR3           | SCI1Control Register 3                    | 00h             | R/W       |

| 004Eh   |               | SCI1ERPR          | SCI1 Extended Receive Prescaler Register  | 00h             | R/W       |

| 004Fh   |               | SCI1ETPR          | SCI1 Extended Transmit Prescaler Register | 00h             | R/W       |

| 0050h   |               |                   | Reserved Area (1 byte)                    |                 | 1         |

| 0051h   |               | T16CR2            | Timer Control Register 2                  | 00h             | R/W       |

| 0052h   |               | T16CR1            | Timer Control Register 1                  | 00h             | R/W       |

| 0053h   |               | T16CSR            | Timer Control/Status Register             | 00h             | R/W       |

| 0054h   |               | T16IC1HR          | Timer Input Capture 1 High Register       | xxh             | Read Only |

| 0055h   |               | T16IC1LR          | Timer Input Capture 1 Low Register        | xxh             | Read Only |

| 0056h   |               | T16OC1HR          | Timer Output Compare 1 High Register      | 80h             | R/W       |

| 0057h   | 16-BIT        | T16OC1LR          | Timer Output Compare 1 Low Register       | 00h             | R/W       |

| 0058h   | TIMER         | T16CHR            | Timer Counter High Register               | FFh             | Read Only |

| 0059h   |               | T16CLR            | Timer Counter Low Register                | FCh             | Read Only |

| 005Ah   |               | T16ACHR           | Timer Alternate Counter High Register     | FFh             | Read Only |

| 005Bh   |               | T16ACLR           | Timer Alternate Counter Low Register      | FCh             | Read Only |

| 005Ch   |               | T16IC2HR          | Timer Input Capture 2 High Register       | xxh             | Read Only |

| 005Dh   |               | T16IC2LR          | Timer Input Capture 2 Low Register        | xxh             | Read Only |

| 005Eh   |               | T16OC2HR          | Timer Output Compare 2 High Register      | 80h             | R/W       |

| 005Fh   |               | T16OC2LR          | Timer Output Compare 2 Low Register       | 00h             | R/W       |

| 0060h   |               | SCI2SR 🖌          | SCI2 Status Register                      | C0h             | Read Only |

| 0061h   |               | SCI2DR            | SCI2 Data Register                        | xxh             | R/W       |

| 0062h   |               | SCI2BRR           | SCI2 Baud Rate Register                   | 00h             | R/W       |

| 0063h   | LINSCI2       | SCI2CR1           | SCI2 Control Register 1                   | xxh             | R/W       |

| 0064h   | (LIN Master)  | SCI2CR2           | SCI2 Control Register 2                   | 00h             | R/W       |

| 0065h   | $\mathcal{O}$ | SCI2CR3           | SCI2 Control Register 3                   | 00h             | R/W       |

| 0066h   |               | SCI2ERPR          | SCI2 Extended Receive Prescaler Register  | 00h             | R/W       |

| 0067h   | XU            | SCI2ETPR          | SCI2 Extended Transmit Prescaler Register | 00h             | R/W       |

| 0068h   | 6             |                   |                                           |                 |           |

| to      | •             |                   | Reserved area (24 bytes)                  |                 |           |

| 007Fh   |               |                   |                                           |                 |           |

**Legend**: x = undefined, R/W = read/write

#### Notes:

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

# I/O PORTS (Cont'd)

#### Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

#### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

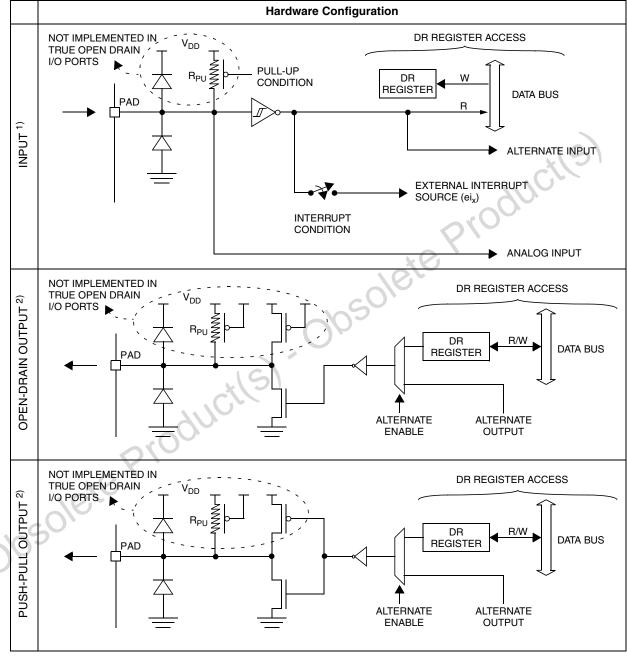

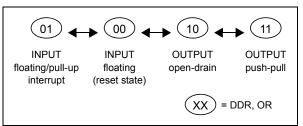

#### 9.3 I/O PORT IMPLEMENTATION

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 33 on page 49. Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 33. Interrupt I/O Port State Transitions

#### 9.4 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

# 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit |     | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|-----|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes |                      |

# PWM AUTO-RELOAD TIMER (Cont'd)

# Table 17. PWM Auto-Reload Timer Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label       | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0       |

|-------------------|-------------------------|----------|----------|----------|----------|----------|----------|----------|---------|

| 0031h             | PWMDCR3                 | DC7      | DC6      | DC5      | DC4      | DC3      | DC2      | DC1      | DC      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 0032h             | PWMDCR2                 | DC7      | DC6      | DC5      | DC4      | DC3      | DC2      | DC1      | DC      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 0033h             | PWMDCR1<br>Reset Value  | DC7<br>0 | DC6<br>0 | DC5<br>0 | DC4<br>0 | DC3<br>0 | DC2<br>0 | DC1<br>0 |         |

| 0034h             | PWMDCR0                 | DC7      | DC6      | DC5      | DC4      | DC3      | DC2      | DC1      | DC      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 0035h             | PWMCR                   | OE3      | OE2      | OE1      | OE0      | OP3      | OP2      | OP1      | OF      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 0036h             | ARTCSR                  | EXCL     | CC2      | CC1      | CC0      | TCE      | FCRL     | RIE      | 0V      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 0037h             | ARTCAR                  | CA7      | CA6      | CA5      | CA4      | CA3      | CA2      | CA1      | CA      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 0038h             | ARTARR                  | AR7      | AR6      | AR5      | AR4      | AR3      | AR2      | AR1      | AR      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 0039h             | ARTICCSR<br>Reset Value | 0        | 0        | CE2<br>0 | CE1<br>0 | CS2<br>0 | CS1<br>0 | CF2<br>0 | CF<br>0 |

| 003Ah             | ARTICR1                 | IC7      | IC6      | IC5      | IC4      | IC3      | IC2      | IC1      | IC      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| 003Bh             | ARTICR2                 | IC7      | IC6      | IC5      | IC4      | IC3      | IC2      | IC1      | IC      |

|                   | Reset Value             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0       |

| osoli             | 2                       |          |          |          |          |          |          |          |         |

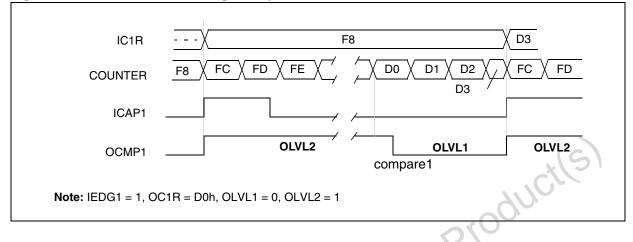

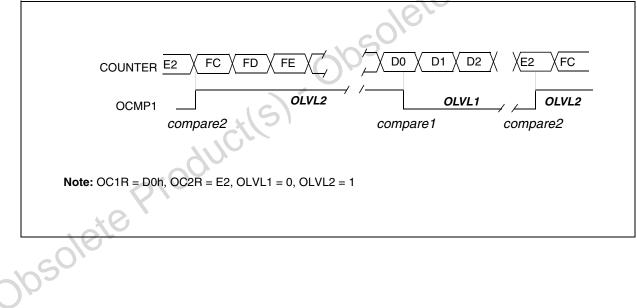

#### 16-BIT TIMER (Cont'd)

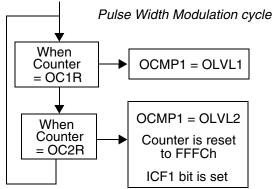

#### 10.4.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

#### Procedure

To use Pulse Width Modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1 = 0 and OLVL2 = 1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

If OLVL1 = 1 and OLVL2 = 0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$OC_{i}R Value = \frac{t \cdot t_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock the formula is:

Where:

= Signal or pulse period (in seconds)

$f_{EXT}$  = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 58)

#### Notes:

- 1. After a write instruction to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 3. The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- 5. When the Pulse Width Modulation (PWM) and One Pulse mode (OPM) bits are both set, the PWM mode is the only active one.

# 8-BIT TIMER (Cont'd)

#### Figure 68. One Pulse Mode Timing Example

# 8-BIT TIMER (Cont'd) CONTROL REGISTER 2 (CR2)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |     |     |     |       | 0 |

|------|------|-----|-----|-----|-----|-------|---|

| OC1E | OC2E | OPM | PWM | CC1 | CC0 | IEDG2 | 0 |

### Bit 7 = **OC1E** *Output Compare 1 Pin Enable.*

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

#### Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

Bit 5 = **OPM** One Pulse Mode.

- 0: One Pulse Mode is not active.

- 1: One Pulse Mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

Bit 4 = **PWM** Pulse Width Modulation.

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

#### Bit 3, 2 = **CC[1:0]** *Clock Control.*

The timer clock mode depends on these bits:

#### Table 20. Clock Control Bits

| Timer Clock               | CC1 | CC0 |

|---------------------------|-----|-----|

| f <sub>CPU</sub> / 4      | 0   | 0   |

| f <sub>CPU</sub> / 2      | 0   | 1   |

| f <sub>CPU</sub> / 8      | KU1 | 0   |

| f <sub>OSC2</sub> / 8000* | 1   | 1   |

16

\* Not available in Slow mode in ST72F561.

Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

Bit 0 = Reserved, must be kept at 0.

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

#### How to operate the SPI in master mode

To operate the SPI in master mode, perform the following steps in order:

- Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 74 shows the four possible configurations. **Note:** The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

Note: MSTR and SPE bits remain set only if SS is high).

Important note: if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account.

The transmit sequence begins when software writes a byte in the SPIDR register.

#### 10.6.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register

Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.6.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see **Note:** The slave must have the same CPOL and CPHA settings as the master.

- Manage the  $\overline{SS}$  pin as described in Section 10.6.3.2 and Figure 72. If CPHA = 1 SS must be held low continuously. If CPHA = 0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

#### 10.6.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- A write or a read to the SPIDR register

Notes: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.6.5.2).

#### SERIAL PERIPHERAL INTERFACE (cont'd)

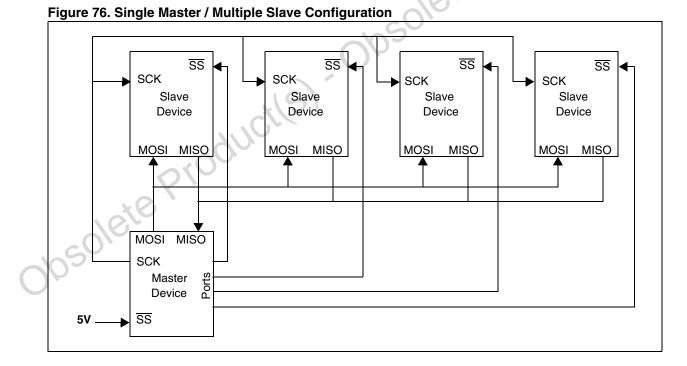

# 10.6.5.4 Single Master and Multimaster Configurations

There are two types of SPI systems:

- Single Master System

- Multimaster System

#### Single Master System

A typical single master system may be configured using a device as the master and four devices as slaves (see Figure 76).

The master device selects the individual slave devices by <u>using</u> four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line, the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

#### Multimaster System

A multimaster system may also be configured by the user. Transfer of master control could be implemented using a handshake method through the I/O ports or by an exchange of code messages through the serial peripheral interface system.

The multimaster system is principally handled by the MSTR bit in the SPICR register and the MODF bit in the SPICSR register.

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.4 LIN Error Detection

#### LIN Header Error Flag

The LIN Header Error Flag indicates that an invalid LIN Header has been detected.

When a LIN Header Error occurs:

- The LHE flag is set

- An interrupt is generated if the RIE bit is set and the I[1:0] bits are cleared in the CCR register.

If autosynchronization is enabled (LASE bit = 1), this can mean that the LIN Synch Field is corrupted, and that the SCI is in a blocked state (LSF bit is set). The only way to recover is to reset the LSF bit and then to clear the LHE bit.

- The LHE bit is reset by an access to the SCISR register followed by a read of the SCIDR register.

#### LHE/OVR Error Conditions

When Auto Resynchronization is disabled (LASE bit = 0), the LHE flag detects:

- That the received LIN Synch Field is not equal to 55h.

- That an overrun occurred (as in standard SCI mode)

- Furthermore, if LHDM is set it also detects that a LIN Header Reception Timeout occurred (only if LHDM is set).

When the LIN auto-resynchronization is enabled (LASE bit = 1), the LHE flag detects:

- That the deviation error on the Synch Field is outside the LIN specification which allows up to +/-15.5% of period deviation between the slave and master oscillators.

- A LIN Header Reception Timeout occurred.

If T<sub>HEADER</sub> > T<sub>HEADER\_MAX</sub> then the LHE flag is set. Refer to Figure 6. (only if LHDM is set to 1)

- An overflow during the Synch Field Measurement, which leads to an overflow of the divider registers. If LHE is set due to this error then the SCI goes into a blocked state (LSF bit is set).

- That an overrun occurred on Fields other than the Synch Field (as in standard SCI mode)

#### **Deviation Error on the Synch Field**

The deviation error is checking by comparing the current baud rate (relative to the slave oscillator) with the received LIN Synch Field (relative to the master oscillator). Two checks are performed in parallel:

The first check is based on a measurement between the first falling edge and the last falling edge of the Synch Field. Let us refer to this period deviation as D:

If the LHE flag is set, it means that:

D > 15.625%

If LHE flag is not set, it means that:

D < 16.40625%

If  $15.625\% \le D < 16.40625\%$ , then the flag can be either set or reset depending on the dephasing between the signal on the RDI line and the CPU clock.

The second check is based on the measurement of each bit time between both edges of the Synch Field: this checks that each of these bit times is large enough compared to the bit time of the current baud rate.

When LHE is set due to this error then the SCI goes into a blocked state (LSF bit is set).

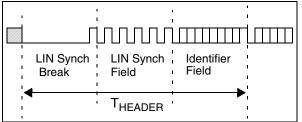

#### LIN Header Time-out Error

When the LIN Identifier Field Detection Method is used (by configuring LHDM to 1) or when LIN auto-resynchronization is enabled (LASE bit = 1), the LINSCI automatically monitors the  $T_{HEADER\_MAX}$  condition given by the LIN protocol.

If the entire Header (up to and including the STOP bit of the LIN Identifier Field) is not received within the maximum time limit of 57 bit times then a LIN Header Error is signalled and the LHE bit is set in the SCISR register.

#### Figure 82. LIN Header Reception Timeout

The time-out counter is enabled at each break detection. It is stopped in the following conditions:

- A LIN Identifier Field has been received

- An LHE error occurred (other than a timeout error).

- A software reset of LSF bit (transition from high to low) occurred during the analysis of the LIN Synch Field or

If LHE bit is set due to this error during the LIN Synchr Field (if LASE bit = 1) then the SCI goes into a blocked state (LSF bit is set).

#### 10.8 LINSCI SERIAL COMMUNICATION INTERFACE (LIN Master Only)

#### 10.8.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

#### 10.8.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud.

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- 2 receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- 4 error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- 5 interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Transmitter clock output

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

- LIN Synch Break send capability

#### **10.8.3 General Description**

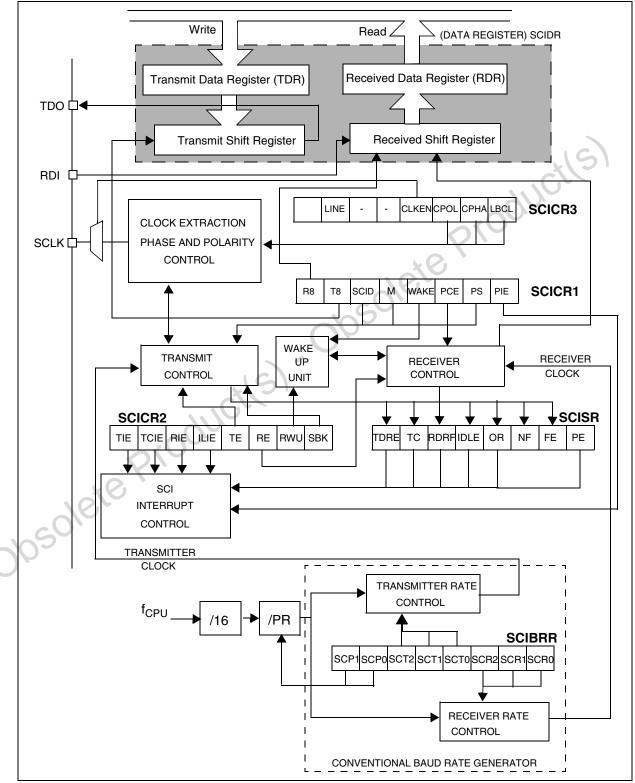

The interface is externally connected to another device by three pins (see Figure 88 on page 153). Any SCI bidirectional communication requires a minimum of two pins: Receive Data In (RDI) and Transmit Data Out (TDO):

- SCLK: Transmitter clock output. This pin outputs the transmitter data clock for synchronous transmission (no clock pulses on start bit and stop bit, and a software option to send a clock pulse on the last data bit). This can be used to control peripherals that have shift registers (e.g. LCD drivers). The clock phase and polarity are software programmable.

- TDO: Transmit Data Output. When the transmitter is disabled, the output pin returns to its I/O port configuration. When the transmitter is enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete.

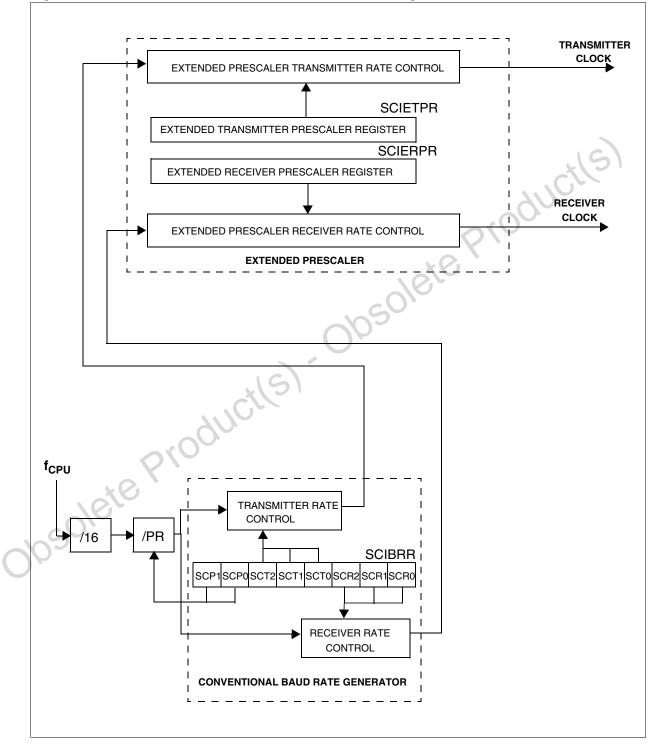

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates,

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies.

67/

# LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

# Figure 88. SCI Block Diagram

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

#### Figure 90. SCI Baud Rate and Extended Prescaler Block Diagram

Ĺ**Ţ**

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd) CONTROL REGISTER 1 (SCICR1)

Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

Bit 7 = R8 Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = T8 Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software. 0: SCI enabled

1: SCI prescaler and outputs disabled

Bit 4 = M Word length.

This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = **WAKE** Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line

1: Address Mark

#### Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

#### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software. 0: Parity error interrupt disabled

1: Parity error interrupt enabled

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

#### DATA REGISTER (SCIDR)

Read/Write

Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 88 on page 153).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 88).

#### **BAUD RATE REGISTER (SCIBRR)**

Read/Write

**67/**

Reset Value: 0000 0000 (00h)

| 7    |      |      |      | 2    | 6    | 0    |      |

|------|------|------|------|------|------|------|------|

| SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

#### Bits 7:6 = **SCP[1:0**] *First SCI Prescaler*

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

|                      | 0    | 0    |

| 3                    | 0    | 1    |

| 4                    | 1    | 0    |

| 13                   |      | 1    |

Bits 5:3 = **SCT[2:0]** *SCI Transmitter rate divisor* These 3 bits, in conjunction with the SCP1 and SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.

| TR dividing factor | SCT2 | SCT1 | SCT0 |

|--------------------|------|------|------|

| 1                  |      | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 4    | 0    |

| 8                  |      | I    | 1    |

| 16                 |      | 0    | 50   |

| 32                 | 1    | 0    | 1    |

| 64                 |      |      | 0    |

| 128                |      |      | 1    |

**Note:** This TR factor is used only when the ETPR fine tuning factor is equal to 00h; otherwise, TR is replaced by the (TR\*ETPR) dividing factor.

Bits 2:0 = **SCR[2:0]** *SCI Receiver rate divisor.* These 3 bits, in conjunction with the SCP1 and SCP0 bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR dividing factor | SCR2 | SCR1 | SCR0 |

|--------------------|------|------|------|

| 1                  | 0    | 0    | 0    |

| 2                  |      | 0    | 1    |

| 4                  |      | -1   | 0    |

| 8                  |      | I    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 |      | 0    | 1    |

| 64                 |      | -1   | 0    |

| 128                |      | I    | 1    |

**Note:** This RR factor is used only when the ERPR fine tuning factor is equal to 00h; otherwise, RR is replaced by the (RR\*ERPR) dividing factor.

165/225

#### **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

#### 12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                    | Ratings                                                                                                                                                                             | Maximum value           | Unit    |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|

| V <sub>DD</sub> - V <sub>SS</sub>         | V <sub>DD</sub> - V <sub>SS</sub> Supply voltage           V <sub>PP</sub> - V <sub>SS</sub> Programming Voltage           V <sub>IN</sub> Input voltage on any pin <sup>1)2)</sup> |                         |         |

| V <sub>PP</sub> - V <sub>SS</sub>         |                                                                                                                                                                                     |                         | V       |

| V <sub>IN</sub>                           |                                                                                                                                                                                     |                         |         |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins                                                                                                                                     | 50                      | mV      |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins                                                                                                                                   | 50                      | niv     |

| V <sub>ESD(HBM)</sub>                     | Electro-static discharge voltage (Human Body Model)                                                                                                                                 | see Section 12.8.3 on p | 200 102 |

| V <sub>ESD(MM)</sub>                      | Electro-static discharge voltage (Machine Model)                                                                                                                                    | see Section 12.8.3 on p | age 192 |

#### **12.2.2 Current Characteristics**

| Symbol                                                                                            | Ratings                                                                                 | Maximum value | Unit |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                                                                                  | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup>                   | 150           |      |

| I <sub>VSS</sub>                                                                                  | I <sub>VSS</sub> Total current out of V <sub>SS</sub> ground lines (sink) <sup>3)</sup> |               |      |

|                                                                                                   | Output current sunk by any standard I/O and control pin                                 | 25            |      |

| I <sub>IO</sub>                                                                                   | Output current sunk by any high sink I/O pin                                            | 50            | ļ    |

|                                                                                                   | Output current source by any I/Os and control pin                                       | - 25          |      |

|                                                                                                   | Injected current on V <sub>PP</sub> pin                                                 |               | mA   |

|                                                                                                   | Injected current on RESET pin                                                           | ± 5           |      |

| I <sub>INJ(PIN)</sub> 2)4)                                                                        | Injected current on OSC1 and OSC2 pins                                                  |               |      |

|                                                                                                   | Injected current on PB3 (on Flash devices)                                              | +5            |      |

|                                                                                                   | Injected current on any other pin <sup>5)</sup>                                         | ± 5           |      |

| $\Sigma I_{INJ(PIN)}^{2)}$ Total injected current (sum of all I/O and control pins) <sup>5)</sup> |                                                                                         | ± 25          |      |

#### **12.2.3 Thermal Characteristics**

| Γ | Symbol           | Ratings                                                                  | Value       | Unit |  |

|---|------------------|--------------------------------------------------------------------------|-------------|------|--|

|   | T <sub>STG</sub> | Storage temperature range                                                | -65 to +150 | °C   |  |

|   | Тј               | aximum junction temperature (see Section 13.2 "THERMAL CHARACTERISTICS") |             |      |  |

#### Notes:

1. Directly connecting the RESET and I/O pins to  $V_{DD}$  or  $V_{SS}$  could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical:  $4.7k\Omega$  for RESET,  $10k\Omega$  for I/Os). Unused I/O pins must be tied in the same way to  $V_{DD}$  or  $V_{SS}$  according to their reset configuration. 2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

3. All power (V<sub>DD</sub>) and ground (V<sub>SS</sub>) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "10-BIT ADC CHARACTERISTICS" on page 204.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

<u>ل</u>رک

#### CONTROL PIN CHARACTERISTICS (Cont'd)

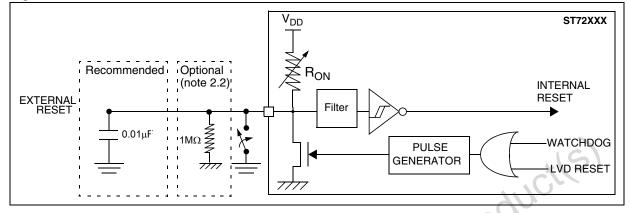

#### Figure 112. RESET Pin Protection When LVD Is Enabled<sup>1)2)</sup>

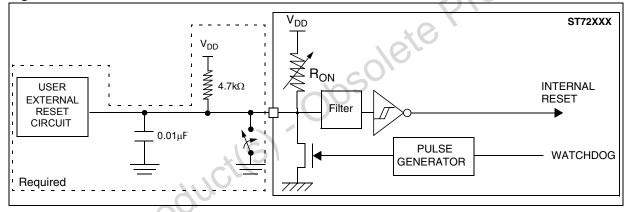

#### Figure 113. RESET Pin Protection When LVD Is Disabled<sup>1)</sup>

#### Note 1:

1.1 The reset network protects the device against parasitic resets.

1.2 The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

1.3 Whatever the reset source is (internal or external), the user must ensure that the level on the  $\overline{\text{RESET}}$  pin can go below the  $V_{\text{IL}}$  max. level specified in Section 12.10.1. Otherwise the reset will not be taken into account internally.

1.4 Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin (by an external pull-up for example) is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in Section 12.2.2 on page 179.

#### Note 2:

2.1 When the LVD is enabled, it is mandatory not to connect a pull-up resistor. A 10nF pull-down capacitor is recommended to filter noise on the reset line.

2.2. In case a capacitive power supply is used, it is recommended to connect a1MW pull-down resistor to the  $\overrightarrow{\text{RESET}}$  pin to discharge any residual voltage induced by this capacitive power supply (this will add 5µA to the power consumption of the MCU).

2.3. Tips when using the LVD:

- 1. Check that all recommendations related to reset circuit have been applied (see notes above)

- 2. Check that the power supply is properly decoupled (100nF + 10μF close to the MCU). Refer to AN1709. If this cannot be done, it is recommended to put a 100nF + 1MW pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoiding any start-up marginality. In most cases, steps 1 and 2 above are sufficient for a robust solution. Otherwise: Replace 10nF pull-down on the RESET pin with a 5µF to 20µF capacitor.

#### ADC CHARACTERISTICS (Cont'd)

#### 12.13.0.1 Analog Power Supply and Reference Pins

Depending on the MCU pin count, the package may feature separate V<sub>DDA</sub> and V<sub>SSA</sub> analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion. In smaller packages V<sub>DDA</sub> and V<sub>SSA</sub> pins are not available and the analog supply and reference pads are internally bonded to the V<sub>DD</sub> and V<sub>SS</sub> pins.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see Section 12.13.0.2 "General PCB Design Guidelines").

#### 12.13.0.2 General PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

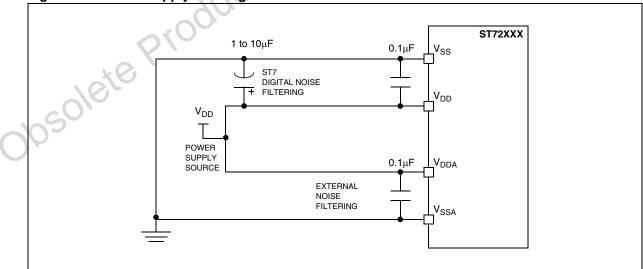

Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB. - Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing 0.1µF and optionally, if needed 10pF capacitors as close as possible to the ST7 power supply pins and a 1 to 10µF capacitor close to the power source (see Figure 122).

The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>DDA</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

# 12.13.0.3 Software Filtering of Spurious Conversion Results

For EMC performance reasons, it is recommended to filter A/D conversion outliers using software filtering techniques.

**/رک**ا

### Figure 122. Power Supply Filtering

### DEVICE CONFIGURATION AND ORDER INFORMATION (cont'd)

#### Table 35. FLASH User Programmable Device Types

| Part Number   | Package      | Memory<br>(Kbytes) | RAM<br>(Kbytes) | Temp Range    |  |

|---------------|--------------|--------------------|-----------------|---------------|--|

| ST72F361AR6T6 |              | 32                 | 1.5             |               |  |

| ST72F361AR7T6 | LQFP64 10x10 | 48                 | 2               |               |  |

| ST72F361AR9T6 | 1            | 60                 | 2               |               |  |

| ST72F361J6T6  |              | 32                 | 1.5             |               |  |

| ST72F361J7T6  | LQFP44 10x10 | 48                 | 2               | -40 to +85°C  |  |

| ST72F361J9T6  |              | 60                 | 2               |               |  |

| ST72F361K6T6  |              | 32                 | 1.5             | 16            |  |

| ST72F361K7T6  | LQFP32 7x7   | 48                 | 2               | *(2)          |  |

| ST72F361K9T6  |              | 60                 | 2               |               |  |

| ST72F361AR6T3 |              | 32                 | 1.5             | 40.5          |  |

| ST72F361AR7T3 | LQFP64 10x10 | 48                 | 2               |               |  |

| ST72F361AR9T3 |              | 60                 | 2               |               |  |

| ST72F361J6T3  |              | 32                 | 1.5             |               |  |

| ST72F361J7T3  | LQFP44 10x10 | 48                 | 2               | -40 to +125°C |  |

| ST72F361J9T3  | 1            | 60                 | 2               |               |  |

| ST72F361K6T3  |              | 32                 | 1.5             |               |  |

| ST72F361K7T3  | LQFP32 7x7   | 48                 | 2               |               |  |

| ST72F361K9T3  | 1            | 60                 | 2               |               |  |

# 14.2 TRANSFER OF CUSTOMER CODE

Customer code is made up of the ROM/FAS-TROM contents and the list of the selected options (if any). The ROM/FASTROM contents are to be sent on diskette, or by electronic means, with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

The selected options are communicated to STMicroelectronics using the correctly completed OPTION LIST appended.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.