# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | LINbusSCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 48KB (48K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 11x10b                                                           |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 44-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f361j7t3 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.2 MULTI-OSCILLATOR (MO)

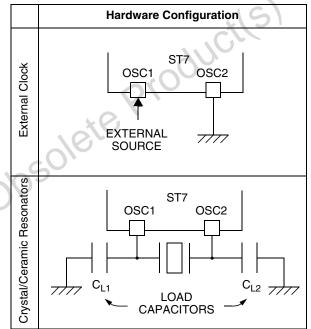

The main clock of the ST7 can be generated by two different source types coming from the multioscillator block:

- an external source

- a crystal or ceramic resonator oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configuration are shown in Table 6. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (> 16 MHz), putting the ST7 in an unsafe/undefined state. The product behavior must therefore be considered undefined when the OSC pins are left unconnected.

#### **External Clock Source**

)bsole

<u>لرک</u>

In external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

#### Crystal/Ceramic Oscillators

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of five oscillators with different frequency ranges must be done by option byte in order to reduce consumption (refer to Section 14.1 on page 210 for more details on the frequency ranges). The resonator and the load capacitors must be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

## Table 6. ST7 Clock Sources

#### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 6.4.4 Register Description

#### SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

Read/Write

Reset Value: 000x 000x (00h)

| 7 |           |          |           |   |   |   | 0         |

|---|-----------|----------|-----------|---|---|---|-----------|

| 0 | AVD<br>IE | AVD<br>F | LVD<br>RF | 0 | 0 | 0 | WDG<br>RF |

Bit 7 = Reserved, must be kept cleared.

Bit 6 = **AVDIE** Voltage Detector interrupt enable This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine. 0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 16 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  over  $V_{IT+(AVD)}$  threshold 1:  $V_{DD}$  under  $V_{IT-(AVD)}$  threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined. Bits 3:1 = Reserved, must be kept cleared.

#### Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

|                    |       |       |

#### **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

**/**

#### INTERRUPTS (Cont'd)

#### 7.6.2 Register Description

#### EXTERNAL INTERRUPT CONTROL REGISTER 0 (EICR0) Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| IS31 | IS30 | IS21 | IS20 | IS11 | IS10 | IS01 | IS00 |

#### Bits 7:6 = IS3[1:0] ei3 sensitivity

The interrupt sensitivity, defined using the IS3[1:0] bits, is applied to the ei3 external interrupts:

| IS31 | IS30 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

#### Bits 5:4 = IS2[1:0] ei2 sensitivity

The interrupt sensitivity, defined using the IS2[1:0] bits, is applied to the ei2 external interrupts:

| IS21 | IS20 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

#### Bits 3:2 = IS1[1:0] ei1 sensitivity

The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the ei1 external interrupts:

| IS11 | IS10 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when 11 and 10 of the CC register are both set to 1 (level 3).

#### Bits 1:0 = **ISO[1:0]** ei0 sensitivity

The interrupt sensitivity, defined using the ISO[1:0] bits, is applied to the ei0 external interrupts:

| IS01 | IS00 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

### EXTERNAL INTERUPT CONTROL REGISTER 1 (EICR1)

Read/Write Reset Value: 0000 0000 (00h)

| Ç | 7 |   |   |   |   |   |      | 0    |

|---|---|---|---|---|---|---|------|------|

|   | 0 | 0 | 0 | 0 | 0 | 0 | TLIS | TLIE |

Blts 7:2 = Reserved

Bit 1 = **TLIS** *Top Level Interrupt sensitivity* This bit configures the TLI edge sensitivity. It can be set and cleared by software only when TLIE bit is cleared.

- 0: Falling edge

- 1: Rising edge

Bit 0 = **TLIE** *Top Level Interrupt enable* This bit allows to enable or disable the TLI capability on the dedicated pin. It is set and cleared by software.

0: TLI disabled

1: TLI enabled

#### Notes:

- A parasitic interrupt can be generated when clearing the TLIE bit.

- In some packages, the TLI pin is not available. In this case, the TLIE bit must be kept low to avoid parasitic TLI interrupts.

57

## INTERRUPTS (Cont'd)

## Table 10. Nested Interrupts Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label    | 7          | 6          | 5          | 4          | 3              | 2          | 1         | 0          |

|-------------------|----------------------|------------|------------|------------|------------|----------------|------------|-----------|------------|

|                   |                      | е          | i1         | е          | 0          | CL             | KM         | Т         |            |

| 0025h             | ISPR0<br>Reset Value | l1_3<br>1  | 10_3<br>1  | l1_2<br>1  | 10_2<br>1  | l1_1<br>1      | I0_1<br>1  | 1         | 1          |

|                   |                      |            | •          |            |            | е              | i3         | e         | 2          |

| 0026h             | ISPR1<br>Reset Value | 1_7<br>1   | 10_7<br>1  | l1_6<br>1  | l0_6<br>1  | l1_5<br>1      | 10_5<br>1  | 11_4<br>1 | 10_4<br>1  |

|                   |                      | LINS       | SCI 2      | TIME       | R 16       | TIM            | ER 8       | S         | PI         |

| 0027h             | ISPR2<br>Reset Value | 11_11<br>1 | 10_11<br>1 | l1_10<br>1 | 10_10<br>1 | l1_9<br>1      | 10_9<br>1  | l1_8<br>1 | 10_8<br>1  |

|                   |                      |            |            |            |            | A              | AT .       | LINS      | SCI 1      |

| 0028h             | ISPR3<br>Reset Value | 1          | 1          | 1          | 1          | l1_13<br>1     | 10_13<br>1 | 11_12 I1  | 10_12<br>1 |

| 0029h             | EICR0<br>Reset Value | IS31<br>0  | IS30<br>0  | IS21<br>0  | IS20<br>0  | IS11<br>0      | IS10<br>0  | IS01<br>0 | IS00<br>0  |

| 002Ah             | EICR1<br>Reset Value | 0          | 0          | 0          | 0          | O <sub>0</sub> | 0          | TLIS<br>0 | TLIE<br>0  |

|                   | etePr                | odu        | cils       |            |            |                |            |           |            |

## WINDOW WATCHDOG (Cont'd)

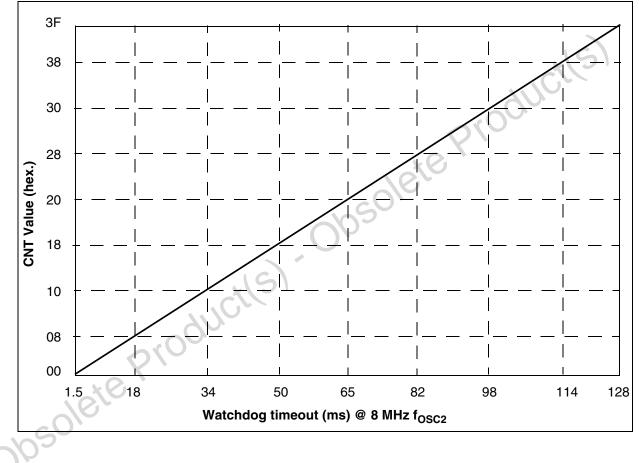

#### 10.1.5 How to Program the Watchdog Timeout

Figure 2 shows the linear relationship between the 6-bit value to be loaded in the Watchdog Counter (CNT) and the resulting timeout duration in milliseconds. This can be used for a quick calculation without taking the timing variations into account. If

more precision is needed, use the formulae in Figure 3.

**Caution:** When writing to the WDGCR register, always write 1 in the T6 bit to avoid generating an immediate reset.

Figure 35. Approximate Timeout Duration

## 16-BIT TIMER (Cont'd) 10.4.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                              |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                                   |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                                     |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequent-<br>ly, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and<br>the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

## 10.4.5 Interrupts

| Interrupt Event                                    | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |    |

|----------------------------------------------------|---------------|--------------------------|----------------------|----------------------|----|

| Input Capture 1 event/Counter reset in PWM mode    |               | ICF1                     | ICIE                 |                      |    |

| Input Capture 2 event                              |               | ICF2                     | ICIE                 |                      |    |

| Output Compare 1 event (not available in PWM mode) |               | OCF1                     | OCIE                 | Yes                  | No |

| Output Compare 2 event (not available in PWM mode) |               | OCF2                     | OCIE                 |                      |    |

| Timer Overflow event                               | S             | TOF                      | TOIE                 |                      |    |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

## 10.4.6 Summary of Timer Modes

| MODES                       | AV-             | TIMER RES                     | SOURCES          |                         |  |

|-----------------------------|-----------------|-------------------------------|------------------|-------------------------|--|

| MODES                       | Input Capture 1 | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |

| Input Capture (1 and/or 2)  | Yes             | Yes                           | Yes              | Yes                     |  |

| Output Compare (1 and/or 2) | 165             | 165                           | 165              | 165                     |  |

| One Pulse Mode              | No              | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |

| PWM Mode                    | NO              | Not Recommended <sup>3)</sup> | NO               | No                      |  |

1) See note 4 in Section 10.4.3.5 "One Pulse Mode"

2) See note 5 in Section 10.4.3.5 "One Pulse Mode"

3) See note 4 in Section 10.4.3.6 "Pulse Width Modulation Mode"

**لركم**

## 16-BIT TIMER (Cont'd) INPUT CAPTURE 1 HIGH REGISTER (IC1HR)

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

Read Only

<u>ل</u>رک

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

| 7                 |     |     |    |    |     |    | 0   |  |

|-------------------|-----|-----|----|----|-----|----|-----|--|

| MSB               |     |     |    |    |     |    | LSB |  |

|                   |     |     |    |    |     |    |     |  |

|                   |     |     |    |    |     | iG | Ń   |  |

|                   |     |     |    |    | . C |    |     |  |

|                   |     |     |    | -6 | JC  |    |     |  |

|                   |     |     | 05 | 0  |     |    |     |  |

|                   |     | .0. | X  |    |     |    |     |  |

|                   | 16  | 30  |    |    |     |    |     |  |

| S                 | ole |     |    |    |     |    |     |  |

| $O^{\mathcal{V}}$ |     |     |    |    |     |    |     |  |

|                   |     |     |    |    |     |    |     |  |

## OUTPUT COMPARE 1 HIGH REGISTER (OC1HR)

#### Read/Write

\_

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

#### 10.5 8-BIT TIMER (TIM8)

#### 10.5.1 Introduction

The timer consists of a 8-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the clock prescaler.

#### 10.5.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4, 8 or f<sub>OSC2</sub> divided by 8000.

- Overflow status flag and maskable interrupt

- Output compare functions with

- 2 dedicated 8-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Input capture functions with

- 2 dedicated 8-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One pulse mode

- Reduced Power Mode

- 4 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2)\*

The Block Diagram is shown in Figure 59.

\*Note: Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

#### 10.5.3 Functional Description

One Pulse mode and PWM mode.

#### 10.5.3.1 Counter

The main block of the Programmable Timer is a 8bit free running upcounter and its associated 8-bit registers.

These two read-only 8-bit registers contain the same value but with the difference that reading the ACTR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR).

Writing in the CTR register or ACTR register resets the free running counter to the FCh value. Both counters have a reset value of FCh (this is the only value which is reloaded in the 8-bit timer). The reset value of both counters is also FCh in

The timer clock depends on the clock control bits of the CR2 register, as shown in Table 19 Clock Control Bits. The value in the counter register repeats every 512, 1024, 2048 or 20480000  $f_{CPU}$  clock cycles depending on the CC[1:0] bits. The timer frequency can be  $f_{CPU}/2$ ,  $f_{CPU}/4$ ,  $f_{CPU}/8$  or  $f_{OSC2}$  /8000.

For example, if  $f_{OSC2}$ /8000 is selected, and  $f_{OSC2} = 8$  MHz, the timer frequency will be 1 ms. Refer to Table 19 on page 105.

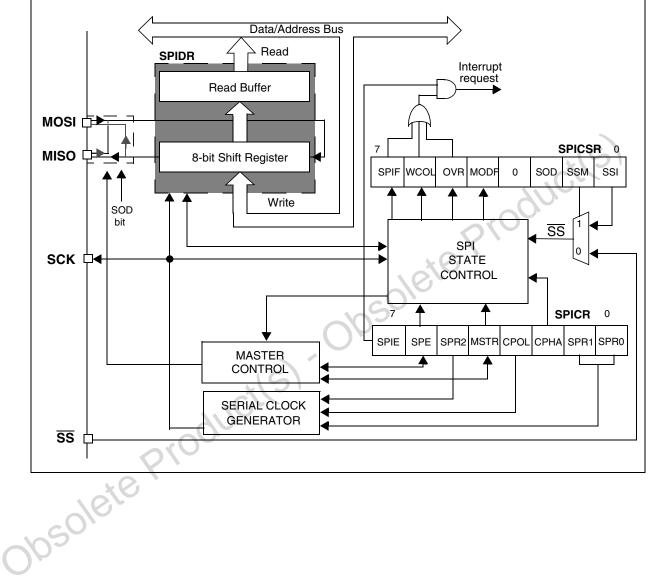

## SERIAL PERIPHERAL INTERFACE (SPI) (cont'd)

#### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Mode)

#### 10.7.9 LIN Mode - Functional Description.

The block diagram of the Serial Control Interface, in LIN slave mode is shown in Figure 5.

It uses six registers:

- 3 control registers: SCICR1, SCICR2 and SCICR3

- 2 status registers: the SCISR register and the LHLR register mapped at the SCIERPR address

- A baud rate register: LPR mapped at the SCI-BRR address and an associated fraction register LPFR mapped at the SCIETPR address

The bits dedicated to LIN are located in the SCICR3. Refer to the register descriptions in Section 0.1.10 for the definitions of each bit.

#### 10.7.9.1 Entering LIN Mode

To use the LINSCI in LIN mode the following configuration must be set in SCICR3 register:

- Clear the M bit to configure 8-bit word length.

- Set the LINE bit.

#### Master

To enter master mode the LSLV bit must be reset In this case, setting the SBK bit will send 13 low bits.

Then the baud rate can programmed using the SCIBRR, SCIERPR and SCIETPR registers.

In LIN master mode, the Conventional and / or Extended Prescaler define the baud rate (as in standard SCI mode)

#### Slave

Set the LSLV bit in the SCICR3 register to enter LIN slave mode. In this case, setting the SBK bit will have no effect.

In LIN Slave mode the LIN baud rate generator is selected instead of the Conventional or Extended Prescaler. The LIN baud rate generator is common to the transmitter and the receiver.

Then the baud rate can be programmed using LPR and LPRF registers.

**Note:** It is mandatory to set the LIN configuration first before programming LPR and LPRF, because the LIN configuration uses a different baud rate generator from the standard one.

#### 10.7.9.2 LIN Transmission

In LIN mode the same procedure as in SCI mode has to be applied for a LIN transmission.

To transmit the LIN Header the proceed as follows:

- First set the SBK bit in the SCICR2 register to start transmitting a 13-bit LIN Synch Break

- reset the SBK bit

- Load the LIN Synch Field (0x55) in the SCIDR register to request Synch Field transmission

- Wait until the SCIDR is empty (TDRE bit set in the SCISR register)

- Load the LIN message Identifier in the SCIDR register to request Identifier transmission.

<u>لرک</u>

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.9 Error due to LIN Synch measurement

The LIN Synch Field is measured over eight bit times.

This measurement is performed using a counter clocked by the CPU clock. The edge detections are performed using the CPU clock cycle.

This leads to a precision of 2 CPU clock cycles for the measurement which lasts 16\*8\*LDIV clock cycles.

Consequently, this error (D<sub>MEAS</sub>) is equal to:

2 / (128\*LDIV<sub>MIN</sub>).

$LDIV_{MIN}$  corresponds to the minimum LIN prescaler content, leading to the maximum baud rate, taking into account the maximum deviation of +/-15%.

#### 10.7.9.10 Error due to Baud Rate Quantization

The baud rate can be adjusted in steps of 1 / (16 \* LDIV). The worst case occurs when the "real" baud rate is in the middle of the step.

This leads to a quantization error ( $D_{QUANT}$ ) equal to 1 / (2\*16\*LDIV<sub>MIN</sub>).

#### 10.7.9.11 Impact of Clock Deviation on Maximum Baud Rate

The choice of the nominal baud rate (LDIV<sub>NOM</sub>) will influence both the quantization error ( $D_{QUANT}$ ) and the measurement error ( $D_{MEAS}$ ). The worst case occurs for LDIV<sub>MIN</sub>.

Consequently, at a given CPU frequency, the maximum possible nominal baud rate (LPR<sub>MIN</sub>) should be chosen with respect to the maximum tolerated deviation given by the equation:

D<sub>TRA</sub> + 2 / (128\*LDIV<sub>MIN</sub>) + 1 / (2\*16\*LDIV<sub>MIN</sub>)

$+ D_{REC} + D_{TCL} < 3.75\%$

#### Example:

A nominal baud rate of 20Kbits/s at  $T_{CPU}$  = 125ns (8 MHz) leads to LDIV<sub>NOM</sub> = 25d.

LDIV<sub>MIN</sub> = 25 - 0.15\*25 = 21.25

D<sub>MEAS</sub> = 2 / (128\*LDIV<sub>MIN</sub>) \* 100 = 0.00073%

D<sub>QUANT</sub> = 1 / (2\*16\*LDIV<sub>MIN</sub>) \* 100 = 0.0015%

#### LIN Slave systems

For LIN Slave systems (the LINE and LSLV bits are set), receivers wake up by LIN Synch Break or LIN Identifier detection (depending on the LHDM bit).

#### Hot Plugging Feature for LIN Slave Nodes

In LIN Slave Mute Mode (the LINE, LSLV and RWU bits are set) it is possible to hot plug to a network during an ongoing communication flow. In this case the SCI monitors the bus on the RDI line until 11 consecutive dominant bits have been detected and discards all the other bits received.

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

### **10.9.6 Register Description**

## **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only) Reset Value: 0000 0000 (00h)

| 7   |       |      |      |     |     |     | 0   |

|-----|-------|------|------|-----|-----|-----|-----|

| EOC | SPEED | ADON | SLOW | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by software reading the ADCDRH register or writing to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 =**SPEED** *A/D clock selection* This bit is set and cleared by software.

#### Table 29. A/D Clock Selection

| f <sub>ADC</sub>                                           | SLOW | SPEED |  |

|------------------------------------------------------------|------|-------|--|

| f <sub>CPU</sub> /2                                        | 0    | 0     |  |

| f <sub>CPU</sub> (where f <sub>CPU</sub> <= 4 MHz)         | 0    |       |  |

| f <sub>CPU</sub> /4                                        | 1    | 0     |  |

| f <sub>CPU</sub> /2 (same frequency as<br>SLOW=0, SPEED=0) | 14   |       |  |

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **SLOW** A/D Clock Selection This bit is set and cleared by software. It works together with the SPEED bit. Refer to Table 29.

## Bits 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

\*The number of channels is device dependent. Refer to the device pinout description.

| Channel Pin* | СНЗ | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 3   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

## DATA REGISTER (ADCDRH)

Read Only

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

Bits 7:0 = D[9:2] MSB of Analog Converted Value

## DATA REGISTER (ADCDRL)

Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bits 7:2 = Reserved. Forced by hardware to 0.

Bits 1:0 = D[1:0] LSB of Analog Converted Value

## **12.4 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode for which the clock is stopped).

| Cumhal          | Deveneter                                          | Conditions                                                                                                                                                                                                                                                            | Flash [                    | Devices                | ROM I                        | Devices                  | 11   |

|-----------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|------------------------------|--------------------------|------|

| Symbol          | Parameter                                          | Conditions                                                                                                                                                                                                                                                            | Typ <sup>1)</sup>          | Max <sup>2)</sup>      | Typ <sup>1</sup>             | Max <sup>2)</sup>        | Unit |

|                 | Supply current in RUN mode <sup>3)</sup>           | $ \begin{array}{l} f_{OSC} = 2 \ \text{MHz}, \ f_{CPU} = 1 \ \text{MHz} \\ f_{OSC} = 4 \ \text{MHz}, \ f_{CPU} = 2 \ \text{MHz} \\ f_{OSC} = 8 \ \text{MHz}, \ f_{CPU} = 4 \ \text{MHz} \\ f_{OSC} = 16 \ \text{MHz}, \ f_{CPU} = 8 \ \text{MHz} \end{array} $        | 1.8<br>3.2<br>6<br>10      | 3<br>5<br>8<br>15      | 1.1<br>2.2<br>4.4<br>8.9     | 2<br>3.5<br>6<br>12      |      |

|                 | Supply current in SLOW mode <sup>3)</sup>          | $ \begin{array}{l} f_{OSC} = 2 \ \text{MHz}, \ f_{CPU} = 62.5 \text{kHz} \\ f_{OSC} = 4 \ \text{MHz}, \ f_{CPU} = 125 \ \text{kHz} \\ f_{OSC} = 8 \ \text{MHz}, \ f_{CPU} = 250 \ \text{kHz} \\ f_{OSC} = 16 \ \text{MHz}, \ f_{CPU} = 500 \ \text{kHz} \end{array} $ | 0.5<br>0.6<br>0.85<br>1.25 | 2.7<br>3<br>3.6<br>4   | 0.1<br>0.2<br>0.4<br>0.8     | 0.2<br>0.4<br>0.8<br>1.5 | mA   |

| I <sub>DD</sub> | Supply current in WAIT mode <sup>3)</sup>          | $ \begin{array}{l} f_{OSC} = 2 \ \text{MHz}, \ f_{CPU} = 1 \ \text{MHz} \\ f_{OSC} = 4 \ \text{MHz}, \ f_{CPU} = 2 \ \text{MHz} \\ f_{OSC} = 8 \ \text{MHz}, \ f_{CPU} = 4 \ \text{MHz} \\ f_{OSC} = 16 \ \text{MHz}, \ f_{CPU} = 8 \ \text{MHz} \end{array} $        | 1<br>1.8<br>3.4<br>6.4     | 3<br>4<br>5<br>7       | 0.7<br>1.4<br>2.9<br>5.7     | 3<br>4<br>5<br>7         |      |

| 00              | Supply current in SLOW WAIT mode <sup>2)</sup>     |                                                                                                                                                                                                                                                                       | 0.4<br>0.5<br>0.6<br>0.8   | 1.2<br>1.3<br>1.8<br>2 | 0.07<br>0.14<br>0.28<br>0.56 | 0.12<br>0.25<br>0.5<br>1 |      |

|                 | Supply current in HALT mode <sup>4)</sup>          | $V_{DD} = 5.5V \frac{-40^{\circ}C \le T_A \le +85^{\circ}C}{-40^{\circ}C \le T_A \le +125^{\circ}C}$                                                                                                                                                                  | <1                         | 10<br>50               | <1                           | 10<br>50                 | μA   |

|                 | Supply current in ACTIVE HALT mode <sup>4)5)</sup> |                                                                                                                                                                                                                                                                       | 0.5                        | 1.2                    | 0.18                         | 0.25                     | mA   |

|                 | Supply current in AWUFH                            | $V_{DD} = 5.5V -40^{\circ}C \le T_A \le +85^{\circ}C$                                                                                                                                                                                                                 | 25                         | 30                     | 25                           | 30                       | μA   |

|                 | mode <sup>4)5)</sup>                               | $-40^{\circ}C \le T_{A} \le +125^{\circ}C$                                                                                                                                                                                                                            |                            | 70                     |                              | 70                       | •    |

Notes:

1. Typical data are based on  $T_A$  = 25°C,  $V_{DD}$  = 5V (4.5V  $\leq V_{DD} \leq$  5.5V range).

2. Data based on characterization results, tested in production at  $V_{DD}$  max.,  $f_{CPU}$  max. and  $T_A$  max.

3. Measurements are done in the following conditions:

- Program executed from Flash, CPU running with Flash (for flash devices).

- All I/O pins in input mode with a static value at  $V_{\text{DD}}$  or  $V_{\text{SS}}$  (no load)

- All peripherals in reset state.

- Clock input (OSC1) driven by external square wave.

- In SLOW and SLOW WAIT mode,  $f_{CPU}$  is based on  $f_{OSC}$  divided by 32.

To obtain the total current consumption of the device, add the clock source (Section 12.5.3) and the peripheral power consumption (Section 12.4.2).

4. All I/O pins in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load). Data based on characterization results, tested in production at V<sub>DD</sub> max.,  $f_{CPU}$  max. and  $T_A$  max.

5. This consumption refers to the Halt period only and not the associated run period which is software dependent.

## CLOCK CHARACTERISTICS (Cont'd)

## 12.6 Auto Wakeup from Halt Oscillator (AWU)

| Symbol             | Parameter                              | Conditions | Min | Тур | Max | Unit |

|--------------------|----------------------------------------|------------|-----|-----|-----|------|

| f <sub>AWU</sub>   | AWU oscillator frequency <sup>1)</sup> |            | 50  | 100 | 250 | kHz  |

| t <sub>RCSRT</sub> | AWU oscillator startup time            |            |     | 10  |     | μs   |

1. Data based on characterization results, not tested in production.

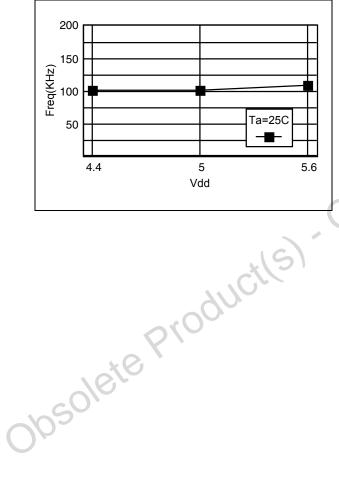

## Figure 102. AWU Oscillator Freq. @ T<sub>A</sub> 25°C

#### EMC CHARACTERISTICS (Cont'd)

#### 12.8.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity (see Table 33 and Table 34 below). For more details, refer to application note AN1181.

#### 12.8.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

## 12.8.3.2 Static Latch-Up

■ LU: Two complementary static tests are required on 6 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/ O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard.

#### Table 33. Absolute Maximum Ratings

| ar001                                |

|--------------------------------------|

| ns Maximum value <sup>1)</sup> Unit  |

| 2000                                 |

| °C 200 V                             |

| 750 on corner pins,<br>500 on others |

| 5                                    |

Notes:

1. Data based on characterization results, not tested in production.

| Table 34. Electrical Sensitivities |  |

|------------------------------------|--|

|------------------------------------|--|

| Symbol | Parameter             | Conditions                                      | Class      |

|--------|-----------------------|-------------------------------------------------|------------|

| LU     | Static latch-up class | T <sub>A</sub> =+125°C<br>conforming to JESD 78 | II level A |

|        | 010                   |                                                 |            |

|        | ×C                    |                                                 |            |

| 18     |                       |                                                 |            |

| ~~°`   |                       |                                                 |            |

| 0      |                       |                                                 |            |

| 1 .    |                       |                                                 |            |

**67/**

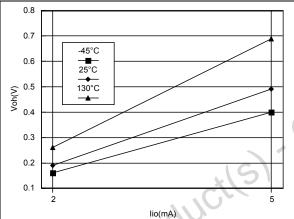

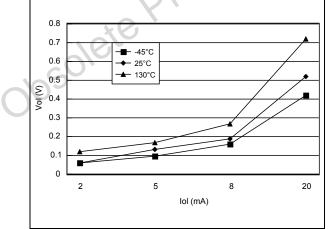

## I/O PORT PIN CHARACTERISTICS (Cont'd)

## 12.9.2 Output Driving Current

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                        | Parameter                                                                             |                  | Conditions                                                          | Min                  | Мах        | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|---------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------|----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | Output low level voltage for a standard I/O pin                                       |                  | I <sub>IO</sub> =+5mA                                               |                      | 1.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                               | when eight pins are sunk at same time (see Figure 106)                                |                  | I <sub>IO</sub> =+2mA                                               |                      | 0.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>OL</sub> <sup>1)</sup> | Output low level voltage for a high sink I/O pin when four pins are sunk at same time | <sub>0</sub> =5V | I <sub>IO</sub> =+20mA,T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C |                      | 1.3<br>1.5 | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | (see Figure 107 and Figure 110)                                                       | V <sub>DD</sub>  | I <sub>IO</sub> =+8mA                                               |                      | 0.6        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

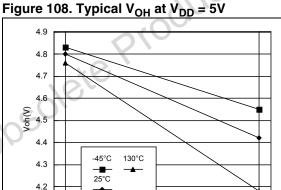

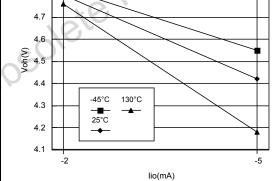

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when four pins are sourced at same time      |                  | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C |                      | 10         | in the second se |

| _                             | (see Figure 108 and Figure 111)                                                       |                  | I <sub>IO</sub> =-2mA                                               | V <sub>DD</sub> -0.7 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Figure 106. Typical $V_{OL}$ at $V_{DD}$ = 5V (Standard)

Figure 107. Typical V<sub>OL</sub> at V<sub>DD</sub> = 5V (High-sink)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins does not have V<sub>OH</sub>.

## **14 DEVICE CONFIGURATION AND ORDERING INFORMATION**

Each device is available for production in user programmable versions (FLASH) as well as in factory coded versions (ROM/FASTROM).

ST72361 devices are ROM versions. ST72P361 devices are Factory Advanced Service Technique ROM (FASTROM) versions: They are factory-programmed HDFlash devices.

ST72F361 FLASH devices are shipped to customers with a default content (FFh), while ROM factory coded parts contain the code supplied by the customer. This implies that FLASH devices have to be configured by the customer using the Option Bytes while the ROM devices are factory-configured.

#### **14.1 FLASH OPTION BYTES**

The option bytes allows the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with a reserved internal clock source enabled. In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see option list).

#### **OPTION BYTE 0**

OPT7 = **WDGHALT** Watchdog reset on HALT This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

- 0: No Reset generation when entering Halt mode

- 1: Reset generation when entering Halt mode

OPT6 = **WDGSW** *Hardware or software watchdog* This option bit selects the watchdog type. 0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

OPT4 = **LVD** Voltage detection This option bit enables the voltage detection block (LVD).

| Selected Low Voltage Detector | VD |

|-------------------------------|----|

| LVD Off                       | 1  |

| LVD On                        | 0  |

#### OPT3 = PLL OFF PLL activation

This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL is guaranteed only with an input frequency between 2 and 4 MHz.

0: PLL x2 enabled

1: PLL x2 disabled

**Caution**: The PLL can be enabled only if the "OSC RANGE" (OPT11:10) bits are configured to "MP - 2~4 MHz". Otherwise, the device functionality is not guaranteed.

| STATIC OPTION BYTE 0 |                 |                   |    |       |   | 0   | 7 |      | STAT  | IC OP   | TION B | YTE 1 |   | 0 |   |      |    |

|----------------------|-----------------|-------------------|----|-------|---|-----|---|------|-------|---------|--------|-------|---|---|---|------|----|

|                      | <u> </u>        | WDG P LVD O PKG C |    |       |   |     |   | ANGE | irved | TC<br>D |        |       |   |   |   |      |    |

| $\mathbf{O}$         | 02              | HALT              | SW | Resei |   | PLL | 1 | 0    | FMP   | 1       | 0      | 1     | 0 | 1 | 0 | Rese | RS |

|                      | De-<br>fault(*) | 1                 | 1  | 1     | 1 | 1   | 1 | 1    | 1     | 1       | 1      | 1     | 0 | 1 | 1 | 1    | 1  |

(\*): Option bit values programmed by ST

## FLASH OPTION BYTES (Cont'd)

OPT2:1 = **PKG[1:0]** Package selection These option bits select the device package.

| Selected Package | PKG |   |  |  |

|------------------|-----|---|--|--|

| Selected Fackage | 1   | 0 |  |  |

| LQFP 64          | 1   | x |  |  |

| LQFP 44          | 0   | 1 |  |  |

| LQFP 32          | 0   | 0 |  |  |

**Note:** Pads that are not bonded to external pins are in input pull-up configuration when the package selection option bits have been properly programmed. The configuration of these pads must be kept in reset state to avoid added current consumption.

OPT0 = **FMP\_R** Flash memory read-out protection

Read-out protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first, and the device can be reprogrammed. Refer to Section 4.3.1 and the *ST7 Flash Programming Reference Manual* for more details.

0: Read-out protection enabled

1: Read-out protection disabled

#### **OPTION BYTE 1**

#### OPT7:6 = AFI MAP[1:0] AFI Mapping

These option bits allow the mapping of some of the Alternate Functions to be changed.

| AFI Mapping 1                                                                                                                                   | AFI_MAP(1) |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| T16_OCMP1 on PD3<br>T16_OCMP2 on PD5<br>T16_ICAP1 on PD4<br>LINSCI2_SCK not available<br>LINSCI2_TDO not available<br>LINSCI2_RDI not available | 0          |

| T16_OCMP1 on PB6<br>T16_OCMP2 on PB7<br>T16_ICAP1 on PC0<br>LINSCI2_SCK on PD3<br>LINSCI2_TDO on PD5<br>LINSCI2_RDI on PD4                      | 1          |

| AFI Mapping 0              | AFI_MAP(0) |

|----------------------------|------------|

| T16_ICAP2 is mapped on PD1 | 0          |

| T16_ICAP2 is mapped on PC1 | 1          |

OPT5:4 = **OSCTYPE[1:0]** Oscillator Type These option bits select the ST7 main clock source type.

| Clock Source                                           | OSCTYPE |   |  |  |

|--------------------------------------------------------|---------|---|--|--|

| Clock Source                                           | 1       | 0 |  |  |

| Resonator Oscillator                                   | 0       | 0 |  |  |

| Reserved                                               | 0       | 1 |  |  |

| Reserved internal clock source (used only in ICC mode) | 1       | 0 |  |  |

| External Source                                        | 1       | 1 |  |  |

OPT3:2 = **OSCRANGE[1:0]** Oscillator range If the resonator oscillator type is selected, these option bits select the resonator oscillator. This selection corresponds to the frequency range of the resonator used. If external source is selected with the OSCTYPE option, then the OSCRANGE option must be selected with the corresponding range.

| т. | n Frog Bongo    | OSCRANGE |   |  |  |

|----|-----------------|----------|---|--|--|

| 1) | vp. Freq. Range | 1        | 0 |  |  |

| LP | 1~2 MHz         | 0        | 0 |  |  |

| MP | 2~4 MHz         | 0        | 1 |  |  |

| MS | 4~8 MHz         | 1        | 0 |  |  |

| HS | 8~16 MHz        | 1        | 1 |  |  |

#### OPT1 = Reserved

OPT0 = **RSTC** *RESET* clock cycle selection This option bit selects the number of CPU cycles inserted during the RESET phase and when exiting HALT mode. For resonator oscillators, it is advised to select 4096 due to the long crystal stabilization time.

0: Reset phase with 4096 CPU cycles

1: Reset phase with 256 CPU cycles

## **16 IMPORTANT NOTES**

#### **16.1 ALL DEVICES**

#### 16.1.1 RESET Pin Protection with LVD Enabled

As mentioned in note 2 below Figure 112 on page 199, when the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

## 16.1.2 Clearing Active Interrupts Outside Interrupt Routine

When an active interrupt request occurs at the same time as the related flag or interrupt mask is being cleared, the CC register may be corrupted.

#### Concurrent interrupt context

The symptom does not occur when the interrupts are handled normally, that is, when:

- The interrupt request is cleared (flag reset or interrupt mask) within its own interrupt routine

- The interrupt request is cleared (flag reset or interrupt mask) within any interrupt routine

- The interrupt request is cleared (flag reset or interrupt mask) in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

Perform SIM and RIM operation before and after resetting an active interrupt request

Example:

SIM

reset flag or interrupt mask

#### Nested interrupt context

The symptom does not occur when the interrupts are handled normally, that is, when:

- The interrupt request is cleared (flag reset or interrupt mask) within its own interrupt routine

- The interrupt request is cleared (flag reset or interrupt mask) within any interrupt routine with higher or identical priority level

- The interrupt request is cleared (flag reset or interrupt mask) in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

PUSH CC

SIM

reset flag or interrupt mask POP CC

#### 16.1.3 External Interrupt Missed

To avoid any risk of generating a parasitic interrupt, the edge detector is automatically disabled for one clock cycle during an access to either DDR and OR. Any input signal edge during this period will not be detected and will not generate an interrupt.

This case can typically occur if the application refreshes the port configuration registers at intervals during runtime.

#### Workaround

The workaround is based on software checking the level on the interrupt pin before and after writing to the PxOR or PxDDR registers. If there is a level change (depending on the sensitivity programmed for this pin) the interrupt routine is invoked using the call instruction with three extra PUSH instructions before executing the interrupt routine (this is to make the call compatible with the IRET instruction at the end of the interrupt service routine).

But detection of the level change does ensure that edge occurs during the critical 1 cycle duration and the interrupt has been missed. This may lead to occurrence of same interrupt twice (one hardware and another with software call).

To avoid this, a semaphore is set to '1' before checking the level change. The semaphore is changed to level '0' inside the interrupt routine. When a level change is detected, the semaphore status is checked and if it is '1' this means that the last interrupt has been missed. In this case, the interrupt routine is invoked with the call instruction.

There is another possible case, that is, if writing to PxOR or PxDDR is done with global interrupts disabled (interrupt mask bit set). In this case, the semaphore is changed to '1' when the level change is detected. Detecting a missed interrupt is done after the global interrupts are enabled (interrupt mask bit reset) and by checking the status of the semaphore. If it is '1' this means that the last interrupt was missed and the interrupt routine is invoked with the call instruction.

To implement the workaround, the following software sequence is to be followed for writing into the PxOR/PxDDR registers. The example is for Port PF1 with falling edge interrupt sensitivity. The

#### IMPORTANT NOTES (Cont'd)

## 16.1.5 Header Time-out Does Not Prevent Wake-up from Mute Mode

Normally, when LINSCI is configured in LIN slave mode, if a header time-out occurs during a LIN header reception (that is, header length > 57 bits), the LIN Header Error bit (LHE) is set, an interrupt occurs to inform the application but the LINSCI should stay in mute mode, waiting for the next header reception.

#### **Problem Description**

The LINSCI sampling period is Tbit / 16. If a LIN Header time-out occurs between the 9th and the 15th sample of the Identifier Field Stop Bit (refer to Figure 130), the LINSCI wakes up from mute mode. Nevertheless, LHE is set and LIN Header Detection Flag (LHDF) is kept cleared.

In addition, if LHE is reset by software before this 15th sample (by accessing the SCISR register and

#### Figure 130. Header Reception Event Sequence

reading the SCIDR register in the LINSCI interrupt routine), the LINSCI will generate another LINSCI interrupt (due to the RDRF flag setting).

#### Impact on application

Software may execute the interrupt routine twice after header reception.

Moreover, in reception mode, as the receiver is no longer in mute mode, an interrupt will be generated on each data byte reception.

#### Workaround

The problem can be detected in the LINSCI interrupt routine. In case of timeout error (LHE is set and LHLR is loaded with 00h), the software can check the RWU bit in the SCICR2 register. If RWU is cleared, it can be set by software. Refer to Figure 131 on page 221. Workaround is shown in bold characters.

**67/**