# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | LINbusSCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 11x10b                                                           |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 44-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f361j9t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address        | Block  | Register Register Name |                                                                   | Reset<br>Status   | Remarks           |

|----------------|--------|------------------------|-------------------------------------------------------------------|-------------------|-------------------|

| 000Fh          |        | PFDR                   | Port F Data Register                                              | 00h <sup>1)</sup> | R/W <sup>2)</sup> |

| 0010h          | Port F | PFDDR                  | Port F Data Direction Register                                    | 00h               | R/W <sup>2)</sup> |

| 0011h          |        | PFOR                   | Port F Option Register                                            | 00h               | R/W <sup>2)</sup> |

| 0012h          |        |                        | Beconved Area (15 bytea)                                          |                   |                   |

| to<br>0020h    |        |                        | Reserved Area (15 bytes)                                          |                   |                   |

| 0021h          |        | SPIDR                  | SPI Data I/O Register                                             | xxh               | R/W               |

| 0022h          | SPI    | SPICR                  | SPI Control Register                                              | 0xh               | R/W               |

| 0023h          |        | SPICSR                 | SPI Control/Status Register                                       | 00h               | R/W               |

| 0024h          | FLASH  | FCSR                   | Flash Control/Status Register                                     | 00h               | R/W               |

| 0025h          |        | ISPR0                  | Interrupt Software Priority Register 0                            | FFh               | R/W               |

| 0026h          |        | ISPR1                  | Interrupt Software Priority Register 1                            | FFh               | R/W               |

| 0027h          | ITC    | ISPR2                  | Interrupt Software Priority Register 2                            | FFh               | R/W               |

| 0028h          | 110    | ISPR3                  | Interrupt Software Priority Register 3                            | FFh               | R/W               |

| 0029h          |        | EICR0                  | External Interrupt Control Register 0                             | 00h               | R/W               |

| 002Ah          |        | EICR1                  | External Interrupt Control Register 1                             | 00h               | R/W               |

| 002Bh          | AWU    | AWUCSR                 | Auto Wake up f. Halt Control/Status Register                      | 00h               | R/W               |

| 002Ch          | AWO    | AWUPR                  | Auto Wake Up From Halt Prescaler                                  | FFh               | R/W               |

| 002Dh          | CKCTRL | SICSR                  | System Integrity Control / Status Register                        | 0xh               | R/W               |

| 002Eh          | OROTHE | MCCSR                  | Main Clock Control / Status Register                              | 00h               | R/W               |

| 002Fh          | WWDG   | WDGCR                  | Watchdog Control Register                                         | 7Fh               | R/W               |

| 0030h          | Wbg    | WDGWR                  | Watchdog Window Register                                          | 7Fh               | R/W               |

| 0031h          |        | PWMDCR3                | Pulse Width Modulator Duty Cycle Register 3                       | 00h               | R/W               |

| 0032h          |        | PWMDCR2                | PWM Duty Cycle Register 2                                         | 00h               | R/W               |

| 0033h          |        | PWMDCR1                | PWM Duty Cycle Register 1                                         | 00h               | R/W               |

| 0034h          | O      | PWMDCR0                | PWM Duty Cycle Register 0                                         | 00h               | R/W               |

| 0035h          | PWM    | PWMCR                  | PWM Control register                                              | 00h               | R/W               |

| 0036h          | ART    | ARTCSR                 | Auto-Reload Timer Control/Status Register                         | 00h               | R/W               |

| 0037h          |        | ARTCAR                 | Auto-Reload Timer Counter Access Register                         | 00h               | R/W               |

| 0038h          |        | ARTARR                 | Auto-Reload Timer Auto-Reload Register                            | 00h               | R/W               |

| 0039h          | ν      | ARTICCSR               | ART Input Capture Control/Status Register                         | 00h               | R/W               |

| 003Ah          |        | ARTICR1                | ART Input Capture Register 1                                      | 00h               | Read Only         |

| 003Bh          |        | ARTICR2                | ART Input Capture register 2                                      | 00h               | Read Only         |

| 003Ch          |        | T8CR2                  | Timer Control Register 2                                          | 00h               | R/W               |

| 003Dh          |        | T8CR1                  | Timer Control Register 1                                          | 00h               | R/W               |

| 003Eh          |        | T8CSR                  | Timer Control/Status Register                                     | 00h               | Read Only         |

| 003Fh          | 8-BIT  | T8IC1R                 | Timer Input Capture 1 Register                                    | xxh               | Read Only         |

| 0040h          | TIMER  | T8OC1R                 | Timer Output Compare 1 Register                                   | 00h               | R/W               |

| 0041h          |        | T8CTR                  | Timer Counter Register                                            | FCh               | Read Only         |

| 0042h          |        | T8ACTR                 | Timer Alternate Counter Register                                  | FCh               | Read Only         |

| 0043h<br>0044h |        | T8IC2R<br>T8OC2R       | Timer Input Capture 2 Register<br>Timer Output Compare 2 Register | xxh<br>00h        | Read Only<br>R/W  |

|                |        |                        |                                                                   |                   |                   |

| 0045h          |        | ADCCSR                 | Control/Status Register                                           | 00h               | R/W<br>Read Only  |

| 0046h          | ADC    | ADCDRH                 | Data High Register                                                | 00h               | Read Only         |

| 0047h          |        | ADCDRL                 | Data Low Register                                                 | 00h               | Read Only         |

#### WINDOW WATCHDOG (Cont'd)

## Figure 36. Exact Timeout Duration ( $t_{min}$ and $t_{max}$ )

#### WHERE:

$t_{min0} = (LSB + 128) \times 64 \times t_{OSC2}$  $t_{max0} = 16384 \text{ x } t_{OSC2}$

$t_{OSC2}$  = 125ns if  $f_{OSC2}$  = 8 MHz

CNT = Value of T[5:0] bits in the WDGCR register (6 bits)

MSB and LSB are values from the table below depending on the timebase selected by the TB[1:0] bits in the MCCSR register

| TB1 Bit<br>(MCCSR Reg.) | TB0 Bit<br>(MCCSR Reg.) | Selected MCCSR<br>Timebase | MSB | LSB |

|-------------------------|-------------------------|----------------------------|-----|-----|

| 0                       | 0                       | 2ms                        | 4   | 59  |

| 0                       | 1                       | 4ms                        | 8   | 53  |

| 1                       | 0                       | 10ms                       | 20  | 35  |

| 1                       | 1                       | 25ms                       | 49  | 54  |

To calculate the minimum Watchdog Timeout (t<sub>min</sub>):

**IF** CNT <  $\left[\frac{MS}{4}\right]$

<u>ل</u>رک

$$\frac{\textbf{TB0 Bit}}{(\text{MCCSR Reg.})} \frac{\textbf{Selected MCCSR}}{\textbf{Timebase}} | \textbf{MSB} | \textbf{LSB} | \\ \hline 0 & 2ms & 4 & 59 \\ \hline 1 & 4ms & 8 & 53 \\ \hline 0 & 10ms & 20 & 35 \\ \hline 1 & 25ms & 49 & 54 \\ \hline \textbf{the minimum Watchdog Timeout (t_{min}):} \\ \hline \textbf{B} \end{bmatrix} \textbf{THEN } t_{min} = t_{min0} + 16384 \times \text{CNT} \times t_{osc2} \\ \hline \textbf{ELSE } t_{min} = t_{min0} + \left[ 16384 \times \left( \text{CNT} - \left[ \frac{4\text{CNT}}{\text{MSB}} \right] \right) + (192 + \text{LSB}) \times 64 \times \left[ \frac{4\text{CNT}}{\text{MSB}} \right] \times t_{osc2} \\ \hline \textbf{sc} \end{bmatrix}$$

×C

To calculate the maximum Watchdog Timeout (t<sub>max</sub>):

**IF** CNT

$$\leq \left[\frac{MSB}{4}\right]$$

**THEN**  $t_{max} = t_{max0} + 16384 \times CNT \times t_{osc2}$

**ELSE**  $t_{max} = t_{max0} + \left[16384 \times \left(CNT - \left[\frac{4CNT}{MSB}\right]\right) + (192 + LSB) \times 64 \times \left[\frac{4CNT}{MSB}\right]\right] \times t_{osc2}$

Note: In the above formulae, division results must be rounded down to the next integer value. Example:

With 2ms timeout selected in MCCSR register

| Min. Watchdog<br>Timeout (ms)<br>t <sub>min</sub> | Max. Watchdog<br>Timeout (ms)<br>t <sub>max</sub> |  |  |

|---------------------------------------------------|---------------------------------------------------|--|--|

| 1.496                                             | 2.048                                             |  |  |

| 128                                               | 128.552                                           |  |  |

|                                                   | Timeout (ms)<br>t <sub>min</sub><br>1.496         |  |  |

#### **ON-CHIP PERIPHERALS** (Cont'd)

#### **10.3.3 Register Description**

#### CONTROL / STATUS REGISTER (ARTCSR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |     |     |     |     |      |     | 0   |  |

|------|-----|-----|-----|-----|------|-----|-----|--|

| EXCL | CC2 | CC1 | CC0 | TCE | FCRL | OIE | OVF |  |

#### Bit 7 = **EXCL** External Clock

This bit is set and cleared by software. It selects the input clock for the 7-bit prescaler.

0: CPU clock. 1: External clock.

Bit 6:4 = **CC[2:0]** Counter Clock Control These bits are set and cleared by software. They determine the prescaler division ratio from  $f_{INPUT}$ .

| <b>f</b> COUNTER         | With f <sub>INPUT</sub> =8 MHz | CC2 | CC1 | CC0 |

|--------------------------|--------------------------------|-----|-----|-----|

| f <sub>INPUT</sub>       | 8 MHz                          | 0   | 0   | 0   |

| f <sub>INPUT</sub> / 2   | 4 MHz                          | 0   | 0   | 1   |

| f <sub>INPUT</sub> / 4   | 2 MHz                          | 0   | 1   | 0   |

| f <sub>INPUT</sub> / 8   | 1 MHz                          | 0   | 1   | 1   |

| f <sub>INPUT</sub> / 16  | 500 kHz                        | 1   | 0   | 0   |

| f <sub>INPUT</sub> / 32  | 250 kHz                        | 1   | 0   | 1   |

| f <sub>INPUT</sub> / 64  | 125 kHz                        | 1   | 1   | 0   |

| f <sub>INPUT</sub> / 128 | 62.5 kHz                       | 1   | D   | 1   |

#### Bit 3 = **TCE** *Timer Counter Enable*

This bit is set and cleared by software. It puts the timer in the lowest power consumption mode. 0: Counter stopped (prescaler and counter frozen).

1: Counter running.

#### Bit 2 = **FCRL** Force Counter Re-Load

This bit is write-only and any attempt to read it will yield a logical zero. When set, it causes the contents of ARTARR register to be loaded into the counter, and the content of the prescaler register to be cleared in order to initialize the timer before starting to count.

#### Bit 1 = **OIE** Overflow Interrupt Enable

This bit is set and cleared by software. It allows to enable/disable the interrupt which is generated when the OVF bit is set.

0: Overflow Interrupt disable.

1: Overflow Interrupt enable.

#### Bit 0 = **OVF** Overflow Flag

This bit is set by hardware and cleared by software reading the ARTCSR register. It indicates the transition of the counter from FFh to the ARTARR value.

#### 0: New transition not yet reached 1: Transition reached

## COUNTER ACCESS REGISTER (ARTCAR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

Bit 7:0 = CA[7:0] Counter Access Data

These bits can be set and cleared either by hardware or by software. The ARTCAR register is used to read or write the auto-reload counter "on the fly" (while it is counting).

## AUTO-RELOAD REGISTER (ARTARR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| AR7 | AR6 | AR5 | AR4 | AR3 | AR2 | AR1 | AR0 |

#### Bit 7:0 = AR[7:0] Counter Auto-Reload Data

These bits are set and cleared by software. They are used to hold the auto-reload value which is automatically loaded in the counter when an overflow occurs. At the same time, the PWM output levels are changed according to the corresponding OPx bit in the PWMCR register.

This register has two PWM management functions:

- Adjusting the PWM frequency

- Setting the PWM duty cycle resolution

#### PWM Frequency vs Resolution:

| ARTARR     | Resolution | f <sub>P\</sub> | WМ        |  |

|------------|------------|-----------------|-----------|--|

| value      | Resolution | Min             | Max       |  |

| 0          | 8-bit      | ~0.244 kHz      | 31.25 kHz |  |

| [ 0127 ]   | > 7-bit    | ~0.244 kHz      | 62.5 kHz  |  |

| [ 128191 ] | > 6-bit    | ~0.488 kHz      | 125 kHz   |  |

| [ 192223 ] | > 5-bit    | ~0.977 kHz      | 250 kHz   |  |

| [ 224239 ] | > 4-bit    | ~1.953 kHz      | 500 kHz   |  |

#### **ON-CHIP PERIPHERALS** (Cont'd)

#### **PWM CONTROL REGISTER (PWMCR)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| OE3 | OE2 | OE1 | OE0 | OP3 | OP2 | OP1 | OP0 |

Bit 7:4 = **OE[3:0]** *PWM Output Enable*

These bits are set and cleared by software. They enable or disable the PWM output channels independently acting on the corresponding I/O pin. 0: PWM output disabled.

1: PWM output enabled.

#### Bit 3:0 = OP[3:0] PWM Output Polarity

These bits are set and cleared by software. They independently select the polarity of the four PWM output signals.

| PWMx ou         | OPx            |   |

|-----------------|----------------|---|

| Counter <= OCRx | Counter > OCRx |   |

| 1               | 0              | 0 |

| 0               | 1              | 1 |

Note: When an OPx bit is modified, the PWMx output signal polarity is immediately reversed.

#### **DUTY CYCLE REGISTERS (PWMDCRx)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DC7 | DC6 | DC5 | DC4 | DC3 | DC2 | DC1 | DC0 |

#### Bit 7:0 = DC[7:0] Duty Cycle Data

These bits are set and cleared by software.

A PWMDCRx register is associated with the OCRx register of each PWM channel to determine the second edge location of the PWM signal (the first edge location is common to all channels and given by the ARTARR register). These PWMDCR registers allow the duty cycle to be set independently for each PWM channel.

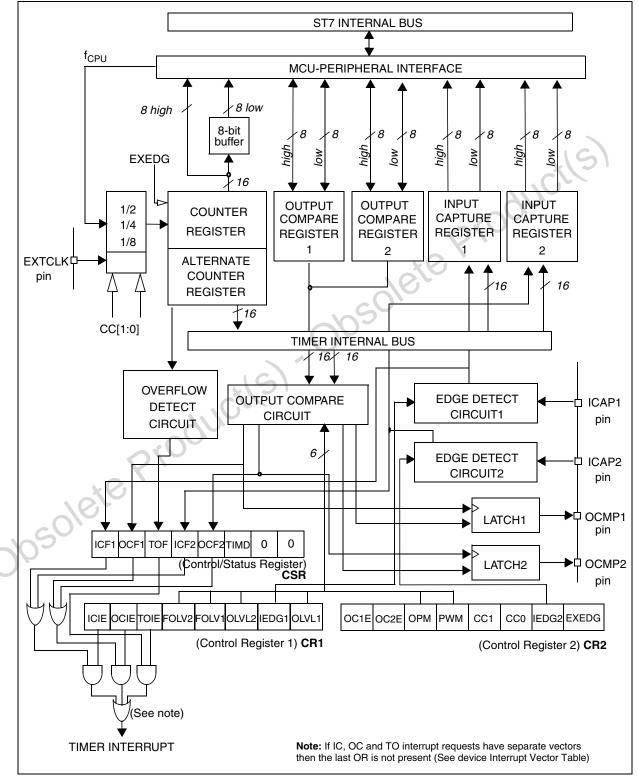

#### Figure 48. Timer Block Diagram

#### 10.4.3.3 Input Capture

In this section, the index, *i*, may be 1 or 2 because there are two input capture functions in the 16-bit timer.

The two 16-bit input capture registers (IC1R and IC2R) are used to latch the value of the free running counter after a transition is detected on the ICAP*i* pin (see Figure 52).

|      | MS Byte        | LS Byte        |

|------|----------------|----------------|

| ICiR | IC <i>i</i> HR | IC <i>i</i> LR |

IC*i*R register is a read-only register.

The active transition is software programmable through the IEDG*i* bit of Control Registers (CR*i*).

Timing resolution is one count of the free running counter:  $(f_{CPU}/CC[1:0])$ .

#### Procedure:

To use the input capture function select the following in the CR2 register:

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

- Select the edge of the active transition on the ICAP2 pin with the IEDG2 bit (the ICAP2 pin must be configured as floating input or input with pull-up without interrupt if this configuration is available).

And select the following in the CR1 register:

- Set the ICIE bit to generate an interrupt after an input capture coming from either the ICAP1 pin or the ICAP2 pin

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1pin must be configured as floating input or input with pullup without interrupt if this configuration is available).

When an input capture occurs:

- ICF*i* bit is set.

- The IC*i*R register contains the value of the free running counter on the active transition on the ICAP*i* pin (see Figure 53).

- A timer interrupt is generated if the ICIE bit is set and the I bit is cleared in the CC register. Otherwise, the interrupt remains pending until both conditions become true.

Clearing the Input Capture interrupt request (that is, clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set.

- 2. An access (read or write) to the ICiLR register.

#### Notes:

- 1. After reading the IC*i*HR register, transfer of input capture data is inhibited and ICF*i* will never be set until the IC*i*LR register is also read.

- 2. The IC/R register contains the free running counter value which corresponds to the most recent input capture.

- 3. The two input capture functions can be used together even if the timer also uses the two output compare functions.

- 4. In One Pulse mode and PWM mode only Input Capture 2 can be used.

- 5. The alternate inputs (ICAP1 and ICAP2) are always directly connected to the timer. So any transitions on these pins activates the input capture function. Moreover if one of the ICAP*i* pins is configured as an input and the second one as an output, an interrupt can be generated if the user toggles the output pin and if the ICIE bit is set.

This can be avoided if the input capture function i is disabled by reading the IC*i*HR (see note 1).

6. The TOF bit can be used with interrupt generation in order to measure events that go beyond the timer range (FFFFh).

**/**

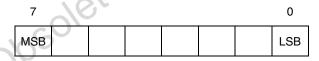

### 16-BIT TIMER (Cont'd) INPUT CAPTURE 1 HIGH REGISTER (IC1HR)

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

Read Only

<u>ل</u>رک

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

| 7                 |     |     |    |    |     |    | 0   |  |

|-------------------|-----|-----|----|----|-----|----|-----|--|

| MSB               |     |     |    |    |     |    | LSB |  |

|                   |     |     |    |    |     |    |     |  |

|                   |     |     |    |    |     | iG | Ń   |  |

|                   |     |     |    |    | . C |    |     |  |

|                   |     |     |    | -6 | JC  |    |     |  |

|                   |     |     | 05 | 0  |     |    |     |  |

|                   |     | .0. | X  |    |     |    |     |  |

|                   | 16  | 30  |    |    |     |    |     |  |

| S                 | ole |     |    |    |     |    |     |  |

| $O^{\mathcal{V}}$ |     |     |    |    |     |    |     |  |

|                   |     |     |    |    |     |    |     |  |

## OUTPUT COMPARE 1 HIGH REGISTER (OC1HR)

#### Read/Write

\_

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

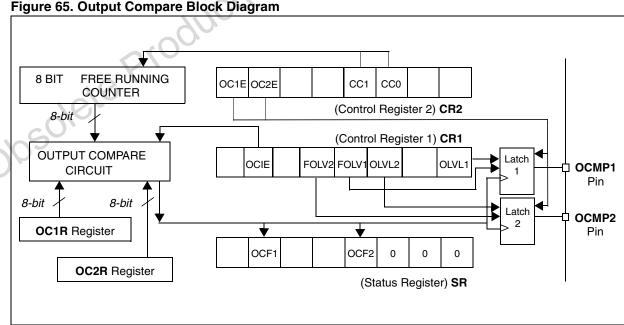

#### 10.5 8-BIT TIMER (TIM8)

#### 10.5.1 Introduction

The timer consists of a 8-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the clock prescaler.

#### 10.5.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4, 8 or f<sub>OSC2</sub> divided by 8000.

- Overflow status flag and maskable interrupt

- Output compare functions with

- 2 dedicated 8-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Input capture functions with

- 2 dedicated 8-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One pulse mode

- Reduced Power Mode

- 4 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2)\*

The Block Diagram is shown in Figure 59.

\*Note: Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

#### 10.5.3 Functional Description

#### 10.5.3.1 Counter

The main block of the Programmable Timer is a 8bit free running upcounter and its associated 8-bit registers.

These two read-only 8-bit registers contain the same value but with the difference that reading the ACTR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR).

Writing in the CTR register or ACTR register resets the free running counter to the FCh value. Both counters have a reset value of FCh (this is the only value which is reloaded in the 8-bit timer). The reset value of both counters is also FCh in One Pulse mode and PWM mode.

The timer clock depends on the clock control bits of the CR2 register, as shown in Table 19 Clock Control Bits. The value in the counter register repeats every 512, 1024, 2048 or 20480000  $f_{CPU}$  clock cycles depending on the CC[1:0] bits. The timer frequency can be  $f_{CPU}/2$ ,  $f_{CPU}/4$ ,  $f_{CPU}/8$  or  $f_{OSC2}$  /8000.

For example, if  $f_{OSC2}$ /8000 is selected, and  $f_{OSC2}$  = 8 MHz, the timer frequency will be 1 ms. Refer to Table 19 on page 105.

#### Notes:

**لركم**

- 1. Once the OCIE bit is set both output compare features may trigger interrupt requests. If only one is needed in the application, the interrupt routine software needs to discard the unwanted compare interrupt. This can be done by checking the OCF1 and OCF2 flags and resetting them both.

- 2. If the OCIE bit is not set, the OCMPi pin is a general I/O port and the OLVLi bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- 3. When the timer clock is f<sub>CPU</sub>/2, OCFi and OCMPi are set while the counter value equals the OCiR register value (see Figure 66 on page 99). This behaviour is the same in OPM or PWM mode.

When the timer clock is  $f_{CPU}\!/4,\,f_{CPU}\!/8$  or  $f_{CPU}\!/$ 8000, OCFi and OCMPi are set while the counter value equals the OC/R register value plus 1 (see Figure 67 on page 99).

- 4. The output compare functions can be used both for generating external events on the OCMPi pins even if the input capture mode is also used.

- 5. The value in the 8-bit OCiR register and the OLVi bit should be changed after each suc-

cessful comparison in order to control an output waveform or establish a new elapsed timeout.

#### Forced Compare Output capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit = 1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVLi bits have no effect in both one pulse solete Product mode and PWM mode.

#### 10.5.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 8-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                       |

|      | 8-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                            |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

#### 10.5.5 Interrupts

| Interrupt Event                                    |   | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|---|---------------|--------------------------|----------------------|----------------------|

| Input Capture 1 event/Counter reset in PWM mode    |   | ICF1          | ICIE                     |                      |                      |

| Input Capture 2 event                              |   | ICF2          |                          |                      |                      |

| Output Compare 1 event (not available in PWM mode) |   | OCF1          | OCIE                     | Yes                  | No                   |

| Output Compare 2 event (not available in PWM mode) |   | OCF2          | OCIE                     |                      |                      |

| Timer Overflow event                               | S | TOF           | TOIE                     |                      |                      |

**Note:** The 8-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

#### 10.5.6 Summary of Timer modes

| MODES                       | AVAILABLE RESOURCES |                               |                  |                         |  |  |  |

|-----------------------------|---------------------|-------------------------------|------------------|-------------------------|--|--|--|

| MODES                       | Input Capture 1     | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |  |

| Input Capture (1 and/or 2)  | Yes                 | Yes                           | Yes              | Yes                     |  |  |  |

| Output Compare (1 and/or 2) | 165                 | 165                           | 165              | 163                     |  |  |  |

| One Pulse Mode              | No                  | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |  |

| PWM Mode                    | NO                  | Not Recommended <sup>3)</sup> | NO               | No                      |  |  |  |

1) See note 4 in "One Pulse Mode" on page 100

2) See note 5 in "One Pulse Mode" on page 100

3) See note 4 in "Pulse Width Modulation Mode" on page 102

#### 8-BIT TIMER (Cont'd) 10.5.8 8-bit Timer Register Map

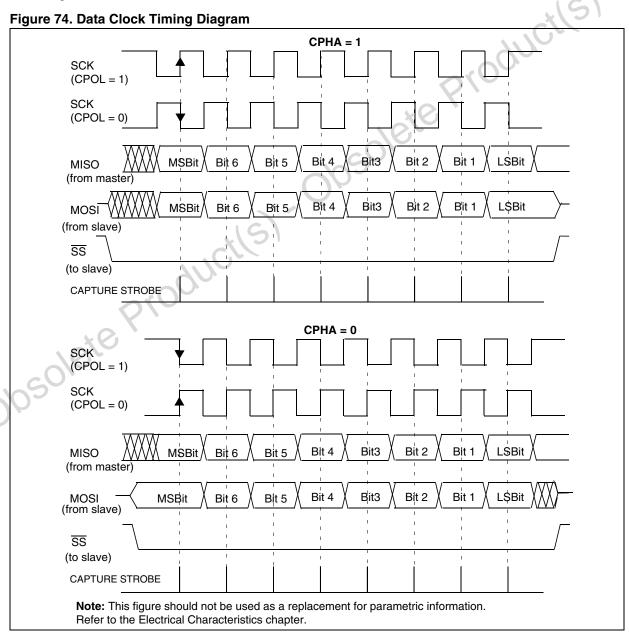

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

#### How to operate the SPI in master mode

To operate the SPI in master mode, perform the following steps in order:

- Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 74 shows the four possible configurations. **Note:** The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

Note: MSTR and SPE bits remain set only if SS is high).

Important note: if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account.

The transmit sequence begins when software writes a byte in the SPIDR register.

#### 10.6.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register

Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.6.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see Figure 74). Note: The slave must have the same CPOL and CPHA settings as the master.

- Manage the  $\overline{SS}$  pin as described in Section 10.6.3.2 and Figure 72. If CPHA = 1 SS must be held low continuously. If CPHA = 0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

#### 10.6.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- A write or a read to the SPIDR register

Notes: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.6.5.2).

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.4 Clock Phase and Clock Polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 74).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge.

Figure 74 shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin and the MOSI pin are directly connected between the master and the slave device.

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

## **/**

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the device is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the Device. |

## 10.6.6.1 Using the SPI to wake up the device from Halt mode

In slave configuration, the SPI is able to wake up the device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

Note: When waking up from HALT mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from HALT mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the device from HALT mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the device enters HALT mode. So, if Slave selection is configured as external (see Section 10.6.3.2), make sure the master drives a low level on the SS pin when the slave enters HALT mode.

#### 10.6.7 Interrupts

|                              |               |                          | X \                  |                      |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

| SPI End of<br>Transfer Event | SPIF          | 0                        |                      | Yes                  |

| Master Mode<br>Fault Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          |                      |                      |

|                              | -             | •                        |                      |                      |

**Note:** The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

#### 10.7.5.6 Receiver Muting and Wake-up Feature

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non-addressed receivers.

The non-addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits can not be set.

All the receive interrupts are inhibited.

A muted receiver may be woken up in one of the following ways:

- by Idle Line detection if the WAKE bit is reset,

- by Address Mark detection if the WAKE bit is set.

#### Idle Line Detection

Receiver wakes up by Idle Line detection when the Receive line has recognized an Idle Line. Then the RWU bit is reset by hardware but the IDLE bit is not set.

This feature is useful in a multiprocessor system when the first characters of the message determine the address and when each message ends by an idle line: As soon as the line becomes idle, every receivers is waken up and analyse the first characters of the message which indicates the addressed receiver. The receivers which are not addressed set RWU bit to enter in mute mode. Consequently, they will not treat the next characters constituting the next part of the message. At the end of the message, an idle line is sent by the transmitter: this wakes up every receivers which are ready to analyse the addressing characters of the new message.

In such a system, the inter-characters space must be smaller than the idle time.

#### Address Mark Detection

Receiver wakes up by Address Mark detection when it received a "1" as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

This feature is useful in a multiprocessor system when the most significant bit of each character (except for the break character) is reserved for Address Detection. As soon as the receivers received an address character (most significant bit = '1'), the receivers are waken up. The receivers which are not addressed set RWU bit to enter in mute mode. Consequently, they will not treat the next characters constituting the next part of the message.

#### 10.7.5.7 Parity Control

Hardware byte Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the character format defined by the M bit, the possible SCI character formats are as listed in Table 1.

**Note**: In case of wake-up by an address mark, the MSB bit of the data is taken into account and not the parity bit

#### Table 23. Character Formats

| M bit | PCE bit | Character format           |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | Ϋ́      | SB   7-bit data   PB   STB |

| 5     | 0       | SB   9-bit data   STB      |

| Q     | 1       | SB   8-bit data   PB   STB |

**Legend:** SB = Start Bit, STB = Stop Bit, PB = Parity Bit

**Even parity:** The parity bit is calculated to obtain an even number of "1s" inside the character made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit will be 0 if even parity is selected (PS bit = 0).

**Odd parity:** The parity bit is calculated to obtain an odd number of "1s" inside the character made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit will be 1 if odd parity is selected (PS bit = 1).

**Transmission mode:** If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**Reception mode:** If the PCE bit is set then the interface checks if the received data byte has an even number of "1s" if even parity is selected (PS = 0) or an odd number of "1s" if odd parity is selected (PS = 1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PCIE is set in the SCICR1 register.

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

#### **BAUD RATE REGISTER (SCIBRR)**

Read/Write Reset Value: 0000 0000 (00h)

| 7    | 7    |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|

| SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

Note: When LIN slave mode is disabled, the SCI-BRR register controls the conventional baud rate generator.

Bits 7:6 = SCP[1:0] First SCI Prescaler

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| 1                    | 0    | 0    |

| 3                    | 0    | 1    |

| 4                    | -    | 0    |

| 13                   | 1    | 1    |

Bits 5:3 = **SCT[2:0]** SCI Transmitter rate divisor These 3 bits, in conjunction with the SCP1 and SCP0 bits define the total division applied to the Josolete Productle bus clock to yield the transmit rate clock in conven-

| TR dividing factor | SCT2 | SCT1 | SCT0 |

|--------------------|------|------|------|

| 1                  |      | _    | 0    |

| 2                  |      | 0    | 1    |

| 4                  | 0    | -    | 0    |

| 8                  |      | I    | 1    |

| 16                 |      | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                |      | I    | 1    |

|                    |      |      | G    |

Bits 2:0 = SCR[2:0] SCI Receiver rate divider These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR dividing factor | SCR2             | SCR1 | SCR0 |  |  |  |  |

|--------------------|------------------|------|------|--|--|--|--|

| 1                  |                  | 0    | 0    |  |  |  |  |

| 2                  | 2 0<br>4 8<br>16 | 0    | 1    |  |  |  |  |

| 4                  |                  | 4    | 0    |  |  |  |  |

| 8                  |                  | I    | 1    |  |  |  |  |

| 16                 |                  | 0    | 0    |  |  |  |  |

| 32                 | 4                | 0    | 1    |  |  |  |  |

| 64                 | 64<br>128        | 4    | 0    |  |  |  |  |

| 128                |                  | I    | 1    |  |  |  |  |

|                    |                  |      |      |  |  |  |  |

<u>ل</u>رک

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.7 LINSCI Clock Tolerance

#### LINSCI Clock Tolerance when unsynchronized

When LIN slaves are unsynchronized (meaning no characters have been transmitted for a relatively long time), the maximum tolerated deviation of the LINSCI clock is +/-15%.

If the deviation is within this range then the LIN Synch Break is detected properly when a new reception occurs.

This is made possible by the fact that masters send 13 low bits for the LIN Synch Break, which can be interpreted as 11 low bits (13 bits -15% = 11.05) by a "fast" slave and then considered as a LIN Synch Break. According to the LIN specification, a LIN Synch Break is valid when its duration is greater than  $t_{\text{SBRKTS}} = 10$ . This means that the LIN Synch Break must last at least 11 low bits.

**Note:** If the period desynchronization of the slave is +15% (slave too slow), the character "00h" which represents a sequence of 9 low bits must not be interpreted as a break character (9 bits + 15% = 10.35). Consequently, a valid LIN Synch break must last at least 11 low bits.

#### LINSCI Clock Tolerance when Synchronized

When synchronization has been performed, following reception of a LIN Synch Break, the LINS-CI, in LIN mode, has the same clock deviation tolerance as in SCI mode, which is explained below:

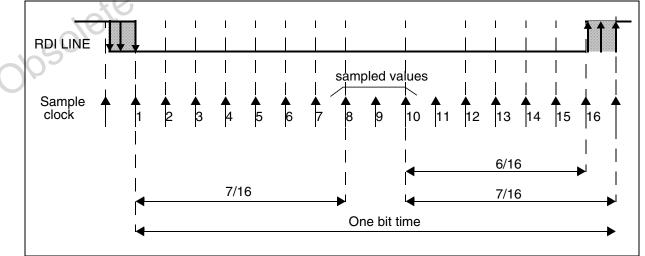

During reception, each bit is oversampled 16 times. The mean of the 8th, 9th and 10th samples is considered as the bit value.

Figure 86.Bit Sampling in Reception Mode

67/

Consequently, the clock frequency should not vary more than 6/16 (37.5%) within one bit.

The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation should not exceed 3.75%.

#### 10.7.9.8 Clock Deviation Causes

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error.

Note: The transmitter can be either a master or a slave (in case of a slave listening to the response of another slave).

- D<sub>MEAS</sub>: Error due to the LIN Synch measurement performed by the receiver.

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete LIN message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the LINSCI clock tolerance:

$D_{TRA} + D_{MEAS} + D_{QUANT} + D_{REC} + D_{TCL} < 3.75\%$

#### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

#### 10.8.4.4 Conventional Baud Rate Generation

The baud rates for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows

:

$$Tx = \frac{f_{CPU}}{(16*PR)*TR} \qquad Rx = \frac{f_{CPU}}{(16*PR)*RR}$$

with:

PR = 1, 3, 4 or 13 (see SCP[1:0] bits)

TR = 1, 2, 4, 8, 16, 32, 64, 128

(see SCT[2:0] bits)

RR = 1, 2, 4, 8, 16, 32, 64, 128

(see SCR[2:0] bits)

All these bits are in the SCIBRR register.

**Example:** If  $f_{CPU}$  is 8 MHz (normal mode) and if PR = 13 and TR = RR = 1, the transmit and receive baud rates are 38400 baud.

**Note:** The baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

#### 10.8.4.5 Extended Baud Rate Generation

The extended prescaler option gives a very fine tuning on the baud rate, using a 255 value prescaler, whereas the conventional Baud Rate Generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in the Figure 90.

The output clock rate sent to the transmitter or to the receiver is the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCI-ERPR or the SCIETPR register.

**Note:** The extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value

other than zero. The baud rates are calculated as follows:

$$Tx = \frac{f_{CPU}}{16 \cdot ETPR^{*}(PR^{*}TR)} Rx = \frac{f_{CPU}}{16 \cdot ERPR^{*}(PR^{*}RR)}$$

with:

ETPR = 1, ..., 255 (see SCIETPR register)

ERPR = 1, ..., 255 (see SCIERPR register)

#### 10.8.4.6 Receiver Muting and Wake-up Feature

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non addressed receivers.

The non addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits cannot be set.

All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

- by Idle Line detection if the WAKE bit is reset,

- by Address Mark detection if the WAKE bit is set.

Receiver wakes-up by Idle Line detection when the Receive line has recognized an Idle Frame. Then the RWU bit is reset by hardware but the IDLE bit is not set.

Receiver wakes-up by Address Mark detection when it received a "1" as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

157/225

**/**

#### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

#### EXTENDED RECEIVE PRESCALER DIVISION **REGISTER (SCIERPR)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ERPR |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

#### Bits 7:0 = ERPR[7:0] 8-bit Extended Receive Prescaler Register.

The extended Baud Rate Generator is activated when a value other than 00h is stored in this register. The clock frequency from the 16 divider (see Figure 90) is divided by the binary factor set in the SCIERPR register (in the range 1 to 255).

The extended baud rate generator is not active after a reset.

#### **EXTENDED TRANSMIT PRESCALER DIVISION REGISTER (SCIETPR)**

Read/Write

Reset Value:0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ETPR |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

#### Bits 7:0 = ETPR[7:0] 8-bit Extended Transmit Prescaler Register.

The extended Baud Rate Generator is activated when a value other than 00h is stored in this register. The clock frequency from the 16 divider (see Figure 90) is divided by the binary factor set in the SCIETPR register (in the range 1 to 255).

The extended baud rate generator is not active after a reset.

**/رک**ا

| Table 27. Baud R | ate Selection |

|------------------|---------------|

|------------------|---------------|

|                                    |                         | Conditions       |                          |                                                                                                                                                                                                                                               |                                                                | Devel                                                      |      |

|------------------------------------|-------------------------|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|------|

| Symbol                             | Parameter               | f <sub>CPU</sub> | Accuracy vs.<br>Standard | Prescaler                                                                                                                                                                                                                                     | Standard                                                       | Baud<br>Rate                                               | Unit |

| f <sub>Tx</sub><br>f <sub>Rx</sub> | Communication frequency | 8 MHz            | ~0.16%                   | Conventional Mode<br>TR (or RR) = 128, PR = 13<br>TR (or RR) = 32, PR = 13<br>TR (or RR) = 16, PR = 13<br>TR (or RR) = 8, PR = 13<br>TR (or RR) = 4, PR = 13<br>TR (or RR) = 16, PR = 3<br>TR (or RR) = 2, PR = 13<br>TR (or RR) = 1, PR = 13 | 300<br>1200<br>2400<br>4800<br>9600<br>10400<br>19200<br>38400 | ~2403.84<br>~4807.69<br>~9615.38<br>~10416.67<br>~19230.77 | Hz   |

| <u> </u>                           | (et                     |                  | ~0.79%                   | Extended Mode<br>ETPR (or ERPR) = 35,<br>TR (or RR) = 1, PR = 1                                                                                                                                                                               | 14400                                                          | ~14285.71                                                  |      |

## **15 DEVELOPMENT TOOLS**

Development tools for the ST7 microcontrollers include a complete range of hardware systems and software tools from STMicroelectronics and thirdparty tool suppliers. The range of tools includes solutions to help you evaluate microcontroller peripherals, develop and debug your application, and program your microcontrollers.

#### 15.0.1 Evaluation Tools and Starter Kits

ST offers complete, affordable **starter kits** and full-featured **evaluation boards** that allow you to evaluate microcontroller features and quickly start developing ST7 applications. Starter kits are complete, affordable hardware/software tool packages that include features and samples to help you quickly start developing your application. ST evaluation boards are open-design, embedded systems, which are developed and documented to serve as references for your application design. They include sample application software to help you demonstrate, learn about and implement your ST7's features.

#### 15.0.2 Development and Debugging Tools

Application development for ST7 is supported by fully optimizing **C Compilers** and the **ST7 Assembler-Linker** toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The Cosmic C Compiler is available in a free version that outputs up to 16K of code. The range of hardware tools includes cost effective **ST7-DVP3 series emulators**. These tools are supported by the **ST7 Toolset** from STMicroelectronics, which includes the STVD7 integrated development environment (IDE) with high-level language debugger, editor, project manager and integrated programming interface.

#### 15.0.3 Programming Tools

During the development cycle, the **ST7-DVP3** and **ST7-EMU3 series emulators** and the **RLink** provide in-circuit programming capability for programming the Flash microcontroller on your application board.

ST also provides dedicated a low-cost dedicated in-circuit programmer, the **ST7-STICK**, as well as **ST7 Socket Boards** which provide all the sockets required for programming any of the devices in a specific ST7 sub-family on a platform that can be used with any tool with in-circuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.

For additional ordering codes for spare parts, accessories and tools available for the ST7 (including from third party manufacturers), refer to the online product selector at www.st.com.

#### 15.0.4 Order Codes for ST72361 Development Tools

#### Table 37. Development Tool Order Codes for the ST72361 Family

| -010    | In-circuit Debugger            |                             | Program                                              | ning Tool                      |

|---------|--------------------------------|-----------------------------|------------------------------------------------------|--------------------------------|

| MCU     | Starter Kit with Demo<br>Board | Emulator                    | In-circuit<br>Programmer                             | ST7 Socket Board <sup>6)</sup> |

| ST72361 | ST72F36X-SK/RAIS <sup>1)</sup> | ST7MDT25-DVP3 <sup>2)</sup> | ST7-STICK <sup>3)4)</sup><br>STX-RLINK <sup>5)</sup> | ST7SB25 <sup>3)</sup>          |

#### Notes:

1. In-circuit programming only. In-circuit debugging is not yet supported for HDFlash devices without debug module such as the ST72F36x.

2. Requires optional connection kit. See "How to order and EMU or DVP" for connection kit ordering information in ST product and tool selection guide

3. Add suffix /EU, /UK or /US for the power supply for your region

4. Parellel port connection to PC

5. USB connection to PC

6. Socket boards complement any tool with ICC capabilities (ST7-STICK, InDART, RLINK, DVP3, EMU3, etc.)