Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | LINbusSCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1.5K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f361k6t3 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

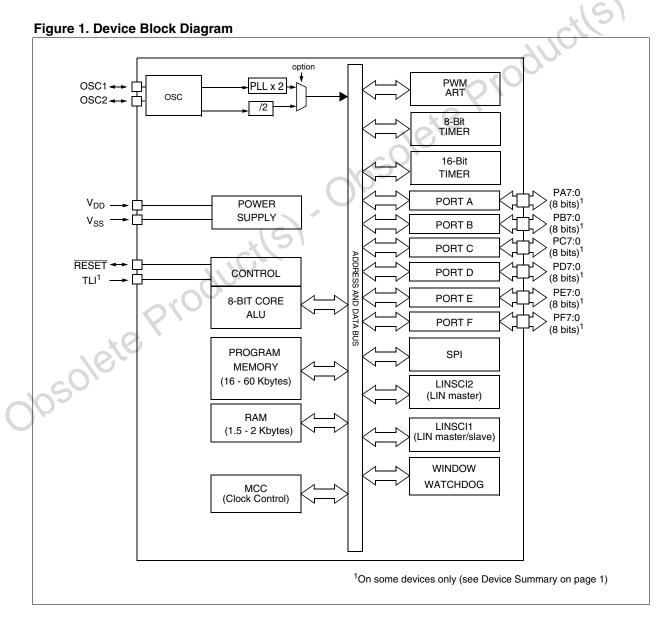

# **1 DESCRIPTION**

The ST72361 devices are members of the ST7 microcontroller family designed for mid-range applications with LIN (Local Interconnect Network) interface.

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruction set and are available with Flash or ROM program memory. The ST7 family architecture offers both power and flexibility to software developers, enabling the design of highly efficient and compact application code. The on-chip peripherals include an A/D converter, a PWM Autoreload timer, 2 general purpose timers, 2 asynchronous serial interfaces, and an SPI interface.

For power economy, microcontroller can switch dynamically into WAIT, SLOW, Active-Halt, Auto Wake-up from HALT (AWU) or HALT mode when the application is in idle or stand-by state.

Typical applications are consumer, home, office and industrial products.

<u>لرکم</u>

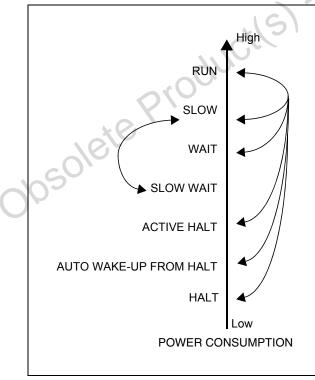

# **8 POWER SAVING MODES**

### **8.1 INTRODUCTION**

To give a large measure of flexibility to the application in terms of power consumption, five main power saving modes are implemented in the ST7 (see Figure 22):

- Slow

- Wait (and Slow-Wait)

- Active Halt

- Auto Wake-up From Halt (AWUFH)

- Halt

**67/**

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 ( $f_{OSC2}$ ).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

### Figure 22. Power Saving Mode Transitions

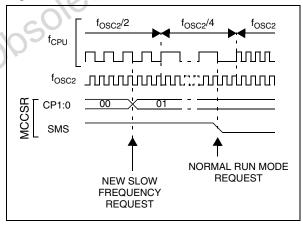

## 8.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

SLOW mode is controlled by three bits in the MCCSR register: the SMS bit which enables or disables Slow mode and two CPx bits which select the internal slow frequency (f<sub>CPU</sub>).

In this mode, the master clock frequency ( $f_{OSC2}$ ) can be divided by 2, 4, 8 or 16. The CPU and peripherals are clocked at this lower frequency ( $f_{CPU}$ ).

**Note**: SLOW-WAIT mode is activated by entering WAIT mode while the device is in SLOW mode.

### Figure 23. SLOW Mode Clock Transitions

#### POWER SAVING MODES (Cont'd)

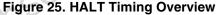

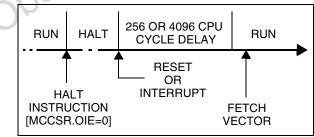

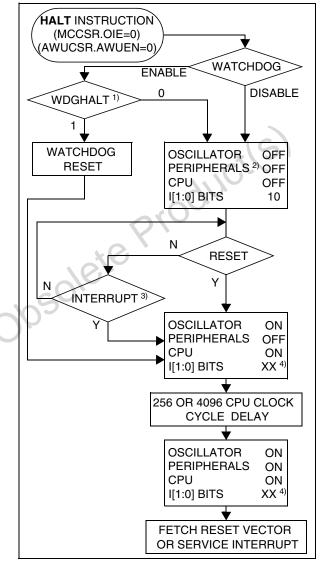

#### 8.4 HALT MODE

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see Section 10.2 on page 58 for more details on the MCCSR register) and when the AWUEN bit in the AWUCSR register is cleared.

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 9, "Interrupt Mapping," on page 33) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 26).

When entering HALT mode, the I[1:0] bits in the CC register are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see Section 10.1 on page 52 for more details).

Figure 26. HALT Mode Flow-chart

#### Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 33 for more details.

**4.** Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

# 57

### **POWER SAVING MODES** (Cont'd)

### Figure 31. AWUFH Mode Flow-chart

#### Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only an AWUFH interrupt and some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 33 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

57

## **ON-CHIP PERIPHERALS** (Cont'd)

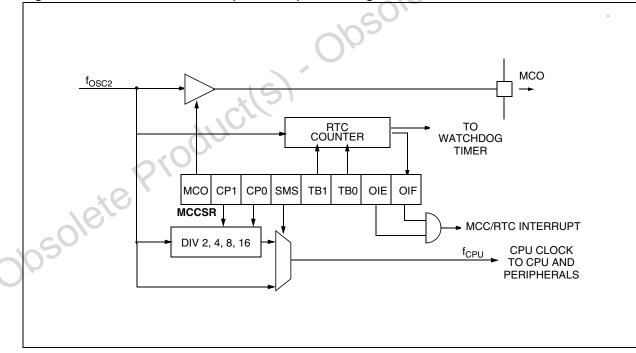

# 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK MCC/RTC

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real time clock timer with interrupt capability

Each function can be used independently and simultaneously.

# 10.2.1 Programmable CPU Clock Prescaler

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages SLOW power saving mode (See Section 8.2 "SLOW MODE" for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

# 10.2.2 Clock-out Capability

The clock-out capability is an alternate function of an I/O port pin that outputs a  $f_{OSC2}$  clock to drive external devices. It is controlled by the MCO bit in the MCCSR register.

# 10.2.3 Real Time Clock Timer (RTC)

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by 4 bits of the MCCSR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE HALT mode when the HALT instruction is executed. See Section 8.5 "ACTIVE HALT MODE" for more details.

**/رک**ا

# Figure 39. Main Clock Controller (MCC/RTC) Block Diagram

### **ON-CHIP PERIPHERALS** (Cont'd)

# INPUT CAPTURE CONTROL / STATUS REGISTER (ARTICCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |     |     |      |      |     | 0   |

|---|---|-----|-----|------|------|-----|-----|

| 0 | 0 | CS2 | CS1 | CIE2 | CIE1 | CF2 | CF1 |

Bit 7:6 = Reserved, always read as 0.

#### Bit 5:4 = **CS[2:1]** Capture Sensitivity

These bits are set and cleared by software. They determine the trigger event polarity on the corresponding input capture channel.

0: Falling edge triggers capture on channel x.

1: Rising edge triggers capture on channel x.

Bit 3:2 = **CIE[2:1]** Capture Interrupt Enable

These bits are set and cleared by software. They enable or disable the Input capture channel interrupts independently.

0: Input capture channel x interrupt disabled. 1: Input capture channel x interrupt enabled.

### Bit 1:0 = CF[2:1] Capture Flag

These bits are set by hardware and cleared by software reading the corresponding ARTICRx register. Each CFx bit indicates that an input capture x has occurred.

0: No input capture on channel x.

)bsolet

<u>ل</u>حک

1: An input capture has occurred on channel x.

### **INPUT CAPTURE REGISTERS (ARTICRx)**

Read only

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IC7 | IC6 | IC5 | IC4 | IC3 | IC2 | IC1 | IC0 |

### Bit 7:0 = IC[7:0] Input Capture Data

These read only bits are set and cleared by hardware. An ARTICRx register contains the 8-bit auto-reload counter value transferred by the input capture channel x event.

# 16-BIT TIMER (Cont'd) 10.4.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                      |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                           |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

### 10.4.5 Interrupts

| Interrupt Event                                    |   | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|---|---------------|--------------------------|----------------------|----------------------|

| Input Capture 1 event/Counter reset in PWM mode    |   | ICF1          | ICIE                     |                      |                      |

| Input Capture 2 event                              |   | ICF2          | ICIE                     |                      |                      |

| Output Compare 1 event (not available in PWM mode) |   | OCF1          | OCIE                     | Yes                  | No                   |

| Output Compare 2 event (not available in PWM mode) |   | OCF2          | OCIE                     |                      |                      |

| Timer Overflow event                               | S | TOF           | TOIE                     |                      |                      |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# 10.4.6 Summary of Timer Modes

| MODES                       | TIMER RESOURCES |                               |                  |                         |  |  |  |

|-----------------------------|-----------------|-------------------------------|------------------|-------------------------|--|--|--|

| MODES                       | Input Capture 1 | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |  |

| Input Capture (1 and/or 2)  | Yes             | Yes                           | Yes              | Yes                     |  |  |  |

| Output Compare (1 and/or 2) | 165             | 165                           | 165              | 165                     |  |  |  |

| One Pulse Mode              | No              | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |  |

| PWM Mode                    | NO              | Not Recommended <sup>3)</sup> | NO               | No                      |  |  |  |

1) See note 4 in Section 10.4.3.5 "One Pulse Mode"

2) See note 5 in Section 10.4.3.5 "One Pulse Mode"

3) See note 4 in Section 10.4.3.6 "Pulse Width Modulation Mode"

<u>ل</u>رک

16

# 16-BIT TIMER (Cont'd) CONTROL REGISTER 2 (CR2)

### Read/Write

Reset Value: 0000 0000 (00h)

| 1    |      |     |     |     |     |       | 0     |

|------|------|-----|-----|-----|-----|-------|-------|

| OC1E | OC2E | OPM | PWM | CC1 | CC0 | IEDG2 | EXEDG |

### Bit 7 = **OC1E** *Output Compare 1 Pin Enable.*

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

#### Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

# Bit 5 = **OPM** One Pulse Mode.

0: One Pulse mode is not active.

1: One Pulse mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

#### Bit 4 = **PWM** *Pulse Width Modulation.*

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

### Bit 3, 2 = **CC[1:0]** *Clock Control.*

The timer clock mode depends on these bits:

#### Table 18. Clock Control Bits

| Timer Clock                      | CC1 | CC0 |

|----------------------------------|-----|-----|

| f <sub>CPU</sub> / 4             | 0   | 0   |

| f <sub>CPU</sub> / 2             |     | 1   |

| f <sub>CPU</sub> / 8             | 1   | 0   |

| External Clock (where available) |     | 1   |

**Note**: If the external clock pin is not available, programming the external clock configuration stops the counter.

### Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture. 0: A falling edge triggers the capture. 1: A rising edge triggers the capture.

#### Bit 0 = **EXEDG** External Clock Edge.

This bit determines which type of level transition on the external clock pin EXTCLK will trigger the counter register.

0: A falling edge triggers the counter register. 1: A rising edge triggers the counter register.

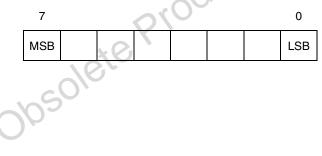

# 8-BIT TIMER (Cont'd) INPUT CAPTURE 1 REGISTER (IC1R)

Read Only

\_

Reset Value: Undefined

This is an 8-bit read only register that contains the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

### **OUTPUT COMPARE 1 REGISTER (OC1R)**

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the value to be compared to the CTR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## **OUTPUT COMPARE 2 REGISTER (OC2R)**

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the value to be compared to the CTR register.

#### **COUNTER REGISTER (CTR)**

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

|     |  |  |  |     |

# ALTERNATE COUNTER REGISTER (ACTR)

Read Only Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| G   | 0 |  |  |  |  |  |     |  |  |

|-----|---|--|--|--|--|--|-----|--|--|

| MSB |   |  |  |  |  |  | LSB |  |  |

### **INPUT CAPTURE 2 REGISTER (IC2R)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

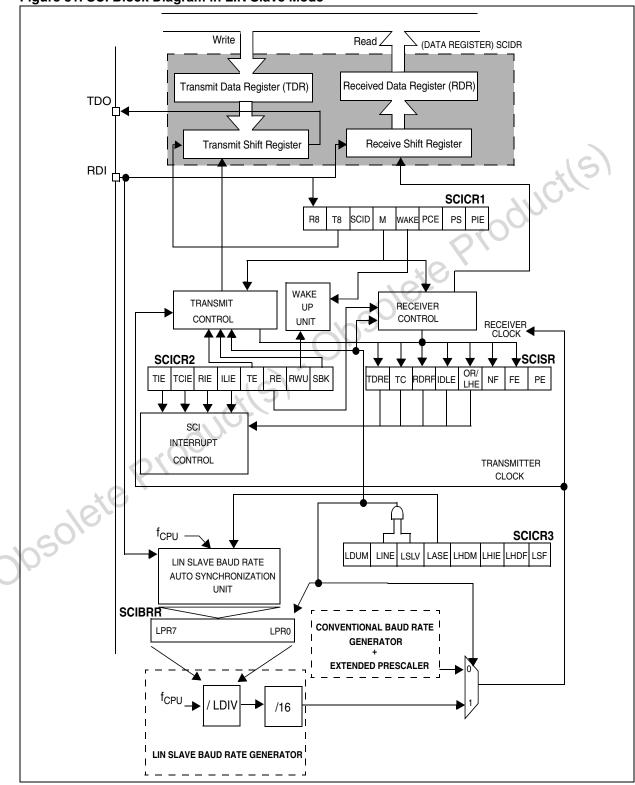

### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

### 10.7.5 SCI Mode - Functional Description

#### **Conventional Baud Rate Generator Mode**

The block diagram of the Serial Control Interface in conventional baud rate generator mode is shown in Figure 1.

It uses four registers:

<u>ل</u>رک

- 2 control registers (SCICR1 and SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

#### **Extended Prescaler Mode**

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

## Figure 78. Word Length Programming

#### 10.7.5.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 2).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as a continuous logic high level for 10 (or 11) full bit times.

A Break character is a character with a sufficient number of low level bits to break the normal data format followed by an extra "1" bit to acknowledge the start bit.

|   | Extended           | rrescaler would                                                                    | format followed by an ex   | tra "1" bit to acknowledge |

|---|--------------------|------------------------------------------------------------------------------------|----------------------------|----------------------------|

|   |                    | ional prescalers are available in extend-<br>ler mode. They are shown in Figure 3. | the start bit.             | ctlest                     |

| - | – An exter<br>PR)  | nded prescaler receiver register (SCIER-                                           |                            | oducite                    |

| - | – An exte<br>ETPR) | nded prescaler transmitter register (SCI-                                          | P                          |                            |

|   | Figure 78          | 8. Word Length Programming                                                         |                            |                            |

|   |                    | 9-bit Word length (M bit is set)                                                   | Possible                   |                            |

|   |                    | Data Character                                                                     | Possible<br>Parity<br>Bit  | Next Data Character        |

|   |                    | Start<br>Bit Bit0 Bit1 Bit2 Bit3 Bit4 Bit5                                         | Bit6 Bit7 Bit8 Stop<br>Bit | Start<br>Bit               |

|   |                    | Idle Line                                                                          |                            | Start<br>Bit               |

|   |                    | Break Character                                                                    |                            | Extra Start                |

|   |                    | Dieak Character                                                                    |                            | '1' Bit                    |

|   |                    | 8-bit Word length (M bit is reset)                                                 | Possible                   | Next Data Character        |

|   | <u> </u>           | Data Character                                                                     | Parity<br>Bit Ne           |                            |

|   | Q                  | Start<br>Bit Bit0 Bit1 Bit2 Bit3 Bit4 B                                            | it5 Bit6 Bit7 Stop Bit Bi  | art<br>t                   |

|   |                    |                                                                                    | Sta                        | art                        |

|   |                    | Idle Line                                                                          | Bi                         | t                          |

|   |                    | Break Character                                                                    | Ext<br>'1                  |                            |

|   |                    |                                                                                    |                            |                            |

### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

#### 10.7.5.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### Character Transmission

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 1).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to send a preamble of 10 (M = 0) or 11 (M = 1) consecutive ones (Idle Line) as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

- The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I[1:0] bits are cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission. When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set.

When a character transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I[1:0] bits are cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### Break Characters

Setting the SBK bit loads the shift register with a break character. The break character length depends on the M bit (see Figure 2).

As long as the SBK bit is set, the SCI sends break characters to the TDO pin. After clearing this bit by software, the SCI inserts a logic 1 bit at the end of the last break character to guarantee the recognition of the start bit of the next character.

### Idle Line

Setting the TE bit drives the SCI to send a preamble of 10 (M = 0) or 11 (M = 1) consecutive '1's (idle line) before the first character.

In this case, clearing and then setting the TE bit during a transmission sends a preamble (idle line) after the current word. Note that the preamble duration (10 or 11 consecutive '1's depending on the M bit) does not take into account the stop bit of the previous character.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

# LINSCI<sup>™</sup> SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd) Figure 81. SCI Block Diagram in LIN Slave Mode

57

137/225

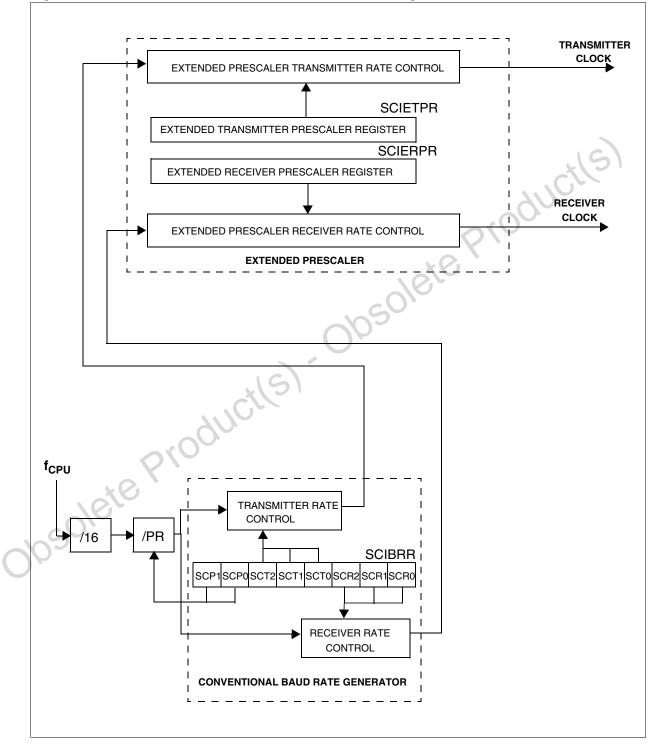

### 10.8 LINSCI SERIAL COMMUNICATION INTERFACE (LIN Master Only)

#### 10.8.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

### 10.8.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud.

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- 2 receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- 4 error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- 5 interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Transmitter clock output

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

- LIN Synch Break send capability

#### **10.8.3 General Description**

The interface is externally connected to another device by three pins (see Figure 88 on page 153). Any SCI bidirectional communication requires a minimum of two pins: Receive Data In (RDI) and Transmit Data Out (TDO):

- SCLK: Transmitter clock output. This pin outputs the transmitter data clock for synchronous transmission (no clock pulses on start bit and stop bit, and a software option to send a clock pulse on the last data bit). This can be used to control peripherals that have shift registers (e.g. LCD drivers). The clock phase and polarity are software programmable.

- TDO: Transmit Data Output. When the transmitter is disabled, the output pin returns to its I/O port configuration. When the transmitter is enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete.

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates,

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies.

<u>ل ۲</u>

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

### Figure 90. SCI Baud Rate and Extended Prescaler Block Diagram

Ĺ**Ţ**

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd) CONTROL REGISTER 2 (SCICR2)

Λ

#### Read/Write

Reset Value: 0000 0000 (00h)

7

| '   |      |     |      |    |    |     | Ũ   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TDRE = 1 in the SCISR register

Bit 6 = **TCIE** *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC = 1 in the SCISR register

Bit 5 = **RIE** *Receiver interrupt enable.*

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR = 1 or RDRF = 1 in the SCISR register

Bit 4 = ILIE Idle line interrupt enable.

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE = 1 in the SCISR register.

### Bit 3 = **TE** Transmitter enable.

This bit enables the transmitter. It is set and cleared by software.

- 0: Transmitter is disabled

- 1: Transmitter is enabled

## Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

#### Bit 2 = RE Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

### Bit 1 = RWU Receiver wake-up.

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

0: Receiver in active mode

1: Receiver in mute mode

### Notes:

- Before selecting Mute mode (by setting the RWU bit) the SCI must first receive a data byte, otherwise it cannot function in Mute mode with wakeup by Idle line detection.

- In Address Mark Detection Wake-Up configuration (WAKE bit = 1) the RWU bit cannot be modified by software while the RDRF bit is set.

### Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

## CONTROL PIN CHARACTERISTICS (Cont'd)

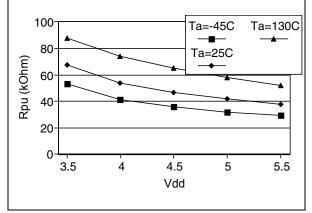

# Figure 114. RESET R<sub>PU</sub> vs V<sub>DD</sub>

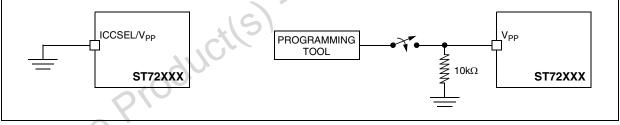

# 12.10.2 ICCSEL/V<sub>PP</sub> Pin

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{OSC}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol          | Parameter                              | Conditions                        | Min                  | Max  | Unit |

|-----------------|----------------------------------------|-----------------------------------|----------------------|------|------|

| V <sub>IL</sub> | Input low level voltage <sup>1)</sup>  |                                   | V <sub>SS</sub>      | 0.2  | V    |

| V <sub>IH</sub> | Input high level voltage <sup>1)</sup> | cO'                               | V <sub>DD</sub> -0.1 | 12.6 | v    |

| ١L              | Input leakage current                  | V <sub>IN</sub> = V <sub>SS</sub> |                      | ±1   | μA   |

# Figure 115. Two Typical Applications with ICCSEL/V<sub>PP</sub> Pin<sup>2)</sup>

#### Notes:

1. Data based on design simulation and/or technology characteristics, not tested in production.

2. When ICC mode is not required by the application ICCSEL/V<sub>PP</sub> pin must be tied to  $V_{SS}$ .

ductle

## COMMUNICATIONS INTERFACE CHARACTERISTICS (Cont'd)

## **12.13 10-BIT ADC CHARACTERISTICS**

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol            | Parameter                                                                                 | Conditions                                                                | Min <sup>1)</sup> | Тур | Max <sup>1)</sup> | Unit               |

|-------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------|-----|-------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                       |                                                                           | 0.4               |     | 4                 | MHz                |

| V <sub>AIN</sub>  | Conversion voltage range <sup>2)</sup>                                                    |                                                                           | V <sub>SSA</sub>  |     | V <sub>DDA</sub>  | V                  |

| R <sub>AIN</sub>  | External input impedance                                                                  |                                                                           |                   |     | see Figure        | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                        |                                                                           |                   |     | 119 and           | рF                 |

| f <sub>AIN</sub>  | Variation frequency of analog input signal                                                |                                                                           |                   |     | Figure<br>120     | Hz                 |

| l <sub>lkg</sub>  | Negative input leakage current on ro-<br>bust analog pins (refer to Table 2 on<br>page 8) | $V_{IN} < V_{SS,} \mid I_{IN} \mid$ < 400µA on adjacent robust analog pin | Ó                 | 60  | 6                 | μA                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                        |                                                                           | X                 | 6   |                   | pF                 |

| +                 | Conversion time                                                                           | f <sub>ADC</sub> = 4 MHz                                                  | 0                 | 3.5 |                   | μS                 |

| <sup>t</sup> CONV |                                                                                           |                                                                           |                   | 14  |                   | 1/f <sub>ADC</sub> |

| 1                 | Analog part                                                                               | Sunk on V <sub>DDA</sub> <sup>2)</sup>                                    |                   |     | 3.6               | mA                 |

| ADC               | Digital part                                                                              | Sunk on V <sub>DD</sub>                                                   |                   |     | 0.2               | IIIA               |

#### Notes:

1. Data based on characterization results, not tested in production.

2. When  $V_{DDA}$  and  $V_{SSA}$  pins are not available on the pinout, the ADC refers to  $V_{DD}$  and  $V_{SS}$ .

# **14 DEVICE CONFIGURATION AND ORDERING INFORMATION**

Each device is available for production in user programmable versions (FLASH) as well as in factory coded versions (ROM/FASTROM).

ST72361 devices are ROM versions. ST72P361 devices are Factory Advanced Service Technique ROM (FASTROM) versions: They are factory-programmed HDFlash devices.

ST72F361 FLASH devices are shipped to customers with a default content (FFh), while ROM factory coded parts contain the code supplied by the customer. This implies that FLASH devices have to be configured by the customer using the Option Bytes while the ROM devices are factory-configured.

### **14.1 FLASH OPTION BYTES**

The option bytes allows the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with a reserved internal clock source enabled. In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see option list).

### **OPTION BYTE 0**

OPT7 = **WDGHALT** Watchdog reset on HALT This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

- 0: No Reset generation when entering Halt mode

- 1: Reset generation when entering Halt mode

OPT6 = **WDGSW** *Hardware or software watchdog* This option bit selects the watchdog type. 0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

OPT4 = **LVD** Voltage detection This option bit enables the voltage detection block (LVD).

| Selected Low Voltage Detector | VD |  |  |

|-------------------------------|----|--|--|

| LVD Off                       | 1  |  |  |

| LVD On                        | 0  |  |  |

### OPT3 = PLL OFF PLL activation

This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL is guaranteed only with an input frequency between 2 and 4 MHz.

0: PLL x2 enabled

1: PLL x2 disabled

**Caution**: The PLL can be enabled only if the "OSC RANGE" (OPT11:10) bits are configured to "MP - 2~4 MHz". Otherwise, the device functionality is not guaranteed.

| 5 STATIC OPTION BYTE 0 |                 |      |    |       |     |     |    |   | STATIC OPTION BYTE 1 |      |     |     |      |      | 0    |       |         |

|------------------------|-----------------|------|----|-------|-----|-----|----|---|----------------------|------|-----|-----|------|------|------|-------|---------|

|                        | <u> </u>        | w    | DG | irved | LVD | OFF | Pŀ | G | ш<br>ш               | AFI_ | MAP | OSC | TYPE | OSCR | ANGE | irved | TC<br>D |

| $\mathbf{O}$           | 02              | HALT | SW | Resei |     | PLL | 1  | 0 | FMP                  | 1    | 0   | 1   | 0    | 1    | 0    | Rese  | RS      |

|                        | De-<br>fault(*) | 1    | 1  | 1     | 1   | 1   | 1  | 1 | 1                    | 1    | 1   | 1   | 0    | 1    | 1    | 1     | 1       |

(\*): Option bit values programmed by ST

## DEVICE CONFIGURATION AND ORDER INFORMATION (cont'd)

#### Table 35. FLASH User Programmable Device Types

| Part Number   | Package      | Memory<br>(Kbytes) | RAM<br>(Kbytes) | Temp Range    |  |  |

|---------------|--------------|--------------------|-----------------|---------------|--|--|

| ST72F361AR6T6 |              | 32                 | 1.5             |               |  |  |

| ST72F361AR7T6 | LQFP64 10x10 | 48                 | 2               |               |  |  |

| ST72F361AR9T6 | 1            | 60                 | 2               |               |  |  |

| ST72F361J6T6  |              | 32                 | 1.5             |               |  |  |

| ST72F361J7T6  | LQFP44 10x10 | 48                 | 2               | -40 to +85°C  |  |  |

| ST72F361J9T6  |              | 60                 | 2               |               |  |  |

| ST72F361K6T6  |              | 32                 | 1.5             | 16            |  |  |

| ST72F361K7T6  | LQFP32 7x7   | 48                 | 2               | *(2)          |  |  |

| ST72F361K9T6  |              | 60                 | 2               |               |  |  |

| ST72F361AR6T3 |              | 32                 | 1.5             | 40.5          |  |  |

| ST72F361AR7T3 | LQFP64 10x10 | 48                 | 2               |               |  |  |

| ST72F361AR9T3 |              | 60                 | 2               |               |  |  |

| ST72F361J6T3  |              | 32                 | 1.5             |               |  |  |

| ST72F361J7T3  | LQFP44 10x10 | 48                 | 2               | -40 to +125°C |  |  |

| ST72F361J9T3  | 1            | 60                 | 2               |               |  |  |

| ST72F361K6T3  |              | 32                 | 1.5             |               |  |  |

| ST72F361K7T3  | LQFP32 7x7   | 48                 | 2               |               |  |  |

| ST72F361K9T3  | 1            | 60                 | 2               |               |  |  |

# 14.2 TRANSFER OF CUSTOMER CODE

Customer code is made up of the ROM/FAS-TROM contents and the list of the selected options (if any). The ROM/FASTROM contents are to be sent on diskette, or by electronic means, with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

The selected options are communicated to STMicroelectronics using the correctly completed OPTION LIST appended.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

## Figure 129. FASTROM Factory Coded Device Types