Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | LINbusSCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f361k9t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## CENTRAL PROCESSING UNIT (Cont'd)

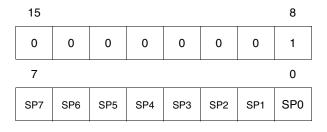

## Stack Pointer (SP)

## Read/Write

<u>لرک</u>

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 9).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

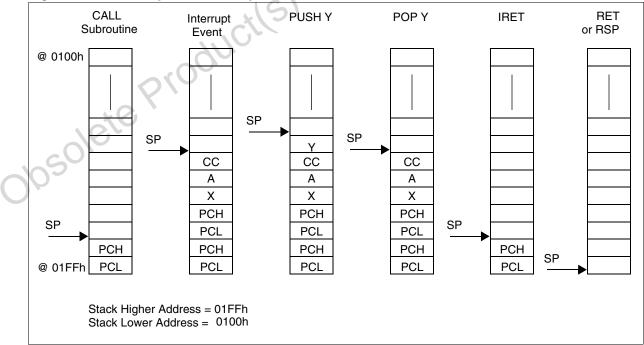

#### Figure 9. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 9.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

## 6.3 RESET SEQUENCE MANAGER (RSM)

#### 6.3.1 Introduction

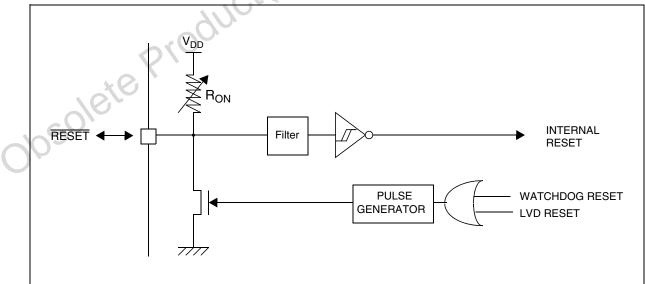

The reset sequence manager includes three RE-SET sources as shown in Figure 2:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

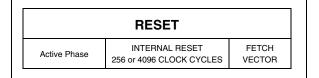

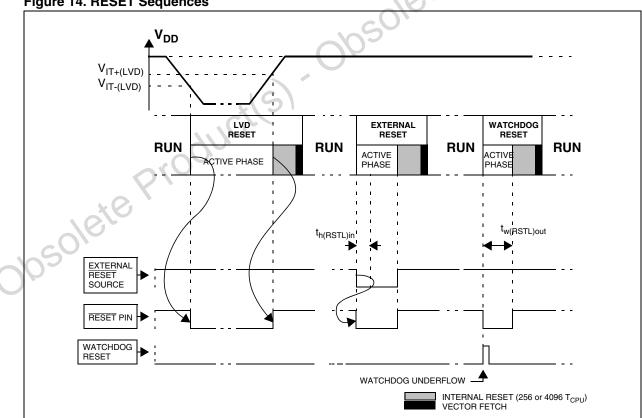

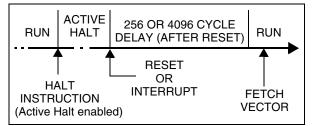

The basic RESET sequence consists of three phases as shown in Figure 1:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (selected by option byte)

- RESET vector fetch

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilize and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay should be selected by option byte to correspond to the stabilization time of the external oscillator used in the application.

The RESET vector fetch phase duration is two clock cycles.

#### Figure 12. RESET Sequence Phases

**Caution:** When the ST7 is unprogrammed or fully erased, the Flash is blank and the RESET vector is not programmed. For this reason, it is recommended to keep the RESET pin in low state until programming mode is entered, in order to avoid unwanted behavior.

## 6.3.2 Asynchronous External RESET pin

The  $\overline{\text{RESET}}$  pin is both an input and an open-drain output with integrated  $R_{ON}$  weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See Electrical Characteristic section for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 3). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

## **RESET SEQUENCE MANAGER** (Cont'd)

The **RESET** pin is an asynchronous signal which plays a major role in EMS performance. In a noisy environment, it is recommended to follow the guidelines mentioned in the electrical characteristics section.

#### 6.3.3 External Power-On RESET

If the LVD is disabled by option byte, to start up the microcontroller correctly, the user must ensure by means of an external reset circuit that the reset signal is held low until  $\ensuremath{\mathsf{V}_{\text{DD}}}$  is over the minimum level specified for the selected f<sub>OSC</sub> frequency.

A proper reset signal for a slow rising V<sub>DD</sub> supply can generally be provided by an external RC network connected to the RESET pin.

## 6.3.4 Internal Low Voltage Detector (LVD) RESET

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-On RESET

- Voltage Drop RESET

The device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low when  $V_{DD} < V_{IT+}$  (rising edge) or  $V_{DD} < V_{IT-}$  (falling edge) as shown in Figure 3.

The LVD filters spikes on  $V_{DD}$  larger than  $t_{q(VDD)}$  to avoid parasitic resets.

#### 6.3.5 Internal Watchdog RESET

The RESET sequence generated by a internal Watchdog counter overflow is shown in Figure 3.

Starting from the Watchdog counter underflow, the device RESET pin acts as an output that is pulled low during at least tw(RSTL)out.

## Figure 14. RESET Sequences

**لرک**ا

## INTERRUPTS (Cont'd)

## **Servicing Pending Interrupts**

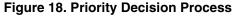

As several interrupts can be pending at the same time, the interrupt to be taken into account is determined by the following two-step process:

- the highest software priority interrupt is serviced,

- if several interrupts have the same software priority then the interrupt with the highest hardware priority is serviced first.

Figure 18 describes this decision process.

When an interrupt request is not serviced immediately, it is latched and then processed when its software priority combined with the hardware priority becomes the highest one.

**Note 1**: The hardware priority is exclusive while the software one is not. This allows the previous process to succeed with only one interrupt.

Note 2: RESET, TRAP and TLI can be considered as having the highest software priority in the decision process.

## **Different Interrupt Vector Sources**

Two interrupt source types are managed by the ST7 interrupt controller: the non-maskable type (RESET, TRAP) and the maskable type (external or from internal peripherals).

## Non-Maskable Sources

These sources are processed regardless of the state of the 11 and I0 bits of the CC register (see Figure 17). After stacking the PC, X, A and CC registers (except for RESET), the corresponding vector is loaded in the PC register and the I1 and I0 bits of the CC are set to disable interrupts (level 3). These sources allow the processor to exit HALT mode.

TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP instruction is executed. It will be serviced according to the flowchart in Figure 17 as a TLI.

Caution: TRAP can be interrupted by a TLI.

## RESET

The RESET source has the highest priority in the ST7. This means that the first current routine has the highest software priority (level 3) and the highest hardware priority.

See the RESET chapter for more details.

#### **Maskable Sources**

Maskable interrupt vector sources can be serviced if the corresponding interrupt is enabled and if its own interrupt software priority (in ISPRx registers) is higher than the one currently being serviced (I1 and I0 in CC register). If any of these two conditions is false, the interrupt is latched and thus remains pending.

TLI (Top Level Hardware Interrupt)

This hardware interrupt occurs when a specific edge is detected on the dedicated TLI pin.

**Caution**: A TRAP instruction must not be used in a TLI service routine.

External Interrupts

External interrupts allow the processor to exit from HALT low power mode.

External interrupt sensitivity is software selectable through the External Interrupt Control register (EICR).

External interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins of a group connected to the same interrupt line are selected simultaneously, these will be logically ORed.

Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to exit from HALT mode except those mentioned in the "Interrupt Mapping" table.

A peripheral interrupt occurs when a specific flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register.

The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (that is, waiting for being serviced) will therefore be lost if the clear sequence is executed.

57

## INTERRUPTS (Cont'd)

## Table 9. Interrupt Mapping

| N° | Source<br>Block | Description                                                     | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT <sup>1)</sup> | Address<br>Vector |

|----|-----------------|-----------------------------------------------------------------|-------------------|-------------------|------------------------------------|-------------------|

|    | RESET           | Reset                                                           | N/A               |                   | yes                                | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                                              | IN/A              |                   | no                                 | FFFCh-FFFDh       |

| 0  | TLI             | External top level interrupt                                    | EICR              | Highest           | yes                                | FFFAh-FFFBh       |

| 1  | MCC/RTC         | Main clock controller time base interrupt                       | MCCSR             | Priority          | yes                                | FFF8h-FFF9h       |

| 2  | ei0/AWUFH       | External interrupt ei0/ Auto wake-up from Halt                  | EICR/<br>AWUCSR   |                   |                                    | FFF6h-FFF7h       |

| 3  | ei1/AVD         | External interrupt ei1/Auxiliary Voltage Detector               | EICR/<br>SICSR    |                   | yes <sup>2)</sup>                  | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt ei2                                          | EICR              |                   | 0.                                 | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt ei3                                          | EICR              | <b>bk</b>         |                                    | FFF0h-FFF1h       |

| 6  |                 | not used                                                        |                   |                   |                                    | FFEEh-FFEFh       |

| 7  |                 | not used                                                        | ×0                |                   |                                    | FFECh-FFEDh       |

| 8  | SPI             | SPI peripheral interrupts                                       | SPICSR            |                   | yes                                | FFEAh-FFEBh       |

| 9  | TIMER8          | 8-bit TIMER peripheral interrupts                               | T8_TCR1           |                   | no                                 | FFE8h-FFE9h       |

| 10 | TIMER16         | 16-bit TIMER peripheral interrupts                              | TCR1              |                   | no                                 | FFE6h-FFE7h       |

| 11 | LINSCI2         | LINSCI2 Peripheral interrupts                                   | SCI2CR1           |                   | no                                 | FFE4h-FFE5h       |

| 12 | LINSCI1         | I1 LINSCI1 Peripheral interrupts (LIN Master/<br>Slave) SCI1CR1 |                   | ↓<br>Lowest       | no <sup>3)</sup>                   | FFE2h-FFE3h       |

| 13 | PWM ART         | 8-bit PWM ART interrupts                                        | PWMCR             | Priority          | yes                                | FFE0h-FFE1h       |

Notes:

1. Valid for HALT and ACTIVE HALT modes except for the MCC/RTC interrupt source which exits from ACTIVE HALT mode only.

2. Except AVD interrupt

3. It is possible to exit from Halt using the external interrupt which is mapped on the RDI pin.

## POWER SAVING MODES (Cont'd)

#### Halt Mode Recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

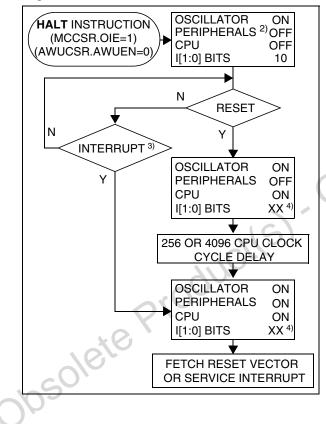

## 8.5 ACTIVE HALT MODE

ACTIVE HALT mode is the lowest power consumption mode of the MCU with a real time clock available. It is entered by executing the 'HALT' instruction when MCC/RTC interrupt enable flag (OIE bit in MCCSR register) is set and when the AWUEN bit in the AWUCSR register is cleared (See "Register Description" on page 44.)

| MCCSR<br>OIE bit | Power Saving Mode entered when HALT instruction is executed |  |  |

|------------------|-------------------------------------------------------------|--|--|

| 0                | HALT mode                                                   |  |  |

| 1                | ACTIVE HALT mode                                            |  |  |

|                  |                                                             |  |  |

The MCU can exit ACTIVE HALT mode on reception of the RTC interrupt and some specific interrupts (see Table 9, "Interrupt Mapping," on page 33) or a RESET. When exiting ACTIVE HALT mode by means of a RESET a 4096 or 256 CPU cycle delay occurs (depending on the option byte). After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 28).

When entering ACTIVE HALT mode, the I[1:0] bits in the CC register are are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In ACTIVE HALT mode, only the main oscillator and its associated counter (MCC/RTC) are running to keep a wake-up time base. All other peripherals are not clocked except those which get their clock supply from another clock generator (such as external or auxiliary oscillator).

The safeguard against staying locked in ACTIVE HALT mode is provided by the oscillator interrupt.

**Note:** As soon as active halt is enabled, executing a HALT instruction while the Watchdog is active does not generate a RESET.

This means that the device cannot spend more than a defined delay in this power saving mode.

**47/**

## POWER SAVING MODES (Cont'd)

## Figure 27. ACTIVE HALT Timing Overview

#### Figure 28. ACTIVE HALT Mode Flow-chart

#### Notes:

psolete

- 1. This delay occurs only if the MCU exits ACTIVE HALT mode by means of a RESET.

- 2. Peripheral clocked with an external clock source can still be active.

- 3. Only the RTC interrupt and some specific interrupts can exit the MCU from ACTIVE HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 33 for more details.

- 4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits in the CC register are set to the current software priority level of the interrupt routine and restored when the CC register is popped.

41/225

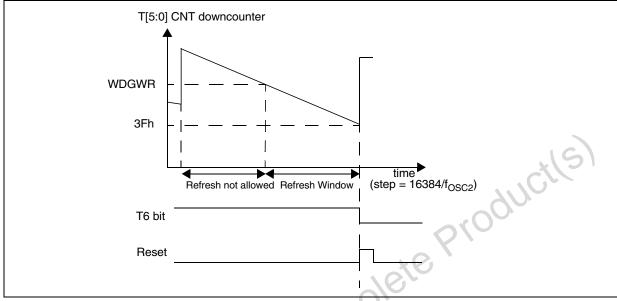

# WINDOW WATCHDOG (Cont'd)

# Figure 37. Window Watchdog Timing Diagram

## 10.1.6 Low Power Modes

| Mode           | Description                                                    |                                  |                                                                                                                                                                                                                                                                                                                                                           |

|----------------|----------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wode           | Description                                                    |                                  |                                                                                                                                                                                                                                                                                                                                                           |

| SLOW           | No effect on                                                   | Watchdog: The                    | e downcounter continues to decrement at normal speed.                                                                                                                                                                                                                                                                                                     |

| WAIT           | No effect on Watchdog: The downcounter continues to decrement. |                                  |                                                                                                                                                                                                                                                                                                                                                           |

|                | OIE bit in<br>MCCSR<br>register                                | WDGHALT bit<br>in Option<br>Byte |                                                                                                                                                                                                                                                                                                                                                           |

| HALT           | P                                                              | 000                              | No Watchdog reset is generated. The MCU enters Halt mode. The Watch-<br>dog counter is decremented once and then stops counting and is no longer<br>able to generate a watchdog reset until the MCU receives an external inter-<br>rupt or a reset.                                                                                                       |

| 50             | eto                                                            | 0                                | If an interrupt is received (refer to interrupt table mapping to see interrupts which can occur in halt mode), the Watchdog restarts counting after 256 or 4096 CPU clocks. If a reset is generated, the Watchdog is disabled (reset state) unless Hardware Watchdog is selected by option byte. For application recommendations see Section 0.1.8 below. |

|                | 0                                                              | 1                                | A reset is generated instead of entering halt mode.                                                                                                                                                                                                                                                                                                       |

| ACTIVE<br>HALT | 1                                                              | x                                | No reset is generated. The MCU enters Active Halt mode. The Watchdog counter is not decremented. It stop counting. When the MCU receives an oscillator interrupt or external interrupt, the Watchdog restarts counting immediately. When the MCU receives a reset the Watchdog restarts counting after 256 or 4096 CPU clocks.                            |

## 10.1.7 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte, the watchdog is always active and the WDGA bit in the WDGCR is not used. Refer to the Option Byte description.

# 10.1.8 Using Halt Mode with the WDG (WDGHALT option)

The following recommendation applies if Halt mode is used when the watchdog is enabled.

Before executing the HALT instruction, refresh the WDG counter, to avoid an unexpected WDG reset immediately after waking up the microcontroller.

## **ON-CHIP PERIPHERALS** (Cont'd)

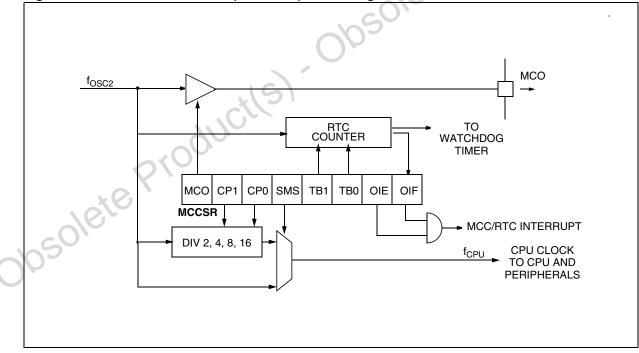

## **10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK MCC/RTC**

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real time clock timer with interrupt capability

Each function can be used independently and simultaneously.

## 10.2.1 Programmable CPU Clock Prescaler

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages SLOW power saving mode (See Section 8.2 "SLOW MODE" for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

## 10.2.2 Clock-out Capability

The clock-out capability is an alternate function of an I/O port pin that outputs a  $f_{OSC2}$  clock to drive external devices. It is controlled by the MCO bit in the MCCSR register.

#### 10.2.3 Real Time Clock Timer (RTC)

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by 4 bits of the MCCSR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE HALT mode when the HALT instruction is executed. See Section 8.5 "ACTIVE HALT MODE" for more details.

**/رک**ا

#### Figure 39. Main Clock Controller (MCC/RTC) Block Diagram

## **16-BIT TIMER** (Cont'd)

#### **10.4.7 Register Description**

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

## **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = **ICIE** *Input Capture Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

#### Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.* 0: Interrupt is inhibited.

Jbsolete P

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

- This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

Bit 3 = FOLV1 Forced Output Compare 1.

- This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

## Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse mode and Pulse Width Modulation mode.

## Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture. 0: A falling edge triggers the capture. 1: A rising edge triggers the capture.

## Bit 0 = OLVL1 Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

## **ON-CHIP PERIPHERALS** (cont'd)

## **10.6 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 10.6.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 10.6.2 Main Features

- Full duplex synchronous transfers (on three lines)

- Simplex synchronous transfers (on two lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

Note: In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### **10.6.3 General Description**

Figure 70 on page 110 shows the serial peripheral interface (SPI) block diagram. There are three registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through four pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

## SERIAL PERIPHERAL INTERFACE (cont'd)

## 10.6.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the device is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the Device. |

# 10.6.6.1 Using the SPI to wake up the device from Halt mode

In slave configuration, the SPI is able to wake up the device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

Note: When waking up from HALT mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from HALT mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the device from HALT mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the device enters HALT mode. So, if Slave selection is configured as external (see Section 10.6.3.2), make sure the master drives a low level on the SS pin when the slave enters HALT mode.

## 10.6.7 Interrupts

|                              |               |                          | X \                  |                      |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

| SPI End of<br>Transfer Event | SPIF          | 0                        |                      | Yes                  |

| Master Mode<br>Fault Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          |                      |                      |

|                              | -             | •                        |                      |                      |

**Note:** The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

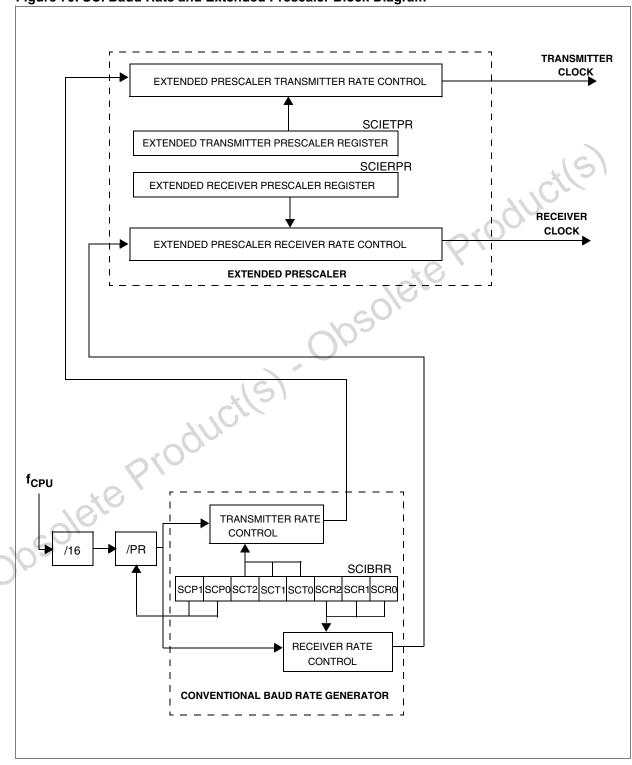

# LINSCI<sup>™</sup> SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd) Figure 79. SCI Baud Rate and Extended Prescaler Block Diagram

57

127/225

## LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

## 10.8.4.7 Parity control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in Table 24.

## Table 25. Frame Formats

| M bit | PCE bit | SCI frame                  |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | 1       | SB   7-bit data   PB   STB |

| 1     | 0       | SB   9-bit data   STB      |

| I     | 1       | SB   8-bit data PB   STB   |

## Legend:

SB: Start Bit

STB: Stop Bit

**PB:** Parity Bit

Note: In case of wake up by an address mark, the MSB bit of the data is taken into account and not the parity bit

**Even parity:** The parity bit is calculated to obtain an even number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 0 if even parity is selected (PS bit = 0).

**Odd parity:** The parity bit is calculated to obtain an odd number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 1 if odd parity is selected (PS bit = 1).

<u>**Transmission mode:**</u> If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**<u>Reception mode:</u>** If the PCE bit is set then the interface checks if the received data byte has an

even number of "1s" if even parity is selected (PS = 0) or an odd number of "1s" if odd parity is selected (PS = 1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

## 10.8.5 Low Power Modes

| Mode | Description                                                                        |

|------|------------------------------------------------------------------------------------|

|      | No effect on SCI.                                                                  |

| WAIT | SCI interrupts cause the device to exit from Wait mode.                            |

|      | SCI registers are frozen.                                                          |

| HALT | In Halt mode, the SCI stops transmitting/re-<br>ceiving until Halt mode is exited. |

## 10.8.6 Interrupts

| Interrupt Event                 | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|---------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register<br>Empty | TDRE          | TIE                      |                      |                      |

| Transmission Com-<br>plete      | тс            | TCIE                     |                      |                      |

| Received Data Ready to be Read  | RDRF          | RIE                      | Yes                  | No                   |

| Overrun Error Detect-<br>ed     | OR            | 111                      |                      |                      |

| Idle Line Detected              | IDLE          | ILIE                     |                      |                      |

| Parity Error                    | PE            | PIE                      |                      |                      |

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### 10.9.3.2 A/D Conversion

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the "I/O ports" chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

Select the CS[3:0] bits to assign the analog channel to convert.

#### ADC Conversion mode

In the ADCCSR register:

Set the ADON bit to enable the A/D converter and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

– The result is in the ADCDR registers.

A read to the ADCDRH resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll EOC bit

- 2. Read the ADCDRL register

- 3. Read the ADCDRH register. This clears EOC automatically.

To read only 8 bits, perform the following steps:

1. Poll EOC bit

**لرك**ا

2. Read the ADCDRH register. This clears EOC automatically.

#### 10.9.3.3 Changing the conversion channel

The application can change channels during conversion. When software modifies the CH[3:0] bits

in the ADCCSR register, the current conversion is stopped, the EOC bit is cleared, and the A/D converter starts converting the newly selected channel.

## 10.9.3.4 ADCDR consistency

If an End Of Conversion event occurs after software has read the ADCDRLSB but before it has read the ADCDRMSB, there would be a risk that the two values read would belong to different samples.

To guarantee consistency:

- The ADCDRL and the ADCDRH registers are locked when the ADCCRL is read

- The ADCDRL and the ADCDRH registers are unlocked when the ADCDRH register is read or when ADON is reset.

This is important, as the ADCDR register will not be updated until the ADCDRH register is read.

## 10.9.4 Low Power Modes

**Note:** The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed and between single shot conversions.

| Mode | Description                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on A/D Converter                                                                                                                                                                |

|      | A/D Converter disabled.                                                                                                                                                                   |

| HALT | After wakeup from Halt mode, the A/D<br>Converter requires a stabilization time<br>t <sub>STAB</sub> (see Electrical Characteristics)<br>before accurate conversions can be<br>performed. |

#### 10.9.5 Interrupts

None.

## **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

## 12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                    | Ratings                                             | Maximum value                    | Unit    |

|-------------------------------------------|-----------------------------------------------------|----------------------------------|---------|

| V <sub>DD</sub> - V <sub>SS</sub>         | Supply voltage                                      | 6.5                              |         |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming Voltage                                 | 13                               | V       |

| V <sub>IN</sub>                           | Input voltage on any pin <sup>1)2)</sup>            | $V_{SS}$ - 0.3 to $V_{DD}$ + 0.3 |         |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins     | 50                               | mV      |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins   | 50                               | niv     |

| V <sub>ESD(HBM)</sub>                     | Electro-static discharge voltage (Human Body Model) | see Section 12.8.3 on p          | 200 102 |

| V <sub>ESD(MM)</sub>                      | Electro-static discharge voltage (Machine Model)    | see Section 12.8.3 on p          | age 192 |

## **12.2.2 Current Characteristics**

| Symbol                          | Ratings                                                                | Maximum value | Unit |

|---------------------------------|------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup>  | 150           |      |

| I <sub>VSS</sub>                | Total current out of V <sub>SS</sub> ground lines (sink) <sup>3)</sup> |               |      |

|                                 | Output current sunk by any standard I/O and control pin                | 25            |      |

| I <sub>IO</sub>                 | Output current sunk by any high sink I/O pin                           | 50            |      |

|                                 | Output current source by any I/Os and control pin                      | - 25          |      |

|                                 | Injected current on V <sub>PP</sub> pin                                |               | mA   |

|                                 | Injected current on RESET pin                                          | ± 5           |      |

| I <sub>INJ(PIN)</sub> 2)4)      | Injected current on OSC1 and OSC2 pins                                 | +5            |      |

|                                 | Injected current on PB3 (on Flash devices)                             |               |      |

|                                 | Injected current on any other pin <sup>5)</sup>                        | ± 5           |      |

| $\Sigma I_{\rm INJ(PIN)}^{(2)}$ | Total injected current (sum of all I/O and control pins) <sup>5)</sup> | ± 25          |      |

## **12.2.3 Thermal Characteristics**

| Γ | Symbol           | Ratings                                              | Value               | Unit |

|---|------------------|------------------------------------------------------|---------------------|------|

|   | T <sub>STG</sub> | Storage temperature range                            | -65 to +150         | °C   |

|   | Тј               | Maximum junction temperature (see Section 13.2 "THEF | RMAL CHARACTERISTIC | CS") |

#### Notes:

1. Directly connecting the RESET and I/O pins to  $V_{DD}$  or  $V_{SS}$  could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical:  $4.7k\Omega$  for RESET,  $10k\Omega$  for I/Os). Unused I/O pins must be tied in the same way to  $V_{DD}$  or  $V_{SS}$  according to their reset configuration. 2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

3. All power (V<sub>DD</sub>) and ground (V<sub>SS</sub>) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "10-BIT ADC CHARACTERISTICS" on page 204.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

<u>ل</u>رک

## **12.7 MEMORY CHARACTERISTICS**

## 12.7.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Мах | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

#### 12.7.2 FLASH Memory

## DUAL VOLTAGE HDFLASH MEMORY

| Symbol                                  | Parameter                                   | Conditions                 | Min <sup>2)</sup> | Тур              | Max <sup>2)</sup> | Unit   |

|-----------------------------------------|---------------------------------------------|----------------------------|-------------------|------------------|-------------------|--------|

| £                                       | Operating frequency                         | Read mode                  | 0                 |                  | 8                 | MHz    |

| f <sub>CPU</sub>                        |                                             | Write / Erase mode         | 1                 |                  | 8                 |        |

| V <sub>PP</sub>                         | Programming voltage <sup>3)</sup>           | $4.5V \le V_{DD} \le 5.5V$ | 11.4              |                  | 12.6              | V      |

| I <sub>PP</sub>                         | Read ( $V_{PP} = 12V$ )                     |                            | 200               | μA               |                   |        |

|                                         | V <sub>PP</sub> current <sup>4)5)</sup>     | Write / Erase              |                   |                  | 30                | mA     |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time |                            |                   | 10 <sup>4)</sup> | 5                 | μs     |

| t <sub>RET</sub>                        | Data retention                              | $T_A = 85^{\circ}C$        | 40                |                  |                   |        |

|                                         |                                             | T <sub>A</sub> = 105°C     | 15                |                  |                   | years  |

|                                         |                                             | T <sub>A</sub> = 125°C     | 7                 |                  |                   |        |

| N <sub>RW</sub>                         | Write erase cycles                          | T <sub>A</sub> = 25°C      | 100               |                  |                   | cycles |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing temperature range    |                            | -40               | 25               | 85                | °C     |

#### Notes:

1. Minimum V<sub>DD</sub> supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Not tested in production.

2. Data based on characterization results, not tested in production.

3. V<sub>PP</sub> must be applied only during the programming or erasing operation and not permanently for reliability reasons.

4. Data based on simulation results, not tested in production.

5. In Write / erase mode the I<sub>DD</sub> supply current consumption is the same as in Run mode (see Section 12.2.2)

57

## FLASH OPTION BYTES (Cont'd)

OPT2:1 = **PKG[1:0]** Package selection These option bits select the device package.

| Selected Package | PKG |   |

|------------------|-----|---|

|                  | 1   | 0 |

| LQFP 64          | 1   | x |

| LQFP 44          | 0   | 1 |

| LQFP 32          | 0   | 0 |

**Note:** Pads that are not bonded to external pins are in input pull-up configuration when the package selection option bits have been properly programmed. The configuration of these pads must be kept in reset state to avoid added current consumption.

OPT0 = **FMP\_R** Flash memory read-out protection

Read-out protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first, and the device can be reprogrammed. Refer to Section 4.3.1 and the *ST7 Flash Programming Reference Manual* for more details.

0: Read-out protection enabled

1: Read-out protection disabled

## **OPTION BYTE 1**

## OPT7:6 = AFI MAP[1:0] AFI Mapping

These option bits allow the mapping of some of the Alternate Functions to be changed.

| AFI Mapping 1                                                                                                                                   | AFI_MAP(1) |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| T16_OCMP1 on PD3<br>T16_OCMP2 on PD5<br>T16_ICAP1 on PD4<br>LINSCI2_SCK not available<br>LINSCI2_TDO not available<br>LINSCI2_RDI not available | 0          |

| T16_OCMP1 on PB6<br>T16_OCMP2 on PB7<br>T16_ICAP1 on PC0<br>LINSCI2_SCK on PD3<br>LINSCI2_TDO on PD5<br>LINSCI2_RDI on PD4                      | 1          |

| AFI Mapping 0              | AFI_MAP(0) |

|----------------------------|------------|

| T16_ICAP2 is mapped on PD1 | 0          |

| T16_ICAP2 is mapped on PC1 | 1          |

OPT5:4 = **OSCTYPE[1:0]** Oscillator Type These option bits select the ST7 main clock source type.

| Clock Source                                           | OSCTYPE |   |  |

|--------------------------------------------------------|---------|---|--|

| Clock Source                                           | 1       | 0 |  |

| Resonator Oscillator                                   | 0       | 0 |  |

| Reserved                                               | 0       | 1 |  |

| Reserved internal clock source (used only in ICC mode) | 1       | 0 |  |

| External Source                                        | 1       | 1 |  |

OPT3:2 = **OSCRANGE[1:0]** Oscillator range If the resonator oscillator type is selected, these option bits select the resonator oscillator. This selection corresponds to the frequency range of the resonator used. If external source is selected with the OSCTYPE option, then the OSCRANGE option must be selected with the corresponding range.

| Typ. Freq. Range |          | OSCRANGE |   |  |

|------------------|----------|----------|---|--|

|                  |          | 1        | 0 |  |

| LP               | 1~2 MHz  | 0        | 0 |  |

| MP               | 2~4 MHz  | 0        | 1 |  |

| MS               | 4~8 MHz  | 1        | 0 |  |

| HS               | 8~16 MHz | 1        | 1 |  |

## OPT1 = Reserved

OPT0 = **RSTC** *RESET* clock cycle selection This option bit selects the number of CPU cycles inserted during the RESET phase and when exiting HALT mode. For resonator oscillators, it is advised to select 4096 due to the long crystal stabilization time.

0: Reset phase with 4096 CPU cycles

1: Reset phase with 256 CPU cycles

## IMPORTANT NOTES (Cont'd)

software sequence is given for both cases (global interrupt disabled/enabled).

**Case 1:** Writing to PxOR or PxDDR with Global Interrupts Enabled:

LD A,#01 LD sema.A ; set the semaphore to '1' LD A, PFDR AND A,#02 LD X,A ; store the level before writing to PxOR/PxDDR LD A,#\$90 LD PFDDR,A ; Write to PFDDR LD A,#\$ff LD PFOR,A : Write to PFOR LD A, PFDR AND A,#02 LD Y,A ; store the level after writing to PxOR/PxDDR LD A,X ; check for falling edge cp A,#02 jrne OUT TNZ Y jrne OUT ; check the semaphore status if LD A,sema edge is detected CP A,#01 jrne OUT call call routine; call the interrupt routine OUT:LD A,#00 LD sema,A .call\_routine ; entry to call\_routine PUSH A PUSH X PUSH CC .ext1\_rt ; entry to interrupt routine LD A,#00 LD sema,A

IRET Case 2: Writing to PxOR or PxDDR with Global Interrupts Disabled: SIM ; set the interrupt mask LD A,PFDR

AND A,#\$02

LD X,A ; store the level before writing to PxOR/PxDDR LD A,#\$90 LD PFDDR,A; Write into PFDDR LD A,#\$ff LD PFOR,A ; Write to PFOR LD A, PFDR AND A,#\$02 LD Y,A ; store the level after writing to PxOR/ PxDDR ; check for falling edge LD A,X cp A.#\$02 rodi jrne OUT TNZ Y irne OUT LD A,#\$01 LD sema, A ; set the semaphore to '1' if edge is detected RIM ; reset the interrupt mask LD A,sema ; check the semaphore status CP A,#\$01 irne OUT call call\_routine; call the interrupt routine RIM OUT: RIM JP while\_loop .call\_routine ; entry to call\_routine PUSH A PUSH X PUSH CC .ext1 rt ; entry to interrupt routine LD A,#\$00 LD sema,A IRET **16.1.4 Unexpected Reset Fetch** If an interrupt request occurs while a "POP CC" instruction is executed, the interrupt controller does not recognise the source of the interrupt and, by

Workaround

CPU.

To solve this issue, a "POP CC" instruction must always be preceded by a "SIM" instruction.

default, passes the RESET vector address to the

# **17 REVISION HISTORY**

| Date        | Revision | Main changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Oct-2008 | 7        | Updated static latchup Section 12.8.3.2 on page 192<br>Updated Flash data retention characteristics in Section 12.7.2.<br>Added Section 16.1.6 on page 221                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 04-Oct-2005 | 1        | Initial revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 26-Sep-2006 | 2        | Changed note in "Device Summary" on page 1<br>Changed Section 10.6.3.3 on page 112<br>Changed "FASTROM Factory Coded Device Types" on page 215<br>Deleted Section 15.1.5 "Clearing active interrupts outside interrupt routine" (text already ex-<br>ists in Section 16.1.2 on page 218)<br>Added Section 16.1.5 on page 220<br>Replaced TQFP with LQFP packages throughout document<br>Changed Section 12.12.1 on page 202<br>Changed Section 9.2.1 on page 45<br>Changed title of Section 9.6 on page 49 from "I/O Port Implementation" to "I/O Port Register<br>Configurations"<br>Corrected name of bit 5 in SPICSR register in Table 22 on page 119<br>Changed Section 12.5.4 on page 187<br>Added links to Table 33 and Table 34 in Section 12.8.3 on page 192<br>Removed EMC protection circuitry in Figure 113 on page 199 (device works correctly with-<br>out these components)<br>Changed AFI mapping for "OPTION BYTE 1" on page 211<br>Changed title of Figure 124 on page 208<br>Changed title of Figure 125 on page 209<br>Changed Figure 127 on page 213<br>Added Figure 36 on page 213<br>Replaced "Flash Memory" with "Memory" as column heading in Figure 35 on page 212 and<br>Figure 129 on page 215<br>Changed Section 15 on page 217<br>Added Table 37 on page 217<br>Added Table 37 on page 217<br>Removed automotive part numbers, see separate ST72361-auto datasheet<br>Added EMI characteristics for LQEP44 in Section 12.8 |

| 19-Jun-2007 | 3        | Updated ADC accuracy characteristics in Section 12.13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 02-Oct-2008 | 4        | Updated static latchup Section 12.8.3.2 on page 192<br>Updated Flash data retention characteristics in Section 12.7.2.<br>Added Section 16.1.6 on page 221.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**57**