Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                             |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 16x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f800-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. System Overview                                     |    |

|--------------------------------------------------------|----|

| 2. Ordering Information                                | 25 |

| 3. Pin Definitions                                     |    |

| 4. QFN-20 Package Specifications                       | 33 |

| 5. QSOP-24 Package Specifications                      | 35 |

| 6. SOIC-16 Package Specifications                      | 37 |

| 7. Electrical Characteristics                          |    |

| 7.1. Absolute Maximum Specifications                   | 39 |

| 7.2. Electrical Characteristics                        |    |

| 8. 10-Bit ADC (ADC0)                                   | 46 |

| 8.1. Output Code Formatting                            | 47 |

| 8.2. 8-Bit Mode                                        |    |

| 8.3. Modes of Operation                                | 47 |

| 8.3.1. Starting a Conversion                           | 47 |

| 8.3.2. Tracking Modes                                  | 48 |

| 8.3.3. Settling Time Requirements                      | 49 |

| 8.4. Programmable Window Detector                      | 53 |

| 8.4.1. Window Detector Example                         |    |

| 8.5. ADC0 Analog Multiplexer                           |    |

| 9. Temperature Sensor                                  |    |

| 9.1. Calibration                                       | 58 |

| 10. Voltage and Ground Reference Options               | 60 |

| 10.1. External Voltage References                      |    |

| 10.2. Internal Voltage Reference Options               |    |

| 10.3. Analog Ground Reference                          |    |

| 10.4. Temperature Sensor Enable                        |    |

| 11. Voltage Regulator (REG0)                           | 63 |

| 12. Comparator0                                        | 65 |

| 12.1. Comparator Multiplexer                           | 69 |

| 13. Capacitive Sense (CS0)                             | 71 |

| 13.1. Configuring Port Pins as Capacitive Sense Inputs | 72 |

| 13.2. Capacitive Sense Start-Of-Conversion Sources     | 72 |

| 13.3. Automatic Scanning                               | 72 |

| 13.4. CS0 Comparator                                   | 73 |

| 13.5. CS0 Conversion Accumulator                       | 74 |

| 13.6. Capacitive Sense Multiplexer                     | 80 |

| 14. CIP-51 Microcontroller                             |    |

| 14.1. Instruction Set                                  | 83 |

| 14.1.1. Instruction and CPU Timing                     | 83 |

| 14.2. CIP-51 Register Descriptions                     |    |

| 15. Memory Organization                                | 92 |

| 15.1. Program Memory                                   | 93 |

| 15.1.1. MOVX Instruction and Program Memory            | 93 |

|     | Figure 13.1. CS0 Block Diagram71                                                      |

|-----|---------------------------------------------------------------------------------------|

|     | Figure 13.2. Auto-Scan Example73                                                      |

|     | Figure 13.3. CS0 Multiplexer Block Diagram 80                                         |

| 14. | CIP-51 Microcontroller                                                                |

|     | Figure 14.1. CIP-51 Block Diagram 82                                                  |

| 15. | Memory Organization                                                                   |

| I   | Figure 15.1. C8051F80x-83x Memory Map 92                                              |

|     | Figure 15.2. Flash Program Memory Map                                                 |

|     | In-System Device Identification                                                       |

|     | Special Function Registers                                                            |

|     | Interrupts                                                                            |

|     | Flash Memory                                                                          |

|     | Power Management Modes                                                                |

|     | Reset Sources                                                                         |

|     | Figure 21.1. Reset Sources 123                                                        |

|     | Figure 21.2. Power-On and VDD Monitor Reset Timing 124                                |

|     | Oscillators and Clock Selection                                                       |

|     | Figure 22.1. Oscillator Options 129                                                   |

|     | Figure 22.2. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram 136     |

|     | Port Input/Output                                                                     |

|     | Figure 23.1. Port I/O Functional Block Diagram                                        |

|     | Figure 23.2. Port I/O Cell Block Diagram                                              |

|     | Figure 23.3. Port I/O Overdrive Current                                               |

|     | Figure 23.4. Priority Crossbar Decoder Potential Pin Assignments                      |

|     | Figure 23.5. Priority Crossbar Decoder Example 1—No Skipped Pins                      |

|     | Figure 23.6. Priority Crossbar Decoder Example 2—Skipping Pins                        |

|     | Cyclic Redundancy Check Unit (CRC0)                                                   |

|     | Figure 24.1. CRC0 Block Diagram                                                       |

|     | Enhanced Serial Peripheral Interface (SPI0)                                           |

|     | Figure 25.1. SPI Block Diagram                                                        |

|     |                                                                                       |

|     | Figure 25.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram 169 |

| I   | Figure 25.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram 170   |

| I   | Figure 25.5. Master Mode Data/Clock Timing 172                                        |

| I   | Figure 25.6. Slave Mode Data/Clock Timing (CKPHA = 0) 172                             |

| I   | Figure 25.7. Slave Mode Data/Clock Timing (CKPHA = 1) 173                             |

| I   | Figure 25.8. SPI Master Timing (CKPHA = 0) 177                                        |

|     | Figure 25.9. SPI Master Timing (CKPHA = 1) 177                                        |

| I   | Figure 25.10. SPI Slave Timing (CKPHA = 0)                                            |

| I   | Figure 25.11. SPI Slave Timing (CKPHA = 1) 178                                        |

|     | SMBus                                                                                 |

|     | Figure 26.1. SMBus Block Diagram                                                      |

|     | Figure 26.2. Typical SMBus Configuration                                              |

| SFR Definition 28.8. TMR2CN: Timer 2 Control                     | 222 |

|------------------------------------------------------------------|-----|

| SFR Definition 28.9. TMR2RLL: Timer 2 Reload Register Low Byte   | 223 |

| SFR Definition 28.10. TMR2RLH: Timer 2 Reload Register High Byte | 223 |

| SFR Definition 28.11. TMR2L: Timer 2 Low Byte                    | 224 |

| SFR Definition 28.12. TMR2H Timer 2 High Byte                    | 224 |

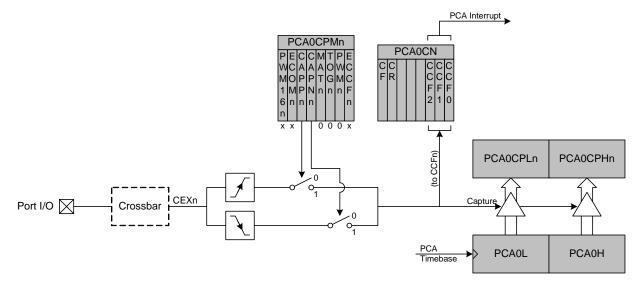

| SFR Definition 29.1. PCA0CN: PCA0 Control                        | 238 |

| SFR Definition 29.2. PCA0MD: PCA0 Mode                           | 239 |

| SFR Definition 29.3. PCA0PWM: PCA0 PWM Configuration             | 240 |

| SFR Definition 29.4. PCA0CPMn: PCA0 Capture/Compare Mode         | 241 |

| SFR Definition 29.5. PCA0L: PCA0 Counter/Timer Low Byte          | 242 |

| SFR Definition 29.6. PCA0H: PCA0 Counter/Timer High Byte         | 242 |

| SFR Definition 29.7. PCA0CPLn: PCA0 Capture Module Low Byte      | 243 |

| SFR Definition 29.8. PCA0CPHn: PCA0 Capture Module High Byte     | 243 |

| C2 Register Definition 30.1. C2ADD: C2 Address                   | 244 |

| C2 Register Definition 30.3. REVID: C2 Revision ID               | 245 |

| C2 Register Definition 30.2. DEVICEID: C2 Device ID              | 245 |

| C2 Register Definition 30.4. FPCTL: C2 Flash Programming Control | 246 |

| C2 Register Definition 30.5. FPDAT: C2 Flash Programming Data    | 246 |

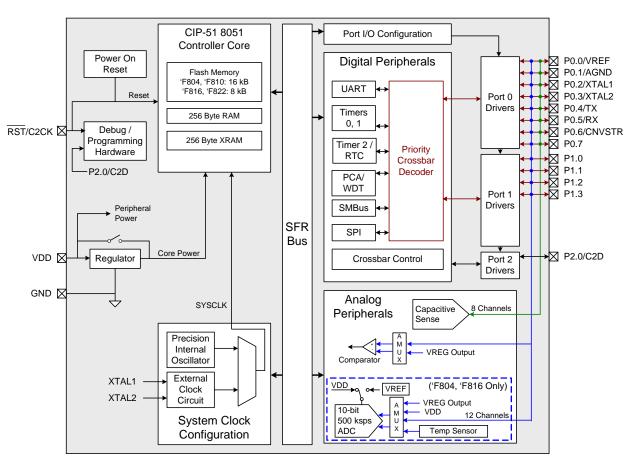

# 1. System Overview

C8051F80x-83x devices are fully integrated, mixed-signal, system-on-a-chip capacitive sensing MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Capacitive sense interface with 16 input channels

- 10-bit 500 ksps single-ended ADC with 16-channel analog multiplexer and integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

- 16 kb of on-chip Flash memory

- 512 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Three general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules

- On-chip internal voltage reference

- On-chip Watchdog timer

- On-chip power-on reset and supply monitor

- On-chip voltage comparator

- 17 general purpose I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F80x-83x devices are truly stand-alone, system-on-a-chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The C8051F80x-83x processors include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8-3.6 V operation over the industrial temperature range (-45 to +85 °C). An internal LDO regulator is used to supply the processor core voltage at 1.8 V. The Port I/O and RST pins are tolerant of input signals up to 5 V. See Table 2.1 for ordering information. Block diagrams of the devices in the C8051F80x-83x family are shown in Figure 1.1 through Figure 1.9.

Figure 1.5. C8051F804, C8051F810, C8051F816, C8051F822 Block Diagram

# SFR Definition 8.4. ADC0CN: ADC0 Control

| Bit   | 7     | 6     | 5      | 4       | 3       | 2          | 1 | 0 |

|-------|-------|-------|--------|---------|---------|------------|---|---|

| Name  | AD0EN | AD0TM | AD0INT | AD0BUSY | AD0WINT | AD0CM[2:0] |   |   |

| Туре  | R/W   | R/W   | R/W    | R/W     | R/W     | R/W        |   |   |

| Reset | 0     | 0     | 0      | 0       | 0       | 0          | 0 | 0 |

### SFR Address = 0xE8; Bit-Addressable

| Bit | Name       |                                                                                                                                                                                                                                                                                                                                                                                                                                               | Function                                                                           |                                                                            |  |  |  |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| 7   | AD0EN      | ADC0 Enable Bit.                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                                            |  |  |  |  |

|     |            | 0: ADC0 Disabled. ADC0 is in                                                                                                                                                                                                                                                                                                                                                                                                                  | low-power shutdown.                                                                |                                                                            |  |  |  |  |

|     |            | 1: ADC0 Enabled. ADC0 is act                                                                                                                                                                                                                                                                                                                                                                                                                  | tive and ready for data conv                                                       | ersions.                                                                   |  |  |  |  |

| 6   | AD0TM      | ADC0 Track Mode Bit.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |                                                                            |  |  |  |  |

|     |            | <ul> <li>0: Normal Track Mode: When ADC0 is enabled, tracking is continuous unless a conversion is in progress. Conversion begins immediately on start-of-conversion event, as defined by AD0CM[2:0].</li> <li>1: Delayed Track Mode: When ADC0 is enabled, input is tracked when a conversion is not in progress. A start-of-conversion signal initiates three SAR clocks of additional tracking, and then begins the conversion.</li> </ul> |                                                                                    |                                                                            |  |  |  |  |

| 5   | AD0INT     | ADC0 Conversion Complete Interrupt Flag.                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                                            |  |  |  |  |

|     |            | 0: ADC0 has not completed a data conversion since AD0INT was last cleared.<br>1: ADC0 has completed a data conversion.                                                                                                                                                                                                                                                                                                                        |                                                                                    |                                                                            |  |  |  |  |

| 4   | AD0BUSY    | ADC0 Busy Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                | Read:                                                                              | Write:                                                                     |  |  |  |  |

|     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0: ADC0 conversion is not<br>in progress.<br>1: ADC0 conversion is in<br>progress. | 0: No Effect.<br>1: Initiates ADC0 Conver-<br>sion if AD0CM[2:0] =<br>000b |  |  |  |  |

| 3   | AD0WINT    | ADC0 Window Compare Inte                                                                                                                                                                                                                                                                                                                                                                                                                      | rrupt Flag.                                                                        |                                                                            |  |  |  |  |

|     |            | 0: ADC0 Window Comparison<br>cleared.<br>1: ADC0 Window Comparison                                                                                                                                                                                                                                                                                                                                                                            |                                                                                    | ed since this flag was last                                                |  |  |  |  |

| 2:0 | AD0CM[2:0] | ADC0 Start of Conversion M                                                                                                                                                                                                                                                                                                                                                                                                                    | ode Select.                                                                        |                                                                            |  |  |  |  |

|     |            | 000: ADC0 start-of-conversion                                                                                                                                                                                                                                                                                                                                                                                                                 | source is write of 1 to ADO                                                        | BUSY.                                                                      |  |  |  |  |

|     |            | 001: ADC0 start-of-conversion                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |                                                                            |  |  |  |  |

|     |            | 010: ADC0 start-of-conversion                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |                                                                            |  |  |  |  |

|     |            | 011: ADC0 start-of-conversion                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |                                                                            |  |  |  |  |

|     |            | 100: ADC0 start-of-conversion 101–111: Reserved.                                                                                                                                                                                                                                                                                                                                                                                              | source is rising edge of ext                                                       | ernal CNVSTR.                                                              |  |  |  |  |

|     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |                                                                            |  |  |  |  |

## SFR Definition 8.7. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7                  | 6                                                    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------------|------------------------------------------------------|---|---|---|---|---|---|--|--|

| Nam   | e                  | ADC0LTH[7:0]                                         |   |   |   |   |   |   |  |  |

| Туре  | 9                  | R/W                                                  |   |   |   |   |   |   |  |  |

| Rese  | et O               | 0                                                    | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | SFR Address = 0xC6 |                                                      |   |   |   |   |   |   |  |  |

| Bit   | Name               | Function                                             |   |   |   |   |   |   |  |  |

| 7:0   | ADC0LTH[7:0        | COLTH[7:0] ADC0 Less-Than Data Word High-Order Bits. |   |   |   |   |   |   |  |  |

# SFR Definition 8.8. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7                  | 6                                                    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------------|------------------------------------------------------|---|---|---|---|---|---|--|--|

| Nam   | e                  | ADC0LTL[7:0]                                         |   |   |   |   |   |   |  |  |

| Туре  | 9                  | R/W                                                  |   |   |   |   |   |   |  |  |

| Rese  | et 0               | 0                                                    | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | SFR Address = 0xC5 |                                                      |   |   |   |   |   |   |  |  |

| Bit   | Name               | Name Function                                        |   |   |   |   |   |   |  |  |

| 7:0   | ADC0LTL[7:0]       | DC0LTL[7:0] ADC0 Less-Than Data Word Low-Order Bits. |   |   |   |   |   |   |  |  |

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |

|-----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operations | S                                        | I     | I               |

| ADD A, Rn             | Add register to A                        | 1     | 1               |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                 | Increment A                              | 1     | 1               |

| INC Rn                | Increment register                       | 1     | 1               |

| INC direct            | Increment direct byte                    | 2     | 2               |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |

| DEC A                 | Decrement A                              | 1     | 1               |

| DEC Rn                | Decrement register                       | 1     | 1               |

| DEC direct            | Decrement direct byte                    | 2     | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |

| MUL AB                | Multiply A and B                         | 1     | 4               |

| DIV AB                | Divide A by B                            | 1     | 8               |

| DA A                  | Decimal adjust A                         | 1     | 1               |

| Logical Operations    | ,                                        |       |                 |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data     | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn             | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri            | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data          | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A         | Exclusive-OR A to direct byte            | 2     | 2               |

Table 14.1. CIP-51 Instruction Set Summary

| Mnemonic                    | Description                                | Bytes | Clock<br>Cycles |

|-----------------------------|--------------------------------------------|-------|-----------------|

| XRL direct, #data           | Exclusive-OR immediate to direct byte      | 3     | 3               |

| CLR A                       | Clear A                                    | 1     | 1               |

| CPL A                       | Complement A                               | 1     | 1               |

| RL A                        | Rotate A left                              | 1     | 1               |

| RLC A                       | Rotate A left through Carry                | 1     | 1               |

| RR A                        | Rotate A right                             | 1     | 1               |

| RRC A                       | Rotate A right through Carry               | 1     | 1               |

| SWAP A                      | Swap nibbles of A                          | 1     | 1               |

| Data Transfer               | -                                          | L.    | 1               |

| MOV A, Rn                   | Move Register to A                         | 1     | 1               |

| MOV A, direct               | Move direct byte to A                      | 2     | 2               |

| MOV A, @Ri                  | Move indirect RAM to A                     | 1     | 2               |

| MOV A, #data                | Move immediate to A                        | 2     | 2               |

| MOV Rn, A                   | Move A to Register                         | 1     | 1               |

| MOV Rn, direct              | Move direct byte to Register               | 2     | 2               |

| MOV Rn, #data               | Move immediate to Register                 | 2     | 2               |

| MOV direct, A               | Move A to direct byte                      | 2     | 2               |

| MOV direct, Rn              | Move Register to direct byte               | 2     | 2               |

| MOV direct, direct          | Move direct byte to direct byte            | 3     | 3               |

| MOV direct, @Ri             | Move indirect RAM to direct byte           | 2     | 2               |

| MOV direct, #data           | Move immediate to direct byte              | 3     | 3               |

| MOV @Ri, A                  | Move A to indirect RAM                     | 1     | 2               |

| MOV @Ri, direct             | Move direct byte to indirect RAM           | 2     | 2               |

| MOV @Ri, #data              | Move immediate to indirect RAM             | 2     | 2               |

| MOV DPTR, #data16           | Load DPTR with 16-bit constant             | 3     | 3               |

| MOVC A, @A+DPTR             | Move code byte relative DPTR to A          | 1     | 3               |

| MOVC A, @A+PC               | Move code byte relative PC to A            | 1     | 3               |

| MOVX A, @Ri                 | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri, A                 | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A, @DPTR               | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR, A               | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct                 | Push direct byte onto stack                | 2     | 2               |

| POP direct                  | Pop direct byte from stack                 | 2     | 2               |

| XCH A, Rn                   | Exchange Register with A                   | 1     | 1               |

| XCH A, direct               | Exchange direct byte with A                | 2     | 2               |

| XCH A, @Ri                  | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A, @Ri                 | Exchange low nibble of indirect RAM with A | 1     | 2               |

| <b>Boolean Manipulation</b> | -                                          | L.    | 1               |

| CLR C                       | Clear Carry                                | 1     | 1               |

| CLR bit                     | Clear direct bit                           | 2     | 2               |

| SETB C                      | Set Carry                                  | 1     | 1               |

| SETB bit                    | Set direct bit                             | 2     | 2               |

| CPL C                       | Complement Carry                           | 1     | 1               |

| CPL bit                     | Complement direct bit                      | 2     | 2               |

Table 14.1. CIP-51 Instruction Set Summary (Continued)

features of the C8051F80x-83x devices.

| Action                                                                   | C2 Debug      | User Firmware executing from: |               |  |  |

|--------------------------------------------------------------------------|---------------|-------------------------------|---------------|--|--|

|                                                                          | Interface     | an unlocked page              | a locked page |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)      | Permitted     | Permitted                     | Permitted     |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)        | Not Permitted | FEDR                          | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)      | Permitted     | Permitted                     | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)       | Not Permitted | FEDR                          | Permitted     |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted     | Permitted                     | Permitted     |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted | FEDR                          | Permitted     |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted     | FEDR                          | FEDR          |  |  |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | Only by C2DE  | FEDR                          | FEDR          |  |  |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted | FEDR                          | FEDR          |  |  |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted | FEDR                          | FEDR          |  |  |

| Read, Write or Erase Reserved Area                                       | Not Permitted | FEDR                          | FEDR          |  |  |

## Table 19.1. Flash Security Summary

C2DE—C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte) FEDR—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is 1 after reset)

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

## 19.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of VDD, system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the VDD Monitor must be enabled and enabled as a reset source on C8051F80x-83x devices for the Flash to be successfully modified. If either the VDD Monitor or the VDD Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

#### 19.4.3. System Clock

- 1. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 2. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in "AN201: Writing to Flash from Firm-ware," available from the Silicon Laboratories website.

## SFR Definition 22.4. OSCXCN: External Oscillator Control

| Bit   | 7      | 6   | 5          | 4  | 3 | 2         | 1   | 0 |

|-------|--------|-----|------------|----|---|-----------|-----|---|

| Name  | XTLVLD | Х   | (OSCMD[2:0 | )] |   | XFCN[2:0] |     |   |

| Туре  | R      | R/W |            |    | R |           | R/W |   |

| Reset | 0      | 0   | 0          | 0  | 0 | 0         | 0   | 0 |

SFR Address = 0xB1

| Bit | Name        |         |                                                                                               | Function                                  |                 |  |  |  |  |

|-----|-------------|---------|-----------------------------------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|

| 7   | XTLVLD      | Crystal | Oscillator Valid Flag.                                                                        |                                           |                 |  |  |  |  |

|     |             | •       | Read only when XOSCMD = 11x.)                                                                 |                                           |                 |  |  |  |  |

|     |             | -       | al Oscillator is unused or                                                                    | •                                         |                 |  |  |  |  |

|     |             | ,       | al Oscillator is running ar                                                                   |                                           |                 |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Selec                                                                       | ct.                                       |                 |  |  |  |  |

|     |             |         | ernal Oscillator circuit of                                                                   |                                           |                 |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                                                        |                                           |                 |  |  |  |  |

|     |             |         | ernal CMOS Clock Mode                                                                         | e with divide by 2 stage.                 |                 |  |  |  |  |

|     |             |         | Oscillator Mode.                                                                              |                                           |                 |  |  |  |  |

|     |             |         | pacitor Oscillator Mode.                                                                      |                                           |                 |  |  |  |  |

|     |             | -       | vstal Oscillator Mode.<br>vstal Oscillator Mode with                                          | divida by 2 staga                         |                 |  |  |  |  |

|     |             |         |                                                                                               | i ulviue by 2 stage.                      |                 |  |  |  |  |

| 3   | Unused      |         | 0; Write = Don't Care                                                                         |                                           |                 |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | I Oscillator Frequency                                                                        |                                           |                 |  |  |  |  |

|     |             |         | -                                                                                             | uency for Crystal or RC r                 | node.           |  |  |  |  |

|     |             |         | ording to the desired K F                                                                     |                                           |                 |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                                                                  | RC Mode                                   | C Mode          |  |  |  |  |

|     |             | 000     | f ≤ 32 kHz                                                                                    | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                                                           | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |

|     |             | 010     | 84 kHz < f ≤ 225 kHz                                                                          | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |

|     |             | 011     | 011 225 kHz < f $\leq$ 590 kHz 100 kHz < f $\leq$ 200 kHz K Factor = 22                       |                                           |                 |  |  |  |  |

|     |             | 100     | 100         590 kHz < f $\le$ 1.5 MHz         200 kHz < f $\le$ 400 kHz         K Factor = 65 |                                           |                 |  |  |  |  |

|     |             | 101     | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                                                       | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |

|     |             | 110     | $4 \text{ MHz} < f \le 10 \text{ MHz}$                                                        | 800 kHz $<$ f $\leq$ 1.6 MHz              | K Factor = 664  |  |  |  |  |

|     |             | 111     | 10 MHz < f ≤ 30 MHz                                                                           | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |

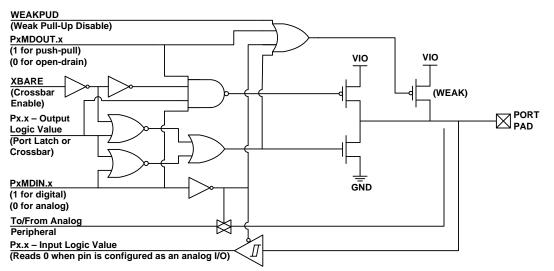

## 23.1. Port I/O Modes of Operation

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 23.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN and PnMDOUT registers. Port pin P2.0 can be configured by software for digital I/O using the P2MDOUT register. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled. Until the crossbar is enabled (XBARE = 1), both the high and low port I/O drive circuits are explicitly disabled on all crossbar pins.

### 23.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, Capacitive Sense input, external oscillator input/output, VREF output, or AGND connection should be configured for analog I/O (PnMDIN.n = 0, Pn.n = 1). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. To prevent the low port I/o drive circuit from pulling the pin low, a '1' should be written to the corresponding port latch (Pn.n = 1). Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital I/O may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

### 23.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

## SFR Definition 23.8. P0MDIN: Port 0 Input Mode

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  |   | P0MDIN[7:0]     |   |   |   |   |   |   |

| Туре  |   | R/W             |   |   |   |   |   |   |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |

SFR Address = 0xF1

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                                                                                                                                                                                                  |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. In order for the P0.n pin to be in analog mode, there <b>MUST be a '1' in the Port Latch register corresponding to that pin.</b><br>0: Corresponding P0.n pin is configured for analog mode.<br>1: Corresponding P0.n pin is not configured for analog mode. |

## SFR Definition 23.9. P0MDOUT: Port 0 Output Mode

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  |   | POMDOUT[7:0]    |   |   |   |   |   |   |

| Туре  |   | R/W             |   |   |   |   |   |   |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

SFR Address = 0xA4

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDOUT[7:0] | Output Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P0MDIN is logic 0.<br>0: Corresponding P0.n Output is open-drain.<br>1: Corresponding P0.n Output is push-pull. |

## 24.3. Preparing for a CRC Calculation

To prepare CRC0 for a CRC calculation, software should select the desired polynomial and set the initial value of the result. Two polynomials are available: 0x1021 (16-bit) and 0x04C11DB7 (32-bit). The CRC0 result may be initialized to one of two values: 0x00000000 or 0xFFFFFFFF. The following steps can be used to initialize CRC0.

- 1. Select a polynomial (Set CRC0SEL to 0 for 32-bit or 1 for 16-bit).

- 2. Select the initial result value (Set CRC0VAL to 0 for 0x0000000 or 1 for 0xFFFFFFF).

- 3. Set the result to its initial value (Write 1 to CRC0INIT).

## 24.4. Performing a CRC Calculation

Once CRC0 is initialized, the input data stream is sequentially written to CRC0IN, one byte at a time. The CRC0 result is automatically updated after each byte is written. The CRC engine may also be configured to automatically perform a CRC on one or more Flash sectors. The following steps can be used to automatically perform a CRC on Flash memory.

- 1. Prepare CRC0 for a CRC calculation as shown above.

- 2. Write the index of the starting page to CRC0AUTO.

- 3. Set the AUTOEN bit in CRC0AUTO.

- 4. Write the number of Flash sectors to perform in the CRC calculation to CRC0CNT.

**Note:** Each Flash sector is 512 bytes.

- 5. Write any value to CRC0CN (or OR its contents with 0x00) to initiate the CRC calculation. The CPU will not execute code any additional code until the CRC operation completes.

- 6. Clear the AUTOEN bit in CRC0AUTO.

- 7. Read the CRC result using the procedure below.

## 24.5. Accessing the CRC0 Result

The internal CRC0 result is 32-bits (CRC0SEL = 0b) or 16-bits (CRC0SEL = 1b). The CRC0PNT bits select the byte that is targeted by read and write operations on CRC0DAT and increment after each read or write. The calculation result will remain in the internal CR0 result register until it is set, overwritten, or additional data is written to CRC0IN.

## 25.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 25.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

### 25.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

### 25.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 25.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- 1. NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- 3. NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 25.2, Figure 25.3, and Figure 25.4 for typical connection diagrams of the various operational modes. **Note that the setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "23. Port Input/Output" on page 138 for general purpose port I/O and crossbar information.

## 25.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag

## SFR Definition 26.3. SMB0ADR: SMBus Slave Address

| Bit   | 7             | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|----------|---|---|---|---|---|---|

| Name  |               | SLV[6:0] |   |   |   |   |   |   |

| Туре  |               | R/W      |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 0 0 |          |   |   |   |   |   | 0 |

SFR Address = 0xD7

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV[6:0] | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |          | Defines the SMBus Slave Address(es) for automatic hardware acknowledgement.<br>Only address bits which have a 1 in the corresponding bit position in SLVM[6:0]<br>are checked against the incoming address. This allows multiple addresses to be<br>recognized.            |

| 0   | GC       | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |          | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

## SFR Definition 26.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7             | 6         | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|-----------|---|---|---|---|---|---|

| Name  |               | SLVM[6:0] |   |   |   |   |   |   |

| Туре  |               | R/W       |   |   |   |   |   |   |

| Reset | 1 1 1 1 1 1 1 |           |   |   |   |   |   | 0 |

### SFR Address = 0xD6

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | <ul><li>Enables hardware acknowledgement of slave address and received data bytes.</li><li>0: Firmware must manually acknowledge all incoming address and data bytes.</li><li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li></ul>                |

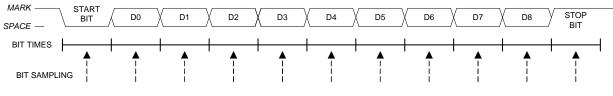

### 27.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to 1. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to 1. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to 1.

## SFR Definition 28.4. TL0: Timer 0 Low Byte

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7            | 6                                                       | 5        | 4 | 3 | 2 | 1 | 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------|----------|---|---|---|---|---|

| Name TL0[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                                         |          |   |   |   |   |   |

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •            | R/W                                                     |          |   |   |   |   |   |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>0</td> <td>0</td> <td>0</td> |              | 0                                                       | 0        | 0 |   |   |   |   |

| SFR A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ddress = 0x8 | A                                                       |          |   |   |   |   |   |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Name         |                                                         | Function |   |   |   |   |   |

| 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TL0[7:0]     | Timer 0 Low Byte.                                       |          |   |   |   |   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              | The TL0 register is the low byte of the 16-bit Timer 0. |          |   |   |   |   |   |

# SFR Definition 28.5. TL1: Timer 1 Low Byte

| Bit   | 7              | 6            | 5     | 4   | 3        | 2 | 1 | 0 |

|-------|----------------|--------------|-------|-----|----------|---|---|---|

| Name  | •              |              |       | TL1 | 7:0]     |   |   |   |

| Туре  |                | R/W          |       |     |          |   |   |   |

| Reset | t 0            | 0            | 0     | 0   | 0        | 0 | 0 | 0 |

| SFR A | Address = 0x8B |              |       |     |          |   |   |   |

| Bit   | Name           |              |       |     | Function |   |   |   |

| 7.0   | TL 4[7.0]      | Time and Las | Durta |     |          |   |   |   |

| 7:0 | TL1[7:0] | Timer 1 Low Byte.                                       |

|-----|----------|---------------------------------------------------------|

|     |          | The TL1 register is the low byte of the 16-bit Timer 1. |