# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                  |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                          |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 16x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f801-gu |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

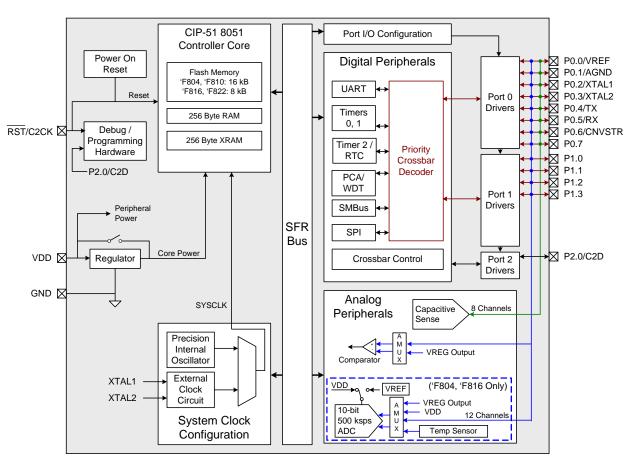

Figure 1.5. C8051F804, C8051F810, C8051F816, C8051F822 Block Diagram

| Part<br>Number | Digital<br>Port I/Os | Capacitive Sense<br>Channels | Flash<br>Memory<br>(kB) | RAM<br>(Bytes) | 10-bit<br>500 ksps<br>ADC | ADC<br>Channels | Temperature<br>Sensor | Package (RoHS) |

|----------------|----------------------|------------------------------|-------------------------|----------------|---------------------------|-----------------|-----------------------|----------------|

| C8051F800-GU   | 17                   | 16                           | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F801-GU   | 17                   | 8                            | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F802-GU   | 17                   |                              | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F800-GM   | 17                   | 16                           | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F801-GM   | 17                   | 8                            | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F802-GM   | 17                   | _                            | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F803-GS   | 13                   | 12                           | 16                      | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F804-GS   | 13                   | 8                            | 16                      | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F805-GS   | 13                   | _                            | 16                      | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F806-GU   | 17                   | 16                           | 16                      | 512            | —                         |                 |                       | QSOP-24        |

| C8051F807-GU   | 17                   | 8                            | 16                      | 512            | —                         |                 |                       | QSOP-24        |

| C8051F808-GU   | 17                   | _                            | 16                      | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F806-GM   | 17                   | 16                           | 16                      | 512            |                           |                 | —                     | QFN-20         |

| C8051F807-GM   | 17                   | 8                            | 16                      | 512            | —                         |                 | —                     | QFN-20         |

| C8051F808-GM   | 17                   | _                            | 16                      | 512            | —                         |                 | —                     | QFN-20         |

| C8051F809-GS   | 13                   | 12                           | 16                      | 512            | —                         |                 |                       | SOIC-16        |

| C8051F810-GS   | 13                   | 8                            | 16                      | 512            | —                         |                 |                       | SOIC-16        |

| C8051F811-GS   | 13                   | _                            | 16                      | 512            | —                         |                 |                       | SOIC-16        |

| C8051F812-GU   | 17                   | 16                           | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F813-GU   | 17                   | 8                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F814-GU   | 17                   | _                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F812-GM   | 17                   | 16                           | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F813-GM   | 17                   | 8                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F814-GM   | 17                   | _                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F815-GS   | 13                   | 12                           | 8                       | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F816-GS   | 13                   | 8                            | 8                       | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F817-GS   | 13                   | —                            | 8                       | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F818-GU   | 17                   | 16                           | 8                       | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F819-GU   | 17                   | 8                            | 8                       | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F820-GU   | 17                   | —                            | 8                       | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F818-GM   | 17                   | 16                           | 8                       | 512            |                           |                 |                       | QFN-20         |

| C8051F819-GM   | 17                   | 8                            | 8                       | 512            | —                         |                 |                       | QFN-20         |

| C8051F820-GM   | 17                   |                              | 8                       | 512            |                           | _               |                       | QFN-20         |

Table 2.1. Product Selection Guide

### Table 7.13. Comparator Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise noted.

| Parameter                                         | Conditions              | Min   | Тур  | Max                    | Units |

|---------------------------------------------------|-------------------------|-------|------|------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 220  | —                      | ns    |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | —     | 225  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 340  | —                      | ns    |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+-CP0-=-100  mV      | —     | 380  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 510  | —                      | ns    |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | —     | 945  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 1500 | —                      | ns    |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100  mV  | —     | 5000 | —                      | ns    |

| Common-Mode Rejection Ratio                       |                         | —     | 1    | 4                      | mV/V  |

| Positive Hysteresis 1                             | Mode 2, CP0HYP1–0 = 00b | —     | 0    | 1                      | mV    |

| Positive Hysteresis 2                             | Mode 2, CP0HYP1–0 = 01b | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                             | Mode 2, CP0HYP1–0 = 10b | 7     | 10   | 20                     | mV    |

| Positive Hysteresis 4                             | Mode 2, CP0HYP1–0 = 11b | 10    | 20   | 30                     | mV    |

| Negative Hysteresis 1                             | Mode 2, CP0HYN1–0 = 00b | —     | 0    | 1                      | mV    |

| Negative Hysteresis 2                             | Mode 2, CP0HYN1–0 = 01b | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                             | Mode 2, CP0HYN1–0 = 10b | 7     | 10   | 20                     | mV    |

| Negative Hysteresis 4                             | Mode 2, CP0HYN1–0 = 11b | 10    | 20   | 30                     | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                         | -0.25 | _    | V <sub>DD</sub> + 0.25 | V     |

| Input Offset Voltage                              |                         | -7.5  | _    | 7.5                    | mV    |

| Power Specifications                              | •                       |       |      |                        |       |

| Power Supply Rejection                            |                         |       | 0.1  | —                      | mV/V  |

| Powerup Time                                      |                         | —     | 10   | —                      | μs    |

| Supply Current at DC                              | Mode 0                  | —     | 20   | —                      | μA    |

|                                                   | Mode 1                  | —     | 8    | —                      | μA    |

|                                                   | Mode 2                  | —     | 3    | —                      | μA    |

|                                                   | Mode 3                  | —     | 0.5  | —                      | μA    |

| Note: Vcm is the common-mode vo                   | Itage on CP0+ and CP0–. | ·     |      |                        |       |

### 8.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

### SFR Definition 8.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit                | 7               | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|-----------------|--------------|---|---|---|---|---|---|

| Name               |                 | ADC0GTH[7:0] |   |   |   |   |   |   |

| Туре               | R/W             |              |   |   |   |   |   |   |

| Reset              | 1 1 1 1 1 1 1 1 |              |   |   |   |   |   |   |

| SFR Address = 0xC4 |                 |              |   |   |   |   |   |   |

| Bit | Name         | Function                                     |

|-----|--------------|----------------------------------------------|

| 7:0 | ADC0GTH[7:0] | ADC0 Greater-Than Data Word High-Order Bits. |

### SFR Definition 8.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit   | 7                  | 6            | 5                                           | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------------|--------------|---------------------------------------------|---|---|---|---|---|--|

| Nam   | e                  | ADC0GTL[7:0] |                                             |   |   |   |   |   |  |

| Туре  | 9                  | R/W          |                                             |   |   |   |   |   |  |

| Rese  | et 1               | 1            | 1                                           | 1 | 1 | 1 | 1 | 1 |  |

| SFR A | SFR Address = 0xC3 |              |                                             |   |   |   |   |   |  |

| Bit   | Name               |              | Function                                    |   |   |   |   |   |  |

| 7:0   | ADC0GTL[7:0]       | ADC0 G       | ADC0 Greater-Than Data Word Low-Order Bits. |   |   |   |   |   |  |

### **10.1. External Voltage References**

To use an external voltage reference, REFSL[1:0] should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference.

### **10.2.** Internal Voltage Reference Options

A 1.65 V high-speed reference is included on-chip. The high speed internal reference is selected by setting REFSL[1:0] to 11. When selected, the high speed internal reference will be automatically enabled on an as-needed basis by ADC0.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide ADC0 with added dynamic range at the cost of reduced power supply noise rejection. To use the 1.8 to 3.6 V power supply voltage ( $V_{DD}$ ) or the 1.8 V regulated digital supply voltage as the reference source, REFSL[1:0] should be set to 01 or 10, respectively.

### 10.3. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for ADC0 is taken from the P0.1/AGND pin. Any external sensors sampled by ADC0 should be referenced to the P0.1/AGND pin. The separate analog ground reference option is enabled by setting REFGND to 1. Note that when using this option, P0.1/AGND must be connected to the same potential as GND.

### 10.4. Temperature Sensor Enable

The TEMPE bit in register REF0CN enables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

## 11. Voltage Regulator (REG0)

C8051F80x-83x devices include an internal voltage regulator (REG0) to regulate the internal core supply to 1.8 V from a  $V_{DD}$  supply of 1.8 to 3.6 V. A power-saving mode is built into the regulator to help reduce current consumption in low-power applications. This mode is accessed through the REG0CN register (SFR Definition 11.1). Electrical characteristics for the on-chip regulator are specified in Table 7.5 on page 41

Under default conditions, when the device enters STOP mode the internal regulator will remain on. This allows any enabled reset source to generate a reset for the device and bring the device out of STOP mode. For additional power savings, the STOPCF bit can be used to shut down the regulator and the internal power network of the device when the part enters STOP mode. When STOPCF is set to 1, the RST pin or a full power cycle of the device are the only methods of generating a reset.

## SFR Definition 11.1. REG0CN: Voltage Regulator Control

| Bit   | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| Name  | STOPCF |     |     |     |     |     |     |     |

| Туре  | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

### SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOPCF   | Stop Mode Configuration.                                                                                                                                                                                                                                                            |

|     |          | This bit configures the regulator's behavior when the device enters STOP mode.<br>0: Regulator is still active in STOP mode. Any enabled reset source will reset the<br>device.<br>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset<br>the device. |

| 6:0 | Reserved | Must write to 000000b.                                                                                                                                                                                                                                                              |

### SFR Definition 13.3. CS0DH: Capacitive Sense Data High Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | CS0DH[7:0] |   |   |   |   |   |   |

| Туре  | R | R          | R | R | R | R | R | R |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xAC

| Bit | Name  | Description                                                                    |

|-----|-------|--------------------------------------------------------------------------------|

| 7:0 | CS0DH | CS0 Data High Byte.                                                            |

|     |       | Stores the high byte of the last completed 16-bit Capacitive Sense conversion. |

### SFR Definition 13.4. CS0DL: Capacitive Sense Data Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | CS0DL[7:0] |   |   |   |   |   |   |

| Туре  | R | R          | R | R | R | R | R | R |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xAB

| Bit | Name  | Description                                                                   |

|-----|-------|-------------------------------------------------------------------------------|

| 7:0 | CS0DL | CS0 Data Low Byte.                                                            |

|     |       | Stores the low byte of the last completed 16-bit Capacitive Sense conversion. |

### SFR Definition 14.3. SP: Stack Pointer

| Bit   | 7            | 6            | 5 | 4 | 3        | 2 | 1 | 0 |

|-------|--------------|--------------|---|---|----------|---|---|---|

| Nam   | e            | SP[7:0]      |   |   |          |   |   |   |

| Туре  | •            | R/W          |   |   |          |   |   |   |

| Rese  | <b>t</b> 0   | 0            | 0 | 0 | 0        | 1 | 1 | 1 |

| SFR A | ddress = 0x8 | 51           |   | 1 |          |   |   |   |

| Bit   | Name         |              |   |   | Function |   |   |   |

| 7:0   | SP[7:0]      | Stack Pointe | r |   |          |   |   |   |

The Stack Pointer holds the location of the top of the stack. The stack pointer is incremented before every PUSH operation. The SP register defaults to 0x07 after reset.

### SFR Definition 14.4. ACC: Accumulator

| Bit   | 7            | 6             | 5     | 4 | 3        | 2 | 1 | 0 |

|-------|--------------|---------------|-------|---|----------|---|---|---|

| Name  | e            | ACC[7:0]      |       |   |          |   |   |   |

| Туре  | •            | R/W           |       |   |          |   |   |   |

| Rese  | t 0          | 0             | 0     | 0 | 0        | 0 | 0 | 0 |

| SFR A | ddress = 0xE | 0; Bit-Addres | sable |   |          |   |   |   |

| Bit   | Name         |               |       |   | Function |   |   |   |

| BIt | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

### SFR Definition 18.2. IP: Interrupt Priority

|       | - |       |     |     |     |     | -   | -   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

### SFR Address = 0xB8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 1b, Write = Don't Care.                                                                                                                                                                                                                                 |

| 6   | PSPI0  | Serial Peripheral Interface (SPI0) Interrupt Priority Control.<br>This bit sets the priority of the SPI0 interrupt.<br>0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level.                                           |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                                                         |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                                                                     |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                                                         |

| 2   | PX1    | <ul> <li>External Interrupt 1 Priority Control.</li> <li>This bit sets the priority of the External Interrupt 1 interrupt.</li> <li>0: External Interrupt 1 set to low priority level.</li> <li>1: External Interrupt 1 set to high priority level.</li> </ul> |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                                                         |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level.                                       |

### SFR Definition 18.4. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|-------|---|---|---|---|---|---|--------|--------|

| Name  |   |   |   |   |   |   | ECSGRT | ECSCPT |

| Туре  | R | R | R | R | R | R | R/W    | R/W    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

SFR Address = 0xE7

| Bit | Name   | Function                                                                                                                                                                           |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b; Write = don't care.                                                                                                                                                |

| 1   | ECSGRT | Enable Capacitive Sense Greater Than Comparator Interrupt.<br>0: Disable Capacitive Sense Greater Than Comparator interrupt.<br>1: Enable interrupt requests generated by CS0CMPF. |

| 0   | ECSCPT | Enable Capacitive Sense Conversion Complete Interrupt.<br>0: Disable Capacitive Sense Conversion Complete interrupt.<br>1: Enable interrupt requests generated by CS0INT.          |

## SFR Definition 18.5. EIP1: Extended Interrupt Priority 1

| Bit   | 7        | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|----------|----------|------|-------|-------|--------|------|-------|

| Name  | Reserved | Reserved | PCP0 | PPCA0 | PADC0 | PWADC0 | PMAT | PSMB0 |

| Туре  | W        | W        | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0        | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

SFR Address = 0xF3

| Bit | Name     | Function                                                                     |

|-----|----------|------------------------------------------------------------------------------|

| 7:6 | Reserved | Must write 0.                                                                |

| 5   | PCP0     | Comparator0 (CP0) Interrupt Priority Control.                                |

|     |          | This bit sets the priority of the CP0 rising edge or falling edge interrupt. |

|     |          | 0: CP0 interrupt set to low priority level.                                  |

|     |          | 1: CP0 interrupt set to high priority level.                                 |

| 4   | PPCA0    | Programmable Counter Array (PCA0) Interrupt Priority Control.                |

|     |          | This bit sets the priority of the PCA0 interrupt.                            |

|     |          | 0: PCA0 interrupt set to low priority level.                                 |

|     |          | 1: PCA0 interrupt set to high priority level.                                |

| 3   | PADC0    | ADC0 Conversion Complete Interrupt Priority Control.                         |

|     |          | This bit sets the priority of the ADC0 Conversion Complete interrupt.        |

|     |          | 0: ADC0 Conversion Complete interrupt set to low priority level.             |

|     |          | 1: ADC0 Conversion Complete interrupt set to high priority level.            |

| 2   | PWADC0   | ADC0 Window Comparator Interrupt Priority Control.                           |

|     |          | This bit sets the priority of the ADC0 Window interrupt.                     |

|     |          | 0: ADC0 Window interrupt set to low priority level.                          |

|     |          | 1: ADC0 Window interrupt set to high priority level.                         |

| 1   | PMAT     | Port Match Interrupt Priority Control.                                       |

|     |          | This bit sets the priority of the Port Match Event interrupt.                |

|     |          | 0: Port Match interrupt set to low priority level.                           |

|     |          | 1: Port Match interrupt set to high priority level.                          |

| 0   | PSMB0    | SMBus (SMB0) Interrupt Priority Control.                                     |

|     |          | This bit sets the priority of the SMB0 interrupt.                            |

|     |          | 0: SMB0 interrupt set to low priority level.                                 |

|     |          | 1: SMB0 interrupt set to high priority level.                                |

### 23.1. Port I/O Modes of Operation

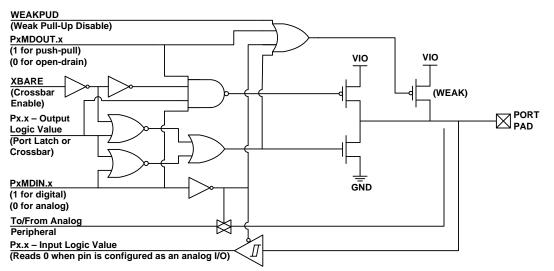

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 23.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN and PnMDOUT registers. Port pin P2.0 can be configured by software for digital I/O using the P2MDOUT register. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled. Until the crossbar is enabled (XBARE = 1), both the high and low port I/O drive circuits are explicitly disabled on all crossbar pins.

### 23.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, Capacitive Sense input, external oscillator input/output, VREF output, or AGND connection should be configured for analog I/O (PnMDIN.n = 0, Pn.n = 1). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. To prevent the low port I/o drive circuit from pulling the pin low, a '1' should be written to the corresponding port latch (Pn.n = 1). Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital I/O may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

### 23.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

imum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                 | Minimum SDA Setup Time                                                                                                                                      | Minimum SDA Hold Time                  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 0                       | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup>                                                                         | 3 system clocks                        |

| 1                       | 11 system clocks                                                                                                                                            | 12 system clocks                       |

| software a<br>ACK is wi | ne for ACK bit transmissions and the<br>acknowledgement, the s/w delay occ<br>ritten and when SI is cleared. Note th<br>es the outgoing ACK value, s/w dela | nat if SI is cleared in the same write |

Table 26.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "26.3.4. SCL Low Timeout" on page 182). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 26.4).

## SFR Definition 26.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1    | 0       |

|-------|-------|-----|------|---------|--------|--------|------|---------|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBC | :S[1:0] |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/   | W       |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0    | 0       |

SFR Address = 0xC1

| ENSMB      | <b>SMBus Enable.</b><br>This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INH        |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INH        |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|            | This bit controls the SDA setup and hold times according to Table 26.2.<br>0: SDA Extended Setup and Hold Times disabled.<br>1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                            |

| SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | These two bits select the SMBus clock source, which is used to generate the SMBus<br>bit rate. The selected device should be configured according to Equation 26.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow                                                                                                                                                |

|            | EXTHOLD<br>SMBTOE<br>SMBFTE                                                                                                                                                                                                                                                                                                                                                                                                           |

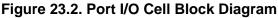

### 27.2. Operational Modes

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown in Figure 27.3.

Figure 27.3. UART Interconnect Diagram

### 27.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

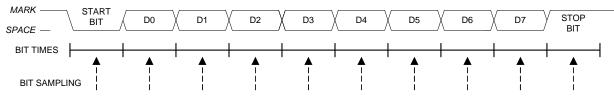

Figure 27.4. 8-Bit UART Timing Diagram

### SFR Definition 28.4. TL0: Timer 0 Low Byte

| Bit           | 7            | 6                                                       | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|--------------|---------------------------------------------------------|---|---|---|---|---|---|

| Name TL0[7:0] |              |                                                         |   |   |   |   |   |   |

| Туре          | R/W          |                                                         |   |   |   |   |   |   |

| Rese          | t 0          | 0                                                       | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR A         | ddress = 0x8 | A                                                       |   |   |   |   |   |   |

| Bit           | Name         | Function                                                |   |   |   |   |   |   |

| 7:0           | TL0[7:0]     | Timer 0 Low Byte.                                       |   |   |   |   |   |   |

|               |              | The TL0 register is the low byte of the 16-bit Timer 0. |   |   |   |   |   |   |

## SFR Definition 28.5. TL1: Timer 1 Low Byte

| Bit                | 7         | 6          | 5 | 4   | 3     | 2 | 1 | 0        |

|--------------------|-----------|------------|---|-----|-------|---|---|----------|

| Name               | 9         |            |   | TL1 | [7:0] |   |   | <u>I</u> |

| Туре               |           | R/W        |   |     |       |   |   |          |

| Rese               | t 0       | 0          | 0 | 0   | 0     | 0 | 0 | 0        |

| SFR Address = 0x8B |           |            |   |     |       |   |   |          |

| Bit                | Name      | e Function |   |     |       |   |   |          |

| 7.0                | TL 4[7.0] |            |   |     |       |   |   |          |

| 7: | 0 | TL1[7:0] | Timer 1 Low Byte.                                       |

|----|---|----------|---------------------------------------------------------|

|    |   |          | The TL1 register is the low byte of the 16-bit Timer 1. |

### 29.3.3. High-Speed Output Mode

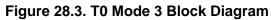

In high-speed output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the high-speed output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 29.6. PCA High-Speed Output Mode Diagram

### C2 Register Definition 30.4. FPCTL: C2 Flash Programming Control

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | FPCTL[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

C2 Address: 0x02

| Bit | Name       | Function                                                                                                                                                                                                                                                          |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FPCTL[7:0] | C2 Flash Programming Control Register.                                                                                                                                                                                                                            |

|     |            | This register is used to enable Flash programming via the C2 interface. To enable C2 Flash programming, the following codes must be written in order: 0x02, 0x01. Once C2 Flash programming is enabled, a system reset must be issued to resume normal operation. |

## C2 Register Definition 30.5. FPDAT: C2 Flash Programming Data

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | FPDAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

C2 Address: 0xBF

| Bit | Name       |                                                                                                                                | Function          |  |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| 7:0 | FPDAT[7:0] | C2 Flash Programming Data Register.                                                                                            |                   |  |  |  |  |

|     |            | This register is used to pass Flash commands, addresses, and data during C2 Flas<br>accesses. Valid commands are listed below. |                   |  |  |  |  |

|     |            | Code Command                                                                                                                   |                   |  |  |  |  |

|     |            | 0x06                                                                                                                           | Flash Block Read  |  |  |  |  |

|     |            | 0x07                                                                                                                           | Flash Block Write |  |  |  |  |

|     |            | 0x08                                                                                                                           | Flash Page Erase  |  |  |  |  |

|     |            | 0x03                                                                                                                           | Device Erase      |  |  |  |  |