Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 16x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f802-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Registers

| SFR | Definition 8.1 | . ADC0CF: ADC0 Configuration                               | . 50 |

|-----|----------------|------------------------------------------------------------|------|

| SFR | Definition 8.2 | . ADC0H: ADC0 Data Word MSB                                | . 51 |

| SFR | Definition 8.3 | . ADC0L: ADC0 Data Word LSB                                | . 51 |

| SFR | Definition 8.4 | . ADC0CN: ADC0 Control                                     | . 52 |

| SFR | Definition 8.5 | . ADC0GTH: ADC0 Greater-Than Data High Byte                | . 53 |

| SFR | Definition 8.6 | . ADC0GTL: ADC0 Greater-Than Data Low Byte                 | . 53 |

| SFR | Definition 8.7 | . ADC0LTH: ADC0 Less-Than Data High Byte                   | . 54 |

| SFR | Definition 8.8 | . ADC0LTL: ADC0 Less-Than Data Low Byte                    | . 54 |

|     |                | . ADC0MX: AMUX0 Channel Select                             |      |

| SFR | Definition 10. | 1. REF0CN: Voltage Reference Control                       | . 62 |

| SFR | Definition 11. | 1. REG0CN: Voltage Regulator Control                       | . 64 |

|     |                | 1. CPT0CN: Comparator0 Control                             |      |

|     |                | 2. CPT0MD: Comparator0 Mode Selection                      |      |

|     |                | 3. CPT0MX: Comparator0 MUX Selection                       |      |

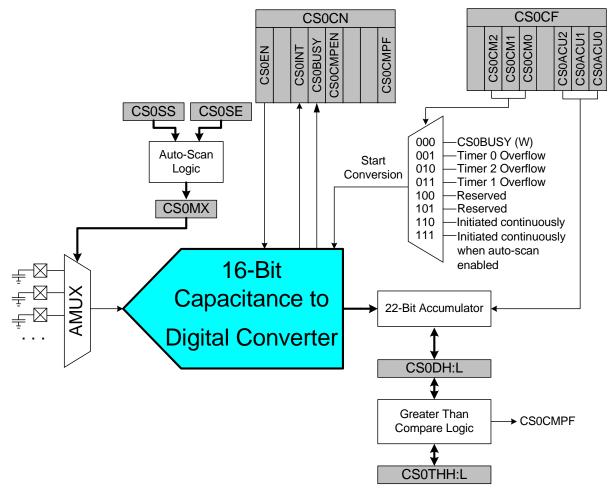

| SFR | Definition 13. | 1. CS0CN: Capacitive Sense Control                         | . 75 |

|     |                | 2. CS0CF: Capacitive Sense Configuration                   |      |

|     |                | 3. CS0DH: Capacitive Sense Data High Byte                  |      |

|     |                | 4. CS0DL: Capacitive Sense Data Low Byte                   |      |

|     |                | 5. CS0SS: Capacitive Sense Auto-Scan Start Channel         |      |

|     |                | 6. CS0SE: Capacitive Sense Auto-Scan End Channel           |      |

|     |                | 7. CS0THH: Capacitive Sense Comparator Threshold High Byte |      |

|     |                | 8. CS0THL: Capacitive Sense Comparator Threshold Low Byte  |      |

|     |                | 9. CS0MX: Capacitive Sense Mux Channel Select              |      |

|     |                | 1. DPL: Data Pointer Low Byte                              |      |

|     |                | 2. DPH: Data Pointer High Byte                             |      |

|     |                | 3. SP: Stack Pointer                                       |      |

|     |                | 4. ACC: Accumulator                                        |      |

|     |                | 5. B: B Register                                           |      |

|     |                | 6. PSW: Program Status Word                                |      |

|     |                | 1. HWID: Hardware Identification Byte                      |      |

|     |                | 2. DERIVID: Derivative Identification Byte                 |      |

|     |                | 3. REVID: Hardware Revision Identification Byte            |      |

|     |                | 1. IE: Interrupt Enable                                    |      |

|     |                | 2. IP: Interrupt Priority                                  |      |

|     |                | 3. EIE1: Extended Interrupt Enable 1                       |      |

|     |                | 4. EIE2: Extended Interrupt Enable 2                       |      |

|     |                | 5. EIP1: Extended Interrupt Priority 1                     |      |

|     |                | 6. EIP2: Extended Interrupt Priority 2                     |      |

|     |                | 7. IT01CF: INT0/INT1 Configuration                         |      |

|     |                | 1. PSCTL: Program Store R/W Control                        |      |

|     |                | 2. FLKEY: Flash Lock and Key                               |      |

|     |                | 1. PCON: Power Control                                     |      |

| SFR | Definition 21. | 1. VDM0CN: VDD Monitor Control                             | 126  |

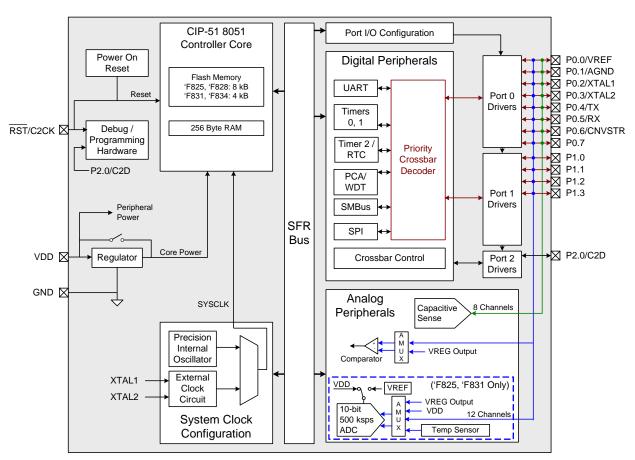

Figure 1.8. C8051F825, C8051F828, C8051F831, C8051F834 Block Diagram

| Name   | Pin<br>QSOP-24   | Pin<br>QFN-20 | Pin<br>SOIC-16 | Туре             | Description                                              |

|--------|------------------|---------------|----------------|------------------|----------------------------------------------------------|

| P0.5   | 21               | 16            | 14             | D I/O or<br>A In | Port 0.5.                                                |

| P0.6/  | 20               | 15            | 13             | D I/O or<br>A In | Port 0.6.                                                |

| CNVSTR |                  |               |                | D In             | ADC0 External Convert Start or IDA0 Update Source Input. |

| P0.7   | 19               | 14            | 12             | D I/O or<br>A In | Port 0.7.                                                |

| P1.0   | 18               | 13            | 11             | D I/O or<br>A In | Port 1.0.                                                |

| P1.1   | 17               | 12            | 10             | D I/O or<br>A In | Port 1.1.                                                |

| P1.2   | 16               | 11            | 9              | D I/O or<br>A In | Port 1.2.                                                |

| P1.3   | 15               | 10            | 8              | D I/O or<br>A In | Port 1.3.                                                |

| P1.4   | 14               | 9             |                | D I/O or<br>A In | Port 1.4.                                                |

| P1.5   | 11               | 8             |                | D I/O or<br>A In | Port 1.5.                                                |

| P1.6   | 10               | 7             |                | D I/O or<br>A In | Port 1.6.                                                |

| P1.7   | 9                | 6             |                | D I/O or<br>A In | Port 1.7.                                                |

| NC     | 1, 12, 13,<br>24 |               |                |                  | No Connection.                                           |

Table 3.1. Pin Definitions for the C8051F80x-83x (Continued)

#### **Table 7.6. Flash Electrical Characteristics**

| Parameter                                          | Conditions                            | Min   | Тур   | Max | Units  |  |  |  |

|----------------------------------------------------|---------------------------------------|-------|-------|-----|--------|--|--|--|

| Flash Size (Note 1)                                | C8051F80x and C8051F810/1             |       | 16384 |     | bytes  |  |  |  |

|                                                    | C8051F812/3/4/5/6/7/8/9 and C8051F82x |       | 8192  |     | bytes  |  |  |  |

|                                                    | C8051F830/1/2/3/4/5                   |       | 4096  |     | bytes  |  |  |  |

| Endurance (Erase/Write)                            |                                       | 10000 |       |     | cycles |  |  |  |

| Erase Cycle Time                                   | 25 MHz Clock                          | 15    | 20    | 26  | ms     |  |  |  |

| Write Cycle Time                                   | 25 MHz Clock                          | 15    | 20    | 26  | μs     |  |  |  |

| Clock Speed during Flash<br>Write/Erase Operations |                                       | 1     | —     | —   | MHz    |  |  |  |

| Note: Includes Security Lock By                    | Note: Includes Security Lock Byte.    |       |       |     |        |  |  |  |

#### Table 7.7. Internal High-Frequency Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions                                                       | Min | Тур  | Max | Units |

|---------------------------|------------------------------------------------------------------|-----|------|-----|-------|

| Oscillator Frequency      | IFCN = 11b                                                       | 24  | 24.5 | 25  | MHz   |

| Oscillator Supply Current | 25 °C, V <sub>DD</sub> = 3.0 V,<br>OSCICN.7 = 1,<br>OCSICN.5 = 0 |     | 350  | 650 | μA    |

#### **Table 7.8. Capacitive Sense Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified.

| Parameter                       | Conditions                                     | Min | Тур | Max | Units |

|---------------------------------|------------------------------------------------|-----|-----|-----|-------|

| Conversion Time                 | Single Conversion                              | 26  | 38  | 50  | μs    |

| Capacitance per Code            |                                                |     | 1   |     | fF    |

| External Capacitive Load        |                                                | —   | _   | 45  | pF    |

| Quantization Noise <sup>1</sup> | RMS                                            |     | 3   |     | fF    |

|                                 | Peak-to-Peak                                   | —   | 20  | —   | fF    |

| Supply Current                  | CS module bias current, 25 °C                  |     | 40  | 60  | μA    |

|                                 | CS module alone, maximum code<br>output, 25 °C | —   | 75  | 105 | μA    |

|                                 | Wake-on-CS Threshold <sup>2</sup> , 25 °C      | —   | 150 | 165 | μA    |

Notes:

1. RMS Noise is equivalent to one standard deviation. Peak-to-peak noise encompasses ±3.3 standard deviations.

2. Includes only current from regulator, CS module, and MCU in suspend mode.

## 8.1. Output Code Formatting

The ADC measures the input voltage with reference to GND. The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit. Conversion codes are represented as 10-bit unsigned integers. Inputs are measured from 0 to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to 0.

|                  | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 1023/1024 | 0x03FF                                       | 0xFFC0                                      |

| VREF x 512/1024  | 0x0200                                       | 0x8000                                      |

| VREF x 256/1024  | 0x0100                                       | 0x4000                                      |

| 0                | 0x0000                                       | 0x0000                                      |

### 8.2. 8-Bit Mode

Setting the ADC08BE bit in register ADC0CF to 1 will put the ADC in 8-bit mode. In 8-bit mode, only the 8 MSBs of data are converted, and the ADC0H register holds the results. The AD0LJST bit is ignored for 8-bit mode. 8-bit conversions take two fewer SAR clock cycles than 10-bit conversions, so the conversion is completed faster, and a 500 ksps sampling rate can be achieved with a slower SAR clock.

### 8.3. Modes of Operation

ADC0 has a maximum conversion speed of 500 ksps. The ADC0 conversion clock is a divided version of the system clock, determined by the AD0SC bits in the ADC0CF register.

#### 8.3.1. Starting a Conversion

A conversion can be initiated in one of six ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 1 overflow

- 5. A rising edge on the CNVSTR input signal

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2 is in 16-bit mode. See Section "28. Timers" on page 209 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as a Port I/O pin. When the CNVSTR input is used as the ADC0 conversion source, the associated pin should be skipped by the Digital Crossbar. See Section "23. Port Input/Output" on page 138 for details on Port I/O configuration.

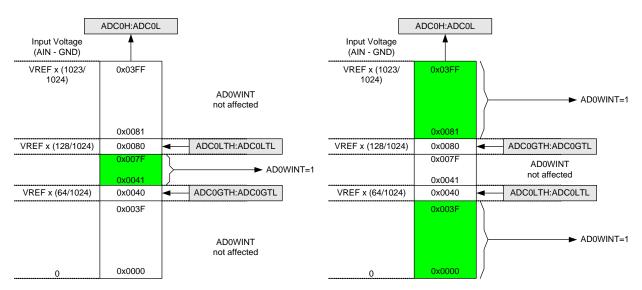

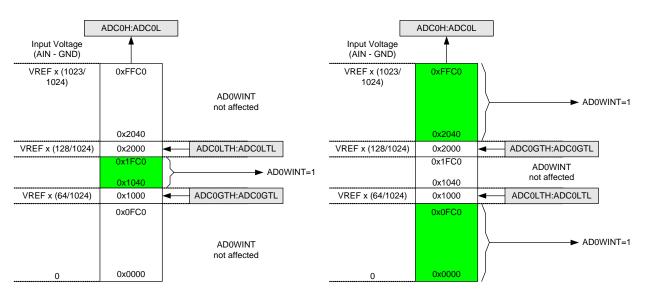

#### 8.4.1. Window Detector Example

Figure 8.4 shows two example window comparisons for right-justified data. with ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 8.5 shows an example using left-justified data with the same comparison values.

Figure 8.4. ADC Window Compare Example: Right-Justified Data

Figure 8.5. ADC Window Compare Example: Left-Justified Data

# 13. Capacitive Sense (CS0)

The Capacitive Sense subsystem included on the C8051F800/1/3/4/6/7/9, C8051F810/2/3/5/6/8/9, C8051F821/2/4/5/7/8, C8051F830/1/3/4 uses a capacitance-to-digital circuit to determine the capacitance on a port pin. The module can take measurements from different port pins using the module's analog multiplexer. The multiplexer supports up to 16 channels. See SFR Definition 13.9. "CSOMX: Capacitive Sense Mux Channel Select" on page 81 for channel availability for specific part numbers. The module is enabled only when the CS0EN bit (CS0CN) is set to 1. Otherwise the module is in a low-power shutdown state. The module can be configured to take measurements on one port pin or a group of port pins, using auto-scan. An accumulator can be configured to accumulate multiple conversions on an input channel. Interrupts can be generated when CS0 completes a conversion or when the measured value crosses a threshold defined in CS0THH:L.

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |

|-----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operations | S                                        | I     | I               |

| ADD A, Rn             | Add register to A                        | 1     | 1               |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                 | Increment A                              | 1     | 1               |

| INC Rn                | Increment register                       | 1     | 1               |

| INC direct            | Increment direct byte                    | 2     | 2               |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |

| DEC A                 | Decrement A                              | 1     | 1               |

| DEC Rn                | Decrement register                       | 1     | 1               |

| DEC direct            | Decrement direct byte                    | 2     | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |

| MUL AB                | Multiply A and B                         | 1     | 4               |

| DIV AB                | Divide A by B                            | 1     | 8               |

| DA A                  | Decimal adjust A                         | 1     | 1               |

| Logical Operations    | ,                                        |       |                 |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data     | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn             | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri            | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data          | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A         | Exclusive-OR A to direct byte            | 2     | 2               |

Table 14.1. CIP-51 Instruction Set Summary

# SFR Definition 18.5. EIP1: Extended Interrupt Priority 1

| Bit   | 7        | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|----------|----------|------|-------|-------|--------|------|-------|

| Name  | Reserved | Reserved | PCP0 | PPCA0 | PADC0 | PWADC0 | PMAT | PSMB0 |

| Туре  | W        | W        | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0        | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

SFR Address = 0xF3

| Bit | Name         | Function                                                                                                                                                     |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Reserved     | Must write 0.                                                                                                                                                |

| 5   | PCP0         | Comparator0 (CP0) Interrupt Priority Control.                                                                                                                |

|     |              | This bit sets the priority of the CP0 rising edge or falling edge interrupt.                                                                                 |

|     |              | 0: CP0 interrupt set to low priority level.                                                                                                                  |

|     |              | 1: CP0 interrupt set to high priority level.                                                                                                                 |

| 4   | PPCA0        | Programmable Counter Array (PCA0) Interrupt Priority Control.                                                                                                |

|     |              | This bit sets the priority of the PCA0 interrupt.                                                                                                            |

|     |              | 0: PCA0 interrupt set to low priority level.                                                                                                                 |

|     | <b>B4B00</b> | 1: PCA0 interrupt set to high priority level.                                                                                                                |

| 3   | PADC0        | ADC0 Conversion Complete Interrupt Priority Control.                                                                                                         |

|     |              | This bit sets the priority of the ADC0 Conversion Complete interrupt.                                                                                        |

|     |              | <ul><li>0: ADC0 Conversion Complete interrupt set to low priority level.</li><li>1: ADC0 Conversion Complete interrupt set to high priority level.</li></ul> |

| 2   | PWADC0       |                                                                                                                                                              |

| 2   | PWADCU       | ADC0 Window Comparator Interrupt Priority Control.<br>This bit sets the priority of the ADC0 Window interrupt.                                               |

|     |              | 0: ADC0 Window interrupt set to low priority level.                                                                                                          |

|     |              | 1: ADC0 Window interrupt set to high priority level.                                                                                                         |

| 1   | PMAT         | Port Match Interrupt Priority Control.                                                                                                                       |

|     | 1 101/31     | This bit sets the priority of the Port Match Event interrupt.                                                                                                |

|     |              | 0: Port Match interrupt set to low priority level.                                                                                                           |

|     |              | 1: Port Match interrupt set to high priority level.                                                                                                          |

| 0   | PSMB0        | SMBus (SMB0) Interrupt Priority Control.                                                                                                                     |

|     |              | This bit sets the priority of the SMB0 interrupt.                                                                                                            |

|     |              | 0: SMB0 interrupt set to low priority level.                                                                                                                 |

|     |              | 1: SMB0 interrupt set to high priority level.                                                                                                                |

## SFR Definition 21.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|---------|--------|--------|--------|--------|--------|--------|

| Name  | VDMEN  | VDDSTAT |        |        |        |        |        |        |

| Туре  | R/W    | R       | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies  | Varies | Varies | Varies | Varies | Varies | Varies |

#### SFR Address = 0xFF

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 21.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. After a power-on reset, the VDD monitor is enabled, and this bit will read 1. The state of this bit is sticky through any other reset source. 0: V <sub>DD</sub> Monitor Disabled. 1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.<br>1: $V_{DD}$ is above the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5:0 | Unused  | Read = Varies; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### 21.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Section "7. Electrical Characteristics" on page 39 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 21.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the MCD timeout, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

## SFR Definition 23.16. P2MDOUT: Port 2 Output Mode

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0          |

|-------|---|---|---|---|---|---|---|------------|

| Name  |   |   |   |   |   |   |   | P2MDOUT[0] |

| Туре  | R | R | R | R | R | R | R | R/W        |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0          |

SFR Address = 0xA6

| Bit | Name       | Function                                                      |

|-----|------------|---------------------------------------------------------------|

| 7:1 | Unused     | Read = 0000000b; Write = Don't Care                           |

| 0   | P2MDOUT[0] | Output Configuration Bits for P2.0.                           |

|     |            | 0: P2.0 Output is open-drain.<br>1: P2.0 Output is push-pull. |

## 24.3. Preparing for a CRC Calculation

To prepare CRC0 for a CRC calculation, software should select the desired polynomial and set the initial value of the result. Two polynomials are available: 0x1021 (16-bit) and 0x04C11DB7 (32-bit). The CRC0 result may be initialized to one of two values: 0x00000000 or 0xFFFFFFFF. The following steps can be used to initialize CRC0.

- 1. Select a polynomial (Set CRC0SEL to 0 for 32-bit or 1 for 16-bit).

- 2. Select the initial result value (Set CRC0VAL to 0 for 0x0000000 or 1 for 0xFFFFFFF).

- 3. Set the result to its initial value (Write 1 to CRC0INIT).

### 24.4. Performing a CRC Calculation

Once CRC0 is initialized, the input data stream is sequentially written to CRC0IN, one byte at a time. The CRC0 result is automatically updated after each byte is written. The CRC engine may also be configured to automatically perform a CRC on one or more Flash sectors. The following steps can be used to automatically perform a CRC on Flash memory.

- 1. Prepare CRC0 for a CRC calculation as shown above.

- 2. Write the index of the starting page to CRC0AUTO.

- 3. Set the AUTOEN bit in CRC0AUTO.

- 4. Write the number of Flash sectors to perform in the CRC calculation to CRC0CNT.

**Note:** Each Flash sector is 512 bytes.

- 5. Write any value to CRC0CN (or OR its contents with 0x00) to initiate the CRC calculation. The CPU will not execute code any additional code until the CRC operation completes.

- 6. Clear the AUTOEN bit in CRC0AUTO.

- 7. Read the CRC result using the procedure below.

### 24.5. Accessing the CRC0 Result

The internal CRC0 result is 32-bits (CRC0SEL = 0b) or 16-bits (CRC0SEL = 1b). The CRC0PNT bits select the byte that is targeted by read and write operations on CRC0DAT and increment after each read or write. The calculation result will remain in the internal CR0 result register until it is set, overwritten, or additional data is written to CRC0IN.

## SFR Definition 25.2. SPI0CN: SPI0 Control

| Bit   | 7    | 6    | 5    | 4      | 3    | 2      | 1     | 0     |

|-------|------|------|------|--------|------|--------|-------|-------|

| Name  | SPIF | WCOL | MODF | RXOVRN | NSSM | D[1:0] | TXBMT | SPIEN |

| Туре  | R/W  | R/W  | R/W  | R/W    | R/W  |        | R     | R/W   |

| Reset | 0    | 0    | 0    | 0      | 0    | 1      | 1     | 0     |

## SFR Address = 0xF8; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | SPI0 Interrupt Flag.                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit is set to logic 1 by hardware at the end of a data transfer. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                                                                                     |

| 6   | WCOL       | Write Collision Flag.                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This bit is set to logic 1 if a write to SPI0DAT is attempted when TXBMT is 0. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                       |

| 5   | MODF       | Mode Fault Flag.                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                             |

| 4   | RXOVRN     | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                         |

| 3:2 | NSSMD[1:0] | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | Selects between the following NSS operation modes:<br>(See Section 25.2 and Section 25.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |

| 1   | TXBMT      | Transmit Buffer Empty.                                                                                                                                                                                                                                                                                                                                                                       |

|     |            | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                              |

| 0   | SPIEN      | SPI0 Enable.                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | 0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                                          |

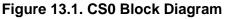

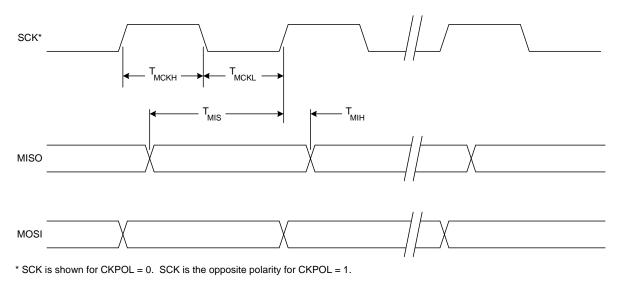

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## Figure 25.9. SPI Master Timing (CKPHA = 1)

| SMBCS1 | SMBCS0 | SMBus Clock Source         |

|--------|--------|----------------------------|

| 0      | 0      | Timer 0 Overflow           |

| 0      | 1      | Timer 1 Overflow           |

| 1      | 0      | Timer 2 High Byte Overflow |

| 1      | 1      | Timer 2 Low Byte Overflow  |

#### Table 26.1. SMBus Clock Source Selection

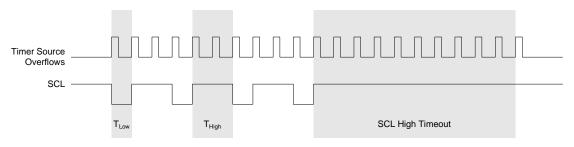

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 26.1. Note that the selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "28. Timers" on page 209.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

#### Equation 26.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 26.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 26.2.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

#### Equation 26.2. Typical SMBus Bit Rate

Figure 26.4 shows the typical SCL generation described by Equation 26.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 26.1.

Figure 26.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 26.2 shows the minimum setup.

# SFR Definition 28.6. TH0: Timer 0 High Byte

| Bit   | 7            | 6             | 5               | 4            | 3              | 2      | 1 | 0 |  |

|-------|--------------|---------------|-----------------|--------------|----------------|--------|---|---|--|

| Name  | ame TH0[7:0] |               |                 |              |                |        |   |   |  |

| Туре  | R/W          |               |                 |              |                |        |   |   |  |

| Rese  | <b>t</b> 0   | 0 0 0 0 0 0 0 |                 |              |                |        |   |   |  |

| SFR A | ddress = 0x8 | С             |                 |              |                |        |   |   |  |

| Bit   | Name         |               | Function        |              |                |        |   |   |  |

| 7:0   | TH0[7:0]     | Timer 0 Hig   | jh Byte.        |              |                |        |   |   |  |

|       |              | The TH0 reg   | gister is the l | high byte of | the 16-bit Tir | mer 0. |   |   |  |

# SFR Definition 28.7. TH1: Timer 1 High Byte

| Bit    | 7            | 6   | 5 | 4 | 3        | 2 | 1 | 0 |

|--------|--------------|-----|---|---|----------|---|---|---|

| Name   | TH1[7:0]     |     |   |   |          |   |   |   |

| Туре   |              | R/W |   |   |          |   |   |   |

| Reset  | 0            | 0   | 0 | 0 | 0        | 0 | 0 | 0 |

| SFR Ad | dress = 0x8l | )   |   |   |          |   |   |   |

| Bit    | Name         |     |   |   | Function |   |   |   |

| Bit | Name     | Function                                                 |  |  |  |  |

|-----|----------|----------------------------------------------------------|--|--|--|--|

| 7:0 | TH1[7:0] | Timer 1 High Byte.                                       |  |  |  |  |

|     |          | The TH1 register is the high byte of the 16-bit Timer 1. |  |  |  |  |

# SFR Definition 28.11. TMR2L: Timer 2 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR2L[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

# SFR Definition 28.12. TMR2H Timer 2 High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR2H[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xCD

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                                                                                   |

|     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |

## SFR Definition 29.1. PCA0CN: PCA0 Control

| Bit   | 7   | 6   | 5 | 4 | 3 | 2    | 1    | 0    |

|-------|-----|-----|---|---|---|------|------|------|

| Name  | CF  | CR  |   |   |   | CCF2 | CCF1 | CCF0 |

| Туре  | R/W | R/W | R | R | R | R/W  | R/W  | R/W  |

| Reset | 0   | 0   | 0 | 0 | 0 | 0    | 0    | 0    |

#### SFR Address = 0xD8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | CF     | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                                   |  |  |  |

|     |        | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000.<br>When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the<br>CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared<br>by hardware and must be cleared by software. |  |  |  |

| 6   | CR     | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                                     |  |  |  |

|     |        | This bit enables/disables the PCA Counter/Timer.                                                                                                                                                                                                                                                                   |  |  |  |

|     |        | 0: PCA Counter/Timer disabled.                                                                                                                                                                                                                                                                                     |  |  |  |

|     |        | 1: PCA Counter/Timer enabled.                                                                                                                                                                                                                                                                                      |  |  |  |

| 5:3 | Unused | Read = 000b, Write = Don't care.                                                                                                                                                                                                                                                                                   |  |  |  |

| 2   | CCF2   | PCA Module 2 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF2 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

| 1   | CCF1   | PCA Module 1 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF1 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

| 0   | CCF0   | PCA Module 0 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF0 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

# **DOCUMENT CHANGE LIST**

## **Revision 0.2 to Revision 1.0**

- Updated Electrical Specification Tables to reflect production characterization data.

- Added Minimum SYSCLK specification for writing or erasing Flash.

- Added caution for going into suspend with wake source active (Section 20.3)

- Corrected VDM0CN reset values to "Varies".

- Removed mention of IDAC in Pinout table.