Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Last Time Buy                                                  |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 16x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f802-gu |

# C8051F80x-83x

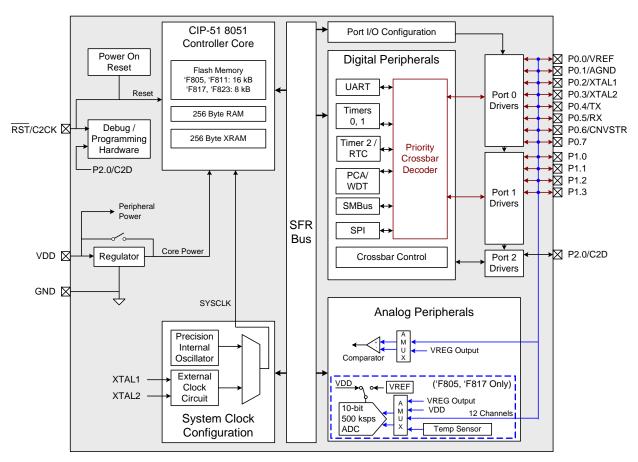

Figure 1.6. C8051F805, C8051F811, C8051F817, C8051F823 Block Diagram

## 10. Voltage and Ground Reference Options

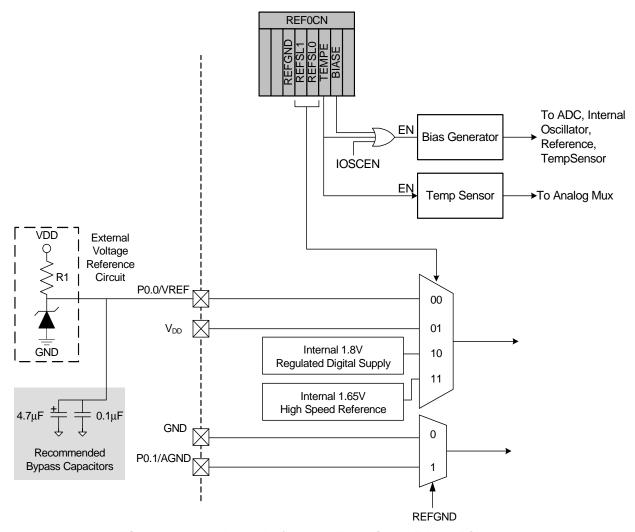

The voltage reference MUX is configurable to use an externally connected voltage reference, the on-chip voltage reference, or one of two power supply voltages (see Figure 10.1). The ground reference MUX allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (P0.1/AGND).

The voltage and ground reference options are configured using the REF0CN SFR described on page 62. Electrical specifications are can be found in the Electrical Specifications Chapter.

Important Note About the  $V_{REF}$  and AGND Inputs: Port pins are used as the external  $V_{REF}$  and AGND inputs. When using an external voltage reference, P0.0/VREF should be configured as an analog input and skipped by the Digital Crossbar. When using AGND as the ground reference to ADC0, P0.1/AGND should be configured as an analog input and skipped by the Digital Crossbar. Refer to Section "23. Port Input/Output" on page 138 for complete Port I/O configuration details. The external reference voltage must be within the range  $0 \le V_{REF} \le V_{DD}$  and the external ground reference must be at the same DC voltage potential as GND.

Figure 10.1. Voltage Reference Functional Block Diagram

#### 14. CIP-51 Microcontroller

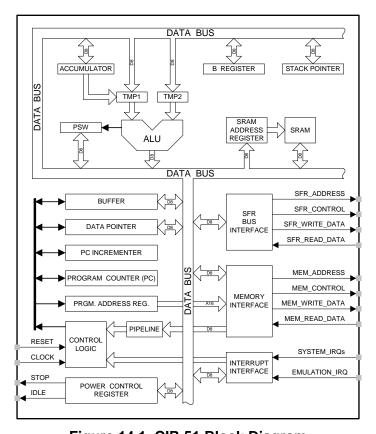

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51™ instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 30), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 14.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### **Performance**

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 14.1. CIP-51 Block Diagram

Table 14.1. CIP-51 Instruction Set Summary

| Mnemonic             | Description                              | Bytes | Clock<br>Cycles |  |

|----------------------|------------------------------------------|-------|-----------------|--|

| Arithmetic Operation | s                                        | 1     |                 |  |

| ADD A, Rn            | Add register to A                        | 1     | 1               |  |

| ADD A, direct        | DD A, direct Add direct byte to A        |       |                 |  |

| ADD A, @Ri           | Add indirect RAM to A                    | 1     | 2               |  |

| ADD A, #data         | Add immediate to A                       | 2     | 2               |  |

| ADDC A, Rn           | Add register to A with carry             | 1     | 1               |  |

| ADDC A, direct       | Add direct byte to A with carry          | 2     | 2               |  |

| ADDC A, @Ri          | Add indirect RAM to A with carry         | 1     | 2               |  |

| ADDC A, #data        | Add immediate to A with carry            | 2     | 2               |  |

| SUBB A, Rn           | Subtract register from A with borrow     | 1     | 1               |  |

| SUBB A, direct       | Subtract direct byte from A with borrow  | 2     | 2               |  |

| SUBB A, @Ri          | Subtract indirect RAM from A with borrow | 1     | 2               |  |

| SUBB A, #data        | Subtract immediate from A with borrow    | 2     | 2               |  |

| INC A                | Increment A                              | 1     | 1               |  |

| INC Rn               | Increment register                       | 1     | 1               |  |

| INC direct           | Increment direct byte                    | 2     | 2               |  |

| INC @Ri              | Increment indirect RAM                   | 1     | 2               |  |

| DEC A                | Decrement A                              | 1     | 1               |  |

| DEC Rn               | Decrement register                       | 1     | 1               |  |

| DEC direct           | Decrement direct byte                    | 2     | 2               |  |

| DEC @Ri              | Decrement indirect RAM                   | 1     | 2               |  |

| INC DPTR             | Increment Data Pointer                   | 1     | 1               |  |

| MUL AB               | Multiply A and B                         | 1     | 4               |  |

| DIV AB               | Divide A by B                            | 1     | 8               |  |

| DA A                 | Decimal adjust A                         | 1     | 1               |  |

| Logical Operations   | ,                                        |       | 1               |  |

| ANL A, Rn            | AND Register to A                        | 1     | 1               |  |

| ANL A, direct        | AND direct byte to A                     | 2     | 2               |  |

| ANL A, @Ri           | AND indirect RAM to A                    | 1     | 2               |  |

| ANL A, #data         | AND immediate to A                       | 2     | 2               |  |

| ANL direct, A        | AND A to direct byte                     | 2     | 2               |  |

| ANL direct, #data    | AND immediate to direct byte             | 3     | 3               |  |

| ORL A, Rn            | OR Register to A                         | 1     | 1               |  |

| ORL A, direct        | OR direct byte to A                      | 2     | 2               |  |

| ORL A, @Ri           | OR indirect RAM to A                     | 1     | 2               |  |

| ORL A, #data         | OR immediate to A                        | 2     | 2               |  |

| ORL direct, A        | OR A to direct byte                      | 2     | 2               |  |

| ORL direct, #data    | OR immediate to direct byte              | 3     | 3               |  |

| XRL A, Rn            | Exclusive-OR Register to A               | 1     | 1               |  |

| XRL A, direct        | Exclusive-OR direct byte to A            | 2     | 2               |  |

| XRL A, @Ri           | Exclusive-OR indirect RAM to A           | 1     | 2               |  |

| XRL A, #data         | Exclusive-OR immediate to A              | 2     | 2               |  |

| XRL direct, A        | Exclusive-OR A to direct byte            | 2     | 2               |  |

# SFR Definition 14.5. B: B Register

| Bit   | 7      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------|-----|---|---|---|---|---|---|--|

| Name  | B[7:0] |     |   |   |   |   |   |   |  |

| Туре  |        | R/W |   |   |   |   |   |   |  |

| Reset | 0      | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

### SFR Address = 0xF0; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

# C8051F80x-83x

## **Table 17.2. Special Function Registers (Continued)**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register   | Address | Description                       | Page |

|------------|---------|-----------------------------------|------|

| P1MAT      | 0xED    | P1 Match                          | 152  |

| P1MDIN     | 0xF2    | Port 1 Input Mode Configuration   | 156  |

| P1MDOUT    | 0xA5    | Port 1 Output Mode Configuration  | 156  |

| P1SKIP     | 0xD5    | Port 1 Skip                       | 157  |

| P2         | 0xA0    | Port 2 Latch                      | 157  |

| P2MDOUT    | 0xA6    | Port 2 Output Mode Configuration  | 158  |

| PCA0CN     | 0xD8    | PCA Control                       | 238  |

| PCA0CPH0   | 0xFC    | PCA Capture 0 High                | 243  |

| PCA0CPH1   | 0xEA    | PCA Capture 1 High                | 243  |

| PCA0CPH2   | 0xEC    | PCA Capture 2 High                | 243  |

| PCA0CPL0   | 0xFB    | PCA Capture 0 Low                 | 243  |

| PCA0CPL1   | 0xE9    | PCA Capture 1 Low                 | 243  |

| PCA0CPL2   | 0xEB    | PCA Capture 2 Low                 | 243  |

| PCA0CPM0   | 0xDA    | PCA Module 0 Mode Register        | 241  |

| PCA0CPM1   | 0xDB    | PCA Module 1 Mode Register        | 241  |

| PCA0CPM2   | 0xDC    | PCA Module 2 Mode Register        | 241  |

| PCA0H      | 0xFA    | PCA Counter High                  | 242  |

| PCA0L      | 0xF9    | PCA Counter Low                   | 242  |

| PCA0MD     | 0xD9    | PCA Mode                          | 239  |

| PCA0PWM    | 0xF7    | PCA PWM Configuration             | 240  |

| PCON       | 0x87    | Power Control                     | 122  |

| PSCTL      | 0x8F    | Program Store R/W Control         | 118  |

| PSW        | 0xD0    | Program Status Word               | 91   |

| REF0CN     | 0xD1    | Voltage Reference Control         | 62   |

| REG0CN     | 0xC9    | Voltage Regulator Control         | 64   |

| REVID 0xB6 |         | Revision ID                       | 96   |

| RSTSRC     | 0xEF    | Reset Source Configuration/Status | 128  |

## SFR Definition 18.4. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|-------|---|---|---|---|---|---|--------|--------|

| Name  |   |   |   |   |   |   | ECSGRT | ECSCPT |

| Туре  | R | R | R | R | R | R | R/W    | R/W    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

### SFR Address = 0xE7

| Bit | Name   | Function                                                       |

|-----|--------|----------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b; Write = don't care.                            |

| 1   | ECSGRT | Enable Capacitive Sense Greater Than Comparator Interrupt.     |

|     |        | 0: Disable Capacitive Sense Greater Than Comparator interrupt. |

|     |        | 1: Enable interrupt requests generated by CS0CMPF.             |

| 0   | ECSCPT | Enable Capacitive Sense Conversion Complete Interrupt.         |

|     |        | 0: Disable Capacitive Sense Conversion Complete interrupt.     |

|     |        | 1: Enable interrupt requests generated by CS0INT.              |

# SFR Definition 19.2. FLKEY: Flash Lock and Key

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|-----|---|---|---|---|---|---|--|

| Name  | FLKEY[7:0] |     |   |   |   |   |   |   |  |

| Type  |            | R/W |   |   |   |   |   |   |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

### SFR Address = 0xB7

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY[7:0] | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |            | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This register provides a lock and key function for Flash erasures and writes. Flash writes and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY register. Flash writes and erases are automatically disabled after the next write or erase is complete. If any writes to FLKEY are performed incorrectly, or if a Flash write or erase operation is attempted while these operations are disabled, the Flash will be permanently |

|     |            | locked from writes or erasures until the next device reset. If an application never writes to Flash, it can intentionally lock the Flash by writing a non-0xA5 value to FLKEY from software.                                                                                                                                                                                                                                                     |

|     |            | Read:                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |            | When read, bits 1–0 indicate the current Flash lock state.                                                                                                                                                                                                                                                                                                                                                                                       |

|     |            | 00: Flash is write/erase locked.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | 01: The first key code has been written (0xA5).                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | 10: Flash is unlocked (writes/erases allowed).                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | 11: Flash writes/erases disabled until the next reset.                                                                                                                                                                                                                                                                                                                                                                                           |

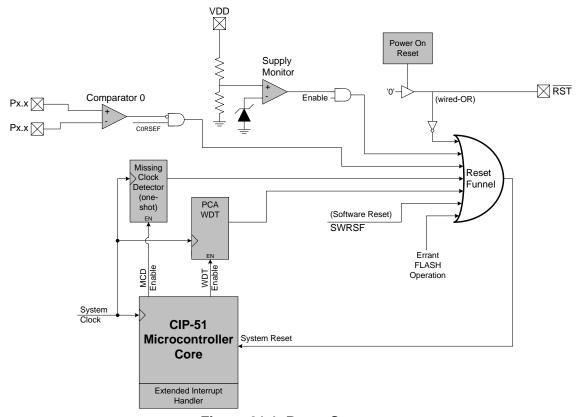

#### 21. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For V<sub>DD</sub> Monitor and power-on resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 21.1. Reset Sources

## SFR Definition 21.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | C0RSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

### SFR Address = 0xEF

| Bit   | Name       | Description                                                                                    | Write                                                                                                                                                                           | Read                                                                                                                                           |

|-------|------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                        | Don't care.                                                                                                                                                                     | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                        | N/A                                                                                                                                                                             | Set to 1 if Flash read/write/erase error caused the last reset.                                                                                |

| 5     | C0RSEF     | Comparator0 Reset Enable and Flag.                                                             | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                           | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                                 | Writing a 1 forces a system reset.                                                                                                                                              | Set to 1 if last reset was caused by a write to SWRSF.                                                                                         |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                             | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the Missing Clock Detector. The MCD triggers a reset if a missing clock condition is detected.                                                              | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the V <sub>DD</sub> monitor as a reset source. Writing 1 to this bit before the V <sub>DD</sub> monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                             | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                           | s register                                                                                                                                                                      | 1                                                                                                                                              |

#### 22.3. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 22.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 22.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 22.4).

Important Note on External Oscillator Usage: Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "23.3. Priority Crossbar Decoder" on page 143 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as analog inputs. In CMOS clock mode, the associated pin should be configured as a digital input. See Section "23.4. Port I/O Initialization" on page 147 for details on Port input mode selection.

## **SFR Definition 22.4. OSCXCN: External Oscillator Control**

| Bit   | 7      | 6           | 5   | 4 | 3 | 2 | 1         | 0 |

|-------|--------|-------------|-----|---|---|---|-----------|---|

| Name  | XTLVLD | XOSCMD[2:0] |     |   |   |   | XFCN[2:0] |   |

| Туре  | R      |             | R/W |   |   |   | R/W       |   |

| Reset | 0      | 0           | 0   | 0 | 0 | 0 | 0         | 0 |

SFR Address = 0xB1

| Bit | Name        |          |                                                                                                            | Function                   |                 |  |  |  |  |  |

|-----|-------------|----------|------------------------------------------------------------------------------------------------------------|----------------------------|-----------------|--|--|--|--|--|

| 7   | XTLVLD      | Crystal  | Oscillator Valid Flag.                                                                                     |                            |                 |  |  |  |  |  |

|     |             | (Read o  | nly when XOSCMD = 11                                                                                       | x.)                        |                 |  |  |  |  |  |

|     |             | -        | al Oscillator is unused or                                                                                 | •                          |                 |  |  |  |  |  |

|     |             | 1: Cryst | : Crystal Oscillator is running and stable.                                                                |                            |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa  | External Oscillator Mode Select.                                                                           |                            |                 |  |  |  |  |  |

|     |             |          | ternal Oscillator circuit of                                                                               | • •                        |                 |  |  |  |  |  |

|     |             |          | ternal CMOS Clock Mode                                                                                     |                            |                 |  |  |  |  |  |

|     |             |          | ternal CMOS Clock Mode                                                                                     | e with divide by 2 stage.  |                 |  |  |  |  |  |

|     |             |          | Oscillator Mode.                                                                                           |                            |                 |  |  |  |  |  |

|     |             |          | O1: Capacitor Oscillator Mode.                                                                             |                            |                 |  |  |  |  |  |

|     |             |          | <ul><li>10: Crystal Oscillator Mode.</li><li>11: Crystal Oscillator Mode with divide by 2 stage.</li></ul> |                            |                 |  |  |  |  |  |

| 3   | Unused      | Read =   | Read = 0; Write = Don't Care                                                                               |                            |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | Externa  | I Oscillator Frequency                                                                                     | Control Bits.              |                 |  |  |  |  |  |

|     |             | Set acc  | ording to the desired freq                                                                                 | juency for Crystal or RC r | node.           |  |  |  |  |  |

|     |             | Set acc  | ording to the desired K F                                                                                  | actor for C mode.          |                 |  |  |  |  |  |

|     |             | XFCN     | Crystal Mode                                                                                               | RC Mode                    | C Mode          |  |  |  |  |  |

|     |             | 000      | f ≤ 32 kHz                                                                                                 | f ≤ 25 kHz                 | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001      | 32 kHz < f ≤ 84 kHz                                                                                        | 25 kHz < f ≤ 50 kHz        | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010      | 84 kHz < f ≤ 225 kHz                                                                                       | 50 kHz < f ≤ 100 kHz       | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011      | 011 225 kHz < f ≤ 590 kHz 100 kHz < f ≤ 200 kHz K Factor = 22                                              |                            |                 |  |  |  |  |  |

|     |             | 100      | 590 kHz < f ≤ 1.5 MHz                                                                                      | 200 kHz < f ≤ 400 kHz      | K Factor = 65   |  |  |  |  |  |

|     |             | 101      | 1.5 MHz < f ≤ 4 MHz                                                                                        | 400 kHz < f ≤ 800 kHz      | K Factor = 180  |  |  |  |  |  |

|     |             | 110      | 4 MHz < f ≤ 10 MHz                                                                                         | 800 kHz < f ≤ 1.6 MHz      | K Factor = 664  |  |  |  |  |  |

|     |             | 111      | 10 MHz < f ≤ 30 MHz                                                                                        | 1.6 MHz $< f \le 3.2$ MHz  | K Factor = 1590 |  |  |  |  |  |

## SFR Definition 23.14. P1SKIP: Port 1 Skip

| Bit   | 7  | 6           | 5  | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|----|-------------|----|----|---|---|---|---|--|--|

| Name  |    | P1SKIP[7:0] |    |    |   |   |   |   |  |  |

| Туре  |    | R/W         |    |    |   |   |   |   |  |  |

| Reset | 0* | 0*          | 0* | 0* | 0 | 0 | 0 | 0 |  |  |

### SFR Address = 0xD5

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                                                                                    |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.  0: Corresponding P1.n pin is not skipped by the Crossbar.  1: Corresponding P1.n pin is skipped by the Crossbar.  Note: P1.4–P1.7 are not available on 16-pin packages, with the reset value of 1111b for P1SKIP[7:4]. |

## SFR Definition 23.15. P2: Port 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|-------|---|---|---|---|---|---|---|-------|

| Name  |   |   |   |   |   |   |   | P2[0] |

| Туре  | R | R | R | R | R | R | R | R/W   |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1     |

### SFR Address = 0xA0; Bit-Addressable

| Bit | Name   | Description                                                                                                              | Write                                                              | Read                                                                    |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:1 | Unused | Unused.                                                                                                                  | Don't Care                                                         | 0000000b                                                                |

| 0   | P2[0]  | Port 2 Data. Sets the Port latch logic value or reads the Port pin logic state in Port cells configured for digital I/O. | O: Set output latch to logic LOW.  Set output latch to logic HIGH. | 0: P2.0 Port pin is logic<br>LOW.<br>1: P2.0 Port pin is logic<br>HIGH. |

## C8051F80x-83x

### 24.3. Preparing for a CRC Calculation

To prepare CRC0 for a CRC calculation, software should select the desired polynomial and set the initial value of the result. Two polynomials are available: 0x1021 (16-bit) and 0x04C11DB7 (32-bit). The CRC0 result may be initialized to one of two values: 0x00000000 or 0xFFFFFFFF. The following steps can be used to initialize CRC0.

- 1. Select a polynomial (Set CRC0SEL to 0 for 32-bit or 1 for 16-bit).

- 2. Select the initial result value (Set CRC0VAL to 0 for 0x00000000 or 1 for 0xFFFFFFF).

- 3. Set the result to its initial value (Write 1 to CRC0INIT).

#### 24.4. Performing a CRC Calculation

Once CRC0 is initialized, the input data stream is sequentially written to CRC0IN, one byte at a time. The CRC0 result is automatically updated after each byte is written. The CRC engine may also be configured to automatically perform a CRC on one or more Flash sectors. The following steps can be used to automatically perform a CRC on Flash memory.

- 1. Prepare CRC0 for a CRC calculation as shown above.

- 2. Write the index of the starting page to CRC0AUTO.

- 3. Set the AUTOEN bit in CRC0AUTO.

- 4. Write the number of Flash sectors to perform in the CRC calculation to CRC0CNT.

Note: Each Flash sector is 512 bytes.

- 5. Write any value to CRC0CN (or OR its contents with 0x00) to initiate the CRC calculation. The CPU will not execute code any additional code until the CRC operation completes.

- 6. Clear the AUTOEN bit in CRC0AUTO.

- 7. Read the CRC result using the procedure below.

### 24.5. Accessing the CRC0 Result

The internal CRC0 result is 32-bits (CRC0SEL = 0b) or 16-bits (CRC0SEL = 1b). The CRC0PNT bits select the byte that is targeted by read and write operations on CRC0DAT and increment after each read or write. The calculation result will remain in the internal CR0 result register until it is set, overwritten, or additional data is written to CRC0IN.

## SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|----------|---|---|---|---|---|---|--|--|

| Name  |   | SCR[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W      |   |   |   |   |   |   |  |  |

| Reset | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

### SFR Address = 0xA2

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0 | SCR[7:0] | SPI0 Clock Rate.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|     |          | These bits determine the frequency of the SCK output when the SPI0 module is configured for master mode operation. The SCK clock frequency is a divided version of the system clock, and is given in the following equation, where SYSCLK is the system clock frequency and SPI0CKR is the 8-bit value held in the SPI0CKR register. |  |  |  |  |

|     |          | $f_{SCK} = \frac{SYSCLK}{2 \times (SPIOCKR[7:0] + 1)}$                                                                                                                                                                                                                                                                               |  |  |  |  |

|     |          | for 0 <= SPI0CKR <= 255                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|     |          | Example: If SYSCLK = 2 MHz and SPI0CKR = 0x04,                                                                                                                                                                                                                                                                                       |  |  |  |  |

|     |          | $f_{SCK} = \frac{2000000}{2 \times (4+1)}$                                                                                                                                                                                                                                                                                           |  |  |  |  |

|     |          | $f_{SCK} = 200kHz$                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

## SFR Definition 25.4. SPI0DAT: SPI0 Data

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|--------------|---|---|---|---|---|---|--|--|

| Name  |   | SPI0DAT[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W          |   |   |   |   |   |   |  |  |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0xA3

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

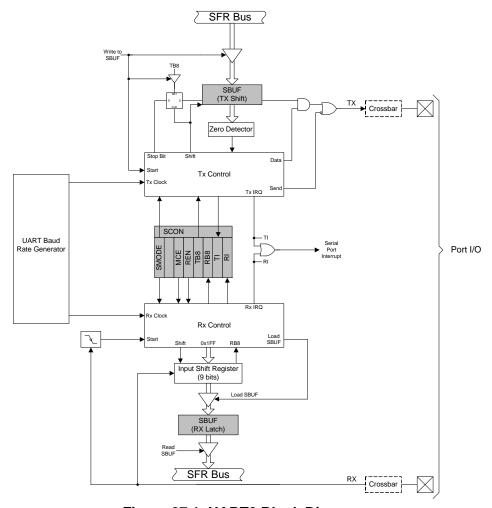

#### 27. UARTO

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "27.1. Enhanced Baud Rate Generation" on page 202). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. **Writes to SBUF0** always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 27.1. UARTO Block Diagram

Table 27.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHz Oscillator

|                    |                              | Frequency: 24.5 MHz  |                                |                       |                                                 |                  |                                  |  |  |  |

|--------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|

|                    | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |

|                    | 230400                       | -0.32%               | 106                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |  |  |  |

| ٠. ع               | 115200                       | -0.32%               | 212                            | SYSCLK                | XX                                              | 1                | 0x96                             |  |  |  |

| from<br>Osc.       | 57600                        | 0.15%                | 426                            | SYSCLK                | XX                                              | 1                | 0x2B                             |  |  |  |

|                    | 28800                        | -0.32%               | 848                            | SYSCLK/4              | 01                                              | 0                | 0x96                             |  |  |  |

| rns                | 14400                        | 0.15%                | 1704                           | SYSCLK/12             | 00                                              | 0                | 0xB9                             |  |  |  |

| SYSCLK<br>Internal | 9600                         | -0.32%               | 2544                           | SYSCLK/12             | 00                                              | 0                | 0x96                             |  |  |  |

| ა <u>−</u>         | 2400                         | -0.32%               | 10176                          | SYSCLK/48             | 10                                              | 0                | 0x96                             |  |  |  |

|                    | 1200                         | 0.15%                | 20448                          | SYSCLK/48             | 10                                              | 0                | 0x2B                             |  |  |  |

#### Notes:

- 1. SCA1-SCA0 and T1M bit definitions can be found in Section 28.1.

- 2. X = Don't care.

Table 27.2. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz Oscillator

|                    |                              |                      | Frequ                          | uency: 22.1184        | MHz                                             |                  |                                  |

|--------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                    | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                    | 230400                       | 0.00%                | 96                             | SYSCLK                | XX²                                             | 1                | 0xD0                             |

| ٠: ع               | 115200                       | 0.00%                | 192                            | SYSCLK                | XX                                              | 1                | 0xA0                             |

| from<br>Osc.       | 57600                        | 0.00%                | 384                            | SYSCLK                | XX                                              | 1                | 0x40                             |

| κ<br>F             | 28800                        | 0.00%                | 768                            | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| SYSCLK<br>External | 14400                        | 0.00%                | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| SYSC<br>Exter      | 9600                         | 0.00%                | 2304                           | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| S III              | 2400                         | 0.00%                | 9216                           | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

|                    | 1200                         | 0.00%                | 18432                          | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

| <b>L</b> .         | 230400                       | 0.00%                | 96                             | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |

| from<br>Osc.       | 115200                       | 0.00%                | 192                            | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |

| K fr               | 57600                        | 0.00%                | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

| CL<br>rna          | 28800                        | 0.00%                | 768                            | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |

| SYSCLK<br>Internal | 14400                        | 0.00%                | 1536                           | EXTCLK / 8            | 11                                              | 0                | 0xA0                             |

| S                  | 9600                         | 0.00%                | 2304                           | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

#### Notes:

208

- 1. SCA1–SCA0 and T1M bit definitions can be found in Section 28.1.

- 2. X = Don't care.

## SFR Definition 28.2. TCON: Timer Control

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name  | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| Туре  | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0x88; Bit-Addressable

| Bit | Name | Function                                                                                                                                                                                                                                                      |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag.                                                                                                                                                                                                                                        |

|     |      | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                 |

| 6   | TR1  | Timer 1 Run Control.                                                                                                                                                                                                                                          |

|     |      | Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                                                  |

| 5   | TF0  | Timer 0 Overflow Flag.                                                                                                                                                                                                                                        |

|     |      | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                 |

| 4   | TR0  | Timer 0 Run Control.                                                                                                                                                                                                                                          |

|     |      | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                  |

| 3   | IE1  | External Interrupt 1.                                                                                                                                                                                                                                         |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                       |

| 2   | IT1  | Interrupt 1 Type Select.                                                                                                                                                                                                                                      |

|     |      | This bit selects whether the configured /INT1 interrupt will be edge or level sensitive. /INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see SFR Definition 18.7).  0: /INT1 is level triggered.  1: /INT1 is edge triggered. |

| 1   | IE0  | External Interrupt 0.                                                                                                                                                                                                                                         |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                       |

| 0   | IT0  | Interrupt 0 Type Select.                                                                                                                                                                                                                                      |

|     |      | This bit selects whether the configured INT0 interrupt will be edge or level sensitive. INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR Definition 18.7).  0: INT0 is level triggered.  1: INT0 is edge triggered.         |

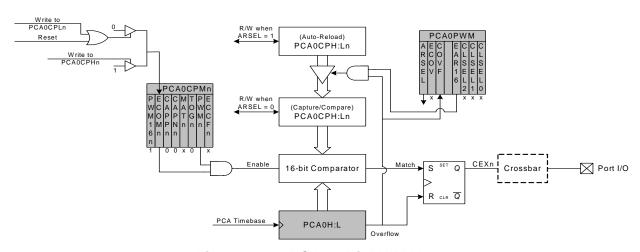

#### 29.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8-bit through 15-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register.

The duty cycle of the PWM output signal can be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0. This synchronous update feature allows software to asynchronously write a new PWM high time, which will then take effect on the following PWM period.

For backwards-compatibility with the 16-bit PWM mode available on other devices, the PWM duty cycle can also be changed without using the "Auto-Reload" register. To output a varying duty cycle without using the "Auto-Reload" register, new value writes should be synchronized with PCA CCFn match interrupts. Match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 29.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(65536 - PCA0CPn)}{65536}$$

#### Equation 29.4. 16-Bit PWM Duty Cycle

Using Equation 29.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 29.10. PCA 16-Bit PWM Mode

### 30. C2 Interface

C8051F80x-83x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface operates using only two pins: a bi-directional data signal (C2D), and a clock input (C2CK). See the C2 Interface Specification for details on the C2 protocol.

#### 30.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming functions through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

### C2 Register Definition 30.1. C2ADD: C2 Address

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | C2ADD[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit   | Name                                                                                                    | Function                                                                                                                         |                                                     |                                                   |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------|--|--|--|--|

| 7:0   | C2ADD[7:0]                                                                                              | C2 Address.                                                                                                                      |                                                     |                                                   |  |  |  |  |

|       |                                                                                                         | The C2ADD register is accessed via the C2 interface to select the target Data register for C2 Data Read and Data Write commands. |                                                     |                                                   |  |  |  |  |

|       |                                                                                                         | Address                                                                                                                          | Name Description                                    |                                                   |  |  |  |  |

|       |                                                                                                         | 0x00                                                                                                                             | DEVICEID Selects the Device ID Register (read only) |                                                   |  |  |  |  |

|       |                                                                                                         | 0x01                                                                                                                             | REVID                                               | Selects the Revision ID Register (read only)      |  |  |  |  |

|       |                                                                                                         | 0x02                                                                                                                             | FPCTL                                               | Selects the C2 Flash Programming Control Register |  |  |  |  |

|       |                                                                                                         | 0xBF                                                                                                                             | FPDAT                                               | Selects the C2 Flash Data Register                |  |  |  |  |

|       |                                                                                                         | 0xD2                                                                                                                             | CRC0AUTO*                                           | Selects the CRC0AUTO Register                     |  |  |  |  |

|       |                                                                                                         | 0xD3                                                                                                                             | CRC0CNT*                                            | Selects the CRC0CNT Register                      |  |  |  |  |

|       |                                                                                                         | 0xCE                                                                                                                             | CRC0CN*                                             | Selects the CRC0CN Register                       |  |  |  |  |

|       |                                                                                                         | 0xDE                                                                                                                             | CRC0DATA*                                           | Selects the CRC0DATA Register                     |  |  |  |  |

|       |                                                                                                         | 0xCF                                                                                                                             | CRC0FLIP*                                           | Selects the CRC0FLIP Register                     |  |  |  |  |

|       |                                                                                                         | 0xDD                                                                                                                             | CRC0IN*                                             | Selects the CRC0IN Register                       |  |  |  |  |

| *Note | Note: CRC registers and functions are described in Section "24. Cyclic Redundancy Check Unit (CRC0)" on |                                                                                                                                  |                                                     |                                                   |  |  |  |  |

Note: CRC registers and functions are described in Section "24. Cyclic Redundancy Check Unit (CRC0)" or page 159.