# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f803-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 26.4.4. Data Register                                     |             |

|-----------------------------------------------------------|-------------|

| 26.5. SMBus Transfer Modes                                |             |

| 26.5.1. Write Sequence (Master)                           |             |

| 26.5.2. Read Sequence (Master)                            | 194         |

| 26.5.3. Write Sequence (Slave)                            | 195         |

| 26.5.4. Read Sequence (Slave)                             | 196         |

| 26.6. SMBus Status Decoding                               | 196         |

| 27. UART0                                                 |             |

| 27.1. Enhanced Baud Rate Generation                       | 202         |

| 27.2. Operational Modes                                   | 203         |

| 27.2.1. 8-Bit UART                                        |             |

| 27.2.2. 9-Bit UART                                        | 204         |

| 27.3. Multiprocessor Communications                       | 205         |

| 28. Timers                                                |             |

| 28.1. Timer 0 and Timer 1                                 |             |

| 28.1.1. Mode 0: 13-bit Counter/Timer                      |             |

| 28.1.2. Mode 1: 16-bit Counter/Timer                      |             |

| 28.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload      |             |

| 28.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)   |             |

| 28.2. Timer 2                                             |             |

| 28.2.1. 16-bit Timer with Auto-Reload                     |             |

| 28.2.2. 8-bit Timers with Auto-Reload                     |             |

| 29. Programmable Counter Array                            |             |

| 29.1. PCA Counter/Timer                                   |             |

| 29.2. PCA0 Interrupt Sources                              |             |

| 29.3. Capture/Compare Modules                             |             |

| 29.3.1. Edge-Triggered Capture Mode                       |             |

| 29.3.2. Software Timer (Compare) Mode                     |             |

| 29.3.3. High-Speed Output Mode                            |             |

| 29.3.4. Frequency Output Mode                             |             |

| 29.3.5. 8-bit through 15-bit Pulse Width Modulator Modes  |             |

| 29.3.5.1. 8-bit Pulse Width Modulator Mode                |             |

| 29.3.5.2. 9-bit through 15-bit Pulse Width Modulator Mode |             |

| 29.3.6. 16-Bit Pulse Width Modulator Mode                 |             |

| 29.4. Watchdog Timer Mode                                 |             |

| 29.4.1. Watchdog Timer Operation                          |             |

| 29.4.2. Watchdog Timer Usage                              |             |

| 29.5. Register Descriptions for PCA0                      |             |

|                                                           |             |

| <b>30. C2 Interface</b>                                   |             |

|                                                           |             |

| 30.2. C2CK Pin Sharing                                    |             |

| Document Change List                                      |             |

| Contact Information                                       | <b>Z</b> 00 |

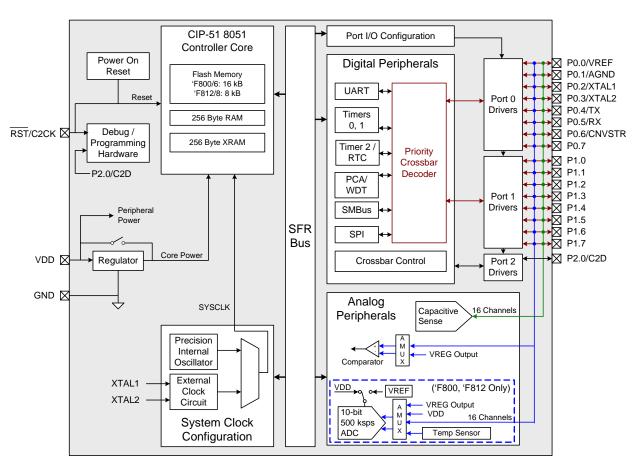

Figure 1.1. C8051F800, C8051F806, C8051F812, C8051F818 Block Diagram

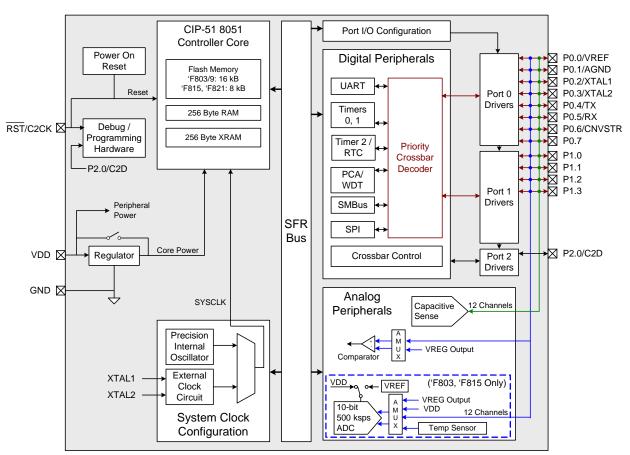

Figure 1.4. C8051F803, C8051F809, C8051F815, C8051F821 Block Diagram

The Comparator response time may be configured in software via the CPT0MD register (see SFR Definition 12.2). Selecting a longer response time reduces the Comparator supply current.

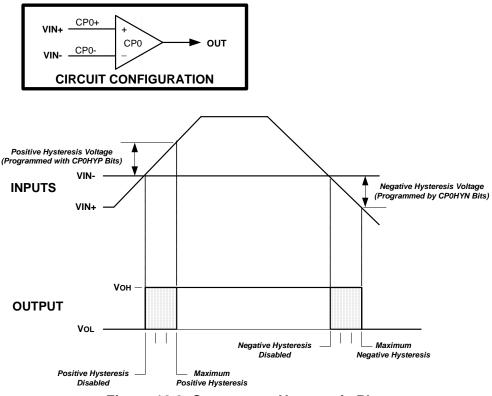

Figure 12.2. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via its Comparator Control register CPT0CN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using bits 3:0 in the Comparator Control Register CPT0CN (shown in SFR Definition 12.1). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Figure 12.2, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section "18.1. MCU Interrupt Sources and Vectors" on page 103). The CP0FIF flag is set to logic 1 upon a Comparator falling-edge occurrence, and the CP0RIF flag is set to logic 1 upon the Comparator rising-edge occurrence. Once set, these bits remain set until cleared by software. The Comparator rising-edge interrupt mask is enabled by setting CP0RIE to a logic 1. The Comparator0 falling-edge interrupt mask is enabled by setting CP0FIE to a logic 1.

The output state of the Comparator can be obtained at any time by reading the CP0OUT bit. The Comparator is enabled by setting the CP0EN bit to logic 1, and is disabled by clearing this bit to logic 0.

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

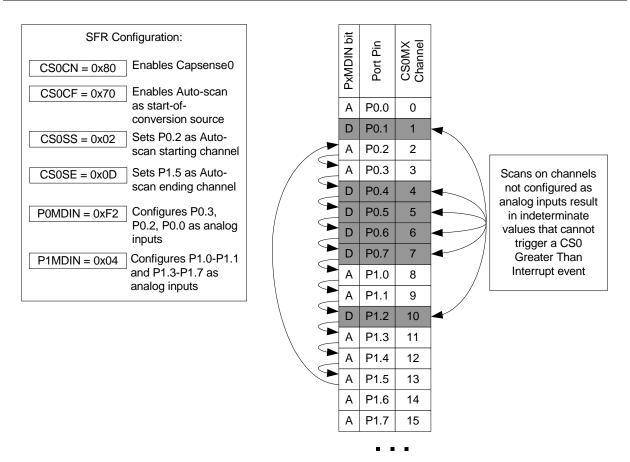

Figure 13.2. Auto-Scan Example

### 13.4. CS0 Comparator

The CS0 comparator compares the latest capacitive sense conversion result with the value stored in CS0THH:CS0THL. If the result is less than or equal to the stored value, the CS0CMPF bit(CS0CN:0) is set to 0. If the result is greater than the stored value, CS0CMPF is set to 1.

If the CS0 conversion accumulator is configured to accumulate multiple conversions, a comparison will not be made until the last conversion has been accumulated.

An interrupt will be generated if CS0 greater-than comparator interrupts are enabled by setting the ECS-GRT bit (EIE2.1) when the comparator sets CS0CMPF to 1.

If auto-scan is running when the comparator sets the CS0CMPF bit, no further auto-scan initiated conversions will start until firmware sets CS0BUSY to 1.

A CS0 greater-than comparator event can wake a device from suspend mode. This feature is useful in systems configured to continuously sample one or more capacitive sense channels. The device will remain in the low-power suspend state until the captured value of one of the scanned channels causes a CS0 greater-than comparator event to occur. It is not necessary to have CS0 comparator interrupts enabled in order to wake a device from suspend with a greater-than event.

**Note:** On waking from suspend mode due to a CS0 greater-than comparator event, the CS0CN register should be accessed only after at least two system clock cycles have elapsed.

For a summary of behavior with different CS0 comparator, auto-scan, and auto accumulator settings, please see Table 13.1.

## Table 17.2. Special Function Registers (Continued)

| Register | Address | Description                      | Page |

|----------|---------|----------------------------------|------|

| CS0CF    | 0x9E    | CS0 Configuration                | 76   |

| CSOMX    | 0x9C    | CS0 Mux                          | 81   |

| CS0SE    | 0xBA    | Auto Scan End Channel            | 78   |

| CS0SS    | 0xB9    | Auto Scan Start Channel          | 78   |

| DERIVID  | 0xAD    | Derivative Identification        | 96   |

| DPH      | 0x83    | Data Pointer High                | 88   |

| DPL      | 0x82    | Data Pointer Low                 | 88   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1      | 107  |

| EIE2     | 0xE7    | Extended Interrupt Enable 2      | 108  |

| EIP1     | 0xF3    | Extended Interrupt Priority 1    | 109  |

| EIP2     | 0xF4    | Extended Interrupt Priority 2    | 110  |

| FLKEY    | 0xB7    | Flash Lock And Key               | 119  |

| HWID     | 0xB5    | Hardware Identification          | 95   |

| IE       | 0xA8    | Interrupt Enable                 | 105  |

| IP       | 0xB8    | Interrupt Priority               | 106  |

| IT01CF   | 0xE4    | INT0/INT1 Configuration          | 112  |

| OSCICL   | 0xB3    | Internal Oscillator Calibration  | 131  |

| OSCICN   | 0xB2    | Internal Oscillator Control      | 132  |

| OSCXCN   | 0xB1    | External Oscillator Control      | 134  |

| P0       | 0x80    | Port 0 Latch                     | 153  |

| POMASK   | 0xFE    | Port 0 Mask                      | 151  |

| POMAT    | 0xFD    | Port 0 Match                     | 151  |

| POMDIN   | 0xF1    | Port 0 Input Mode Configuration  | 154  |

| POMDOUT  | 0xA4    | Port 0 Output Mode Configuration | 154  |

| POSKIP   | 0xD4    | Port 0 Skip                      | 155  |

| P1       | 0x90    | Port 1 Latch                     | 155  |

| P1MASK   | 0xEE    | P0 Mask                          | 152  |

## SFR Definition 18.2. IP: Interrupt Priority

|       | - |       |     |     |     |     | -   | -   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xB8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 1b, Write = Don't Care.                                                                                                                                                                                                                                 |

| 6   | PSPI0  | Serial Peripheral Interface (SPI0) Interrupt Priority Control.<br>This bit sets the priority of the SPI0 interrupt.<br>0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level.                                           |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                                                         |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                                                                     |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                                                         |

| 2   | PX1    | <ul> <li>External Interrupt 1 Priority Control.</li> <li>This bit sets the priority of the External Interrupt 1 interrupt.</li> <li>0: External Interrupt 1 set to low priority level.</li> <li>1: External Interrupt 1 set to high priority level.</li> </ul> |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                                                         |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level.                                       |

#### 19.4.3. System Clock

- 1. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 2. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in "AN201: Writing to Flash from Firm-ware," available from the Silicon Laboratories website.

## SFR Definition 19.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

#### SFR Address =0x8F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

## 20.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

### 20.3. Suspend Mode

Suspend mode allows a system running from the internal oscillator to go to a very low power state similar to Stop mode, but the processor can be awakened by certain events without requiring a reset of the device. Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into Suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in Suspend mode. The exception to this is the Port Match feature and Timer 3, when it is run from an external oscillator source.

The clock divider bits CLKDIV[2:0] in register CLKSEL must be set to "divide by 1" when entering suspend mode.

Suspend mode can be terminated by five types of events, a port match (described in Section "23.5. Port Match" on page 150), a Timer 2 overflow (described in Section "28.2. Timer 2" on page 219), a comparator low output (if enabled), a capacitive sense greater-than comparator event, or a device reset event. In order to run Timer 3 in suspend mode, the timer must be configured to clock from the external clock source. When suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event (port match or Timer 2 overflow) was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** The device will still enter suspend mode if a wake source is "pending", and the device will not wake on such pending sources. It is important to ensure that the intended wake source will trigger after the device enters suspend mode. For example, if a CS0 conversion completes and the interrupt fires before the device is in suspend mode, that interrupt cannot trigger the wake event. Because port match events are level-sensitive, pre-existing port match events will trigger a wake, as long as the match condition is still present when the device enters suspend.

## SFR Definition 22.4. OSCXCN: External Oscillator Control

| Bit   | 7      | 6 | 5          | 4  | 3 | 2         | 1 0 |   |  |  |  |

|-------|--------|---|------------|----|---|-----------|-----|---|--|--|--|

| Name  | XTLVLD | Х | (OSCMD[2:0 | )] |   | XFCN[2:0] |     |   |  |  |  |

| Туре  | R      |   | R/W        |    | R |           | R/W |   |  |  |  |

| Reset | 0      | 0 | 0          | 0  | 0 | 0         | 0   | 0 |  |  |  |

SFR Address = 0xB1

| Bit | Name        |         | Function                                             |                                           |                 |  |  |  |  |  |  |  |

|-----|-------------|---------|------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|--|--|

| 7   | XTLVLD      | Crystal | Crystal Oscillator Valid Flag.                       |                                           |                 |  |  |  |  |  |  |  |

|     |             | •       | Read only when XOSCMD = 11x.)                        |                                           |                 |  |  |  |  |  |  |  |

|     |             | -       | ): Crystal Oscillator is unused or not yet stable.   |                                           |                 |  |  |  |  |  |  |  |

|     |             | ,       | : Crystal Oscillator is running and stable.          |                                           |                 |  |  |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Selec                              | ct.                                       |                 |  |  |  |  |  |  |  |

|     |             |         | ernal Oscillator circuit of                          |                                           |                 |  |  |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                               |                                           |                 |  |  |  |  |  |  |  |

|     |             |         | ernal CMOS Clock Mode                                | e with divide by 2 stage.                 |                 |  |  |  |  |  |  |  |

|     |             |         | Oscillator Mode.                                     |                                           |                 |  |  |  |  |  |  |  |

|     |             |         | pacitor Oscillator Mode.                             |                                           |                 |  |  |  |  |  |  |  |

|     |             | -       | vstal Oscillator Mode.<br>vstal Oscillator Mode with | divida by 2 staga                         |                 |  |  |  |  |  |  |  |

|     |             |         |                                                      | i ulviue by 2 stage.                      |                 |  |  |  |  |  |  |  |

| 3   | Unused      |         | 0; Write = Don't Care                                |                                           |                 |  |  |  |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | I Oscillator Frequency                               |                                           |                 |  |  |  |  |  |  |  |

|     |             |         | -                                                    | uency for Crystal or RC r                 | node.           |  |  |  |  |  |  |  |

|     |             |         | ording to the desired K F                            |                                           |                 |  |  |  |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                         | RC Mode                                   | C Mode          |  |  |  |  |  |  |  |

|     |             | 000     | f ≤ 32 kHz                                           | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                  | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |  |  |

|     |             | 010     | 84 kHz < f ≤ 225 kHz                                 | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |  |  |

|     |             | 011     | 225 kHz < f ≤ 590 kHz                                | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |  |  |  |  |  |  |  |

|     |             | 100     | 590 kHz < f ≤ 1.5 MHz                                | 200 kHz < f $\leq$ 400 kHz                | K Factor = 65   |  |  |  |  |  |  |  |

|     |             | 101     | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$              | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |  |  |

|     |             | 110     | $4 \text{ MHz} < f \le 10 \text{ MHz}$               | 800 kHz $<$ f $\leq$ 1.6 MHz              | K Factor = 664  |  |  |  |  |  |  |  |

|     |             | 111     | 10 MHz < f ≤ 30 MHz                                  | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |  |  |

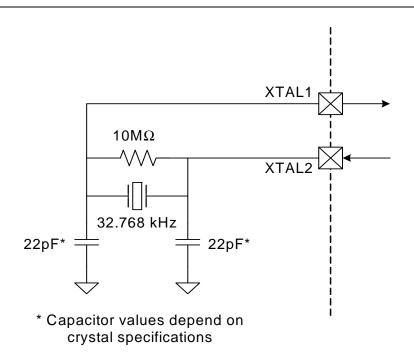

#### Figure 22.2. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

#### 22.3.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 22.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 22.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in k $\Omega$ .

#### Equation 22.1. RC Mode Oscillator Frequency

$f = 1.23 \times 10^3 / (R \times C)$

Rev. 1.0

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$f = 1.23(10^3) / RC = 1.23(10^3) / [246 \times 50] = 0.1 MHz = 100 kHz$

Referring to the table in SFR Definition 22.4, the required XFCN setting is 010b.

| Port                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       | P     | 0    |   |        |   | P1 |   |   |     |                |                | P2             |                       |                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------|---|--------|---|----|---|---|-----|----------------|----------------|----------------|-----------------------|-----------------------|

| Pin Number                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                | 1    | 2     | 3     | 4    | 5 | 6      | 7 | 0  | 1 | 2 | 3   | 4 <sup>1</sup> | 5 <sup>1</sup> | 6 <sup>1</sup> | <b>7</b> <sup>1</sup> | 0                     |

| Special<br>Function<br>Signals                                                                                                                                                                                                                                                                                                                               | VREF                                                                                                                                                                                                                                                                                                                                                                                             | AGND | XTAL1 | XTAL2 |      |   | CNVSTR |   |    |   |   |     |                |                |                |                       |                       |

| ТХО                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| RX0                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| SCK                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| MISO                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | ar                    |

| MOSI                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | Crossbal              |

| NSS <sup>2</sup>                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | 5<br>S                |

| SDA                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | Signal Unavailable to |

| SCL                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | able                  |

| CP0                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | /ail                  |

| CP0A                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | na/                   |

| SYSCLK                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | al C                  |

| CEX0                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | ign                   |

| CEX1                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       | ပ                     |

| CEX2                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| ECI                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| TO                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| T1                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| Pin Skip                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                | 0    | 0     | 0     | 0    | 0 | 0      | 0 | 0  | 0 | 0 | 0   | 0              | 0              | 0              | 0                     |                       |

| Settings                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       | P0S   | SKIF | ) |        |   |    |   |   | P15 | SKIF           | >              |                |                       |                       |

| RX0 signals, t<br>signals are as<br>using the P0S<br>These box<br>in this configu<br>1 <sup>st</sup> TX0 is ass<br>2 <sup>nd</sup> RX0 is ass                                                                                                                                                                                                                | In this example, the crossbar is configured to assign the UART TX0 and RX0 signals, the SPI signals, and the PCA signals. Note that the SPI signals are assigned as multiple signals, and there are no pins skipped using the P0SKIP or P1SKIP registers.  These boxes represent the port pins which are used by the peripherals in this configuration.  1 <sup>st</sup> TX0 is assigned to P0.4 |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

| <ul> <li>2<sup>nd</sup> RX0 is assigned to P0.5</li> <li>3<sup>rd</sup> SCK, MISO, MOSI, and NSS are assigned to P0.0, P0.1, P0.2, and P0.3, respectively.</li> <li>4<sup>th</sup> CEX0, CEX1, and CEX2 are assigned to P0.6, P0.7, and P1.0, respectively.</li> <li>All unassigned pins can be used as GPIO or for other non-crossbar functions.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                  |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

|                                                                                                                                                                                                                                                                                                                                                              | Notes:<br>1. P1.4-P1.7 are not available on 16-pin packages.<br>2. NSS is only pinned out when the SPI is in 4-wire mode.                                                                                                                                                                                                                                                                        |      |       |       |      |   |        |   |    |   |   |     |                |                |                |                       |                       |

Figure 23.5. Priority Crossbar Decoder Example 1—No Skipped Pins

## SFR Definition 23.12. P1MDIN: Port 1 Input Mode

| Bit   | 7           | 6  | 5  | 4  | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------|-------------|----|----|----|---|---|---|---|--|--|--|--|--|

| Name  | P1MDIN[7:0] |    |    |    |   |   |   |   |  |  |  |  |  |

| Туре  |             |    |    | R/ | W |   |   |   |  |  |  |  |  |

| Reset | 1*          | 1* | 1* | 1* | 1 | 1 | 1 | 1 |  |  |  |  |  |

SFR Address = 0xF2

| Bit | Name        | Function                                                                                                                                                                                                                            |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDIN[7:0] | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                             |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. In order for the P1.n pin to be in analog mode, there MUST be a 1 in the Port Latch register corresponding to that pin. |

|     |             | 0: Corresponding P1.n pin is configured for analog mode.                                                                                                                                                                            |

|     |             | 1: Corresponding P1.n pin is not configured for analog mode.                                                                                                                                                                        |

|     |             | Note: P1.4–P1.7 are not available on 16-pin packages, with the reset value of 0000b for P1MDIN[7:4].                                                                                                                                |

### SFR Definition 23.13. P1MDOUT: Port 1 Output Mode

| Bit   | 7            | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |  |  |  |

|-------|--------------|---|---|----|---|---|---|---|--|--|--|--|--|--|--|

| Name  | P1MDOUT[7:0] |   |   |    |   |   |   |   |  |  |  |  |  |  |  |

| Туре  |              |   |   | R/ | W |   |   |   |  |  |  |  |  |  |  |

| Reset | 0            | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |  |  |  |  |

SFR Address = 0xA5

| Bit | Name         | Function                                                                       |

|-----|--------------|--------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                        |

|     |              | These bits are ignored if the corresponding bit in register P1MDIN is logic 0. |

|     |              | 0: Corresponding P1.n Output is open-drain.                                    |

|     |              | 1: Corresponding P1.n Output is push-pull.                                     |

|     |              | <b>Note:</b> P1.4–P1.7 are not available on 16-pin packages.                   |

## 26.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

### 26.2. SMBus Configuration

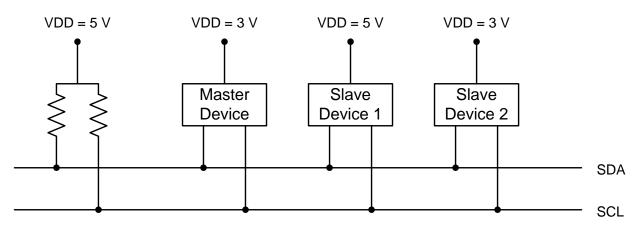

Figure 26.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 26.2. Typical SMBus Configuration

## 26.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 26.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

## SFR Definition 26.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | 0: Clear interrupt, and initi-<br>ate next state machine<br>event.<br>1: Force interrupt.                                                                                            |

|                    |                                                                              |                      | Fre                            | quency: 24.5 M        | lHz                                             |                  |                                  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|--|--|

|                    | Target<br>Baud Rate<br>(bps)                                                 | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |  |  |

|                    | 230400                                                                       | -0.32%               | 106                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |  |  |  |  |  |

| . ء                | 115200                                                                       | -0.32%               | 212                            | SYSCLK                | XX                                              | 1                | 0x96                             |  |  |  |  |  |

| from<br>Osc.       | 57600                                                                        | 0.15%                | 426                            | SYSCLK                | XX                                              | 1                | 0x2B                             |  |  |  |  |  |

| Υ Ξ                | 28800                                                                        | -0.32%               | 848                            | SYSCLK/4              | 01                                              | 0                | 0x96                             |  |  |  |  |  |

| SYSCLK<br>Internal | 14400                                                                        | 0.15%                | 1704                           | SYSCLK/12             | 00                                              | 0                | 0xB9                             |  |  |  |  |  |

| ΥS                 | 9600                                                                         | -0.32%               | 2544                           | SYSCLK/12             | 00                                              | 0                | 0x96                             |  |  |  |  |  |

| ίω ⊨               | 2400                                                                         | -0.32%               | 10176                          | SYSCLK/48             | 10                                              | 0                | 0x96                             |  |  |  |  |  |

|                    | 1200                                                                         | 0.15%                | 20448                          | SYSCLK/48             | 10                                              | 0                | 0x2B                             |  |  |  |  |  |

|                    | Notes:<br>1. SCA1–SCA0 and T1M bit definitions can be found in Section 28.1. |                      |                                |                       |                                                 |                  |                                  |  |  |  |  |  |

# Table 27.1. Timer Settings for Standard Baud RatesUsing The Internal 24.5 MHz Oscillator

# Table 27.2. Timer Settings for Standard Baud RatesUsing an External 22.1184 MHz Oscillator

|        |          |                              |                      | Frequ                          | uency: 22.1184        | MHz                                             |                  |                                  |

|--------|----------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|        |          | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|        |          | 230400                       | 0.00%                | 96                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xD0                             |

| ٦      | പ        | 115200                       | 0.00%                | 192                            | SYSCLK                | XX                                              | 1                | 0xA0                             |

| from   | Osc      | 57600                        | 0.00%                | 384                            | SYSCLK                | XX                                              | 1                | 0x40                             |

| Υf     |          | 28800                        | 0.00%                | 768                            | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| SYSCLK | External | 14400                        | 0.00%                | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| ΥS     | xte      | 9600                         | 0.00%                | 2304                           | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| Ś      | ш        | 2400                         | 0.00%                | 9216                           | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

|        |          | 1200                         | 0.00%                | 18432                          | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

| ٤      |          | 230400                       | 0.00%                | 96                             | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |

| from   | Osc.     | 115200                       | 0.00%                | 192                            | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |

| Υ      |          | 57600                        | 0.00%                | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

| 5      | rna      | 28800                        | 0.00%                | 768                            | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |

| SYSCLK | Internal | 14400                        | 0.00%                | 1536                           | EXTCLK / 8            | 11                                              | 0                | 0xA0                             |

| Ś      | -        | 9600                         | 0.00%                | 2304                           | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| No     | tes:     |                              |                      |                                |                       |                                                 |                  |                                  |

Notes:

1. SCA1–SCA0 and T1M bit definitions can be found in Section 28.1.

**2.** X = Don't care.

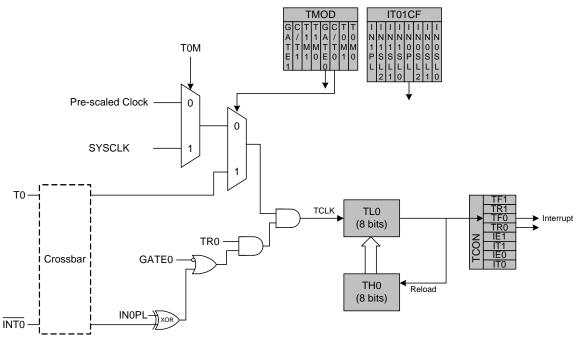

Figure 28.2. T0 Mode 2 Block Diagram

#### 28.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

## SFR Definition 28.8. TMR2CN: Timer 2 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1 | 0      |

|-------|------|------|--------|--------|---------|-----|---|--------|

| Name  | TF2H | TF2L | TF2LEN | TF2CEN | T2SPLIT | TR2 |   | T2XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0 | 0      |

#### SFR Address = 0xC8; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2H    | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |         | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                         |

| 6   | TF2L    | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                      |

| 5   | TF2LEN  | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |