# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 13                                                             |

| Program Memory Size        | 16KB (16K × 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 12x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 16-SOIC                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f805-gs |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## C8051F80x-83x

| 15.2. Data Memory                                           | 93    |

|-------------------------------------------------------------|-------|

| 15.2.1. Internal RAM                                        |       |

| 15.2.1.1. General Purpose Registers                         |       |

| 15.2.1.2. Bit Addressable Locations                         |       |

| 15.2.1.3. Stack                                             |       |

| 16. In-System Device Identification                         |       |

| 17. Special Function Registers                              |       |

| 18. Interrupts                                              |       |

| 18.1. MCU Interrupt Sources and Vectors                     |       |

| 18.1.1. Interrupt Priorities                                |       |

| 18.1.2. Interrupt Latency                                   |       |

| 18.2. Interrupt Register Descriptions                       |       |

| 18.3. INTO and INT1 External Interrupts                     |       |

| 19. Flash Memory                                            |       |

| 19.1. Programming The Flash Memory                          | . 113 |

| 19.1.1. Flash Lock and Key Functions                        |       |

| 19.1.2. Flash Erase Procedure                               |       |

| 19.1.3. Flash Write Procedure                               |       |

| 19.2. Non-volatile Data Storage                             |       |

| 19.3. Security Options                                      |       |

| 19.4. Flash Write and Erase Guidelines                      |       |

| 19.4.1. VDD Maintenance and the VDD Monitor                 |       |

| 19.4.2. PSWE Maintenance                                    |       |

| 19.4.3. System Clock                                        | . 117 |

| 20. Power Management Modes                                  | . 120 |

| 20.1. Idle Mode                                             | . 120 |

| 20.2. Stop Mode                                             | . 121 |

| 20.3. Suspend Mode                                          |       |

| 21. Reset Sources                                           |       |

| 21.1. Power-On Reset                                        |       |

| 21.2. Power-Fail Reset / VDD Monitor                        |       |

| 21.3. External Reset                                        |       |

| 21.4. Missing Clock Detector Reset                          |       |

| 21.5. Comparator0 Reset                                     |       |

| 21.6. PCA Watchdog Timer Reset                              |       |

| 21.7. Flash Error Reset                                     |       |

| 21.8. Software Reset                                        |       |

| 22. Oscillators and Clock Selection                         |       |

| 22.1. System Clock Selection                                |       |

| 22.2. Programmable Internal High-Frequency (H-F) Oscillator |       |

| 22.3. External Oscillator Drive Circuit                     |       |

| 22.3.1. External Crystal Example                            |       |

| 22.3.2. External RC Example                                 |       |

| 22.3.3. External Capacitor Example                          |       |

| 23. Port Input/Output                                       | . 138 |

#### 1. System Overview

C8051F80x-83x devices are fully integrated, mixed-signal, system-on-a-chip capacitive sensing MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Capacitive sense interface with 16 input channels

- 10-bit 500 ksps single-ended ADC with 16-channel analog multiplexer and integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

- 16 kb of on-chip Flash memory

- 512 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Three general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules

- On-chip internal voltage reference

- On-chip Watchdog timer

- On-chip power-on reset and supply monitor

- On-chip voltage comparator

- 17 general purpose I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F80x-83x devices are truly stand-alone, system-on-a-chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The C8051F80x-83x processors include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8-3.6 V operation over the industrial temperature range (-45 to +85 °C). An internal LDO regulator is used to supply the processor core voltage at 1.8 V. The Port I/O and RST pins are tolerant of input signals up to 5 V. See Table 2.1 for ordering information. Block diagrams of the devices in the C8051F80x-83x family are shown in Figure 1.1 through Figure 1.9.

### 3. Pin Definitions

| Name            | Pin<br>QSOP-24 | Pin<br>QFN-20 | Pin<br>SOIC-16 | Туре             | Description                                                                                                                                                                                |

|-----------------|----------------|---------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | 5              | 2             | 4              |                  | Ground.<br>This ground connection is required. The center<br>pad may optionally be connected to ground as<br>well on the QFN-20 packages.                                                  |

| V <sub>DD</sub> | 6              | 3             | 5              |                  | Power Supply Voltage.                                                                                                                                                                      |

| RST/            | 7              | 4             | 6              | D I/O            | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor. An external source can initiate a system reset by driving this pin low for at least 10 $\mu$ s.                       |

| C2CK            |                |               |                | D I/O            | Clock signal for the C2 Debug Interface.                                                                                                                                                   |

| P2.0/           | 8              | 5             | 7              | D I/O            | Bi-directional data signal for the C2 Debug Inter-<br>face. Shared with P2.0 on 20-pin packaging and<br>P2.4 on 24-pin packaging.                                                          |

| C2D             |                |               |                | D I/O            | Bi-directional data signal for the C2 Debug Inter-<br>face. Shared with P2.0 on 20-pin packaging and<br>P2.4 on 24-pin packaging.                                                          |

| P0.0/           | 4              | 1             | 3              | D I/O or<br>A In | Port 0.0.                                                                                                                                                                                  |

| VREF            |                |               |                | A In             | External VREF input.                                                                                                                                                                       |

| P0.1            | 3              | 20            | 2              | D I/O or<br>A In | Port 0.1.                                                                                                                                                                                  |

| P0.2/           | 2              | 19            | 1              | D I/O or<br>A In | Port 0.2.                                                                                                                                                                                  |

| XTAL1           |                |               |                | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator.                                                                                               |

| P0.3/           | 23             | 18            | 16             | D I/O or<br>A In | Port 0.3.                                                                                                                                                                                  |

| XTAL2           |                |               |                | A I/O or<br>D In | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. |

| P0.4            | 22             | 17            | 15             | D I/O or<br>A In | Port 0.4.                                                                                                                                                                                  |

Table 3.1. Pin Definitions for the C8051F80x-83x

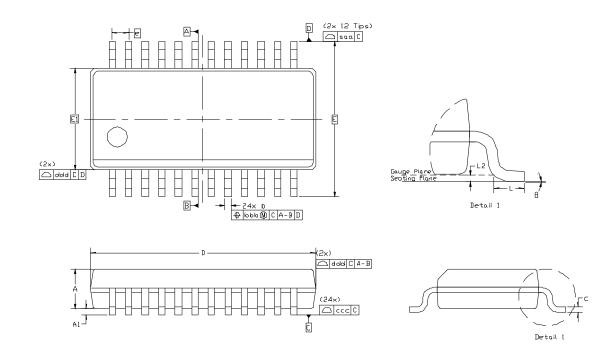

### 5. **QSOP-24** Package Specifications

Figure 5.1. QSOP-24 Package Drawing

|           |      |           | -    | - |           |      | -        |      |

|-----------|------|-----------|------|---|-----------|------|----------|------|

| Dimension | Min  | Nom       | Max  |   | Dimension | Min  | Nom      | Max  |

| А         |      | —         | 1.75 |   | L         | 0.40 | —        | 1.27 |

| A1        | 0.10 |           | 0.25 |   | L2        |      | 0.25 BSC |      |

| b         | 0.20 | —         | 0.30 |   | θ         | 0°   | —        | 8º   |

| С         | 0.10 | _         | 0.25 | 1 | aaa       |      | 0.20     |      |

| D         |      | 8.65 BSC  |      |   | bbb       |      | 0.18     |      |

| E         |      | 6.00 BSC  |      |   | CCC       |      | 0.10     |      |

| E1        |      | 3.90 BSC  |      | 1 | ddd       |      | 0.10     |      |

| е         |      | 0.635 BSC | ;    | 1 |           |      |          |      |

|           |      |           |      |   |           |      |          |      |

Table 5.1. QSOP-24 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

- Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 7.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameters          | Conditions                                   | Min                    | Тур                   | Мах | Units |

|---------------------|----------------------------------------------|------------------------|-----------------------|-----|-------|

| Output High Voltage | I <sub>OH</sub> = –3 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7  | _                     | _   | V     |

|                     | I <sub>OH</sub> = –10 μA, Port I/O push-pull | V <sub>DD</sub> - 0.1  | —                     | —   | V     |

|                     | I <sub>OH</sub> = –10 mA, Port I/O push-pull | —                      | V <sub>DD</sub> - 0.8 | —   | V     |

| Output Low Voltage  | I <sub>OL</sub> = 8.5 mA                     | —                      | _                     | 0.6 | V     |

|                     | I <sub>OL</sub> = 10 μA                      | —                      | —                     | 0.1 | V     |

|                     | I <sub>OL</sub> = 25 mA                      |                        | 1.0                   | —   | V     |

| Input High Voltage  |                                              | 0.75 x V <sub>DD</sub> |                       |     | V     |

| Input Low Voltage   |                                              |                        | _                     | 0.6 | V     |

| Input Leakage       | Weak Pullup Off                              | -1                     |                       | 1   | μA    |

| Current             | Weak Pullup On, V <sub>IN</sub> = 0 V        | —                      | 15                    | 50  | μA    |

#### **Table 7.4. Reset Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                                       | Conditions                                                                            | Min                  | Тур  | Max                   | Units    |

|-------------------------------------------------|---------------------------------------------------------------------------------------|----------------------|------|-----------------------|----------|

| RST Output Low Voltage                          | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                         | —                    | _    | 0.6                   | V        |

| RST Input High Voltage                          |                                                                                       | $0.75 \times V_{DD}$ |      |                       | V        |

| RST Input Low Voltage                           |                                                                                       | —                    |      | 0.3 x V <sub>DD</sub> | $V_{DD}$ |

| RST Input Pullup Current                        | RST = 0.0 V                                                                           | _                    | 25   | 50                    | μA       |

| V <sub>DD</sub> POR Ramp Time                   |                                                                                       | —                    | —    | 1                     | ms       |

| $V_{DD}$ Monitor Threshold ( $V_{RST}$ )        |                                                                                       | 1.7                  | 1.75 | 1.8                   | V        |

| Missing Clock Detector<br>Timeout               | Time from last system clock rising edge to reset initiation                           | 100                  | 500  | 1000                  | μs       |

| Reset Time Delay                                | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | _                    |      | 30                    | μs       |

| Minimum RST Low Time to Generate a System Reset |                                                                                       | 15                   | _    | _                     | μs       |

| V <sub>DD</sub> Monitor Turn-on Time            | $V_{DD} = V_{RST} - 0.1 V$                                                            |                      | 50   |                       | μs       |

| V <sub>DD</sub> Monitor Supply Current          |                                                                                       |                      | 20   | 30                    | μA       |

#### Table 7.5. Internal Voltage Regulator Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter           | Conditions | Min | Тур | Мах | Units |

|---------------------|------------|-----|-----|-----|-------|

| Input Voltage Range |            | 1.8 | _   | 3.6 | V     |

| Bias Current        |            |     | 50  | 65  | μA    |

#### Table 7.10. Power Management Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions | Min | Тур | Мах | Units   |

|---------------------------|------------|-----|-----|-----|---------|

| Idle Mode Wake-Up Time    |            | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time |            | _   | 500 | _   | ns      |

#### Table 7.11. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                | Conditions                                              | Min | Тур  | Max | Units |  |  |  |

|--------------------------|---------------------------------------------------------|-----|------|-----|-------|--|--|--|

| Linearity                |                                                         | -   | 1    | —   | °C    |  |  |  |

| Slope                    |                                                         | —   | 2.43 | _   | mV/°C |  |  |  |

| Slope Error*             |                                                         |     | ±45  | —   | µV/°C |  |  |  |

| Offset                   | Temp = 0 °C                                             | —   | 873  | —   | mV    |  |  |  |

| Offset Error*            | Temp = 0 °C                                             |     | 14.5 | —   | mV    |  |  |  |

| *Note: Represents one st | *Note: Represents one standard deviation from the mean. |     |      |     |       |  |  |  |

#### Table 7.12. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V; -40 to +85 °C unless otherwise specified.

| Parameter           | Conditions                                      | Min  | Тур  | Max      | Units |  |  |  |  |

|---------------------|-------------------------------------------------|------|------|----------|-------|--|--|--|--|

| In                  | Internal High Speed Reference (REFSL[1:0] = 11) |      |      |          |       |  |  |  |  |

| Output Voltage      | 25 °C ambient                                   | 1.55 | 1.65 | 1.75     | V     |  |  |  |  |

| Turn-on Time        |                                                 | —    | —    | 1.7      | μs    |  |  |  |  |

| Supply Current      |                                                 |      | 180  |          | μA    |  |  |  |  |

|                     | External Reference (REF0E = 0)                  |      |      |          |       |  |  |  |  |

| Input Voltage Range |                                                 | 0    | —    | $V_{DD}$ |       |  |  |  |  |

| Input Current       | Sample Rate = 500 ksps; VREF = 3.0 V            |      | 7    | _        | μA    |  |  |  |  |

#### SFR Definition 8.4. ADC0CN: ADC0 Control

| Bit   | 7     | 6     | 5      | 4       | 3       | 2 | 1          | 0 |

|-------|-------|-------|--------|---------|---------|---|------------|---|

| Name  | AD0EN | AD0TM | AD0INT | AD0BUSY | AD0WINT |   | AD0CM[2:0] |   |

| Туре  | R/W   | R/W   | R/W    | R/W     | R/W     |   | R/W        |   |

| Reset | 0     | 0     | 0      | 0       | 0       | 0 | 0          | 0 |

#### SFR Address = 0xE8; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                                            |  |  |  |  |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| 7   | AD0EN      | ADC0 Enable Bit.                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                                            |  |  |  |  |  |

|     |            | ): ADC0 Disabled. ADC0 is in low-power shutdown.                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                                            |  |  |  |  |  |

|     |            | 1: ADC0 Enabled. ADC0 is act                                                                                                                                                                                                                                                                                                                                                                                                                  | 1: ADC0 Enabled. ADC0 is active and ready for data conversions.                    |                                                                            |  |  |  |  |  |

| 6   | AD0TM      | ADC0 Track Mode Bit.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |                                                                            |  |  |  |  |  |

|     |            | <ul> <li>0: Normal Track Mode: When ADC0 is enabled, tracking is continuous unless a conversion is in progress. Conversion begins immediately on start-of-conversion event, as defined by AD0CM[2:0].</li> <li>1: Delayed Track Mode: When ADC0 is enabled, input is tracked when a conversion is not in progress. A start-of-conversion signal initiates three SAR clocks of additional tracking, and then begins the conversion.</li> </ul> |                                                                                    |                                                                            |  |  |  |  |  |

| 5   | AD0INT     | ADC0 Conversion Complete                                                                                                                                                                                                                                                                                                                                                                                                                      | Interrupt Flag.                                                                    |                                                                            |  |  |  |  |  |

|     |            | 0: ADC0 has not completed a 1.<br>1: ADC0 has completed a data                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | NT was last cleared.                                                       |  |  |  |  |  |

| 4   | AD0BUSY    | ADC0 Busy Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                | Read:                                                                              | Write:                                                                     |  |  |  |  |  |

|     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0: ADC0 conversion is not<br>in progress.<br>1: ADC0 conversion is in<br>progress. | 0: No Effect.<br>1: Initiates ADC0 Conver-<br>sion if AD0CM[2:0] =<br>000b |  |  |  |  |  |

| 3   | AD0WINT    | ADC0 Window Compare Inte                                                                                                                                                                                                                                                                                                                                                                                                                      | rrupt Flag.                                                                        |                                                                            |  |  |  |  |  |

|     |            | 0: ADC0 Window Comparison<br>cleared.<br>1: ADC0 Window Comparison                                                                                                                                                                                                                                                                                                                                                                            |                                                                                    | ed since this flag was last                                                |  |  |  |  |  |

| 2:0 | AD0CM[2:0] | ADC0 Start of Conversion M                                                                                                                                                                                                                                                                                                                                                                                                                    | ode Select.                                                                        |                                                                            |  |  |  |  |  |

|     |            | 000: ADC0 start-of-conversion                                                                                                                                                                                                                                                                                                                                                                                                                 | source is write of 1 to AD0                                                        | BUSY.                                                                      |  |  |  |  |  |

|     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 001: ADC0 start-of-conversion source is overflow of Timer 0.                       |                                                                            |  |  |  |  |  |

|     |            | 010: ADC0 start-of-conversion                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |                                                                            |  |  |  |  |  |

|     |            | 011: ADC0 start-of-conversion                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |                                                                            |  |  |  |  |  |

|     |            | 100: ADC0 start-of-conversion 101–111: Reserved.                                                                                                                                                                                                                                                                                                                                                                                              | source is rising edge of ext                                                       | ernal CNVSTR.                                                              |  |  |  |  |  |

|     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |                                                                            |  |  |  |  |  |

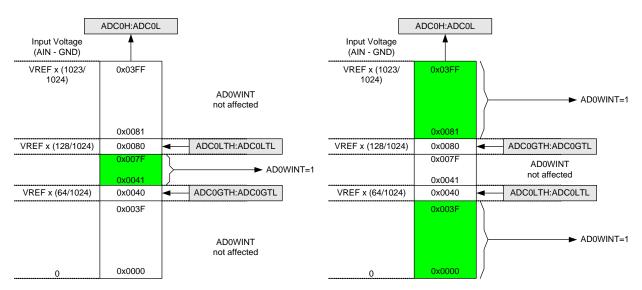

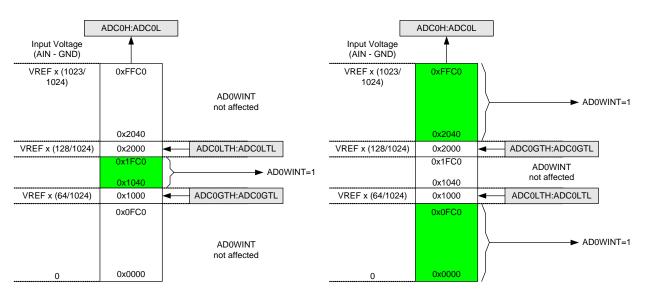

#### 8.4.1. Window Detector Example

Figure 8.4 shows two example window comparisons for right-justified data. with ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 8.5 shows an example using left-justified data with the same comparison values.

Figure 8.4. ADC Window Compare Example: Right-Justified Data

Figure 8.5. ADC Window Compare Example: Left-Justified Data

### 13. Capacitive Sense (CS0)

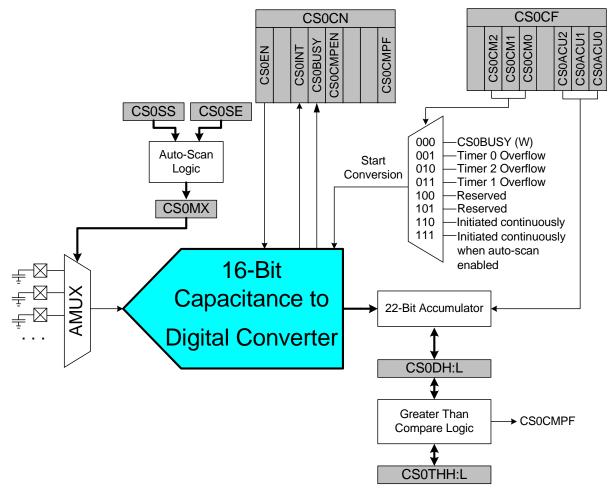

The Capacitive Sense subsystem included on the C8051F800/1/3/4/6/7/9, C8051F810/2/3/5/6/8/9, C8051F821/2/4/5/7/8, C8051F830/1/3/4 uses a capacitance-to-digital circuit to determine the capacitance on a port pin. The module can take measurements from different port pins using the module's analog multiplexer. The multiplexer supports up to 16 channels. See SFR Definition 13.9. "CSOMX: Capacitive Sense Mux Channel Select" on page 81 for channel availability for specific part numbers. The module is enabled only when the CS0EN bit (CS0CN) is set to 1. Otherwise the module is in a low-power shutdown state. The module can be configured to take measurements on one port pin or a group of port pins, using auto-scan. An accumulator can be configured to accumulate multiple conversions on an input channel. Interrupts can be generated when CS0 completes a conversion or when the measured value crosses a threshold defined in CS0THH:L.

#### SFR Definition 13.5. CS0SS: Capacitive Sense Auto-Scan Start Channel

| Bit   | 7 | 6 | 5 | 4   | 3   | 2          | 1   | 0   |

|-------|---|---|---|-----|-----|------------|-----|-----|

| Name  |   |   |   |     |     | CS0SS[4:0] |     |     |

| Туре  | R | R | R | R/W | R/W | R/W        | R/W | R/W |

| Reset | 0 | 0 | 0 | 0   | 0   | 0          | 0   | 0   |

SFR Address = 0xB9

| Bit | Name       | Description                                                                                                                |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused     | Read = 000b; Write = Don't care                                                                                            |

| 4:0 | CS0SS[4:0] | Starting Channel for Auto-Scan.                                                                                            |

|     |            | Sets the first CS0 channel to be selected by the mux for Capacitive Sense conversion when auto-scan is enabled and active. |

|     |            | When auto-scan is enabled, a write to CS0SS will also update CS0MX.                                                        |

#### SFR Definition 13.6. CS0SE: Capacitive Sense Auto-Scan End Channel

| Bit   | 7 | 6 | 5 | 4   | 3   | 2          | 1   | 0   |

|-------|---|---|---|-----|-----|------------|-----|-----|

| Name  |   |   |   |     |     | CS0SE[4:0] |     |     |

| Туре  | R | R | R | R/W | R/W | R/W        | R/W | R/W |

| Reset | 0 | 0 | 0 | 0   | 0   | 0          | 0   | 0   |

SFR Address = 0xBA

| Bit | Name       | Description                                                                                                               |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused     | Read = 000b; Write = Don't care                                                                                           |

| 4:0 | CS0SE[4:0] | Ending Channel for Auto-Scan.                                                                                             |

|     |            | Sets the last CS0 channel to be selected by the mux for Capacitive Sense conversion when auto-scan is enabled and active. |

#### 14.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

#### SFR Definition 14.1. DPL: Data Pointer Low Byte

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7             | 6           | 5                 | 4             | 3           | 2   | 1 | 0 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------------|---------------|-------------|-----|---|---|--|

| Name DPL[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |             |                   |               |             |     |   |   |  |

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9             | R/W         |                   |               |             |     |   |   |  |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>0</td> <td>0</td> |               |             |                   |               | 0           | 0   |   |   |  |

| SFR A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Address = 0x8 | 2           |                   |               |             |     |   |   |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Name          |             | Function          |               |             |     |   |   |  |

| 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DPL[7:0]      | Data Pointe | Data Pointer Low. |               |             |     |   |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               | The DPL reg | gister is the lo  | ow byte of th | e 16-bit DP | TR. |   |   |  |

#### SFR Definition 14.2. DPH: Data Pointer High Byte

| Bit   | 7        | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|-----|---|---|---|---|---|---|

| Name  | DPH[7:0] |     |   |   |   |   |   |   |

| Туре  |          | R/W |   |   |   |   |   |   |

| Reset | 0        | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x83

| Bit | Name     | Function                                              |

|-----|----------|-------------------------------------------------------|

| 7:0 | DPH[7:0] | Data Pointer High.                                    |

|     |          | The DPH register is the high byte of the 16-bit DPTR. |

#### Table 17.2. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register         | Address | Description                 | Page |

|------------------|---------|-----------------------------|------|

| SBUF0            | 0x99    | UART0 Data Buffer           | 207  |

| SCON0            | 0x98    | UART0 Control               | 206  |

| SMB0ADM          | 0xD6    | SMBus Slave Address mask    | 191  |

| SMB0ADR          | 0xD7    | SMBus Slave Address         | 191  |

| SMB0CF           | 0xC1    | SMBus Configuration         | 186  |

| SMB0CN           | 0xC0    | SMBus Control               | 188  |

| SMB0DAT          | 0xC2    | SMBus Data                  | 192  |

| SP               | 0x81    | Stack Pointer               | 89   |

| SPI0CFG          | 0xA1    | SPI0 Configuration          | 174  |

| SPIOCKR          | 0xA2    | SPI0 Clock Rate Control     | 176  |

| SPI0CN           | 0xF8    | SPI0 Control                | 175  |

| SPIODAT          | 0xA3    | SPI0 Data                   | 176  |

| TCON             | 0x88    | Timer/Counter Control       | 215  |

| TH0              | 0x8C    | Timer/Counter 0 High        | 218  |

| TH1              | 0x8D    | Timer/Counter 1 High        | 218  |

| TL0              | 0x8A    | Timer/Counter 0 Low         | 217  |

| TL1              | 0x8B    | Timer/Counter 1 Low         | 217  |

| TMOD             | 0x89    | Timer/Counter Mode          | 216  |

| TMR2CN           | 0xC8    | Timer/Counter 2 Control     | 222  |

| TMR2H            | 0xCD    | Timer/Counter 2 High        | 224  |

| TMR2L            | 0xCC    | Timer/Counter 2 Low         | 224  |

| TMR2RLH          | 0xCB    | Timer/Counter 2 Reload High | 223  |

| TMR2RLL          | 0xCA    | Timer/Counter 2 Reload Low  | 223  |

| VDM0CN           | 0xFF    | VDD Monitor Control         | 126  |

| XBR0             | 0xE1    | Port I/O Crossbar Control 0 | 148  |

| XBR1             | 0xE2    | Port I/O Crossbar Control 1 | 149  |

| All other SFR Lo | cations | Reserved                    |      |

## C8051F80x-83x

#### 20.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

#### 20.3. Suspend Mode

Suspend mode allows a system running from the internal oscillator to go to a very low power state similar to Stop mode, but the processor can be awakened by certain events without requiring a reset of the device. Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into Suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in Suspend mode. The exception to this is the Port Match feature and Timer 3, when it is run from an external oscillator source.

The clock divider bits CLKDIV[2:0] in register CLKSEL must be set to "divide by 1" when entering suspend mode.

Suspend mode can be terminated by five types of events, a port match (described in Section "23.5. Port Match" on page 150), a Timer 2 overflow (described in Section "28.2. Timer 2" on page 219), a comparator low output (if enabled), a capacitive sense greater-than comparator event, or a device reset event. In order to run Timer 3 in suspend mode, the timer must be configured to clock from the external clock source. When suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event (port match or Timer 2 overflow) was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** The device will still enter suspend mode if a wake source is "pending", and the device will not wake on such pending sources. It is important to ensure that the intended wake source will trigger after the device enters suspend mode. For example, if a CS0 conversion completes and the interrupt fires before the device is in suspend mode, that interrupt cannot trigger the wake event. Because port match events are level-sensitive, pre-existing port match events will trigger a wake, as long as the match condition is still present when the device enters suspend.

#### SFR Definition 20.1. PCON: Power Control

| Bit   | 7 | 6                                     | 5  | 4    | 3    | 2 | 1   | 0   |

|-------|---|---------------------------------------|----|------|------|---|-----|-----|

| Name  |   | · · · · · · · · · · · · · · · · · · · |    | STOP | IDLE |   |     |     |

| Туре  |   |                                       | R/ | W    |      |   | R/W | R/W |

| Reset | 0 | 0                                     | 0  | 0    | 0    | 0 | 0   | 0   |

SFR Address = 0x87

| Bit | Name    | Function                                                                                                                                                                                                                                                               |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.                                                                                                                                                                                                                                             |

|     |         | These are general purpose flags for use under software control.                                                                                                                                                                                                        |

| 1   | STOP    | Stop Mode Select.                                                                                                                                                                                                                                                      |

|     |         | Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.<br>1: CPU goes into Stop mode (internal oscillator stopped).                                                                                                                   |

| 0   | IDLE    | IDLE: Idle Mode Select.<br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts,<br>Serial Ports, and Analog Peripherals are still active.) |

#### SFR Definition 23.8. P0MDIN: Port 0 Input Mode

| Bit   | 7 | 6           | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-------------|---|----|---|---|---|---|--|

| Name  |   | P0MDIN[7:0] |   |    |   |   |   |   |  |

| Туре  |   |             |   | R/ | W |   |   |   |  |

| Reset | 1 | 1           | 1 | 1  | 1 | 1 | 1 | 1 |  |

SFR Address = 0xF1

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                                                                                                                                                                                                  |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. In order for the P0.n pin to be in analog mode, there <b>MUST be a '1' in the Port Latch register corresponding to that pin.</b><br>0: Corresponding P0.n pin is configured for analog mode.<br>1: Corresponding P0.n pin is not configured for analog mode. |

#### SFR Definition 23.9. P0MDOUT: Port 0 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P0MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xA4

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDOUT[7:0] | Output Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P0MDIN is logic 0.<br>0: Corresponding P0.n Output is open-drain.<br>1: Corresponding P0.n Output is push-pull. |

## C8051F80x-83x

overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 26.3.5. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods (as defined by the timer configured for the SMBus clock source). If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. A clock source is required for free timeout detection, even in a slave-only implementation.

#### 26.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

- Optional hardware recognition of slave address and automatic acknowledgement of address/data

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware acknowledgement is disabled, the point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e., sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e., receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement is enabled, these interrupts are always generated after the ACK cycle. See Section 26.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 26.4.2; Table 26.5 provides a quick SMB0CN decoding reference.

#### 26.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes, select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however, the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of the current transfer).

#### 26.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 26.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 26.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

#### 26.4.2.1. Software ACK Generation

When the EHACK bit in register SMB0ADM is cleared to 0, the firmware on the device must detect incoming slave addresses and ACK or NACK the slave address and incoming data bytes. As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

#### 26.4.2.2. Hardware ACK Generation

When the EHACK bit in register SMB0ADM is set to 1, automatic slave address recognition and ACK generation is enabled. More detail about automatic slave address recognition can be found in Section 26.4.3. As a receiver, the value currently specified by the ACK bit will be automatically sent on the bus during the ACK cycle of an incoming data byte. As a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. The ACKRQ bit is not used when hardware ACK generation is enabled. If a received slave address is NACKed by hardware, further slave events will be ignored until the next START is detected, and no interrupt will be generated.

Table 26.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 26.5 for SMBus status decoding using the SMB0CN register.

#### 27.1. Enhanced Baud Rate Generation

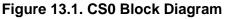

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 27.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 27.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "28.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 212). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK/4, SYSCLK/12, SYSCLK/48, the external oscillator clock/8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 27.1-A and Equation 27.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

#### Equation 27.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "28. Timers" on page 209. A quick reference for typical baud rates and system clock frequencies is given in Table 27.1 through Table 27.2. The internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

#### 28. Timers

Each MCU includes three counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and one is a 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 offers 16-bit and split 8-bit timer functionality with auto-reload. Additionally, Timer 2 offers the ability to be clocked from the external oscillator while the device is in Suspend mode, and can be used as a wake-up source. This allows for implementation of a very low-power system, including RTC capability.

| Timer 0 and Timer 1 Modes                  | Timer 2 Modes                       |  |

|--------------------------------------------|-------------------------------------|--|

| 13-bit counter/timer                       | 16-bit timer with auto-reload       |  |

| 16-bit counter/timer                       |                                     |  |

| 8-bit counter/timer with auto-reload       | - Two 8-bit timers with auto-reload |  |

| Two 8-bit counter/timers<br>(Timer 0 only) |                                     |  |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M– T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 28.1 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

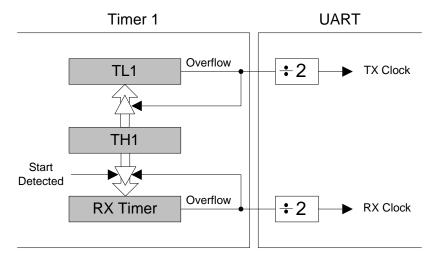

#### 28.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 28.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode. Timer 2 can also be used in capture mode to capture rising edges of the Comparator 0 output.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 28.5. Timer 2 8-Bit Mode Block Diagram