Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 20-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 20-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f806-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 23.1. Port I/O Modes of Operation                                           |     |

|----|-----------------------------------------------------------------------------|-----|

|    | 23.1.1. Port Pins Configured for Analog I/O                                 |     |

|    | 23.1.2. Port Pins Configured For Digital I/O                                |     |

|    | 23.1.3. Interfacing Port I/O to 5 V Logic                                   | 140 |

|    | 23.2. Assigning Port I/O Pins to Analog and Digital Functions               | 140 |

|    | 23.2.1. Assigning Port I/O Pins to Analog Functions                         | 140 |

|    | 23.2.2. Assigning Port I/O Pins to Digital Functions                        | 141 |

|    | 23.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions | 142 |

|    | 23.3. Priority Crossbar Decoder                                             |     |

|    | 23.4. Port I/O Initialization                                               |     |

|    | 23.5. Port Match                                                            |     |

|    | 23.6. Special Function Registers for Accessing and Configuring Port I/O     |     |

| 24 | Cyclic Redundancy Check Unit (CRC0)                                         |     |

|    | 24.1. 16-bit CRC Algorithm                                                  |     |

|    | 24.2. 32-bit CRC Algorithm.                                                 |     |

|    | 24.3. Preparing for a CRC Calculation                                       |     |

|    | 24.4. Performing a CRC Calculation                                          |     |

|    | 24.5. Accessing the CRC0 Result                                             |     |

|    | 24.6. CRC0 Bit Reverse Feature                                              |     |

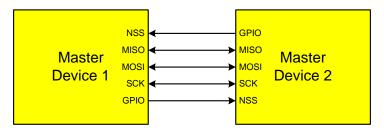

| 25 | Enhanced Serial Peripheral Interface (SPI0)                                 |     |

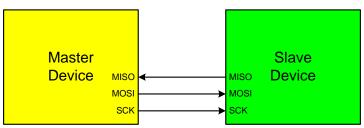

|    | 25.1. Signal Descriptions                                                   |     |

|    | 25.1.1. Master Out, Slave In (MOSI)                                         |     |

|    | 25.1.2. Master In, Slave Out (MISO)                                         |     |

|    | 25.1.3. Serial Clock (SCK)                                                  |     |

|    | 25.1.4. Slave Select (NSS)                                                  |     |

|    | 25.2. SPI0 Master Mode Operation                                            |     |

|    | 25.3. SPI0 Slave Mode Operation                                             |     |

|    | 25.4. SPI0 Interrupt Sources                                                |     |

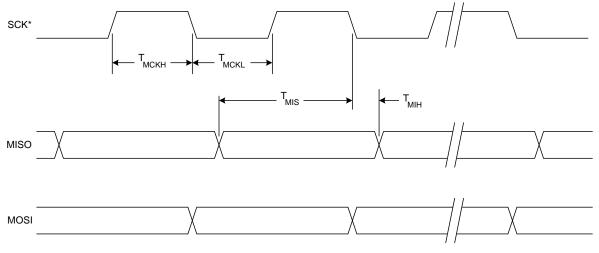

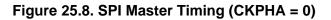

|    | 25.5. Serial Clock Phase and Polarity                                       | 171 |

|    | 25.6. SPI Special Function Registers                                        |     |

| 26 | SMBus                                                                       |     |

|    | 26.1. Supporting Documents                                                  |     |

|    | 26.2. SMBus Configuration                                                   |     |

|    | 26.3. SMBus Operation                                                       |     |

|    | 26.3.1. Transmitter Vs. Receiver.                                           | 182 |

|    | 26.3.2. Arbitration                                                         |     |

|    | 26.3.3. Clock Low Extension                                                 |     |

|    | 26.3.4. SCL Low Timeout                                                     |     |

|    | 26.3.5. SCL High (SMBus Free) Timeout                                       |     |

|    | 26.4. Using the SMBus                                                       |     |

|    | 26.4.1. SMBus Configuration Register                                        |     |

|    | 26.4.2. SMB0CN Control Register                                             |     |

|    | 26.4.2.1. Software ACK Generation                                           |     |

|    | 26.4.2.2. Hardware ACK Generation                                           |     |

|    | 26.4.3. Hardware Slave Address Recognition                                  |     |

|    | 5                                                                           |     |

## List of Figures

## 1. System Overview

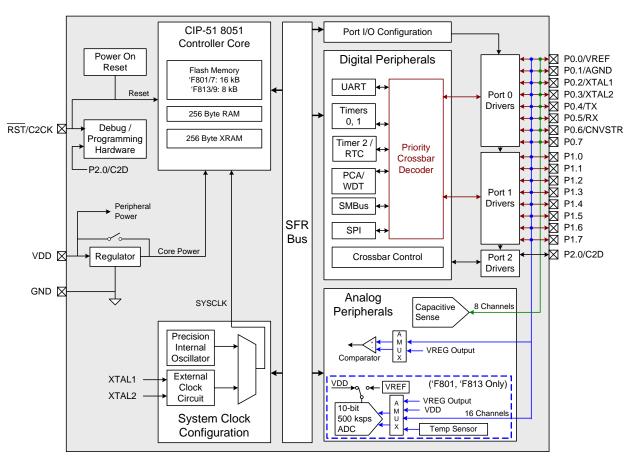

| Figure 1.1. C8051F800, C8051F806, C8051F812, C8051F818 Block Diagram ' |            |

|------------------------------------------------------------------------|------------|

| Figure 1.2. C8051F801, C8051F807, C8051F813, C8051F819 Block Diagram ' |            |

| Figure 1.3. C8051F802, C8051F808, C8051F814, C8051F820 Block Diagram ? |            |

| Figure 1.4. C8051F803, C8051F809, C8051F815, C8051F821 Block Diagram ? |            |

| Figure 1.5. C8051F804, C8051F810, C8051F816, C8051F822 Block Diagram 2 | 20         |

| Figure 1.6. C8051F805, C8051F811, C8051F817, C8051F823 Block Diagram 2 | 21         |

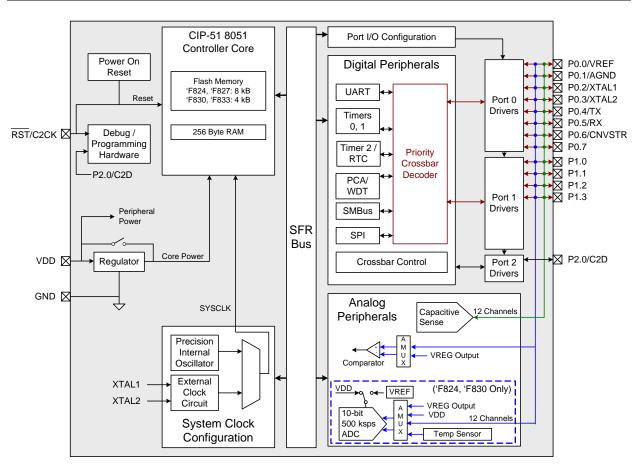

| Figure 1.7. C8051F824, C8051F827, C8051F830, C8051F833 Block Diagram 2 | 22         |

| Figure 1.8. C8051F825, C8051F828, C8051F831, C8051F834 Block Diagram 2 | 23         |

| Figure 1.9. C8051F826, C8051F829, C8051F832, C8051F835 Block Diagram 2 | 24         |

| 2. Ordering Information                                                |            |

| 3. Pin Definitions                                                     |            |

| Figure 3.1. QFN-20 Pinout Diagram (Top View)                           | 30         |

| Figure 3.2. QSOP-24 Pinout Diagram (Top View)                          |            |

| Figure 3.3. SOIC-16 Pinout Diagram (Top View)                          |            |

| 4. QFN-20 Package Specifications                                       |            |

| Figure 4.1. QFN-20 Package Drawing                                     | 33         |

| Figure 4.2. QFN-20 Recommended PCB Land Pattern                        |            |

| 5. QSOP-24 Package Specifications                                      |            |

| Figure 5.1. QSOP-24 Package Drawing                                    | 35         |

| Figure 5.2. QSOP-24 PCB Land Pattern                                   |            |

| 6. SOIC-16 Package Specifications                                      |            |

| Figure 6.1. SOIC-16 Package Drawing                                    | 37         |

| Figure 6.2. SOIC-16 PCB Land Pattern                                   |            |

| 7. Electrical Characteristics                                          | 50         |

| 8. 10-Bit ADC (ADC0)                                                   |            |

| Figure 8.1. ADC0 Functional Block Diagram                              | 46         |

| Figure 8.2. 10-Bit ADC Track and Conversion Example Timing             |            |

| Figure 8.3. ADC0 Equivalent Input Circuits                             |            |

| Figure 8.4. ADC Window Compare Example: Right-Justified Data           |            |

|                                                                        |            |

| Figure 8.5. ADC Window Compare Example: Left-Justified Data            |            |

| 9. Temperature Sensor                                                  | 00         |

|                                                                        | 50         |

| Figure 9.1. Temperature Sensor Transfer Function                       |            |

| Figure 9.2. Temperature Sensor Error with 1-Point Calibration at 0 °C  | 29         |

| 10. Voltage and Ground Reference Options                               | ~~         |

| Figure 10.1. Voltage Reference Functional Block Diagram                | <u>э</u> О |

| 11. Voltage Regulator (REG0)                                           |            |

| 12. Comparator0                                                        | ~ -        |

| Figure 12.1. Comparator0 Functional Block Diagram                      | 55         |

| Figure 12.2. Comparator Hysteresis Plot                                |            |

| Figure 12.3. Comparator Input Multiplexer Block Diagram                | 69         |

| 13. Capacitive Sense (CS0)                                             |            |

Figure 1.2. C8051F801, C8051F807, C8051F813, C8051F819 Block Diagram

Figure 1.7. C8051F824, C8051F827, C8051F830, C8051F833 Block Diagram

## 3. Pin Definitions

| Name            | Pin<br>QSOP-24 | Pin<br>QFN-20 | Pin<br>SOIC-16 | Туре             | Description                                                                                                                                                                                |

|-----------------|----------------|---------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | 5              | 2             | 4              |                  | Ground.<br>This ground connection is required. The center<br>pad may optionally be connected to ground as<br>well on the QFN-20 packages.                                                  |

| V <sub>DD</sub> | 6              | 3             | 5              |                  | Power Supply Voltage.                                                                                                                                                                      |

| RST/            | 7              | 4             | 6              | D I/O            | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor. An external source can initiate a system reset by driving this pin low for at least 10 $\mu$ s.                       |

| C2CK            |                |               |                | D I/O            | Clock signal for the C2 Debug Interface.                                                                                                                                                   |

| P2.0/           | 8              | 5             | 7              | D I/O            | Bi-directional data signal for the C2 Debug Inter-<br>face. Shared with P2.0 on 20-pin packaging and<br>P2.4 on 24-pin packaging.                                                          |

| C2D             |                |               |                | D I/O            | Bi-directional data signal for the C2 Debug Inter-<br>face. Shared with P2.0 on 20-pin packaging and<br>P2.4 on 24-pin packaging.                                                          |

| P0.0/           | 4              | 1             | 3              | D I/O or<br>A In | Port 0.0.                                                                                                                                                                                  |

| VREF            |                |               |                | A In             | External VREF input.                                                                                                                                                                       |

| P0.1            | 3              | 20            | 2              | D I/O or<br>A In | Port 0.1.                                                                                                                                                                                  |

| P0.2/           | 2              | 19            | 1              | D I/O or<br>A In | Port 0.2.                                                                                                                                                                                  |

| XTAL1           |                |               |                | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator.                                                                                               |

| P0.3/           | 23             | 18            | 16             | D I/O or<br>A In | Port 0.3.                                                                                                                                                                                  |

| XTAL2           |                |               |                | A I/O or<br>D In | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. |

| P0.4            | 22             | 17            | 15             | D I/O or<br>A In | Port 0.4.                                                                                                                                                                                  |

Table 3.1. Pin Definitions for the C8051F80x-83x

## SFR Definition 13.2. CS0CF: Capacitive Sense Configuration

| Bit   | 7 | 6   | 5          | 4   | 3 | 2   | 1          | 0   |

|-------|---|-----|------------|-----|---|-----|------------|-----|

| Name  |   |     | CS0CM[2:0] |     |   | (   | CS0ACU[2:0 | ]   |

| Туре  | R | R/W | R/W        | R/W | R | R/W | R/W        | R/W |

| Reset | 0 | 0   | 0          | 0   | 0 | 0   | 0          | 0   |

SFR Address = 0x9E

| Bit | Name        | Description                                                                            |

|-----|-------------|----------------------------------------------------------------------------------------|

| 7   | Unused      | Read = 0b; Write = Don't care                                                          |

| 6:4 | CS0CM[2:0]  | CS0 Start of Conversion Mode Select.                                                   |

|     |             | 000: Conversion initiated on every write of 1 to CS0BUSY.                              |

|     |             | 001: Conversion initiated on overflow of Timer 0.                                      |

|     |             | 010: Conversion initiated on overflow of Timer 2.                                      |

|     |             | 011: Conversion initiated on overflow of Timer 1.                                      |

|     |             | 100: Reserved.                                                                         |

|     |             | 101: Reserved.                                                                         |

|     |             | 110: Conversion initiated continuously after writing 1 to CS0BUSY.                     |

|     |             | 111: Auto-scan enabled, conversions initiated continuously after writing 1 to CS0BUSY. |

| 3   | Unused      | Read = 0b; Write = Don't care                                                          |

| 2:0 | CS0ACU[2:0] | CS0 Accumulator Mode Select.                                                           |

|     |             | 000: Accumulate 1 sample.                                                              |

|     |             | 001: Accumulate 4 samples.                                                             |

|     |             | 010: Accumulate 8 samples.                                                             |

|     |             | 011: Accumulate 16 samples                                                             |

|     |             | 100: Accumulate 32 samples.                                                            |

|     |             | 101: Accumulate 64 samples.                                                            |

|     |             | 11x: Reserved.                                                                         |

| Mnemonic              | onic Description                         |   | Clock<br>Cycles |

|-----------------------|------------------------------------------|---|-----------------|

| Arithmetic Operations | S                                        | I | I               |

| ADD A, Rn             | Add register to A                        | 1 | 1               |

| ADD A, direct         | Add direct byte to A                     | 2 | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1 | 2               |

| ADD A, #data          | Add immediate to A                       | 2 | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1 | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2 | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1 | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2 | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1 | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2 | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1 | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2 | 2               |

| INC A                 | Increment A                              | 1 | 1               |

| INC Rn                | Increment register                       | 1 | 1               |

| INC direct            | Increment direct byte                    | 2 | 2               |

| INC @Ri               | Increment indirect RAM                   | 1 | 2               |

| DEC A                 | Decrement A                              | 1 | 1               |

| DEC Rn                | Decrement register                       | 1 | 1               |

| DEC direct            | Decrement direct byte                    | 2 | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1 | 2               |

| INC DPTR              | Increment Data Pointer                   | 1 | 1               |

| MUL AB                | Multiply A and B                         | 1 | 4               |

| DIV AB                | Divide A by B                            | 1 | 8               |

| DA A                  | Decimal adjust A                         | 1 | 1               |

| Logical Operations    | ,                                        |   |                 |

| ANL A, Rn             | AND Register to A                        | 1 | 1               |

| ANL A, direct         | AND direct byte to A                     | 2 | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1 | 2               |

| ANL A, #data          | AND immediate to A                       | 2 | 2               |

| ANL direct, A         | AND A to direct byte                     | 2 | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3 | 3               |

| ORL A, Rn             | OR Register to A                         | 1 | 1               |

| ORL A, direct         | OR direct byte to A                      | 2 | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1 | 2               |

| ORL A, #data          | OR immediate to A                        | 2 | 2               |

| ORL direct, A         | OR A to direct byte                      | 2 | 2               |

| ORL direct, #data     | OR immediate to direct byte              | 3 | 3               |

| XRL A, Rn             | Exclusive-OR Register to A               | 1 | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2 | 2               |

| XRL A, @Ri            | Exclusive-OR indirect RAM to A           | 1 | 2               |

| XRL A, #data          | Exclusive-OR immediate to A              | 2 | 2               |

| XRL direct, A         | Exclusive-OR A to direct byte            | 2 | 2               |

Table 14.1. CIP-51 Instruction Set Summary

### 14.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

### SFR Definition 14.1. DPL: Data Pointer Low Byte

| Bit           | 7             | 6                 | 5                | 4             | 3           | 2   | 1 | 0 |  |

|---------------|---------------|-------------------|------------------|---------------|-------------|-----|---|---|--|

| Name DPL[7:0] |               |                   |                  |               |             |     |   |   |  |

| Туре          | Type R/W      |                   |                  |               |             |     |   |   |  |

| Rese          | et O          | 0                 | 0                | 0             | 0           | 0   | 0 | 0 |  |

| SFR A         | Address = 0x8 | 2                 |                  |               |             |     |   |   |  |

| Bit           | Name          | ame Function      |                  |               |             |     |   |   |  |

| 7:0           | DPL[7:0]      | Data Pointer Low. |                  |               |             |     |   |   |  |

|               |               | The DPL reg       | gister is the lo | ow byte of th | e 16-bit DP | TR. |   |   |  |

### SFR Definition 14.2. DPH: Data Pointer High Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|----------|---|---|---|---|---|---|---|--|

| Name  | DPH[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W      |   |   |   |   |   |   |   |  |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0x83

| Bit | Name     | Function                                              |

|-----|----------|-------------------------------------------------------|

| 7:0 | DPH[7:0] | Data Pointer High.                                    |

|     |          | The DPH register is the high byte of the 16-bit DPTR. |

### 21.2. Power-Fail Reset / V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 21.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled and selected as a reset source after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the  $V_{DD}$  monitor and configuring it as a reset source from a disabled state is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- 2. If necessary, wait for the  $V_{DD}$  monitor to stabilize.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 21.2 for V<sub>DD</sub> monitor timing; note that the power-on-reset delay is not incurred after a V<sub>DD</sub> monitor reset. See Section "7. Electrical Characteristics" on page 39 for complete electrical characteristics of the V<sub>DD</sub> monitor.

## SFR Definition 22.4. OSCXCN: External Oscillator Control

| Bit   | 7      | 6 | 5          | 4  | 3 | 2 | 1         | 0 |

|-------|--------|---|------------|----|---|---|-----------|---|

| Name  | XTLVLD | Х | (OSCMD[2:0 | )] |   |   | XFCN[2:0] |   |

| Туре  | R      |   | R/W        |    | R |   | R/W       |   |

| Reset | 0      | 0 | 0          | 0  | 0 | 0 | 0         | 0 |

SFR Address = 0xB1

| Bit | Name        |         |                                                                                                               | Function                                  |                 |  |  |  |  |  |  |

|-----|-------------|---------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|--|

| 7   | XTLVLD      | Crystal | Oscillator Valid Flag.                                                                                        |                                           |                 |  |  |  |  |  |  |

|     |             | •       | nly when XOSCMD = 11                                                                                          |                                           |                 |  |  |  |  |  |  |

|     |             | -       | Crystal Oscillator is unused or not yet stable.                                                               |                                           |                 |  |  |  |  |  |  |

|     |             | ,       | Crystal Oscillator is running and stable.                                                                     |                                           |                 |  |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Selec                                                                                       | ct.                                       |                 |  |  |  |  |  |  |

|     |             |         | ernal Oscillator circuit of                                                                                   |                                           |                 |  |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                                                                        |                                           |                 |  |  |  |  |  |  |

|     |             |         | ernal CMOS Clock Mode                                                                                         | e with divide by 2 stage.                 |                 |  |  |  |  |  |  |

|     |             |         | Oscillator Mode.                                                                                              |                                           |                 |  |  |  |  |  |  |

|     |             |         | pacitor Oscillator Mode.                                                                                      |                                           |                 |  |  |  |  |  |  |

|     |             | -       | vstal Oscillator Mode.<br>vstal Oscillator Mode with                                                          | divida by 2 staga                         |                 |  |  |  |  |  |  |

|     |             |         |                                                                                                               | i ulviue by 2 stage.                      |                 |  |  |  |  |  |  |

| 3   | Unused      |         | 0; Write = Don't Care                                                                                         |                                           |                 |  |  |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | I Oscillator Frequency                                                                                        |                                           |                 |  |  |  |  |  |  |

|     |             |         | -                                                                                                             | uency for Crystal or RC r                 | node.           |  |  |  |  |  |  |

|     |             |         | ording to the desired K F                                                                                     |                                           |                 |  |  |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                                                                                  | RC Mode                                   | C Mode          |  |  |  |  |  |  |

|     |             | 000     | f ≤ 32 kHz                                                                                                    | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                                                                           | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |  |

|     |             | 010     | 84 kHz < f ≤ 225 kHz                                                                                          | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |  |

|     |             | 011     | 011 225 kHz < f $\leq$ 590 kHz 100 kHz < f $\leq$ 200 kHz K Factor = 22                                       |                                           |                 |  |  |  |  |  |  |

|     |             | 100     | $100  590 \text{ kHz} < f \le 1.5 \text{ MHz}  200 \text{ kHz} < f \le 400 \text{ kHz}  \text{K Factor} = 65$ |                                           |                 |  |  |  |  |  |  |

|     |             | 101     | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                                                                       | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |  |

|     |             | 110     | $4 \text{ MHz} < f \le 10 \text{ MHz}$                                                                        | 800 kHz $<$ f $\leq$ 1.6 MHz              | K Factor = 664  |  |  |  |  |  |  |

|     |             | 111     | 10 MHz < f ≤ 30 MHz                                                                                           | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |  |

| Analog Function                                       | Potentially Assignable<br>Port Pins | SFR(s) used for<br>Assignment  |  |

|-------------------------------------------------------|-------------------------------------|--------------------------------|--|

| ADC Input                                             | P0.0-P1.7                           | ADC0MX, PnSKIP,<br>PnMDIN      |  |

| Comparator0 Input                                     | P0.0-P1.7                           | CPT0MX, PnSKIP,<br>PnMDIN      |  |

| CS0 Input                                             | P0.0–P1.7                           | CS0MX, CS0SS,<br>CS0SE, PnMDIN |  |

| Voltage Reference (VREF0)                             | P0.0                                | REF0CN, P0SKIP,<br>PnMDIN      |  |

| Ground Reference (AGND)                               | P0.1                                | REF0CN, P0SKIP                 |  |

| External Oscillator in Crystal Mode (XTAL1)           | P0.2                                | OSCXCN, P0SKIP,<br>P0MDIN      |  |

| External Oscillator in RC, C, or Crystal Mode (XTAL2) | P0.3                                | OSCXCN, POSKIP,<br>POMDIN      |  |

Table 23.1. Port I/O Assignment for Analog Functions

#### 23.2.2. Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital func-tions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 23.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

| Special<br>Function<br>Signals<br>(Control<br>Signals)<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK) | P0.0 Skipped    | AGND AGND | P0.2 Skipped XTAL1 N | P0.3 Skipped |   | 5 | CNVSTR 9 | 7 |   |   | 2 | 3   | 4 <sup>1</sup> | 5 <sup>1</sup> | 6 <sup>1</sup> | <b>7</b> <sup>1</sup> | Signal Unavailable to Crossbar |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|----------------------|--------------|---|---|----------|---|---|---|---|-----|----------------|----------------|----------------|-----------------------|--------------------------------|

| Function<br>SignalsTX0RX0RX0SCKMISOMOSINSS2SDASCLCP0ACP0ASYSCLKCEX0CEX1CEX2ECIT1Pin Skip<br>SettingsIn this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Skipped         | AGND      |                      | Skipped      |   |   | CNVSTR   |   |   |   |   |     |                |                |                |                       | Crossbar                       |

| RX0<br>SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |     |                |                |                |                       | Crossbar                       |

| SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |     |                |                |                |                       | Crossbar                       |

| MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |     |                |                |                |                       | Crossbar                       |

| MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |     |                |                |                |                       | Crossbar                       |

| NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |     |                |                |                |                       | Crossl                         |

| SDA<br>SCL<br>CP00<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |     |                |                |                |                       | ō                              |

| SCL<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |     |                |                |                |                       |                                |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skippe     |           | P0.2 Skippe          | P0.3 Skippe  |   |   |          |   |   |   |   |     |                |                |                |                       | e to                           |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Ski        |           | P0.2 Ski             | P0.3 Ski     |   |   |          |   |   |   |   |     |                |                |                |                       | able                           |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0            |           | P0.2                 | P0.3         |   |   |          |   |   |   |   |     |                |                |                |                       | vail                           |