# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                  |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f807-gu |

|                            |                                                                |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 23.1. Port I/O Modes of Operation                                           |     |

|----|-----------------------------------------------------------------------------|-----|

|    | 23.1.1. Port Pins Configured for Analog I/O                                 |     |

|    | 23.1.2. Port Pins Configured For Digital I/O                                |     |

|    | 23.1.3. Interfacing Port I/O to 5 V Logic                                   | 140 |

|    | 23.2. Assigning Port I/O Pins to Analog and Digital Functions               | 140 |

|    | 23.2.1. Assigning Port I/O Pins to Analog Functions                         | 140 |

|    | 23.2.2. Assigning Port I/O Pins to Digital Functions                        | 141 |

|    | 23.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions | 142 |

|    | 23.3. Priority Crossbar Decoder                                             |     |

|    | 23.4. Port I/O Initialization                                               |     |

|    | 23.5. Port Match                                                            |     |

|    | 23.6. Special Function Registers for Accessing and Configuring Port I/O     |     |

| 24 | Cyclic Redundancy Check Unit (CRC0)                                         |     |

|    | 24.1. 16-bit CRC Algorithm                                                  |     |

|    | 24.2. 32-bit CRC Algorithm.                                                 |     |

|    | 24.3. Preparing for a CRC Calculation                                       |     |

|    | 24.4. Performing a CRC Calculation                                          |     |

|    | 24.5. Accessing the CRC0 Result                                             |     |

|    | 24.6. CRC0 Bit Reverse Feature                                              |     |

| 25 | Enhanced Serial Peripheral Interface (SPI0)                                 |     |

|    | 25.1. Signal Descriptions                                                   |     |

|    | 25.1.1. Master Out, Slave In (MOSI)                                         |     |

|    | 25.1.2. Master In, Slave Out (MISO)                                         |     |

|    | 25.1.3. Serial Clock (SCK)                                                  |     |

|    | 25.1.4. Slave Select (NSS)                                                  |     |

|    | 25.2. SPI0 Master Mode Operation                                            |     |

|    | 25.3. SPI0 Slave Mode Operation                                             |     |

|    | 25.4. SPI0 Interrupt Sources                                                |     |

|    | 25.5. Serial Clock Phase and Polarity                                       | 171 |

|    | 25.6. SPI Special Function Registers                                        |     |

| 26 | SMBus                                                                       |     |

|    | 26.1. Supporting Documents                                                  |     |

|    | 26.2. SMBus Configuration                                                   |     |

|    | 26.3. SMBus Operation                                                       |     |

|    | 26.3.1. Transmitter Vs. Receiver.                                           | 182 |

|    | 26.3.2. Arbitration                                                         |     |

|    | 26.3.3. Clock Low Extension                                                 |     |

|    | 26.3.4. SCL Low Timeout                                                     |     |

|    | 26.3.5. SCL High (SMBus Free) Timeout                                       |     |

|    | 26.4. Using the SMBus                                                       |     |

|    | 26.4.1. SMBus Configuration Register                                        |     |

|    | 26.4.2. SMB0CN Control Register                                             |     |

|    | 26.4.2.1. Software ACK Generation                                           |     |

|    | 26.4.2.2. Hardware ACK Generation                                           |     |

|    | 26.4.3. Hardware Slave Address Recognition                                  |     |

|    | 5                                                                           |     |

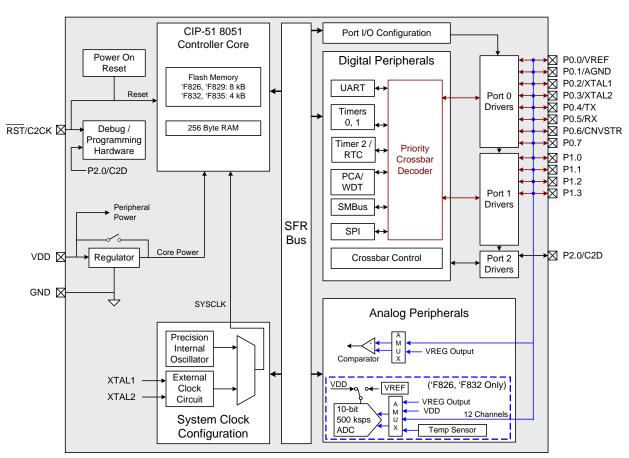

Figure 1.9. C8051F826, C8051F829, C8051F832, C8051F835 Block Diagram

## SFR Definition 8.7. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit               | 7                  | 6                                         | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|--------------------|-------------------------------------------|----------|---|---|---|---|---|--|--|

| Name ADC0LTH[7:0] |                    |                                           |          |   |   |   |   |   |  |  |

| Туре              | 9                  | R/W                                       |          |   |   |   |   |   |  |  |

| Rese              | et O               | 0                                         | 0        | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A             | SFR Address = 0xC6 |                                           |          |   |   |   |   |   |  |  |

| Bit               | Name               |                                           | Function |   |   |   |   |   |  |  |

| 7:0               | ADC0LTH[7:0        | ADC0 Less-Than Data Word High-Order Bits. |          |   |   |   |   |   |  |  |

## SFR Definition 8.8. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit               | 7                  | 6       | 5                                        | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|--------------------|---------|------------------------------------------|---|---|---|---|---|--|--|

| Name ADC0LTL[7:0] |                    |         |                                          |   |   |   |   |   |  |  |

| Туре              | 9                  | R/W     |                                          |   |   |   |   |   |  |  |

| Rese              | et 0               | 0       | 0                                        | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A             | SFR Address = 0xC5 |         |                                          |   |   |   |   |   |  |  |

| Bit               | Name               |         | Function                                 |   |   |   |   |   |  |  |

| 7:0               | ADC0LTL[7:0]       | ADC0 Le | ADC0 Less-Than Data Word Low-Order Bits. |   |   |   |   |   |  |  |

## 12. Comparator0

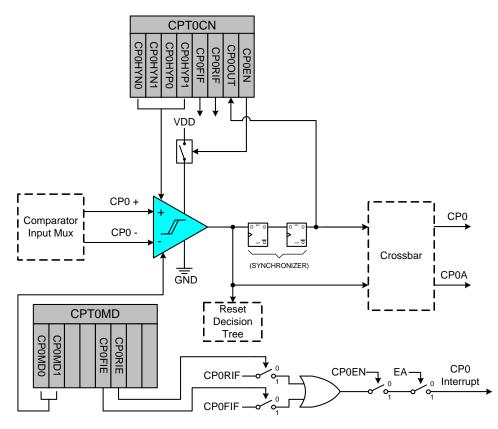

C8051F80x-83x devices include an on-chip programmable voltage comparator, Comparator0, shown in Figure 12.1.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output with the device in STOP mode. When assigned to a Port pin, the Comparator output may be configured as open drain or push-pull (see Section "23.4. Port I/O Initialization" on page 147). Comparator0 may also be used as a reset source (see Section "21.5. Comparator0 Reset" on page 127).

The Comparator0 inputs are selected by the comparator input multiplexer, as detailed in Section "12.1. Comparator Multiplexer" on page 69.

Figure 12.1. Comparator0 Functional Block Diagram

The Comparator output can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, the Comparator output is available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and the power supply to the comparator is turned off. See Section "23.3. Priority Crossbar Decoder" on page 143 for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Section "7. Electrical Characteristics" on page 39.

## SFR Definition 13.2. CS0CF: Capacitive Sense Configuration

| Bit   | 7 | 6          | 5   | 4   | 3 | 2   | 1          | 0   |

|-------|---|------------|-----|-----|---|-----|------------|-----|

| Name  |   | CS0CM[2:0] |     |     |   | (   | CS0ACU[2:0 | ]   |

| Туре  | R | R/W        | R/W | R/W | R | R/W | R/W        | R/W |

| Reset | 0 | 0          | 0   | 0   | 0 | 0   | 0          | 0   |

SFR Address = 0x9E

| Bit | Name                                              | Description                                                                            |  |  |  |  |  |  |

|-----|---------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7   | Unused                                            | Read = 0b; Write = Don't care                                                          |  |  |  |  |  |  |

| 6:4 | CS0CM[2:0]                                        | CS0 Start of Conversion Mode Select.                                                   |  |  |  |  |  |  |

|     |                                                   | 000: Conversion initiated on every write of 1 to CS0BUSY.                              |  |  |  |  |  |  |

|     |                                                   | 001: Conversion initiated on overflow of Timer 0.                                      |  |  |  |  |  |  |

|     |                                                   | 010: Conversion initiated on overflow of Timer 2.                                      |  |  |  |  |  |  |

|     | 011: Conversion initiated on overflow of Timer 1. |                                                                                        |  |  |  |  |  |  |

|     | 100: Reserved.                                    |                                                                                        |  |  |  |  |  |  |

|     |                                                   | 101: Reserved.                                                                         |  |  |  |  |  |  |

|     |                                                   | 110: Conversion initiated continuously after writing 1 to CS0BUSY.                     |  |  |  |  |  |  |

|     |                                                   | 111: Auto-scan enabled, conversions initiated continuously after writing 1 to CS0BUSY. |  |  |  |  |  |  |

| 3   | Unused                                            | Read = 0b; Write = Don't care                                                          |  |  |  |  |  |  |

| 2:0 | CS0ACU[2:0]                                       | CS0 Accumulator Mode Select.                                                           |  |  |  |  |  |  |

|     |                                                   | 000: Accumulate 1 sample.                                                              |  |  |  |  |  |  |

|     |                                                   | 001: Accumulate 4 samples.                                                             |  |  |  |  |  |  |

|     |                                                   | 010: Accumulate 8 samples.                                                             |  |  |  |  |  |  |

|     |                                                   | 011: Accumulate 16 samples                                                             |  |  |  |  |  |  |

|     |                                                   | 100: Accumulate 32 samples.                                                            |  |  |  |  |  |  |

|     |                                                   | 101: Accumulate 64 samples.                                                            |  |  |  |  |  |  |

|     |                                                   | 11x: Reserved.                                                                         |  |  |  |  |  |  |

| Mnemonic             | Description                                                              | Bytes | Clock<br>Cycles |

|----------------------|--------------------------------------------------------------------------|-------|-----------------|

| ANL C, bit           | AND direct bit to Carry                                                  | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry                                    | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                                                   | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                                     | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                                                 | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                                                 | 2     | 2               |

| JC rel               | Jump if Carry is set                                                     | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                                                 | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                                                | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set<br>Jump if direct bit is set and clear bit | 3     | 3/4             |

| JBC bit, rel         | 3                                                                        | 3/4   |                 |

| Program Branching    |                                                                          |       |                 |

| ACALL addr11         | 2                                                                        | 3     |                 |

| LCALL addr16         | Long subroutine call                                                     | 3     | 4               |

| RET                  | Return from subroutine                                                   | 1     | 5               |

| RETI                 | Return from interrupt                                                    | 1     | 5               |

| AJMP addr11          | Absolute jump                                                            | 2     | 3               |

| LJMP addr16          | Long jump                                                                | 3     | 4               |

| SJMP rel             | Short jump (relative address)                                            | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                                           | 1     | 3               |

| JZ rel               | Jump if A equals zero                                                    | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                                            | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal                           | 3     | 4/5             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal                             | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal                      | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal                      | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero                                  | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero                               | 3     | 3/4             |

| NOP                  | No operation                                                             | 1     | 1               |

## **16. In-System Device Identification**

The C8051F80x-83x has SFRs that identify the device family and derivative. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically changing functionality to suit the capabilities of that MCU.

In order for firmware to identify the MCU, it must read three SFRs. HWID describes the MCU's family, DERIVID describes the specific derivative within that device family, and REVID describes the hardware revision of the MCU.

#### SFR Definition 16.1. HWID: Hardware Identification Byte

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------|---|---|---|---|---|---|---|--|

| Name  | HWID[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R         | R | R | R | R | R | R | R |  |

| Reset | 0         | 0 | 1 | 0 | 0 | 0 | 1 | 1 |  |

#### SFR Address = 0xB5

| Bit | Name      | Description                                                                         |

|-----|-----------|-------------------------------------------------------------------------------------|

| 7:0 | HWID[7:0] | Hardware Identification Byte.                                                       |

|     |           | Describes the MCU family.<br>0x23: Devices covered in this document (C8051F80x-83x) |

### Table 17.2. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                        | Page |

|----------|---------|------------------------------------|------|

| ACC      | 0xE0    | Accumulator                        | 89   |

| ADC0CF   | 0xBC    | ADC0 Configuration                 | 50   |

| ADC0CN   | 0xE8    | ADC0 Control                       | 52   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High     | 53   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low      | 53   |

| ADC0H    | 0xBE    | ADC0 High                          | 51   |

| ADC0L    | 0xBD    | ADC0 Low                           | 51   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High   | 54   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low    | 54   |

| ADC0MX   | 0xBB    | AMUX0 Multiplexer Channel Select   | 57   |

| В        | 0xF0    | B Register                         | 90   |

| CKCON    | 0x8E    | Clock Control                      | 210  |

| CLKSEL   | 0xA9    | Clock Select                       | 210  |

| CPT0CN   | 0x9B    | Comparator0 Control                | 67   |

| CPT0MD   | 0x9D    | Comparator0 Mode Selection         | 68   |

| CPT0MX   | 0x9F    | Comparator0 MUX Selection          | 70   |

| CRC0AUTO | 0xD2    | CRC0 Automatic Control Register    | 165  |

| CRC0CN   | 0xCE    | CRC0 Control                       | 163  |

| CRC0CNT  | 0xD3    | CRC0 Automatic Flash Sector Count  | 165  |

| CRC0DATA | 0xDE    | CRC0 Data Output                   | 164  |

| CRC0FLIP | 0xCF    | CRC0 Bit Flip                      | 166  |

| CRCOIN   | 0xDD    | CRC Data Input                     | 164  |

| CS0THH   | 0x97    | CS0 Digital Compare Threshold High | 79   |

| CS0THL   | 0x96    | CS0 Digital Compare Threshold High | 79   |

| CSOCN    | 0xB0    | CS0 Control                        | 75   |

| CS0DH    | 0xAC    | CS0 Data High                      | 77   |

| CS0DL    | 0xAB    | CS0 Data Low                       | 77   |

## SFR Definition 18.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7        | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|----------|----------|------|-------|-------|--------|------|-------|

| Name  | Reserved | Reserved | ECP0 | EADC0 | EPCA0 | EWADC0 | EMAT | ESMB0 |

| Туре  | W        | W        | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0        | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

SFR Address = 0xE6

| Bit | Name     | Function                                                                                                                                                                                                                                                                          |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Must write 0.                                                                                                                                                                                                                                                                     |

| 6   | Reserved | Reserved.                                                                                                                                                                                                                                                                         |

|     |          | Must write 0.                                                                                                                                                                                                                                                                     |

| 5   | ECP0     | <ul> <li>Enable Comparator0 (CP0) Interrupt.</li> <li>This bit sets the masking of the CP0 rising edge or falling edge interrupt.</li> <li>0: Disable CP0 interrupts.</li> <li>1: Enable interrupt requests generated by the CP0RIF and CP0FIF flags.</li> </ul>                  |

| 4   | EADC0    | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 3   | EPCA0    | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EWADC0   | <ul> <li>Enable Window Comparison ADC0 interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 1   | EMAT     | Enable Port Match Interrupts.<br>This bit sets the masking of the Port Match event interrupt.<br>0: Disable all Port Match interrupts.<br>1: Enable interrupt requests generated by a Port Match.                                                                                 |

| 0   | ESMB0    | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

## 20. Power Management Modes

The C8051F80x-83x devices have three software programmable power management modes: Idle, Stop, and Suspend. Idle mode and Stop mode are part of the standard 8051 architecture, while Suspend mode is an enhanced power-saving mode implemented by the high-speed oscillator peripheral.

Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Suspend mode is similar to Stop mode in that the internal oscillator and CPU are halted, but the device can wake on events such as a Port Mismatch, Comparator low output, or a Timer 3 overflow. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode and Suspend mode consume the least power because the majority of the device is shut down with no clocks active. SFR Definition 20.1 describes the Power Control Register (PCON) used to control the C8051F80x-83x's Stop and Idle power management modes. Suspend mode is controlled by the SUSPEND bit in the OSCICN register (SFR Definition 22.3).

Although the C8051F80x-83x has Idle, Stop, and Suspend modes available, more control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off oscillators lowers power consumption considerably, at the expense of reduced functionality.

#### 20.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the hardware to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has two or more opcode bytes, for example:

| // in `C':<br>PCON  = 0x01;<br>PCON = PCON;        | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "29.4. Watchdog Timer Mode" on page 236 for more information on the use and configuration of the WDT.

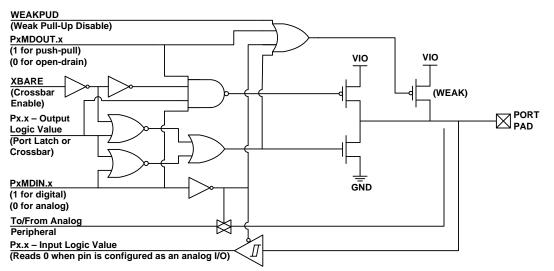

### 23.1. Port I/O Modes of Operation

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 23.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN and PnMDOUT registers. Port pin P2.0 can be configured by software for digital I/O using the P2MDOUT register. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled. Until the crossbar is enabled (XBARE = 1), both the high and low port I/O drive circuits are explicitly disabled on all crossbar pins.

#### 23.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, Capacitive Sense input, external oscillator input/output, VREF output, or AGND connection should be configured for analog I/O (PnMDIN.n = 0, Pn.n = 1). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. To prevent the low port I/o drive circuit from pulling the pin low, a '1' should be written to the corresponding port latch (Pn.n = 1). Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital I/O may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 23.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

#### 26.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 26.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 26.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

#### 26.4.2.1. Software ACK Generation

When the EHACK bit in register SMB0ADM is cleared to 0, the firmware on the device must detect incoming slave addresses and ACK or NACK the slave address and incoming data bytes. As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

#### 26.4.2.2. Hardware ACK Generation

When the EHACK bit in register SMB0ADM is set to 1, automatic slave address recognition and ACK generation is enabled. More detail about automatic slave address recognition can be found in Section 26.4.3. As a receiver, the value currently specified by the ACK bit will be automatically sent on the bus during the ACK cycle of an incoming data byte. As a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. The ACKRQ bit is not used when hardware ACK generation is enabled. If a received slave address is NACKed by hardware, further slave events will be ignored until the next START is detected, and no interrupt will be generated.

Table 26.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 26.5 for SMBus status decoding using the SMB0CN register.

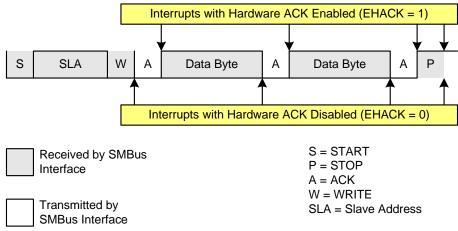

#### 26.5.3. Write Sequence (Slave)

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 26.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the "data byte transferred" interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 26.7. Typical Slave Write Sequence

Table 26.5. SMBus Status Decoding With Hardware ACK Generation Disabled (EHACK = 0)

|                           | Val              | ues   | Rea     | d   |                                                 |                                                                                                |                                             | lues<br>Vrite |     | itus<br>ected                  |      |

|---------------------------|------------------|-------|---------|-----|-------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------|---------------|-----|--------------------------------|------|

| Mode                      | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                             | Typical Response Options                                                                       | STA                                         | STO           | ACK | Next Status<br>Vector Expected |      |

|                           | 1110             | 0     | 0       | х   | A master START was gener-<br>ated.              | Load slave address + R/W into SMB0DAT.                                                         | 0                                           | 0             | Х   | 1100                           |      |

|                           |                  | _     | 0       | 0   | A master data or address byte                   | Set STA to restart transfer.                                                                   | 1                                           | 0             | Х   | 1110                           |      |

| tter                      |                  | 0     | 0       | 0   | was transmitted; NACK received.                 | Abort transfer.                                                                                | 0                                           | 1             | Х   | —                              |      |

| <b>Master Transmitter</b> |                  |       |         |     |                                                 | Load next data byte into SMB0DAT.                                                              | 0                                           | 0             | Х   | 1100                           |      |

| Tr                        | 1100             |       |         |     |                                                 | End transfer with STOP.                                                                        | 0                                           | 1             | Х   | —                              |      |

| lastei                    | 1100             | 0     | 0       | 1   | was transmitted; ACK received.                  | End transfer with STOP and start another transfer.                                             | 1                                           | 1             | Х   | —                              |      |

|                           |                  |       |         |     |                                                 | Send repeated START.                                                                           | 1                                           | 0             | Х   | 1110                           |      |

|                           |                  |       |         |     |                                                 | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT).           | 0                                           | 0             | Х   | 1000                           |      |

|                           |                  |       |         |     |                                                 |                                                                                                | Acknowledge received byte;<br>Read SMB0DAT. | 0             | 0   | 1                              | 1000 |

|                           |                  |       |         |     |                                                 | Send NACK to indicate last byte, and send STOP.                                                | 0                                           | 1             | 0   | _                              |      |

| iver                      |                  |       |         |     |                                                 | Send NACK to indicate last byte,<br>and send STOP followed by<br>START.                        | 1                                           | 1             | 0   | 1110                           |      |

| Master Receiver           | 1000             | 1     | 0       | x   | A master data byte was received; ACK requested. | Send ACK followed by repeated START.                                                           | 1                                           | 0             | 1   | 1110                           |      |

| Aaster                    |                  |       |         |     | Teceived, ACIA Tequested.                       | Send NACK to indicate last byte, and send repeated START.                                      | 1                                           | 0             | 0   | 1110                           |      |

|                           |                  |       |         |     |                                                 | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI).    | 0                                           | 0             | 1   | 1100                           |      |

|                           |                  |       |         |     |                                                 | Send NACK and switch to Mas-<br>ter Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0                                           | 0             | 0   | 1100                           |      |

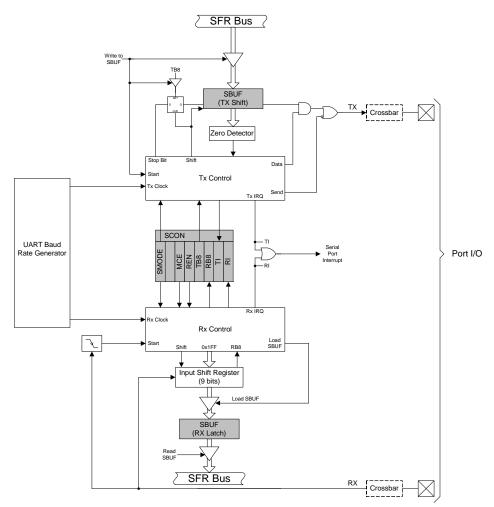

## 27. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "27.1. Enhanced Baud Rate Generation" on page 202). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

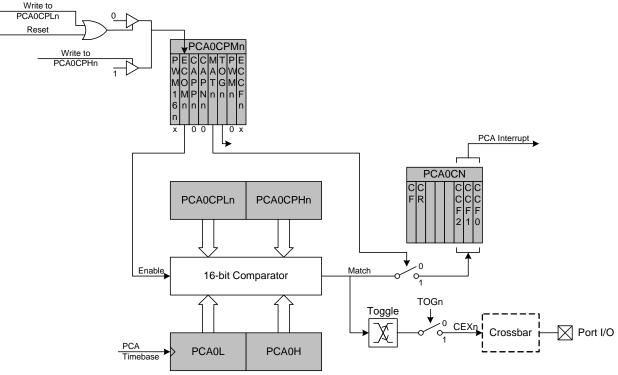

#### 29.3.3. High-Speed Output Mode

In high-speed output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the high-speed output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 29.6. PCA High-Speed Output Mode Diagram

## SFR Definition 29.2. PCA0MD: PCA0 Mode

| Bit   | 7                  | 6                 | 5                                          | 4            | 3             | 2               | 1               | 0          |  |  |

|-------|--------------------|-------------------|--------------------------------------------|--------------|---------------|-----------------|-----------------|------------|--|--|

| Nam   | e CIDL             | WDTE              | WDLCK                                      |              | CPS2          | CPS1            | CPS0            | ECF        |  |  |

| Туре  | e R/W              | R/W               | R/W                                        | R            | R/W           | R/W             | R/W             | R/W        |  |  |

| Rese  | et O               | 1                 | 0                                          | 0            | 0             | 0               | 0               | 0          |  |  |

| SFR A | SFR Address = 0xD9 |                   |                                            |              |               |                 |                 |            |  |  |

| Bit   | Name               |                   |                                            |              | Function      |                 |                 |            |  |  |

| 7     | CIDL               | PCA Counter       | /Timer Idle (                              | Control.     |               |                 |                 |            |  |  |

|       |                    | Specifies PCA     | behavior wh                                | nen CPU is i | n idle mode.  |                 |                 |            |  |  |

|       |                    | 0: PCA contin     | ues to functio                             | on normally  | while the sys | stem controll   | er is in Idle r | node.      |  |  |

|       |                    | 1: PCA operation  | tion is suspe                              | nded while t | he system c   | ontroller is in | idle mode.      |            |  |  |

| 6     | WDTE               | Watchdog Ti       | ner Enable.                                |              |               |                 |                 |            |  |  |

|       |                    | If this bit is se |                                            |              | as the watch  | ndoa timer.     |                 |            |  |  |

|       |                    | 0: Watchdog       |                                            |              |               | lacg allo       |                 |            |  |  |

|       |                    | 0                 | 1: PCA Module 2 enabled as Watchdog Timer. |              |               |                 |                 |            |  |  |

| 5     | WDLCK              | Watchdog Ti       |                                            |              | 5             |                 |                 |            |  |  |

| 5     | VULCK              | •                 |                                            |              |               |                 |                 |            |  |  |

|       |                    | This bit locks/   | unlocks the V                              | Vatchdog Ti  | mer Enable.   | When WDLC       | JK is set, the  | e Watchdog |  |  |

Timer may not be disabled until the next system reset.

|       |          | 0: Watchdog Timer Enable unlocked.<br>1: Watchdog Timer Enable locked.                                                                                        |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4     | Unused   | Read = 0b, Write = Don't care.                                                                                                                                |

| 3:1   | CPS[2:0] | PCA Counter/Timer Pulse Select.                                                                                                                               |

|       |          | These bits select the timebase source for the PCA counter                                                                                                     |

|       |          | 000: System clock divided by 12                                                                                                                               |

|       |          | 001: System clock divided by 4                                                                                                                                |

|       |          | 010: Timer 0 overflow                                                                                                                                         |

|       |          | 011: High-to-low transitions on ECI (max rate = system clock divided by 4)                                                                                    |

|       |          | 100: System clock                                                                                                                                             |

|       |          | 101: External clock divided by 8 (synchronized with the system clock)                                                                                         |

|       |          | 11x: Reserved                                                                                                                                                 |

| 0     | ECF      | PCA Counter/Timer Overflow Interrupt Enable.                                                                                                                  |

|       |          | This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.                                                                                   |

|       |          | 0: Disable the CF interrupt.                                                                                                                                  |

|       |          | 1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is                                                                                |

|       |          | set.                                                                                                                                                          |

| Note: |          | VDTE bit is set to 1, the other bits in the PCA0MD register cannot be modified. To change the the PCA0MD register, the Watchdog Timer must first be disabled. |

### SFR Definition 29.7. PCA0CPLn: PCA0 Capture Module Low Byte

| Bit   | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0CPn[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Addresses: PCA0CPL0 = 0xFB, PCA0CPL1 = 0xE9, PCA0CPL2 = 0xEB

| Bit   | Name                                                                     | Function                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | PCA0CPn[7:0]                                                             | PCA Capture Module Low Byte.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|       |                                                                          | The PCA0CPLn register holds the low byte (LSB) of the 16-bit capture module n.<br>This register address also allows access to the low byte of the corresponding<br>PCA channel's auto-reload value for 9-bit through 15-bit PWM mode and 16-bit<br>PWM mode. The ARSEL bit in register PCA0PWM controls which register is<br>accessed. |  |  |  |  |  |

| Note: | Note: A write to this register will clear the module's ECOMn bit to a 0. |                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

### SFR Definition 29.8. PCA0CPHn: PCA0 Capture Module High Byte

| Bit   | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0CPn[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0             | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Addresses: PCA0CPH0 = 0xFC, PCA0CPH1 = 0xEA, PCA0CPH2 = 0xEC

| Bit  | Name                                                                   | Function                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0  | PCA0CPn[15:8]                                                          | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|      |                                                                        | The PCA0CPHn register holds the high byte (MSB) of the 16-bit capture module n.<br>This register address also allows access to the high byte of the corresponding<br>PCA channel's auto-reload value for 9-bit through 15-bit PWM mode and 16-bit<br>PWM mode. The ARSEL bit in register PCA0PWM controls which register is<br>accessed. |  |  |  |  |  |

| Note | Note: A write to this register will set the module's ECOMn bit to a 1. |                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

## 30. C2 Interface

C8051F80x-83x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface operates using only two pins: a bi-directional data signal (C2D), and a clock input (C2CK). See the C2 Interface Specification for details on the C2 protocol.

#### **30.1. C2 Interface Registers**

The following describes the C2 registers necessary to perform Flash programming functions through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

#### C2 Register Definition 30.1. C2ADD: C2 Address

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|-----|---|---|---|---|---|---|--|

| Name  | C2ADD[7:0] |     |   |   |   |   |   |   |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

| Bit   | Name                                                                                                              |             | Function                                                                                                                         |                                                   |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| 7:0   | C2ADD[7:0]                                                                                                        | C2 Address. |                                                                                                                                  |                                                   |  |  |  |  |  |

|       |                                                                                                                   |             | The C2ADD register is accessed via the C2 interface to select the target Data register for C2 Data Read and Data Write commands. |                                                   |  |  |  |  |  |

|       |                                                                                                                   | Description |                                                                                                                                  |                                                   |  |  |  |  |  |

|       |                                                                                                                   | 0x00        | DEVICEID                                                                                                                         | Selects the Device ID Register (read only)        |  |  |  |  |  |

|       |                                                                                                                   | 0x01        | REVID                                                                                                                            | Selects the Revision ID Register (read only)      |  |  |  |  |  |

|       |                                                                                                                   | 0x02        | FPCTL                                                                                                                            | Selects the C2 Flash Programming Control Register |  |  |  |  |  |

|       |                                                                                                                   | 0xBF        | FPDAT                                                                                                                            | Selects the C2 Flash Data Register                |  |  |  |  |  |

|       |                                                                                                                   | 0xD2        | CRC0AUTO*                                                                                                                        | Selects the CRC0AUTO Register                     |  |  |  |  |  |

|       |                                                                                                                   | 0xD3        | CRC0CNT*                                                                                                                         | Selects the CRC0CNT Register                      |  |  |  |  |  |

|       |                                                                                                                   | 0xCE        | CRC0CN*                                                                                                                          | Selects the CRC0CN Register                       |  |  |  |  |  |

|       |                                                                                                                   | 0xDE        | CRC0DATA*                                                                                                                        | Selects the CRC0DATA Register                     |  |  |  |  |  |

|       |                                                                                                                   | 0xCF        | CRC0FLIP*                                                                                                                        | Selects the CRC0FLIP Register                     |  |  |  |  |  |

|       |                                                                                                                   | 0xDD        | CRC0IN*                                                                                                                          | Selects the CRC0IN Register                       |  |  |  |  |  |

| *Note | Note: CRC registers and functions are described in Section "24. Cyclic Redundancy Check Unit (CRC0)" on page 159. |             |                                                                                                                                  |                                                   |  |  |  |  |  |