# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                  |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f808-gu |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

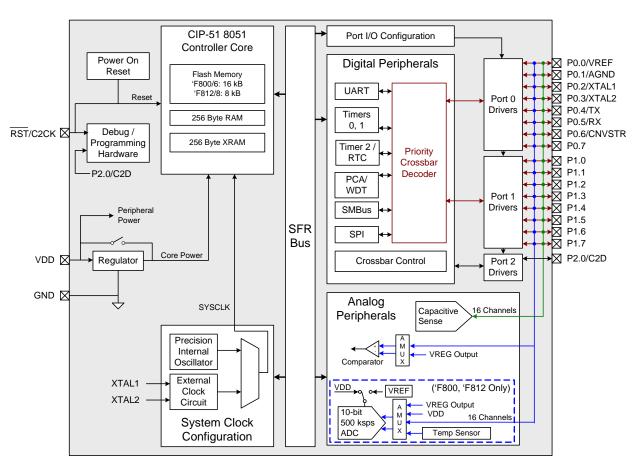

Figure 1.1. C8051F800, C8051F806, C8051F812, C8051F818 Block Diagram

### Figure 5.2. QSOP-24 PCB Land Pattern

### Table 5.2. QSOP-24 PCB Land Pattern Dimensions

| Dimension | Min       | Мах  |  |  |  |

|-----------|-----------|------|--|--|--|

| С         | 5.20 5.30 |      |  |  |  |

| E         | 0.635 BSC |      |  |  |  |

| Х         | 0.30      | 0.40 |  |  |  |

| Y         | 1.50      | 1.60 |  |  |  |

#### Notes: General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on the IPC-7351 guidelines.

#### Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

#### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### Card Assembly

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## SFR Definition 8.1. ADC0CF: ADC0 Configuration

| Bit   | 7             | 6                                                                                                                                | 5                                                                                                                                                                                                                     | 4               | 3               | 2             | 1      | 0       |  |  |  |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------|--------|---------|--|--|--|

| Nam   | е             |                                                                                                                                  | AD0SC[4:0]                                                                                                                                                                                                            | I               | I               | AD0LJST       | AD08BE | AMP0GN0 |  |  |  |

| Туре  | e             |                                                                                                                                  | R/W                                                                                                                                                                                                                   |                 |                 | R/W           | R/W    | R/W     |  |  |  |

| Rese  | et 1          | 1                                                                                                                                | 1                                                                                                                                                                                                                     | 1               | 1               | 0             | 0      | 1       |  |  |  |

| SFR A | Address = 0xB | SC                                                                                                                               |                                                                                                                                                                                                                       |                 |                 |               |        | 11      |  |  |  |

| Bit   | Name          | Function                                                                                                                         |                                                                                                                                                                                                                       |                 |                 |               |        |         |  |  |  |

| 7:3   | AD0SC[4:0]    | ADC0 SAR                                                                                                                         | DC0 SAR Conversion Clock Period Bits.                                                                                                                                                                                 |                 |                 |               |        |         |  |  |  |

|       |               | AD0SC refe                                                                                                                       | AR Conversion clock is derived from system clock by the following equation, where<br>DOSC refers to the 5-bit value held in bits AD0SC4–0. SAR Conversion clock equirements are given in the ADC specification table. |                 |                 |               |        |         |  |  |  |

|       |               |                                                                                                                                  | $ADOSC = \frac{SYSCLK}{CLK_{SAR}} - 1$                                                                                                                                                                                |                 |                 |               |        |         |  |  |  |

| 2     | AD0LJST       | ADC0 Left 、                                                                                                                      | Justify Sele                                                                                                                                                                                                          | ct.             |                 |               |        |         |  |  |  |

|       |               |                                                                                                                                  | 0: Data in ADC0H:ADC0L registers are right-justified.                                                                                                                                                                 |                 |                 |               |        |         |  |  |  |

|       |               | 1: Data in ADC0H:ADC0L registers are left-justified.<br><b>Note:</b> The AD0LJST bit is only valid for 10-bit mode (AD08BE = 0). |                                                                                                                                                                                                                       |                 |                 |               |        |         |  |  |  |

| 1     | AD08BE        | 8-Bit Mode                                                                                                                       |                                                                                                                                                                                                                       |                 |                 | //2008E = 0). |        |         |  |  |  |

|       |               | • =                                                                                                                              | 0: ADC operates in 10-bit mode (normal).                                                                                                                                                                              |                 |                 |               |        |         |  |  |  |

|       |               | •                                                                                                                                | 1: ADC operates in 8-bit mode.                                                                                                                                                                                        |                 |                 |               |        |         |  |  |  |

|       |               | Note: When                                                                                                                       | AD08BE is se                                                                                                                                                                                                          | et to 1, the AD | 00LJST bit is i | gnored.       |        |         |  |  |  |

| 0     | AMP0GN0       | ADC Gain C                                                                                                                       |                                                                                                                                                                                                                       |                 |                 |               |        |         |  |  |  |

|       |               | 0: Gain = 0.<br>1: Gain = 1                                                                                                      | 5                                                                                                                                                                                                                     |                 |                 |               |        |         |  |  |  |

|       |               | 1. Gain = 1                                                                                                                      |                                                                                                                                                                                                                       |                 |                 |               |        |         |  |  |  |

## 11. Voltage Regulator (REG0)

C8051F80x-83x devices include an internal voltage regulator (REG0) to regulate the internal core supply to 1.8 V from a  $V_{DD}$  supply of 1.8 to 3.6 V. A power-saving mode is built into the regulator to help reduce current consumption in low-power applications. This mode is accessed through the REG0CN register (SFR Definition 11.1). Electrical characteristics for the on-chip regulator are specified in Table 7.5 on page 41

Under default conditions, when the device enters STOP mode the internal regulator will remain on. This allows any enabled reset source to generate a reset for the device and bring the device out of STOP mode. For additional power savings, the STOPCF bit can be used to shut down the regulator and the internal power network of the device when the part enters STOP mode. When STOPCF is set to 1, the RST pin or a full power cycle of the device are the only methods of generating a reset.

## SFR Definition 11.1. REG0CN: Voltage Regulator Control

| Bit   | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| Name  | STOPCF |     |     |     |     |     |     |     |

| Туре  | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOPCF   | Stop Mode Configuration.                                                                                                                                                                                                                                                            |

|     |          | This bit configures the regulator's behavior when the device enters STOP mode.<br>0: Regulator is still active in STOP mode. Any enabled reset source will reset the<br>device.<br>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset<br>the device. |

| 6:0 | Reserved | Must write to 000000b.                                                                                                                                                                                                                                                              |

features of the C8051F80x-83x devices.

| Action                                                                   | C2 Debug      | User Firmware executing from: |               |  |  |

|--------------------------------------------------------------------------|---------------|-------------------------------|---------------|--|--|

|                                                                          | Interface     | an unlocked page              | a locked page |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)      | Permitted     | Permitted                     | Permitted     |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)        | Not Permitted | FEDR                          | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)      | Permitted     | Permitted                     | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)       | Not Permitted | FEDR                          | Permitted     |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted     | Permitted                     | Permitted     |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted | FEDR                          | Permitted     |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted     | FEDR                          | FEDR          |  |  |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | Only by C2DE  | FEDR                          | FEDR          |  |  |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted | FEDR                          | FEDR          |  |  |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted | FEDR                          | FEDR          |  |  |

| Read, Write or Erase Reserved Area                                       | Not Permitted | FEDR                          | FEDR          |  |  |

#### Table 19.1. Flash Security Summary

C2DE—C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte) FEDR—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is 1 after reset)

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

### 19.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of VDD, system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the VDD Monitor must be enabled and enabled as a reset source on C8051F80x-83x devices for the Flash to be successfully modified. If either the VDD Monitor or the VDD Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

### 21.1. Power-On Reset

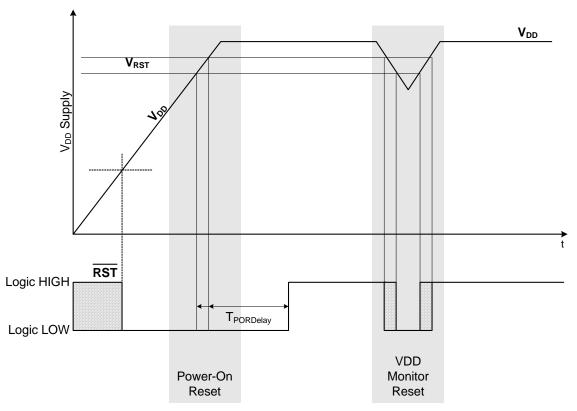

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 21.2. plots the power-on and V<sub>DD</sub> monitor reset timing. The maximum V<sub>DD</sub> ramp time is 1 ms; slower ramp times may cause the device to be released from reset before V<sub>DD</sub> reaches the V<sub>RST</sub> level. For ramp times less than 1 ms, the power-on reset delay (T<sub>PORDelay</sub>) is typically less than 10 ms.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled and selected as a reset source following a power-on reset.

Figure 21.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

### 22.2. Programmable Internal High-Frequency (H-F) Oscillator

All C8051F80x-83x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICL register as defined by SFR Definition 22.2.

On C8051F80x-83x devices, OSCICL is factory calibrated to obtain a 24.5 MHz base frequency.

The internal oscillator output frequency may be divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

The precision oscillator supports a spread spectrum mode which modulates the output frequency in order to reduce the EMI generated by the system. When enabled (SSE = 1), the oscillator output frequency is modulated by a stepped triangle wave whose frequency is equal to the oscillator frequency divided by 384 (63.8 kHz using the factory calibration). The maximum deviation from the center frequency is  $\pm 0.75\%$ . The output frequency updates occur every 32 cycles and the step size is typically 0.25% of the center frequency.

#### SFR Definition 22.2. OSCICL: Internal H-F Oscillator Calibration

| Bit   | 7           | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|-------------|--------|--------|--------|--------|--------|--------|--------|--|--|--|

| Name  | OSCICL[6:0] |        |        |        |        |        |        |        |  |  |  |

| Туре  | R/W         |        |        |        |        |        |        |        |  |  |  |

| Reset | Varies      | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |  |  |

SFR Address = 0xB3

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | OSCICL[7:0] | Internal Oscillator Calibration Bits.                                                                                                                                                                                                                                                                     |

|     |             | These bits determine the internal oscillator period. When set to 00000000b, the H-F oscillator operates at its fastest setting. When set to 1111111b, the H-F oscillator operates at its slowest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz. |

## SFR Definition 22.4. OSCXCN: External Oscillator Control

| Bit   | 7      | 6 | 5          | 4  | 3 | 2         | 1 | 0 |  |

|-------|--------|---|------------|----|---|-----------|---|---|--|

| Name  | XTLVLD | Х | (OSCMD[2:0 | )] |   | XFCN[2:0] |   |   |  |

| Туре  | R      |   | R/W        |    | R | R/W       |   |   |  |

| Reset | 0      | 0 | 0          | 0  | 0 | 0         | 0 | 0 |  |

SFR Address = 0xB1

| Bit | Name        |                                                                |                                                                                     | Function                                  |                 |  |  |  |  |  |

|-----|-------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|

| 7   | XTLVLD      | Crystal                                                        | Oscillator Valid Flag.                                                              |                                           |                 |  |  |  |  |  |

|     |             | •                                                              | nly when XOSCMD = 11                                                                |                                           |                 |  |  |  |  |  |

|     |             | -                                                              | Crystal Oscillator is unused or not yet stable.                                     |                                           |                 |  |  |  |  |  |

|     |             | ,                                                              | al Oscillator is running ar                                                         |                                           |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa                                                        | I Oscillator Mode Selec                                                             | ct.                                       |                 |  |  |  |  |  |

|     |             |                                                                | 0x: External Oscillator circuit off.                                                |                                           |                 |  |  |  |  |  |

|     |             |                                                                | ternal CMOS Clock Mode                                                              |                                           |                 |  |  |  |  |  |

|     |             |                                                                | ernal CMOS Clock Mode                                                               | e with divide by 2 stage.                 |                 |  |  |  |  |  |

|     |             |                                                                | Oscillator Mode.                                                                    |                                           |                 |  |  |  |  |  |

|     |             |                                                                | pacitor Oscillator Mode.                                                            |                                           |                 |  |  |  |  |  |

|     |             | -                                                              | vstal Oscillator Mode.                                                              | divida by 2 staga                         |                 |  |  |  |  |  |

|     |             |                                                                | 11: Crystal Oscillator Mode with divide by 2 stage.<br>Read = 0; Write = Don't Care |                                           |                 |  |  |  |  |  |

| 3   | Unused      |                                                                |                                                                                     |                                           |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | External Oscillator Frequency Control Bits.                    |                                                                                     |                                           |                 |  |  |  |  |  |

|     |             | Set according to the desired frequency for Crystal or RC mode. |                                                                                     |                                           |                 |  |  |  |  |  |

|     |             |                                                                | Set according to the desired K Factor for C mode.                                   |                                           |                 |  |  |  |  |  |

|     |             | XFCN                                                           | Crystal Mode                                                                        | RC Mode                                   | C Mode          |  |  |  |  |  |

|     |             | 000                                                            | f ≤ 32 kHz                                                                          | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001                                                            | 32 kHz < f ≤ 84 kHz                                                                 | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010                                                            | 84 kHz < f ≤ 225 kHz                                                                | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011                                                            | 225 kHz < f ≤ 590 kHz                                                               | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |  |  |  |  |  |

|     |             | 100                                                            | 590 kHz < f ≤ 1.5 MHz                                                               | 200 kHz < f $\leq$ 400 kHz                | K Factor = 65   |  |  |  |  |  |

|     |             | 101                                                            | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                                             | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |

|     |             | 110                                                            | $4 \text{ MHz} < f \le 10 \text{ MHz}$                                              | 800 kHz $<$ f $\leq$ 1.6 MHz              | K Factor = 664  |  |  |  |  |  |

|     |             | 111                                                            | 10 MHz < f ≤ 30 MHz                                                                 | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |

| Special<br>Function<br>Signals<br>(Control<br>Signals)<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK) | P0.0 Skipped    | AGND AGND | P0.2 Skipped XTAL1 N | P0.3 Skipped |   | 5 | CNVSTR 9 | 7 |   |   | 2 | 3 | 4 <sup>1</sup> | 5 <sup>1</sup> | 6 <sup>1</sup> | <b>7</b> <sup>1</sup> | Signal Unavailable to Crossbar |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|----------------------|--------------|---|---|----------|---|---|---|---|---|----------------|----------------|----------------|-----------------------|--------------------------------|

| Function<br>SignalsTX0RX0RX0SCKMISOMOSINSS2SDASCLCP0ACP0ASYSCLKCEX0CEX1CEX2ECIT1Pin Skip<br>SettingsIn this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Skipped         | AGND      |                      | Skipped      |   |   | CNVSTR   |   |   |   |   |   |                |                |                |                       | Crossbar                       |

| RX0<br>SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |   |                |                |                |                       | Crossbar                       |

| SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |   |                |                |                |                       | Crossbar                       |

| MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |   |                |                |                |                       | Crossbar                       |

| MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |   |                |                |                |                       | Crossbar                       |

| NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |   |                |                |                |                       | Crossl                         |

| SDA<br>SCL<br>CP00<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |   |                |                |                |                       | ō                              |

| SCL<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P0.0 Skipped    |           | P0.2 Skipped         | P0.3 Skipped |   |   |          |   |   |   |   |   |                |                |                |                       |                                |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skippe     |           | P0.2 Skippe          | P0.3 Skippe  |   |   |          |   |   |   |   |   |                |                |                |                       | e to                           |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Ski        |           | P0.2 Ski             | P0.3 Ski     |   |   |          |   |   |   |   |   |                |                |                |                       | able                           |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0            |           | P0.2                 | P0.3         |   |   |          |   |   |   |   |   |                |                |                |                       | vail                           |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ط<br> <br> <br> |           | ₫.                   | ۹.           |   |   |          |   |   |   |   |   |                |                |                |                       | Jna                            |

| CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |           |                      |              |   |   |          |   |   |   |   |   |                |                |                |                       | al                             |